JP2007194516A - 複合配線基板およびその製造方法、ならびに電子部品の実装体および製造方法 - Google Patents

複合配線基板およびその製造方法、ならびに電子部品の実装体および製造方法 Download PDFInfo

- Publication number

- JP2007194516A JP2007194516A JP2006013376A JP2006013376A JP2007194516A JP 2007194516 A JP2007194516 A JP 2007194516A JP 2006013376 A JP2006013376 A JP 2006013376A JP 2006013376 A JP2006013376 A JP 2006013376A JP 2007194516 A JP2007194516 A JP 2007194516A

- Authority

- JP

- Japan

- Prior art keywords

- wiring board

- electrically insulating

- insulating substrate

- wiring

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73253—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19105—Disposition of discrete passive components in a side-by-side arrangement on a common die mounting substrate

Landscapes

- Production Of Multi-Layered Print Wiring Board (AREA)

Abstract

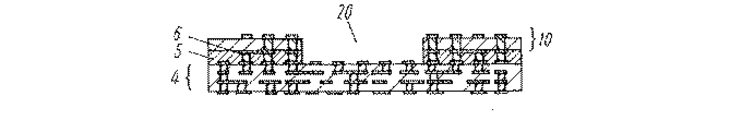

【解決手段】第一の電気絶縁性基材と前記第一の電気絶縁性基材に形成された配線パターンを有する第一の配線基板と、第二の電気絶縁性基材と前記第二の電気絶縁性基材に形成された配線パターンを有し、かつ少なくともその一部にキャビティを形成した第二の配線基板と、前記第一の配線基板と第二の配線基板を厚み方向に接着し、第一の配線基板の配線パターンと前記第二の配線基板の配線パターン間を電気的に接続する導電部を備え、かつ少なくともその一部にキャビティを形成した第三の電気絶縁性基材と、からなる複合配線基板である。

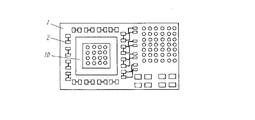

【選択図】図1

Description

以下、実施の形態1を用いて、本発明の特に請求項1、4〜9に記載の発明について図面を参照しながら説明する。

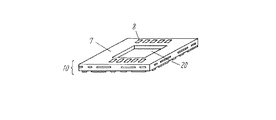

以下、本発明の実施の形態2について、本発明の特に請求項2に記載の発明について、図面を参照しながら説明する。なお、実施の形態1と同一の構造については、同一番号を付与してその説明を省略する。

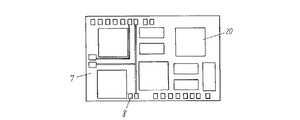

以下、本発明の実施の形態3について、本発明の特に請求項3に記載の発明について、図面を参照しながら説明する。なお、実施の形態1と同一の構造については、同一番号を付与してその説明を省略する。

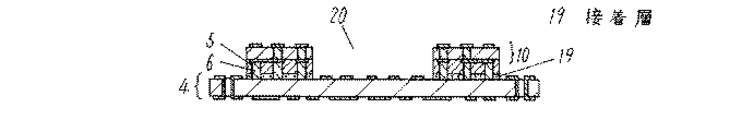

以下、本発明の実施の形態4について、本発明の特に請求項10、12、13に記載の発明について、図面を参照しながら説明する。なお、実施の形態1と同一の構造については、同一番号を付与してその説明を省略する。

以下、本発明の実施の形態5について、本発明の特に請求項11に記載の発明について、図面を参照しながら説明する。なお、実施の形態1と同一の構造については、同一番号を付与してその説明を省略する。

以下、本発明の実施の形態6について、本発明の特に請求項14に記載の発明について、図面を参照しながら説明する。なお、実施の形態1と同一の構造については、同一番号を付与してその説明を省略する。

以下、本発明の実施の形態7について、本発明の特に請求項15に記載の発明について、図面を参照しながら説明する。なお、実施の形態1と同一の構造については、同一番号を付与してその説明を省略する。

以下、本発明の実施の形態8について、本発明の特に請求項16に記載の発明について、図面を参照しながら説明する。なお、実施の形態1と同一の構造については、同一番号を付与してその説明を省略する。

以下、本発明の実施の形態9について、本発明の特に請求項17に記載の発明について、図面を参照しながら説明する。なお、実施の形態1と同一の構造については、同一番号を付与してその説明を省略する。

以下、本発明の実施の形態10について、本発明の特に請求項18に記載の発明について、図面を参照しながら説明する。なお、実施の形態1と同一の構造については、同一番号を付与してその説明を省略する。

2 配線パターン

3 導電部

4 第一の配線基板

5 第三の電気絶縁性基材

6 導電部

7 第二の電気絶縁性基材

8 配線パターン

9 導電部

10 第二の配線基板

11 回路部品

12 回路部品

13 接続電極

14 アンダーフィル

15 接続電極

16 回路部品

17 半田

18 モールド樹脂

19 接着層

20 キャビティ

21 保持基材

22 配線転写シート

Claims (18)

- 第一の電気絶縁性基材と前記第一の電気絶縁性基材に形成された配線パターンを有する第一の配線基板と、

第二の電気絶縁性基材と前記第二の電気絶縁性基材に形成された配線パターンを有し、かつ少なくともその一部にキャビティを形成した第二の配線基板と、

前記第一の配線基板と第二の配線基板を厚み方向に接着し、第一の配線基板の配線パターンと前記第二の配線基板の配線パターン間を電気的に接続する導電部を備え、かつ少なくともその一部にキャビティを形成した第三の電気絶縁性基材と、

からなる複合配線基板。 - 第一の電気絶縁性基材と前記第一の電気絶縁性基材に形成された配線パターンを有する第一の配線基板と、

第二の電気絶縁性基材と、前記第二の電気絶縁性基材に形成された配線パターンを有し、かつ少なくともその一部にキャビティを形成した第二の配線基板と、

前記第一の配線基板と第二の配線基板の少なくとも一つを厚み方向に接着し、第一の配線基板の配線パターンと前記第二の配線基板の配線パターン間を電気的に接続する導電部を備え、かつ少なくともその一部にキャビティを形成した第三の電気絶縁性基材と、第三の電気絶縁性基材の少なくとも一つの面に形成された接着剤層と、

からなる複合配線基板。 - 第一および第二の配線基板は配線パターン間を接続するスルーホールまたは、ビアを含む多層配線基板から構成されていることを特徴とする請求項1もしくは2に記載の複合配線基板。

- 第一ないし第三の電気絶縁性基材のいずれか一つが、可撓性を有するフィルム基材で構成されていることを特徴とする請求項1もしくは2に記載の複合配線基板。

- 第一および第二の配線基板は、配線パターンの一部分が第一および第二の電気絶縁性基材に埋設されていることを特徴とする請求項1または2に記載の複合配線基板。

- 第三の電気絶縁性基材は、無機フィラと熱硬化性樹脂を含む混合物であることを特徴とする請求項1または2に記載の複合配線基板。

- 第三の電気絶縁性基材の熱膨張係数は、第一と第二の配線基板の熱膨張係数の間であることを特徴とする請求項1または2に記載の複合配線基板。

- 第三の電気絶縁性基材の弾性率は、第一と第二の配線基板の弾性率よりも小さいことを特徴とする請求項1または2に記載の複合配線基板。

- 第二の配線基板に形成されたキャビティの面積は、第三の電気絶縁性基材に形成されたキャビティの面積と同じかあるいはそれよりも大きいことを特徴とする請求項1または2に記載の複合配線基板。

- 第一と第二の配線基板上に少なくとも一つ以上の回路部品が実装され、請求項1〜9のいずれか一つに記載の複合配線基板を有して成る電子部品の実装体。

- 第一と第二の配線基板上に少なくとも一つ以上の回路部品が実装され、

第二の配線基板の少なくとも一部と密着し、第二の配線基板に実装された回路部品の少なくとも一部を覆っているモールド樹脂が形成され、請求項1〜9のいずれか一つに記載の複合配線基板を有してなる電子部品の実装体。 - 回路部品の少なくとも一部と第三の電気絶縁性基材は密着していないことを特徴とする請求項10に記載の電子部品の実装体。

- 回路部品は、半導体、コンデンサ、抵抗、コイル、遮断素子の少なくとも1つを含む請求項10または11に記載の電子部品の実装体。

- 第二の配線基板にキャビティを形成する工程と、

第三の電気絶縁性基材に導電部を形成する工程と、

第三の電気絶縁性基材にキャビティを形成する工程と、

第一の配線基板と第二の配線基板を第三の電気絶縁性基材を介して積層する工程と、第三の電気絶縁性基材を硬化する工程と

を備えた複合配線基板の製造方法。 - 第二の配線基板にキャビティを形成する工程と、

第三の電気絶縁性基材に導電部を形成する工程と、

第三の電気絶縁性基材にキャビティを形成する工程と、

第二の配線基板と第三の電気絶縁性基材を積層する工程と、

第三の電気絶縁性基材を硬化する工程と、

第一の配線基板に接着層を形成する工程と、

第一の配線基板と第三の電気絶縁性基材とを接着層を介して積層する工程と、

接着層を硬化する工程と、

を備えた複合配線基板の製造方法。 - 第二の配線基板にキャビティを形成する工程と、

第三の電気絶縁性基材に導電部を形成する工程と、

第三の電気絶縁性基材にキャビティを形成する工程と、

第二の配線基板と第三の電気絶縁性基材を積層する工程と、

第三の電気絶縁性基材を硬化する工程と、

第三の電気絶縁性基材に接着層を形成する工程と、

第一の配線基板と第二の配線基板とを接着層を介して積層する工程と、

接着層を硬化する工程と、

を備えた複合配線基板の製造方法。 - 第一の配線基板に回路部品を実装する工程と、

第二の配線基板にキャビティを形成する工程と、

第三の電気絶縁性基材に導電部を形成する工程と、

第三の電気絶縁性基材にキャビティを形成する工程と、

第一の配線基板と第二の配線基板を第三の電気絶縁性基材を介して積層する工程と、

第三の電気絶縁性基材を硬化する工程と、

第二の配線基板に回路部品を実装する工程と、

を備えた電子部品の実装体の製造方法。 - 第一の配線基板に回路部品を実装する工程と、

第二の配線基板にキャビティを形成する工程と、

第三の電気絶縁性基材に導電部を形成する工程と、

第三の電気絶縁性基材にキャビティを形成する工程と、

第一の配線基板と第二の配線基板を第三の電気絶縁性基材を介して積層する工程と、

第三の電気絶縁性基材を硬化する工程と、

第二の配線基板に回路部品を実装する工程と、

第二の配線基板の少なくとも一部と密着し、第二の配線基板に実装された回路部品の少なくとも一部を覆うようにモールド樹脂を形成するモールド工程と、

を備えた電子部品の実装体の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006013376A JP2007194516A (ja) | 2006-01-23 | 2006-01-23 | 複合配線基板およびその製造方法、ならびに電子部品の実装体および製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006013376A JP2007194516A (ja) | 2006-01-23 | 2006-01-23 | 複合配線基板およびその製造方法、ならびに電子部品の実装体および製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011149808A Division JP2011233915A (ja) | 2011-07-06 | 2011-07-06 | 複合配線基板およびその製造方法、ならびに電子部品の実装体および製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007194516A true JP2007194516A (ja) | 2007-08-02 |

| JP2007194516A5 JP2007194516A5 (ja) | 2009-02-19 |

Family

ID=38449948

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006013376A Pending JP2007194516A (ja) | 2006-01-23 | 2006-01-23 | 複合配線基板およびその製造方法、ならびに電子部品の実装体および製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2007194516A (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009090879A1 (ja) * | 2008-01-18 | 2009-07-23 | Panasonic Corporation | 立体配線板 |

| JP2010238821A (ja) * | 2009-03-30 | 2010-10-21 | Sony Corp | 多層配線基板、スタック構造センサパッケージおよびその製造方法 |

| JP2016511552A (ja) * | 2013-03-15 | 2016-04-14 | クアルコム,インコーポレイテッド | 低減された高さのパッケージオンパッケージ構造 |

| JP2016092196A (ja) * | 2014-11-04 | 2016-05-23 | 日本特殊陶業株式会社 | 配線基板 |

| JP2019080037A (ja) * | 2017-10-20 | 2019-05-23 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | プリント回路基板 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07273464A (ja) * | 1994-03-31 | 1995-10-20 | Ibiden Co Ltd | Ic搭載用プリント配線板の製造方法 |

| JPH09214088A (ja) * | 1996-01-31 | 1997-08-15 | Sumitomo Kinzoku Electro Device:Kk | セラミック基板のプリント配線基板への実装構造 |

| JP2001250909A (ja) * | 2000-02-03 | 2001-09-14 | Fujitsu Ltd | 電気部品搭載基板のための応力低減インターポーザ |

| JP2005045150A (ja) * | 2003-07-25 | 2005-02-17 | Matsushita Electric Ind Co Ltd | 中間接続用配線基材および多層配線基板、ならびにこれらの製造方法 |

| JP2005209904A (ja) * | 2004-01-23 | 2005-08-04 | Matsushita Electric Ind Co Ltd | 多層配線基板、多層配線基板を備えたモジュール、および、電子機器 |

-

2006

- 2006-01-23 JP JP2006013376A patent/JP2007194516A/ja active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07273464A (ja) * | 1994-03-31 | 1995-10-20 | Ibiden Co Ltd | Ic搭載用プリント配線板の製造方法 |

| JPH09214088A (ja) * | 1996-01-31 | 1997-08-15 | Sumitomo Kinzoku Electro Device:Kk | セラミック基板のプリント配線基板への実装構造 |

| JP2001250909A (ja) * | 2000-02-03 | 2001-09-14 | Fujitsu Ltd | 電気部品搭載基板のための応力低減インターポーザ |

| JP2005045150A (ja) * | 2003-07-25 | 2005-02-17 | Matsushita Electric Ind Co Ltd | 中間接続用配線基材および多層配線基板、ならびにこれらの製造方法 |

| JP2005209904A (ja) * | 2004-01-23 | 2005-08-04 | Matsushita Electric Ind Co Ltd | 多層配線基板、多層配線基板を備えたモジュール、および、電子機器 |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009090879A1 (ja) * | 2008-01-18 | 2009-07-23 | Panasonic Corporation | 立体配線板 |

| US8278565B2 (en) | 2008-01-18 | 2012-10-02 | Panasonic Corporation | Three-dimensional wiring board |

| JP2010238821A (ja) * | 2009-03-30 | 2010-10-21 | Sony Corp | 多層配線基板、スタック構造センサパッケージおよびその製造方法 |

| US8446002B2 (en) | 2009-03-30 | 2013-05-21 | Sony Corporation | Multilayer wiring substrate having a castellation structure |

| JP2016511552A (ja) * | 2013-03-15 | 2016-04-14 | クアルコム,インコーポレイテッド | 低減された高さのパッケージオンパッケージ構造 |

| JP2016092196A (ja) * | 2014-11-04 | 2016-05-23 | 日本特殊陶業株式会社 | 配線基板 |

| JP2019080037A (ja) * | 2017-10-20 | 2019-05-23 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | プリント回路基板 |

| JP7207688B2 (ja) | 2017-10-20 | 2023-01-18 | サムソン エレクトロ-メカニックス カンパニーリミテッド. | プリント回路基板 |

| JP7480458B2 (ja) | 2017-10-20 | 2024-05-10 | サムソン エレクトロ-メカニックス カンパニーリミテッド. | プリント回路基板 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4272693B2 (ja) | 部品内蔵モジュールの製造方法 | |

| US6489685B2 (en) | Component built-in module and method of manufacturing the same | |

| JP4279893B2 (ja) | 回路部品内蔵モジュールの製造方法 | |

| US7849591B2 (en) | Method of manufacturing a printed wiring board | |

| JP2003197849A (ja) | 部品内蔵モジュールとその製造方法 | |

| JP3553043B2 (ja) | 部品内蔵モジュールとその製造方法 | |

| JPH11220262A (ja) | 回路部品内蔵モジュールおよびその製造方法 | |

| JP2003188340A (ja) | 部品内蔵モジュールとその製造方法 | |

| JP2006210870A (ja) | 部品内蔵モジュール及びその製造方法 | |

| JP2011233915A (ja) | 複合配線基板およびその製造方法、ならびに電子部品の実装体および製造方法 | |

| JP2004274035A (ja) | 電子部品内蔵モジュールとその製造方法 | |

| JP2007194516A (ja) | 複合配線基板およびその製造方法、ならびに電子部品の実装体および製造方法 | |

| JP2015133387A (ja) | 配線基板、配線基板の製造方法 | |

| JP4503349B2 (ja) | 電子部品実装体及びその製造方法 | |

| JP4417294B2 (ja) | プローブカード用部品内蔵基板とその製造方法 | |

| JP2004055967A (ja) | 電子部品内蔵基板の製造方法 | |

| KR100699237B1 (ko) | 임베디드 인쇄회로기판 제조방법 | |

| JP2007221117A (ja) | 部品内蔵基板およびその製造方法 | |

| JP4287757B2 (ja) | 回路部品内蔵モジュール及びその製造方法 | |

| KR20220061099A (ko) | 회로 기판, 회로 기판의 제조 방법, 및 전자 기기 | |

| JP2005051204A (ja) | 電気部品実装モジュールおよびその製造方法 | |

| JP2006237231A (ja) | 複合配線基板構造体 | |

| JP4509147B2 (ja) | 電気素子内蔵配線基板 | |

| JP2007335487A (ja) | 半導体装置およびその製造方法 | |

| JP2006237230A (ja) | 複合配線基板構造体及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081226 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081226 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20091127 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110428 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110510 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110706 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120207 |