JP2007123773A - 薄膜トランジスタ、及びその製造方法 - Google Patents

薄膜トランジスタ、及びその製造方法 Download PDFInfo

- Publication number

- JP2007123773A JP2007123773A JP2005317486A JP2005317486A JP2007123773A JP 2007123773 A JP2007123773 A JP 2007123773A JP 2005317486 A JP2005317486 A JP 2005317486A JP 2005317486 A JP2005317486 A JP 2005317486A JP 2007123773 A JP2007123773 A JP 2007123773A

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- substrate

- thin film

- film transistor

- drain electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/464—Lateral top-gate IGFETs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/80—Constructional details

- H10K10/82—Electrodes

- H10K10/84—Ohmic electrodes, e.g. source or drain electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

- H10K71/60—Forming conductive regions or layers, e.g. electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/125—Active-matrix OLED [AMOLED] displays including organic TFTs [OTFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

- H10K71/821—Patterning of a layer by embossing, e.g. stamping to form trenches in an insulating layer

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Thin Film Transistor (AREA)

- Electroluminescent Light Sources (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

【解決課題】有機薄膜トランジスタにおいて、ソース電極、ドレイン電極の高精度の微細加工をプラスチック基板などの上に安価なプロセスで実現し、高い性能を安定して実現する手段を提供する。

【解決手段】基板と、ソース電極およびドレイン電極上に形成された有機電子材料膜と、有機電子材料膜上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを含む薄膜トランジスタであって、前記ソース電極およびドレイン電極が、前記基板に形成された溝または穴に埋め込まれ、前記有機電子材料膜と電気的に接触していることを特徴とする薄膜トランジスタである。

【選択図】 図1

【解決手段】基板と、ソース電極およびドレイン電極上に形成された有機電子材料膜と、有機電子材料膜上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを含む薄膜トランジスタであって、前記ソース電極およびドレイン電極が、前記基板に形成された溝または穴に埋め込まれ、前記有機電子材料膜と電気的に接触していることを特徴とする薄膜トランジスタである。

【選択図】 図1

Description

本発明は、有機電子材料を用いた薄膜トランジスタ素子に関する。

近年、情報機器用のフラットディスプレイの普及が目覚しい。このうち液晶ディスプレイは、液晶の光シャッター機能によりバックライトの光をon/off制御し、カラーフィルターを用いて色彩を得る。これに対し、有機ELディスプレイ(あるいは有機LEDディスプレイ)では各画素が個々に発光する(すなわち、自発光する)ので、視野角が広いという利点があるばかりでなく、バックライトが不要であることから薄型化が可能になり、かつフレキシブルな基板上に形成が可能である等、多くの利点を持っている。このため、有機ELディスプレイは次世代のディスプレイとして期待されている。

これらのディスプレイパネルの駆動方式は、大別して2つの種類に分けることができる。第一の駆動方式は、パッシブマトリックス型(あるいは、デューティー駆動方式、単純マトリックス方式)と呼ばれているものである。これは、複数のストライプ電極が行と列にマトリックス状に組み合わされ、行電極と列電極のそれぞれの交点に位置する画素を行電極と列電極に加えた駆動信号により発光させる。発光制御のための信号は、通常、行方向には1行毎に時系列で走査され、同一行の各列には同時に印加される。各画素には通常はアクティブ素子を設けず、行の走査周期のうち各行のデューティー期間にのみ発光制御するようにした方式である。

第二の駆動方式は、各画素にスイッチング素子を持ち、行の走査周期内にわたって発光が可能なアクティブマトリックス型と呼ばれるものである。例えば、100行×150列のパネル全面を100Cd/m2の表示輝度で発光させる場合を想定する。この場合、アクティブマトリックス型では各画素は基本的に常時発光しているので、画素の面積率や各種の損失を考慮しない場合には、100Cd/m2で発光させれば良い。しかし、パッシブマトリックス型で同じ表示輝度を得ようとすると、各画素を駆動するデューティー比が1/100になり、そのデューティー期間(選択期間)のみが発光時間となるので、発光時間内の発光輝度を100倍の10000Cd/m2とする必要がある。

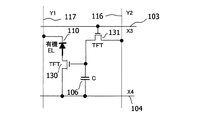

ここで、発光輝度を増すためには発光素子に流す電流を増大させればよい。しかし、例えば有機EL発光素子においては電流を増大させるにつれて発光効率が低下することが知られている。この効率の低下により、アクティブマトリックス型の駆動方式とパッシブマトリックス型の駆動方式を同じ表示輝度で比較した場合、パッシブマトリクス型では相対的に消費電力が大きくなる。また、有機EL素子に流す電流を増すと、発熱等による材料の劣化が生じやすく、表示装置の寿命が短くなるという不都合がある。一方、これらの効率及び寿命の観点から最大電流を制限すると、同じ表示輝度を得るために発光期間を長くする必要が生じる。しかしながら、パッシブマトリックス型駆動方式での発光時間を定めるデューティー比はパネルの行数の逆数であることから、発光期間の延長は、表示容量(駆動ライン数)の制限に結びつく。これらの点から、大面積、高精細度のパネルを実現するにはアクティブマトリックス型の駆動方式を用いる必要があった。通常のアクティブマトリックス駆動の基本回路は、図2に示されるようにスイッチング素子として薄膜トランジスタを用いた方式が知られている。

大面積、高精細度に適したアクティブマトリックス型の駆動方式では、画素のスイッチング素子としてポリシリコンを用いた薄膜トランジスタ(TFT)が最も広く用いられている。しかしながら、例えば、ポリシリコンを用いるTFTを形成するプロセス温度は少なくとも250℃以上の高温であり、フレキシブルなプラスチック基板を用いることが困難である問題点がある。

こういった従来のディスプレイパネルが有する種々の問題点に対処するため、従来から有機薄膜トランジスタ素子を用いることが提案されている。

例えば特開2001−250680号公報(特許文献1)には、有機薄膜整流素子を有機薄膜発光部と直列に接続することが開示されており、また、WO01/15233号(特許文献2)には有機薄膜トランジスタにより画素の駆動制御を行うことが開示されている。特許文献2の開示によれば、駆動素子が有機材料により構成されるので、低温での製造プロセスが可能であり、従ってフレキシブルなプラスチック基板を用いることが可能となる。また、安価な材料やプロセスを選定できるので低コスト化も可能となる。

例えば特開2001−250680号公報(特許文献1)には、有機薄膜整流素子を有機薄膜発光部と直列に接続することが開示されており、また、WO01/15233号(特許文献2)には有機薄膜トランジスタにより画素の駆動制御を行うことが開示されている。特許文献2の開示によれば、駆動素子が有機材料により構成されるので、低温での製造プロセスが可能であり、従ってフレキシブルなプラスチック基板を用いることが可能となる。また、安価な材料やプロセスを選定できるので低コスト化も可能となる。

しかしながら、このような有機薄膜トランジスタにおいては以下の問題があった。

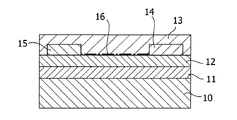

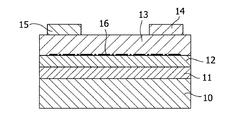

即ち、有機薄膜トランジスタの代表的な構造は図3に示すようなボトムコンタクトと呼ばれるもの、図4に示すようなトップコンタクトと呼ばれるもの、及び図10に示すトップゲートと呼ばれるものに大別される。

ボトムコンタクトにおいてはゲート絶縁膜上にソース電極とドレイン電極が直接、あるいは接着層を介して形成され、その後、有機電子材料膜が形成されてなる。一方、トップコンタクトにおいてはゲート絶縁膜上に有機電子材料膜が形成された後、その上にソース電極とドレイン電極が形成される。これら2つはゲートが基板側に形成される(ボトムゲート)。

一方、トップゲート構造においてはゲートが膜表面側に形成される。このトップゲート構造は特に有機電子材料膜がアモルファスで表面が平滑なポリマー系材料の場合に多く用いられている。

いずれの場合もゲート電極に印加されるゲート電圧により、有機電子材料膜のゲート絶縁膜に接した部分に電荷が誘起され、その電荷がソース電極とドレイン電極との間に印加された電圧により移動することにより電流が流れる。このソース電極とドレイン電極の間の電流経路はチャネルと呼ばれるものである。チャネルは、通常ゲート絶縁膜に接した有機電子材料膜の数分子層の極薄い部分に形成される。

ボトムコンタクトにおいてはゲート絶縁膜上にソース電極とドレイン電極が直接、あるいは接着層を介して形成され、その後、有機電子材料膜が形成されてなる。一方、トップコンタクトにおいてはゲート絶縁膜上に有機電子材料膜が形成された後、その上にソース電極とドレイン電極が形成される。これら2つはゲートが基板側に形成される(ボトムゲート)。

一方、トップゲート構造においてはゲートが膜表面側に形成される。このトップゲート構造は特に有機電子材料膜がアモルファスで表面が平滑なポリマー系材料の場合に多く用いられている。

いずれの場合もゲート電極に印加されるゲート電圧により、有機電子材料膜のゲート絶縁膜に接した部分に電荷が誘起され、その電荷がソース電極とドレイン電極との間に印加された電圧により移動することにより電流が流れる。このソース電極とドレイン電極の間の電流経路はチャネルと呼ばれるものである。チャネルは、通常ゲート絶縁膜に接した有機電子材料膜の数分子層の極薄い部分に形成される。

有機薄膜トランジスタに用いられる有機電子材料としてはペンタセン、チオフェン系ポリマー、フルオレンチオフェン系ポリマー、銅フタロシアニン、フラーレンなどがあげられる。このうち特に低分子系のペンタセン、銅フタロシアニン、フラーレンなどの材料は、室温では溶剤に溶解せず、一般には真空蒸着で形成される。一方、チオフェン系ポリマー、フルオレン/チオフェン系ポリマーは溶剤に可溶であり、塗布により薄膜形成が可能であるので、真空プロセスを用いる必要がなく、更なる低コスト化が可能である。

しかしながら、これらの有機電子材料薄膜の電荷移動度は最も高いペンタセンでも8cm2/Vs以下に止まっており、現在有機ELディスプレイの駆動に用いられているポリシリコンの10〜100cm2/Vsに比して小さい。特に塗布形成が可能なポリマー系材料の移動度は更に小さく0.1cm2/Vs以下の値が報告されている。

例えば一般に電界効果型トランジスタの飽和電流Isdは、下式で表される。

Isd=(W/2L)*C*μ*(Vg−Vth)2 (1)

Isd=(W/2L)*C*μ*(Vg−Vth)2 (1)

ここで、WとLはトランジスタのチャネル幅とチャネル長、Cはゲート絶縁膜の単位面積当りの静電容量、μは電子材料の電荷移動度、Vgはゲート電圧、Vthはゲート電圧の閾値電圧である。一定の電圧条件で充分大きなIsdを得るには、C、μが大きいことが望まれるが、これらは用いる材料により定まる物性値である。またWは素子を形成する面積に制限される。Lは例えばフォトリソグラフにより原理的には数10nmまで小さくすることは可能である。即ち、Lを小さくすることにより電荷移動度が小さな材料でも大きなIsdを得ることが可能となる。

しかしながら、小さなLを得るためには一般には高価なプロセスが必要となる。例えば、通常のフォトプロセスは加工精度は高いが一般に高コストであり、特に数μm以下の加工精度を得るには高価な設備が必要とされる。

また、特に塗布形成可能な導電性材料では、従来各種の印刷(例えばIJP、パッド印刷、フレキソ印刷、グラビア印刷)により電極形成がなされる場合もあった。しかしながら、これらの方法での寸法精度はおおよそ20μmが限界であり、上記目的に必要な10μm以下のチャネル長を精度良く得るのは困難であった。

また、特に塗布形成可能な導電性材料では、従来各種の印刷(例えばIJP、パッド印刷、フレキソ印刷、グラビア印刷)により電極形成がなされる場合もあった。しかしながら、これらの方法での寸法精度はおおよそ20μmが限界であり、上記目的に必要な10μm以下のチャネル長を精度良く得るのは困難であった。

これに加えて、特に基板として安価なプラスチック基板を用いる場合は基板の熱膨張率が大きくなるので、別個のパターニングプロセス間でのパターン位置の整合性を取ることが困難になる。上記のチャネル幅Wとチャネル長Lは、その精度が直接トランジスタ特性に反映されるので、少なくともソース電極とドレイン電極とは、一回のパターニングプロセスで再現性が高い方法で精度良く形成されることが望まれていた。

このように、有機材料の特長を生かすために、有機薄膜トランジスタを、安価、かつ高い寸法精度で形成する方法が強く望まれていた。

特開2001−250680号公報

国際公開第01/15233号パンフレット

このように、有機材料の特長を生かすために、有機薄膜トランジスタを、安価、かつ高い寸法精度で形成する方法が強く望まれていた。

よって本発明の目的は、上述の点に鑑み、有機薄膜トランジスタにおいて、ソース電極、ドレイン電極の高精度の微細加工をプラスチック基板などの上に安価なプロセスで実現し、高い性能を安定して実現する手段を提供することである。

本発明は、上記課題を解決するためになされたものである。すなわち、本発明に係る薄膜トランジスタは、上記目的を達成するために、基板と、ソース電極およびドレイン電極上に形成された有機電子材料膜と、有機電子材料膜上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを含む薄膜トランジスタであって、前記ソース電極およびドレイン電極が、前記基板に形成された溝または穴に埋め込まれ、前記有機電子材料膜と電気的に接触していることを特徴とする。

本発明に係る薄膜トランジスタの製造方法は、基板に溝または穴を形成するステップと、前記溝または穴にソース電極およびドレイン電極を形成するステップと、前記ソース電極およびドレイン電極を形成した基板上に有機電子材料膜、ゲート絶縁膜、および、ゲート電極をこの順で形成するステップとを含むことを特徴とする。

本発明に係る薄膜トランジスタの製造方法は、基板に溝または穴を形成するステップと、前記溝または穴にソース電極およびドレイン電極を形成するステップと、前記ソース電極およびドレイン電極を形成した基板上に有機電子材料膜、ゲート絶縁膜、および、ゲート電極をこの順で形成するステップとを含むことを特徴とする。

本発明によれば、有機薄膜トランジスタにおいて、ソース電極、ドレイン電極の高精度の微細加工をプラスチック基板などの上に安価なプロセスで実現し、高い性能を安定して実現する手段を提供することが出来る。加えて、ソース電極、ドレイン電極へのマトリックス状の配線を簡便にし、かつ、素子からのリーク電流を低減する手段を提供することが出来る。

本発明においては、有機電子材料膜、ゲート絶縁膜、ゲート電極が積層して形成され、別個に形成されたソース電極とドレイン電極との間の電流が上記ゲート絶縁膜に接した有機電子材料膜を介して流れ、かつ、上記電流が上記ゲート電極の電位により制御される薄膜電界効果トランジスタであって、上記ソース電極とドレイン電極とが、基板に形成された溝または穴に埋め込まれ、上記有機電子材料膜、ゲート絶縁膜、ゲート電極が、その上に形成されてなることとした。

上記基板の溝または穴の形成は、熱インプリントによることが好ましい。

基材の材質として熱可塑性のプラスチック材料を用いる場合、例えば、押し出し成型などの方法でも所望の溝を形成した基板を作製することは可能である。しかしながら、押し出し成型では基板寸法が金型寸法により制限される。これに対し、熱インプリントは、ガラス転移点以上に加熱された基板に、溝または穴の形成に必要な鋳型を押し付ける方法である。従って、基本的に基板寸法に制限はなく、大面積基板に連続的に溝形成をするのに適した方法である。

基板の材質として、光硬化樹脂を用いることもできるが、その場合、鋳型による成型の後、光照射により硬化させることにより溝または穴を形成する。この場合は、硬化後の樹脂が弾性に乏しくなるので、例えば、製品として可撓性が求められる場合には作製条件に細かな注意が必要となる。

基材の材質として熱可塑性のプラスチック材料を用いる場合、例えば、押し出し成型などの方法でも所望の溝を形成した基板を作製することは可能である。しかしながら、押し出し成型では基板寸法が金型寸法により制限される。これに対し、熱インプリントは、ガラス転移点以上に加熱された基板に、溝または穴の形成に必要な鋳型を押し付ける方法である。従って、基本的に基板寸法に制限はなく、大面積基板に連続的に溝形成をするのに適した方法である。

基板の材質として、光硬化樹脂を用いることもできるが、その場合、鋳型による成型の後、光照射により硬化させることにより溝または穴を形成する。この場合は、硬化後の樹脂が弾性に乏しくなるので、例えば、製品として可撓性が求められる場合には作製条件に細かな注意が必要となる。

上記溝または穴の形成の際の基板の加熱温度としては、用いる基板の材質にもよるが、通常、100℃〜300℃である。

上記溝または穴の形成のために基板にかける圧力としては、通常、10〜200MPaである。

上記溝または穴の形成に用いる鋳型の材質としては特に限定されず、例えば、

シリコン、シリコンカーバイド、サファイア、ダイヤモンド、タンタル、SiO2/Si、SiN/Si等が挙げられる。鋳型は、予め、加熱しておくことが好ましく、加熱温度としては、100〜350℃であることが好ましい。

上記溝または穴ひとつの幅は、鋳型の厚みにもよるが、通常、10nm〜50μmである。

本発明の薄膜トランジスタの製造方法によれば、基板面積が100nm2以上、より好ましくは、1μm2以上の薄膜トランジスタを得ることができる。

上記溝または穴の形成のために基板にかける圧力としては、通常、10〜200MPaである。

上記溝または穴の形成に用いる鋳型の材質としては特に限定されず、例えば、

シリコン、シリコンカーバイド、サファイア、ダイヤモンド、タンタル、SiO2/Si、SiN/Si等が挙げられる。鋳型は、予め、加熱しておくことが好ましく、加熱温度としては、100〜350℃であることが好ましい。

上記溝または穴ひとつの幅は、鋳型の厚みにもよるが、通常、10nm〜50μmである。

本発明の薄膜トランジスタの製造方法によれば、基板面積が100nm2以上、より好ましくは、1μm2以上の薄膜トランジスタを得ることができる。

上記溝または穴同士の間隔が、チャネル長に相当する。本発明によれば、チャネル長は、1〜50μmとすることができる。チャネル長の好ましい上限は、30μm、より好ましい上限は、12μmである。

また、上記ソース電極またはドレイン電極の形成は、導電性材料溶液もしくは導電性材料分散液を、基板に形成された溝または穴に注入することが好ましい。この方法によれば、溝または穴のアスペクト比が高い場合でも溶液または分散液が表面張力による毛細管現象で溝または穴へ注入されるので、その他の膜形成手段(例えば真空蒸着など)に比して容易に電極形成が可能である。また、ソース電極、ドレイン電極は、高価なフォトリソグラフなどの手段を用いることなく、安価に高精度で再現性良く形成することが可能となる。

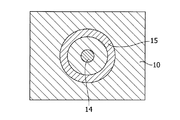

また、ソース電極、もしくはドレイン電極の少なくとも一方が基板を貫通し、上記有機電子材料膜、ゲート絶縁膜、ゲート電極が存在する基板面に対して反対の基板面において電気的に接続されてなることが好ましい。このような構成とすることにより、ソース電極の配線とドレイン電極の配線とが基板の互いに反対面でなされるので、例えば、ディスプレイ駆動で必要とされるマトリックス状の配線が簡便になるという利点が生じる。即ち、薄膜トランジスタのソース電極側の引き出し線とドレイン電極側の引き出し線とが直交する構成でも、各配線は基板の互いに反対面に形成されるので、その交点に絶縁膜を形成する必要がない。また、特に好ましい態様としては、一方の電極が基板を貫通していることで、他方の電極に完全に包囲される構造が挙げられる。

基板を貫通した電極は、電気的接続を確実にするため、上記有機電子材料膜、ゲート絶縁膜、ゲート電極が存在する基板面に対して反対の基板面において、補助的な電極を設けてもよい。

基板を貫通した電極は、電気的接続を確実にするため、上記有機電子材料膜、ゲート絶縁膜、ゲート電極が存在する基板面に対して反対の基板面において、補助的な電極を設けてもよい。

また、上記ソース電極、もしくはドレイン電極のうち、一方の電極が、基板面内で他方の電極の外縁に沿って形成されたものであることが好ましい。

本明細書において、「外縁に沿って形成」とは、一方の電極の輪郭の少なくとも一部分が、距離を隔てて他方の電極の輪郭の一部分を覆うように形成されていることをいう。

従って、一方の電極が、基板面内で他方の電極の外縁に沿って形成されたという場合、一方の電極が、他方の電極によって包囲されているものに限定されず、電極同士が、互いに噛み合ったくし形構造になるように形成されているものであってもよい。

本明細書において、「外縁に沿って形成」とは、一方の電極の輪郭の少なくとも一部分が、距離を隔てて他方の電極の輪郭の一部分を覆うように形成されていることをいう。

従って、一方の電極が、基板面内で他方の電極の外縁に沿って形成されたという場合、一方の電極が、他方の電極によって包囲されているものに限定されず、電極同士が、互いに噛み合ったくし形構造になるように形成されているものであってもよい。

本発明の薄膜トランジスタは、ソース電極またはドレイン電極の一方が、基板面内で他方の電極に包囲されたものであることがより好ましい。

例えば、ドレイン電極を円柱状とし、ソース電極をその周囲にドーナツ状に形成することにより、ソース電極が所謂ガードリングの機能を持ち、リーク電流を抑制することが可能である。特に上記ドーナツ状の形状を、内部電極に対して閉じたものとすることはフォトリソグラフでは2回以上の露光が必要であり位置合わせなど難度が高い作業となるが、本発明の熱インプリントによれば一回の作業ですみ、かつ、両電極の相対位置がずれるおそれがない点において好ましい。

例えば、ドレイン電極を円柱状とし、ソース電極をその周囲にドーナツ状に形成することにより、ソース電極が所謂ガードリングの機能を持ち、リーク電流を抑制することが可能である。特に上記ドーナツ状の形状を、内部電極に対して閉じたものとすることはフォトリソグラフでは2回以上の露光が必要であり位置合わせなど難度が高い作業となるが、本発明の熱インプリントによれば一回の作業ですみ、かつ、両電極の相対位置がずれるおそれがない点において好ましい。

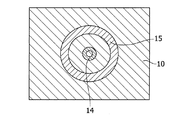

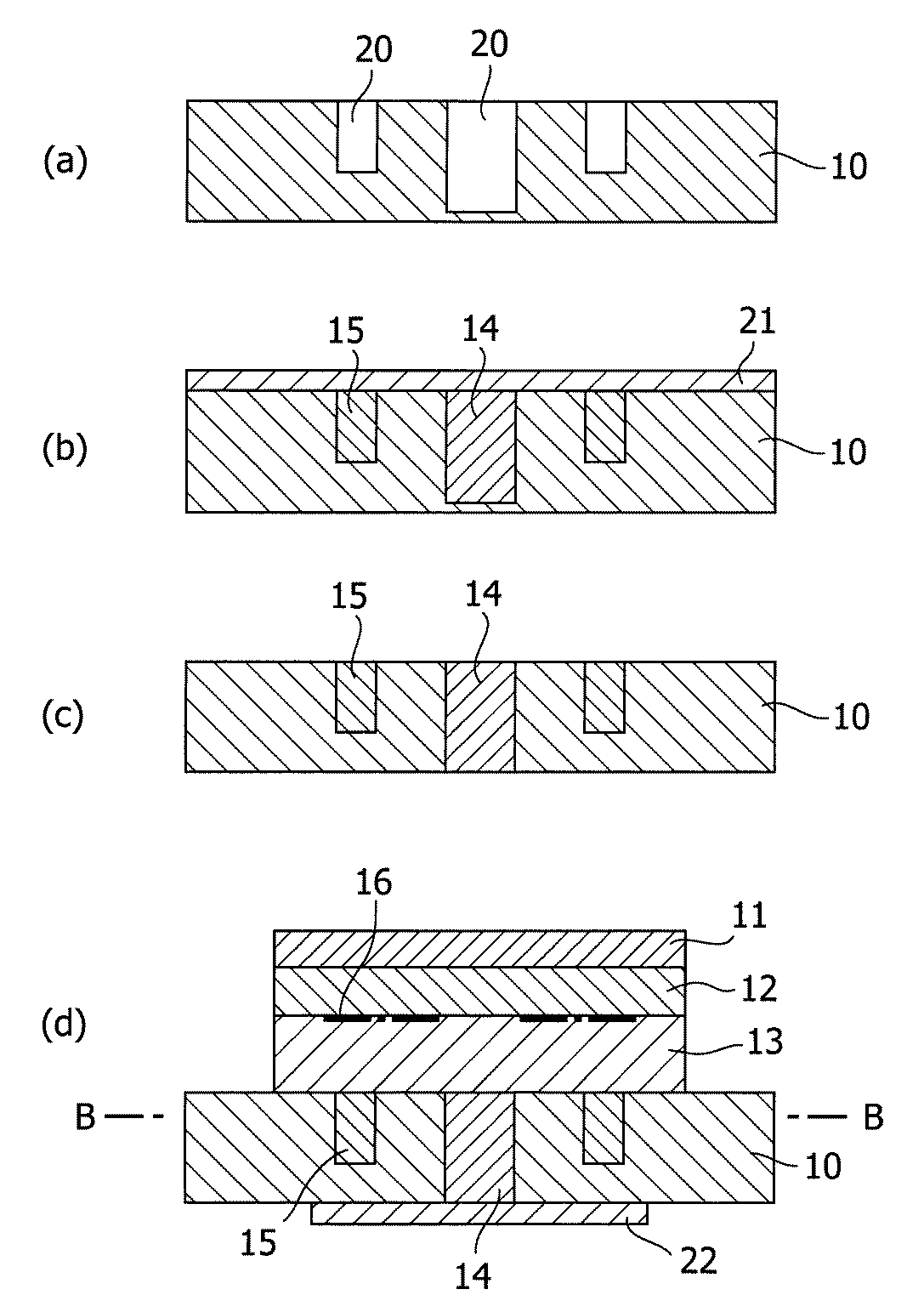

本発明の薄膜トランジスタの作製プロセスと構造の第1の例を図1に示す。熱可塑性プラスチック基板10上に加熱された鋳型を押し付けて、溝20を形成する(図1(a))。その後、当該基板に導電性材料溶液もしくは導電性材料分散液を塗布する。それらの溶液もしくは分散液は、表面張力により上記溝内に注入される(図1(b))。この注入を容易にするには、予め、溝内をオゾン暴露処理や各種親水処理材での被覆などにより親水化しておくことも可能である。塗布した溶液もしくは分散液を乾燥、固化させた後、酸素プラズマなどにより、溝外の導電性材料21を除去することにより、基板内にソース電極とドレイン電極とが一定の距離を隔てた構造が形成される(図1(c))。

なお、塗布した溶液もしくは分散液を乾燥させると体積収縮により溝または穴内に空隙が生じる場合があるが、電気的接続が取れれば機能的問題は生じない。別の理由で空隙を埋める必要がある場合は比較的高い濃度の溶液を用い、重ね塗りをするなどの方法を用いることも可能である。

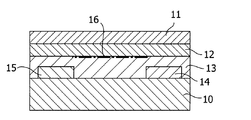

このソース電極およびドレイン電極を形成した基板上に有機電子材料膜、ゲート絶縁膜、ゲート電極が順次、真空蒸着、スピンコート、印刷等の方法で形成される(図1(d))。電荷のチャネル16は、ソース電極とドレイン電極との間の、有機電子材料膜内における、ゲート絶縁膜との界面近傍に形成される。図5にはこの構造の、図1(d) A−A断面での平面図を示した。

なお、塗布した溶液もしくは分散液を乾燥させると体積収縮により溝または穴内に空隙が生じる場合があるが、電気的接続が取れれば機能的問題は生じない。別の理由で空隙を埋める必要がある場合は比較的高い濃度の溶液を用い、重ね塗りをするなどの方法を用いることも可能である。

このソース電極およびドレイン電極を形成した基板上に有機電子材料膜、ゲート絶縁膜、ゲート電極が順次、真空蒸着、スピンコート、印刷等の方法で形成される(図1(d))。電荷のチャネル16は、ソース電極とドレイン電極との間の、有機電子材料膜内における、ゲート絶縁膜との界面近傍に形成される。図5にはこの構造の、図1(d) A−A断面での平面図を示した。

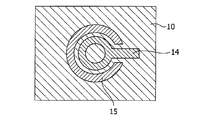

図6には、本発明の薄膜トランジスタの作製プロセスと構造の第2の例を示す。これにおいては、ドレイン電極14はソース電極15より深く形成され(図6(a)、(b))、導電性材料の注入後、溝外の導電性材料21の除去と前後して、基板の反対面をエッチングすることにより、ドレイン電極14は反対面まで貫通させられる(図6(c))。その後、有機電子材料膜13、ゲート絶縁膜12、ゲート電極11が、上記の第1の例と同様にして形成されるが、ドレイン電極14については、反対面での電気的接続を確実にするための電極22を形成することも必要に応じて可能である(図6(d))。

図7にはこの構造の、図6(d) B−B断面での平面図を示した。この例では、ソース電極はドレイン電極の外縁に沿って形成されガードリングの機能を果たすので、ドレイン電圧によるリーク電流が発生しにくい構成となっている。このように閉じた曲線を多重とする構成はフォトリソグラフなどのマスクを使用する方法では(内部の形状を決めるマスクを支える構造が無いので)一回のプロセスでは形成することができないが、本発明の方法では、鋳型が作製してあれば、容易に形成することが可能である。

図7にはこの構造の、図6(d) B−B断面での平面図を示した。この例では、ソース電極はドレイン電極の外縁に沿って形成されガードリングの機能を果たすので、ドレイン電圧によるリーク電流が発生しにくい構成となっている。このように閉じた曲線を多重とする構成はフォトリソグラフなどのマスクを使用する方法では(内部の形状を決めるマスクを支える構造が無いので)一回のプロセスでは形成することができないが、本発明の方法では、鋳型が作製してあれば、容易に形成することが可能である。

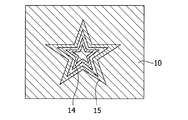

第3の例として、図8に示すように内側の電極を外側の電極と同様にドーナツ形とすることも容易である。この場合は図7に比して溝面積が小さくなり、表面張力による導電性材料液の注入が容易となるが、電極を貫通させる場合は、その内側の基板が導電性材料を介して支えられる構造となる。また、第4の例として、図9に示すように、電極の平面形状を異形として外縁長さを大きくすることにより、チャネル幅を大きくしてトランジスタの飽和電流Isdを大きくすることももちろん可能である。

また、上記の例では電極が貫通しない場合に図5の平面形状、電極が貫通する場合に図7、図8、および図9の平面形状を組み合わせて説明したが、ソース電極とドレイン電極とが逆の組み合わせも当然可能である。

このように形成された本発明の薄膜トランジスタを、従来の素子構造、即ち図3のボトムコンタクト、図4のトップコンタクト、図10のトップゲートと比較すると、ボトムコンタクトとトップゲート構造ではソース電極、ドレイン電極はフォトリソグラフ等の方法で形成されるので、高価な設備と多くのプロセスが必要であったのに対し、本発明の製造方法によれば、設備投資が少なくプロセスも簡便であるという特長を有する。このコスト差はチャネル長が10μm以下の加工を行う場合に特に顕著となるものである。

またトップコンタクトにおけるソース電極およびドレイン電極の形成は元来シャドウマスクにより行われるので、チャネル長30μm以下の形成は困難であった。

このようにして、本発明においては、従来の素子構造の問題点を回避し、高精度の微細加工を安価なプロセスで実現する手段を提供することが出来る。

またトップコンタクトにおけるソース電極およびドレイン電極の形成は元来シャドウマスクにより行われるので、チャネル長30μm以下の形成は困難であった。

このようにして、本発明においては、従来の素子構造の問題点を回避し、高精度の微細加工を安価なプロセスで実現する手段を提供することが出来る。

本発明においては、有機電子材料としては、例えば、ペンタセン、テトラセン、アントラセンなどのアセン系化合物の他、ルブレン、チオフェン、ヘキシルチオフェン系ポリマー、フルオレン/チオフェン系ポリマー、銅フタロシアニン、フラーレン等の材料が好適であるがそれに限定されるものではなく、多くの有機電子材料が適用可能である。

ソース電極およびドレイン電極については各種金属材料、有機導電性材料が適用可能であるが、例えば、有機電子材料を移動する電荷がホールである場合は、ソース電極でのホールの注入を促進し、かつドレイン電極での電子の注入を抑制するため、電極材料としては仕事関数の大きい材料が好適である。特に金属材料としては、分散液として形成しやすい、Au、Ag、Ptなどの微細粒子を主成分とするものが好適である。また、有機導電性材料としては、例えば、ポリ−3,4−エチレンジオキシチオフェン/ポリスチレンスルホネート(PEDOT/PSS)やポリアニリン(PANI)が好適である。

ゲート絶縁膜としては、各種金属酸化物、例えば、シリコン、アルミニウム、タンタル、チタン、ストロンチウム、バリウムなどの酸化物、これら酸化物の混合酸化物を用いることが可能である。また、高分子材料、例えばポリスチレン、ポリビニールアルコール、ポリビニールフェノール、アクリルなどのポリマー材料も用いることが出来る。また、これらの高分子材料に金属酸化物を分散して用いることも可能である。特に金属酸化物は高分子材料に比して誘電率が高い材料が多く、トランジスタを比較的低電圧で駆動することが可能であるという特徴を有する。これに対し高分子材料は比較的誘電率が低いので、高速応答性がよいという特徴がある。

ゲート電極については、各種金属材料、有機導電性材料が適用可能であるが、ゲート絶縁膜への密着性や形成の容易さなどを勘案して決定される。

また、これらの素子を形成する基板の材質としては、各種の基板が可能であるが、熱インプリントにより溝または穴の形成を行う場合は熱可塑性のプラスチック材料を用いることが好ましい。

熱可塑性のプラスチック材料としては特に限定されず、例えば、ポリエーテルイミド(PEI)、 ポリエーテルエーテルケトン(PEEK)、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)、ポリフェニレンサルファイド(PPS)、ポリカーボネート(PC)、ポリスチレン(PS)、ポリメチルメタクリレート(PMMA)などの高分子フィルムを用いることが出来る。

熱可塑性のプラスチック材料としては特に限定されず、例えば、ポリエーテルイミド(PEI)、 ポリエーテルエーテルケトン(PEEK)、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)、ポリフェニレンサルファイド(PPS)、ポリカーボネート(PC)、ポリスチレン(PS)、ポリメチルメタクリレート(PMMA)などの高分子フィルムを用いることが出来る。

本発明の薄膜トランジスタにおけるアスペクト比は、好ましくは、1〜40である。上記アスペクト比のより好ましい上限は、30、より好ましい下限は、3である。

以下に、本発明を、図面を参照して詳細に説明する。同じ部材には同じ符号を付して表した。なお、本発明は以下に説明する形態に制限されるものではない。

ポリエチレンナフタレート(PEN)基板(厚さ100μm)10を220℃に加熱し、これに別途形成したシリコン製の鋳型を270℃に加熱して押し込むことにより、20 x 100μm(100μmがチャネル幅に相当)、深さ60μmの溝を2本、間隔10μm(チャネル長に相当)で形成した。この溝部に波長254nmの紫外光を照射して親水化した後、導電性材料液としてPEDOT:PSS溶液(Bayer社製、Al4083)をスピンコート法により塗布した。スピンコートの回転数は1000rpm、回転時間は180秒であった。塗布したPEDOT:PSS溶液が溝内へ毛細管現象で浸入するのを確認後、これに120℃、10分の乾燥処理を施した。

次に、酸素プラズマにより溝外のPEDOT:PSSをエッチングして、2本の溝の電気的絶縁を確保した。この時、外部回路との電気的接続を得るための導電部はマスクによりエッチングを避けて確保した。

次に、酸素プラズマにより溝外のPEDOT:PSSをエッチングして、2本の溝の電気的絶縁を確保した。この時、外部回路との電気的接続を得るための導電部はマスクによりエッチングを避けて確保した。

次にチオフェン系ポリマー、ポリ(3−ヘキシルチオフェン)(P3HT)(メルク社製)をp−キシレン中に2mg/mLの濃度で溶解させ、これをスピンコートすることにより厚さ30nmの有機電子材料膜13を得た。その後、ポリスチレン(アルドリッチ社製)を酢酸エチル中に70mg/mlの濃度で溶解させ、これをスピンコートすることにより厚さ300nmのゲート絶縁膜を得た。最後にアルミニウムをポリスチレンゲート絶縁膜上に真空蒸着することにより、膜厚60nmのゲート電極を得た。このようにして実施例1の試料を得た。

厚さ100μmのポリエチレンナフタレート(PEN) シートに20x100μm(100μmがチャネル幅に相当)、深さ60μmの溝を2本、間隔5μm(チャネル長に相当)で形成した基板を押し出し成形で作製し、これを基板として用いた他は実施例1と同様にして実施例2の試料を得た。

導電性材料液としてAg微粒子分散液(ナノメタルインク、真空冶金株式会社製)を用い、乾燥条件を150℃、120分とした。また、溝部以外の導電部のエッチングを希硝酸によって行った以外は実施例1と同様にして実施例3の試料を得た。

ポリエチレンテレフタレート(PET)基板(厚さ50μm)10を200℃に加熱し、これに別途形成したシリコン製の鋳型を260℃に加熱して押し込むことにより、内径30μmx外径40μm、深さ30μmの溝と、内径50μmx外径60μm、深さ45μmの溝とを同心円状に形成した。両溝の間隔10μmがチャネル長、チャネルに面する溝円周(各40、50μm)がチャネル幅に相当する。実施例1と同様にして、波長254nmの紫外光を照射して親水化した後、導電性材料液としてPEDOT:PSS溶液(Bayer社製、Al4083)をスピンコート法により塗布した。その後、基板の反対面を酸素プラズマエッチにより研磨して外周溝にドレイン電極を貫通させた。次に実施例1と同様にして有機電子材料膜13としてチオフェン系ポリマー、ポリ(3−ヘキシルチオフェン)(P3HT)(メルク社製)をp−キシレン中に2mg/mLの濃度で溶解させ、これをスピンコートすることにより厚さ30nmの膜を得た。その後、ポリスチレン(アルドリッチ社製)を酢酸エチル中に70mg/mlの濃度で溶解させ、これをスピンコートすることにより厚さ300nmの膜を得た。最後にアルミニウムをポリスチレンゲート絶縁膜上に真空蒸着することにより、膜厚60nmで成膜してゲート電極とした。このようにして実施例4の試料を得た。

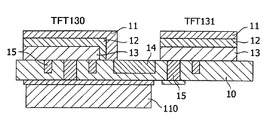

実施例4と同様の方法で、薄膜トランジスタを2個1組で100組、10行x10列のマトリックス状に形成した。また1組のトランジスタにキャパシタと発光素子を付加して図2に示す回路を構成した。2個の薄膜トランジスタは図12に示すように、基板に対してゲート電極を同じ側に形成し、スイッチング用TFTでは貫通電極をソース電極、外側電極をドレイン電極として用いた。即ち、行電極線1:103、行電極線2:104、キャパシタ106は薄膜トランジスタのゲート電極側、発光素子110、列電極線1:116、列電極線2:117はゲート電極の反対側の基板面に配することとした(図12では薄膜トランジスタと発光素子以外は図示を省略)。

[比較例1]

実施例1と同様の構造の素子をフォトリソグラフを用いて、従来のトップゲート構造で作製した。即ち、基板上にフォトレジスト(OFPR−800、東京応化工業株式会社)をスピンコートにより厚さ2μmで塗布した後、フォトマスクを通して、紫外光405nm、11mW/cm2を4秒間照射し、照射部を硬化させた。ソース電極とドレイン電極とを形成する部分は、20 x 100μm(100μmがチャネル幅に相当)の像を2本、間隔10μm(チャネル長に相当)とし、この部分はフォトマスクにより紫外光が照射されないようにした。その後、現像液(NMD−3、東京応化工業株式会社),により非照射部を洗い流して現像した後、プリベーク(110℃、90秒)、ポストベーク(130℃、30分)を行った。その上に膜厚100nmの金薄膜を真空蒸着により形成した。更に、フォトレジストをリフトオフにより剥離した後、露出した基板面を波長254nmの紫外光を照射して洗浄し、その上に有機電子材料膜13としてポリ(3−ヘキシルチオフェン)(P3HT)薄膜(メルク社製)、ポリスチレン薄膜、アルミニウム薄膜を実施例1と同様に形成して比較例1の試料を得た。

実施例1と同様の構造の素子をフォトリソグラフを用いて、従来のトップゲート構造で作製した。即ち、基板上にフォトレジスト(OFPR−800、東京応化工業株式会社)をスピンコートにより厚さ2μmで塗布した後、フォトマスクを通して、紫外光405nm、11mW/cm2を4秒間照射し、照射部を硬化させた。ソース電極とドレイン電極とを形成する部分は、20 x 100μm(100μmがチャネル幅に相当)の像を2本、間隔10μm(チャネル長に相当)とし、この部分はフォトマスクにより紫外光が照射されないようにした。その後、現像液(NMD−3、東京応化工業株式会社),により非照射部を洗い流して現像した後、プリベーク(110℃、90秒)、ポストベーク(130℃、30分)を行った。その上に膜厚100nmの金薄膜を真空蒸着により形成した。更に、フォトレジストをリフトオフにより剥離した後、露出した基板面を波長254nmの紫外光を照射して洗浄し、その上に有機電子材料膜13としてポリ(3−ヘキシルチオフェン)(P3HT)薄膜(メルク社製)、ポリスチレン薄膜、アルミニウム薄膜を実施例1と同様に形成して比較例1の試料を得た。

[比較例2]

実施例4と類似の構成を従来の基板面上構造で試作した。即ち、ポリエチレンテレフタレート(PET)基板(厚さ50μm)10上に、内径30μm x 外径40μmのドーナツ状電極と、内径50μm x 外径60μmのドーナツ状電極とを比較例1と同様の方法で形成した。この時、両電極が同一平面上に形成されており、内側電極の電気的接続の必要性から、外側のドーナツ電極の一部は、図11のように切りかけのある形状となる。

実施例4と類似の構成を従来の基板面上構造で試作した。即ち、ポリエチレンテレフタレート(PET)基板(厚さ50μm)10上に、内径30μm x 外径40μmのドーナツ状電極と、内径50μm x 外径60μmのドーナツ状電極とを比較例1と同様の方法で形成した。この時、両電極が同一平面上に形成されており、内側電極の電気的接続の必要性から、外側のドーナツ電極の一部は、図11のように切りかけのある形状となる。

以上の実施例、比較例の試料の素子特性を表1にまとめた。実施例1、実施例2および実施例3は比較例1に比して移動度や飽和電流Isd(Vg=−20V)の値は同等である(実施例2は、W/Lが実施例1、実施例3、および比較例1の2倍なので、飽和電流Isdは約2倍となっている)。リーク電流も同等であるが、作製した素子100個でのIsdの標準偏差は若干小さくなっており、かつ作業時間(素子100個を作製する時間)は、大幅に短縮されている。これは、比較例1におけるソース/ドレイン電極の形成では、(1)フォトレジスト塗布、(2)紫外光照射、(3)現像、(4)プリベーク、(5)ポストベーク、(6)金薄膜真空蒸着、(7)フォトレジストリフトオフ、(8)基板洗浄、と8ステップのプロセスが必要とされるのに対し、実施例1および実施例2においては、(1)基板への溝形成、(2)導電材料塗布、(3)エッチング、の3ステップであり、かつ各ステップが簡便であるからである。

また、実施例4についても、比較例2に対し作業時間が大幅に短縮されている他、リーク電流は比較例2に対し大きく低減されている。これは比較例2の場合はソース電極によるドレイン電極のガードリング効果が不完全なためと推定される。

また、実施例4についても、比較例2に対し作業時間が大幅に短縮されている他、リーク電流は比較例2に対し大きく低減されている。これは比較例2の場合はソース電極によるドレイン電極のガードリング効果が不完全なためと推定される。

また、実施例5においては、行電極線と列電極線の基板上での交差を回避でき、プロセスが簡便となったのに加えて、発光素子を形成する基板面に形成する素子数が減少するので、発光素子の面積比率を高めることが可能となった。

このように、本発明により、有機薄膜トランジスタにおいて、ソース電極、ドレイン電極の高精度の微細加工をプラスチック基板などの上に安価なプロセスで実現し、高い性能を安定して実現する手段を提供することが出来た。加えて、ソース電極、ドレイン電極へのマトリックス状の配線を簡便にし、かつ、素子からのリーク電流を低減する手段を提供することが出来た。

10:基板、

11:ゲート電極、

12:ゲート絶縁膜、

13:有機電子材料膜

14:ドレイン電極、

15:ソース電極、

16:チャネル

20:溝部

21:導電性材料膜

22:反対面電極

103:行電極線1

104:行電極線2

106:キャパシタ

110:発光素子

116:列電極線1

117:列電極線2

130:駆動用薄膜トランジスタ

131:スイッチング用薄膜トランジスタ

11:ゲート電極、

12:ゲート絶縁膜、

13:有機電子材料膜

14:ドレイン電極、

15:ソース電極、

16:チャネル

20:溝部

21:導電性材料膜

22:反対面電極

103:行電極線1

104:行電極線2

106:キャパシタ

110:発光素子

116:列電極線1

117:列電極線2

130:駆動用薄膜トランジスタ

131:スイッチング用薄膜トランジスタ

Claims (9)

- 基板と、ソース電極およびドレイン電極上に形成された有機電子材料膜と、有機電子材料膜上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを含む薄膜トランジスタであって、

前記ソース電極およびドレイン電極が、前記基板に形成された溝または穴に埋め込まれ、前記有機電子材料膜と電気的に接触している薄膜トランジスタ。 - 前記溝または穴が、熱可塑性プラスチック材料からなる前記基板に形成されている請求項1に記載の薄膜トランジスタ。

- 前記ソース電極および/または前記ドレイン電極が、前記基板を貫通している請求項1または2に記載の薄膜トランジスタ。

- 前記ソース電極またはドレイン電極の一方が、基板面内で他方の電極の外縁に沿って形成されたものである請求項1ないし3のいずれかに記載の薄膜トランジスタ。

- 前記ソース電極またはドレイン電極の一方が、基板面内で他方の電極に包囲されたものである請求項4に記載の薄膜トランジスタ。

- 前記ソース電極とドレイン電極とが、互いに噛み合ったくし形構造である請求項4に記載の薄膜トランジスタ。

- 基板に溝または穴を形成するステップと、

前記溝または穴にソース電極およびドレイン電極を形成するステップと、

前記ソース電極およびドレイン電極を形成した基板上に有機電子材料膜、ゲート絶縁膜、および、ゲート電極をこの順で形成するステップとを含む薄膜トランジスタの製造方法。 - 前記基板の溝または穴が、熱インプリントにより形成される請求項7に記載の薄膜トランジスタの製造方法。

- 前記ソース電極および/または前記ドレイン電極が、導電性材料溶液もしくは導電性材料分散液を前記溝または穴へ注入することにより形成される請求項7または8に記載の薄膜トランジスタの製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005317486A JP2007123773A (ja) | 2005-10-31 | 2005-10-31 | 薄膜トランジスタ、及びその製造方法 |

| US11/537,959 US20070131927A1 (en) | 2005-10-31 | 2006-10-02 | Thin film transistor and manufacturing method thereof |

| EP06021020A EP1780815A3 (en) | 2005-10-31 | 2006-10-06 | Organic thin film transistor and manufacturing method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005317486A JP2007123773A (ja) | 2005-10-31 | 2005-10-31 | 薄膜トランジスタ、及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2007123773A true JP2007123773A (ja) | 2007-05-17 |

Family

ID=37744355

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005317486A Withdrawn JP2007123773A (ja) | 2005-10-31 | 2005-10-31 | 薄膜トランジスタ、及びその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20070131927A1 (ja) |

| EP (1) | EP1780815A3 (ja) |

| JP (1) | JP2007123773A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014512108A (ja) * | 2011-04-21 | 2014-05-19 | シーピーアイ イノベーション サービシズ リミテッド | トランジスタ |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2178110A4 (en) * | 2007-08-07 | 2012-08-29 | Panasonic Corp | SEMICONDUCTOR DEVICE, METHOD FOR MANUFACTURING THE SAME, AND IMAGE DISPLAY DEVICE |

| GB0717055D0 (en) * | 2007-09-01 | 2007-10-17 | Eastman Kodak Co | An electronic device |

| KR20090078527A (ko) * | 2008-01-15 | 2009-07-20 | 삼성전자주식회사 | 표시 기판 |

| GB0814917D0 (en) * | 2008-08-15 | 2008-09-24 | Eastman Kodak Co | Patterning method to create a mask |

| JP2010080800A (ja) * | 2008-09-29 | 2010-04-08 | Seiko Instruments Inc | 発光デバイス及びその製造方法 |

| KR20140038161A (ko) * | 2012-09-20 | 2014-03-28 | 한국전자통신연구원 | 박막 트랜지스터 및 그 제조 방법 |

| CN104934330A (zh) * | 2015-05-08 | 2015-09-23 | 京东方科技集团股份有限公司 | 一种薄膜晶体管及其制备方法、阵列基板和显示面板 |

| CN105047675B (zh) * | 2015-08-06 | 2018-06-22 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制作方法、阵列基板和显示装置 |

| CN106784313A (zh) * | 2016-12-27 | 2017-05-31 | 武汉华星光电技术有限公司 | 有机薄膜晶体管及其制备方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20040036201A1 (en) * | 2000-07-18 | 2004-02-26 | Princeton University | Methods and apparatus of field-induced pressure imprint lithography |

| US6517995B1 (en) * | 1999-09-14 | 2003-02-11 | Massachusetts Institute Of Technology | Fabrication of finely featured devices by liquid embossing |

| WO2001027998A1 (en) * | 1999-10-11 | 2001-04-19 | Koninklijke Philips Electronics N.V. | Integrated circuit |

| DE10061297C2 (de) * | 2000-12-08 | 2003-05-28 | Siemens Ag | Verfahren zur Sturkturierung eines OFETs |

| GB0229191D0 (en) * | 2002-12-14 | 2003-01-22 | Plastic Logic Ltd | Embossing of polymer devices |

| US20060145140A1 (en) * | 2003-01-14 | 2006-07-06 | Walter Fix | Organic field effect transistor and integrated circuit |

| DE10330062A1 (de) * | 2003-07-03 | 2005-01-27 | Siemens Ag | Verfahren und Vorrichtung zur Strukturierung von organischen Schichten |

| JP2005064427A (ja) * | 2003-08-20 | 2005-03-10 | Elpida Memory Inc | 不揮発性ランダムアクセスメモリおよびその製造方法 |

| EP1829132B8 (en) * | 2004-12-23 | 2010-11-24 | Technische Universität Braunschweig | Material for doped and undoped hole and electron transport layer |

-

2005

- 2005-10-31 JP JP2005317486A patent/JP2007123773A/ja not_active Withdrawn

-

2006

- 2006-10-02 US US11/537,959 patent/US20070131927A1/en not_active Abandoned

- 2006-10-06 EP EP06021020A patent/EP1780815A3/en not_active Withdrawn

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014512108A (ja) * | 2011-04-21 | 2014-05-19 | シーピーアイ イノベーション サービシズ リミテッド | トランジスタ |

| US10090482B2 (en) | 2011-04-21 | 2018-10-02 | Cpi Innovation Services Limited | Transistors |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1780815A2 (en) | 2007-05-02 |

| EP1780815A3 (en) | 2008-02-27 |

| US20070131927A1 (en) | 2007-06-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5599190B2 (ja) | 有機薄膜トランジスタの製造方法 | |

| JP5638944B2 (ja) | 有機薄膜トランジスタ | |

| US8089065B2 (en) | Organic thin film transistors | |

| CN1638544A (zh) | 一种有机电致发光器件及其制造方法 | |

| JP2008235861A (ja) | 薄膜トランジスタアレイ、薄膜トランジスタアレイの製造方法、および薄膜トランジスタアレイを用いたアクティブマトリクス型ディスプレイ | |

| CN1846312A (zh) | 电极基板、薄膜晶体管、显示装置、及其制造方法 | |

| JP5138927B2 (ja) | フレキシブルtft基板及びその製造方法とフレキシブルディスプレイ | |

| CN101582391B (zh) | 图样形成方法、半导体装置制造方法以及显示器制造方法 | |

| JP5439723B2 (ja) | 薄膜トランジスタ、マトリクス基板、電気泳動表示装置および電子機器 | |

| CN101587939A (zh) | 有机薄膜晶体管与像素结构及其制作方法以及显示面板 | |

| JP2007123773A (ja) | 薄膜トランジスタ、及びその製造方法 | |

| CN1782841A (zh) | 有源矩阵基板及其制造方法、电光学装置、电子器件 | |

| CN108493229A (zh) | 显示基板及其制备方法、显示装置 | |

| CN1868073B (zh) | 电致发光显示面板 | |

| JP4707996B2 (ja) | フレキシブルディスプレイ及びその製造方法 | |

| JP4589830B2 (ja) | フレキシブルディスプレイ及びその製造方法 | |

| JP2007335560A (ja) | 有機薄膜トランジスタ、表示装置、有機薄膜トランジスタの製造方法 | |

| WO2010010609A1 (ja) | コンタクトホールの形成方法、及び回路基板 | |

| JP4726440B2 (ja) | 有機又は無機トランジスタ及びその製造方法並びに画像表示装置 | |

| JP2006261528A (ja) | 有機薄膜トランジスタ、それを備えた表示装置および有機薄膜トランジスタの製造方法。 | |

| KR100625969B1 (ko) | 전자 발광 소자 | |

| JP2007134546A (ja) | 薄膜トランジスタ | |

| JP2014123540A (ja) | 有機エレクトロルミネッセンス素子及びその製造方法 | |

| KR20120100293A (ko) | 박막 트랜지스터 및 박막 트랜지스터의 제조 방법 | |

| CN112117333A (zh) | 一种薄膜晶体管及其制备方法、显示基板、显示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080916 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20100707 |