JP2006516821A - 歪みチャネルフィンfetの形成方法 - Google Patents

歪みチャネルフィンfetの形成方法 Download PDFInfo

- Publication number

- JP2006516821A JP2006516821A JP2006502829A JP2006502829A JP2006516821A JP 2006516821 A JP2006516821 A JP 2006516821A JP 2006502829 A JP2006502829 A JP 2006502829A JP 2006502829 A JP2006502829 A JP 2006502829A JP 2006516821 A JP2006516821 A JP 2006516821A

- Authority

- JP

- Japan

- Prior art keywords

- crystalline material

- layer

- fin

- lattice constant

- gate electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

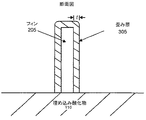

- H10D30/62—Fin field-effect transistors [FinFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/024—Manufacture or treatment of FETs having insulated gates [IGFET] of fin field-effect transistors [FinFET]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/6737—Thin-film transistors [TFT] characterised by the electrodes characterised by the electrode materials

- H10D30/6739—Conductor-insulator-semiconductor electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6741—Group IV materials, e.g. germanium or silicon carbide

- H10D30/6743—Silicon

- H10D30/6744—Monocrystalline silicon

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6741—Group IV materials, e.g. germanium or silicon carbide

- H10D30/6748—Group IV materials, e.g. germanium or silicon carbide having a multilayer structure or superlattice structure

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/751—Insulated-gate field-effect transistors [IGFET] having composition variations in the channel regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/791—Arrangements for exerting mechanical stress on the crystal lattice of the channel regions

Landscapes

- Thin Film Transistor (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/349,042 US6803631B2 (en) | 2003-01-23 | 2003-01-23 | Strained channel finfet |

| PCT/US2004/000967 WO2004068585A1 (en) | 2003-01-23 | 2004-01-15 | Strained channel finfet |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006516821A true JP2006516821A (ja) | 2006-07-06 |

| JP2006516821A5 JP2006516821A5 (enExample) | 2007-03-01 |

Family

ID=32735412

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006502829A Pending JP2006516821A (ja) | 2003-01-23 | 2004-01-15 | 歪みチャネルフィンfetの形成方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US6803631B2 (enExample) |

| EP (1) | EP1593161B1 (enExample) |

| JP (1) | JP2006516821A (enExample) |

| KR (1) | KR20050096155A (enExample) |

| CN (1) | CN100521230C (enExample) |

| TW (1) | TWI326489B (enExample) |

| WO (1) | WO2004068585A1 (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101382846B1 (ko) * | 2012-06-15 | 2014-04-08 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 높은 이동도 및 변형 채널을 갖는 FinFET |

Families Citing this family (94)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6635909B2 (en) * | 2002-03-19 | 2003-10-21 | International Business Machines Corporation | Strained fin FETs structure and method |

| US7358121B2 (en) * | 2002-08-23 | 2008-04-15 | Intel Corporation | Tri-gate devices and methods of fabrication |

| US7091068B1 (en) * | 2002-12-06 | 2006-08-15 | Advanced Micro Devices, Inc. | Planarizing sacrificial oxide to improve gate critical dimension in semiconductor devices |

| WO2004073044A2 (en) * | 2003-02-13 | 2004-08-26 | Massachusetts Institute Of Technology | Finfet device and method to make same |

| US6870179B2 (en) * | 2003-03-31 | 2005-03-22 | Intel Corporation | Increasing stress-enhanced drive current in a MOS transistor |

| TWI231994B (en) * | 2003-04-04 | 2005-05-01 | Univ Nat Taiwan | Strained Si FinFET |

| JP4277021B2 (ja) * | 2003-05-30 | 2009-06-10 | パナソニック株式会社 | 半導体装置 |

| US7045401B2 (en) * | 2003-06-23 | 2006-05-16 | Sharp Laboratories Of America, Inc. | Strained silicon finFET device |

| US6909151B2 (en) | 2003-06-27 | 2005-06-21 | Intel Corporation | Nonplanar device with stress incorporation layer and method of fabrication |

| US7456476B2 (en) | 2003-06-27 | 2008-11-25 | Intel Corporation | Nonplanar semiconductor device with partially or fully wrapped around gate electrode and methods of fabrication |

| US6921982B2 (en) * | 2003-07-21 | 2005-07-26 | International Business Machines Corporation | FET channel having a strained lattice structure along multiple surfaces |

| EP1519420A2 (en) * | 2003-09-25 | 2005-03-30 | Interuniversitaire Microelectronica Centrum vzw ( IMEC) | Multiple gate semiconductor device and method for forming same |

| US6855989B1 (en) * | 2003-10-01 | 2005-02-15 | Advanced Micro Devices, Inc. | Damascene finfet gate with selective metal interdiffusion |

| US6970373B2 (en) * | 2003-10-02 | 2005-11-29 | Intel Corporation | Method and apparatus for improving stability of a 6T CMOS SRAM cell |

| US7144818B2 (en) * | 2003-12-05 | 2006-12-05 | Advanced Micro Devices, Inc. | Semiconductor substrate and processes therefor |

| US6924178B2 (en) * | 2003-12-08 | 2005-08-02 | International Business Machines Corporation | Oxide/nitride stacked in FinFET spacer process |

| US7198995B2 (en) * | 2003-12-12 | 2007-04-03 | International Business Machines Corporation | Strained finFETs and method of manufacture |

| US6936516B1 (en) * | 2004-01-12 | 2005-08-30 | Advanced Micro Devices, Inc. | Replacement gate strained silicon finFET process |

| US7268058B2 (en) * | 2004-01-16 | 2007-09-11 | Intel Corporation | Tri-gate transistors and methods to fabricate same |

| KR100781538B1 (ko) * | 2004-02-07 | 2007-12-03 | 삼성전자주식회사 | 성능이 향상된 멀티 게이트 트랜지스터용 액티브 구조의제조 방법, 이에 의해 제조된 액티브 구조 및 멀티 게이트트랜지스터 |

| US7154118B2 (en) | 2004-03-31 | 2006-12-26 | Intel Corporation | Bulk non-planar transistor having strained enhanced mobility and methods of fabrication |

| US7005302B2 (en) | 2004-04-07 | 2006-02-28 | Advanced Micro Devices, Inc. | Semiconductor on insulator substrate and devices formed therefrom |

| US7176092B2 (en) * | 2004-04-16 | 2007-02-13 | Taiwan Semiconductor Manufacturing Company | Gate electrode for a semiconductor fin device |

| US7084018B1 (en) * | 2004-05-05 | 2006-08-01 | Advanced Micro Devices, Inc. | Sacrificial oxide for minimizing box undercut in damascene FinFET |

| US7579280B2 (en) * | 2004-06-01 | 2009-08-25 | Intel Corporation | Method of patterning a film |

| US7262104B1 (en) | 2004-06-02 | 2007-08-28 | Advanced Micro Devices, Inc. | Selective channel implantation for forming semiconductor devices with different threshold voltages |

| DE102004027691B4 (de) * | 2004-06-07 | 2008-04-30 | Infineon Technologies Ag | Verfahren zum Herstellen eines Steges aus einem Halbleitermaterial |

| US7042009B2 (en) | 2004-06-30 | 2006-05-09 | Intel Corporation | High mobility tri-gate devices and methods of fabrication |

| US7348284B2 (en) * | 2004-08-10 | 2008-03-25 | Intel Corporation | Non-planar pMOS structure with a strained channel region and an integrated strained CMOS flow |

| DE102005045078B4 (de) * | 2004-09-25 | 2009-01-22 | Samsung Electronics Co., Ltd., Suwon | Feldeffekttransistor mit einer verspannten Kanalschicht an Seitenwänden einer Struktur an einem Halbleitersubstrat |

| KR100674914B1 (ko) * | 2004-09-25 | 2007-01-26 | 삼성전자주식회사 | 변형된 채널층을 갖는 모스 트랜지스터 및 그 제조방법 |

| US7422946B2 (en) | 2004-09-29 | 2008-09-09 | Intel Corporation | Independently accessed double-gate and tri-gate transistors in same process flow |

| US7332439B2 (en) | 2004-09-29 | 2008-02-19 | Intel Corporation | Metal gate transistors with epitaxial source and drain regions |

| US7361958B2 (en) | 2004-09-30 | 2008-04-22 | Intel Corporation | Nonplanar transistors with metal gate electrodes |

| JP4064955B2 (ja) * | 2004-09-30 | 2008-03-19 | 株式会社東芝 | 半導体装置及びその製造方法 |

| US20060086977A1 (en) | 2004-10-25 | 2006-04-27 | Uday Shah | Nonplanar device with thinned lower body portion and method of fabrication |

| JP2006135067A (ja) * | 2004-11-05 | 2006-05-25 | Toshiba Corp | 半導体装置およびその製造方法 |

| WO2006069340A2 (en) * | 2004-12-21 | 2006-06-29 | Carnegie Mellon University | Lithography and associated methods, devices, and systems |

| US7193279B2 (en) * | 2005-01-18 | 2007-03-20 | Intel Corporation | Non-planar MOS structure with a strained channel region |

| US7518196B2 (en) | 2005-02-23 | 2009-04-14 | Intel Corporation | Field effect transistor with narrow bandgap source and drain regions and method of fabrication |

| US20060202266A1 (en) | 2005-03-14 | 2006-09-14 | Marko Radosavljevic | Field effect transistor with metal source/drain regions |

| US7858481B2 (en) | 2005-06-15 | 2010-12-28 | Intel Corporation | Method for fabricating transistor with thinned channel |

| US7547637B2 (en) | 2005-06-21 | 2009-06-16 | Intel Corporation | Methods for patterning a semiconductor film |

| US7279375B2 (en) | 2005-06-30 | 2007-10-09 | Intel Corporation | Block contact architectures for nanoscale channel transistors |

| US7402875B2 (en) | 2005-08-17 | 2008-07-22 | Intel Corporation | Lateral undercut of metal gate in SOI device |

| US7400031B2 (en) * | 2005-09-19 | 2008-07-15 | International Business Machines Corporation | Asymmetrically stressed CMOS FinFET |

| US20070090416A1 (en) | 2005-09-28 | 2007-04-26 | Doyle Brian S | CMOS devices with a single work function gate electrode and method of fabrication |

| US7479421B2 (en) | 2005-09-28 | 2009-01-20 | Intel Corporation | Process for integrating planar and non-planar CMOS transistors on a bulk substrate and article made thereby |

| US7309626B2 (en) * | 2005-11-15 | 2007-12-18 | International Business Machines Corporation | Quasi self-aligned source/drain FinFET process |

| US7485503B2 (en) | 2005-11-30 | 2009-02-03 | Intel Corporation | Dielectric interface for group III-V semiconductor device |

| US7402856B2 (en) * | 2005-12-09 | 2008-07-22 | Intel Corporation | Non-planar microelectronic device having isolation element to mitigate fringe effects and method to fabricate same |

| DE102005059231B4 (de) * | 2005-12-12 | 2011-01-13 | Infineon Technologies Ag | Verfahren zum Herstellen eines Verbindungshalbleiter-Feldeffekttransistors mit einer Fin-Struktur und Verbindungshalbleiter-Feldeffekttransistor mit einer Fin-Struktur |

| US7439588B2 (en) * | 2005-12-13 | 2008-10-21 | Intel Corporation | Tri-gate integration with embedded floating body memory cell using a high-K dual metal gate |

| US7512017B2 (en) * | 2005-12-21 | 2009-03-31 | Intel Corporation | Integration of planar and tri-gate devices on the same substrate |

| US7396711B2 (en) | 2005-12-27 | 2008-07-08 | Intel Corporation | Method of fabricating a multi-cornered film |

| US7525160B2 (en) | 2005-12-27 | 2009-04-28 | Intel Corporation | Multigate device with recessed strain regions |

| US20070148926A1 (en) * | 2005-12-28 | 2007-06-28 | Intel Corporation | Dual halo implant for improving short channel effect in three-dimensional tri-gate transistors |

| US20070235763A1 (en) * | 2006-03-29 | 2007-10-11 | Doyle Brian S | Substrate band gap engineered multi-gate pMOS devices |

| US7449373B2 (en) | 2006-03-31 | 2008-11-11 | Intel Corporation | Method of ion implanting for tri-gate devices |

| US7425500B2 (en) | 2006-03-31 | 2008-09-16 | Intel Corporation | Uniform silicide metal on epitaxially grown source and drain regions of three-dimensional transistors |

| US7407847B2 (en) * | 2006-03-31 | 2008-08-05 | Intel Corporation | Stacked multi-gate transistor design and method of fabrication |

| US7442590B2 (en) * | 2006-04-27 | 2008-10-28 | Freescale Semiconductor, Inc | Method for forming a semiconductor device having a fin and structure thereof |

| JP2007299951A (ja) * | 2006-04-28 | 2007-11-15 | Toshiba Corp | 半導体装置およびその製造方法 |

| US20090321830A1 (en) * | 2006-05-15 | 2009-12-31 | Carnegie Mellon University | Integrated circuit device, system, and method of fabrication |

| US8143646B2 (en) | 2006-08-02 | 2012-03-27 | Intel Corporation | Stacking fault and twin blocking barrier for integrating III-V on Si |

| US7999251B2 (en) * | 2006-09-11 | 2011-08-16 | International Business Machines Corporation | Nanowire MOSFET with doped epitaxial contacts for source and drain |

| US7435683B2 (en) * | 2006-09-15 | 2008-10-14 | Intel Corporation | Apparatus and method for selectively recessing spacers on multi-gate devices |

| US7700470B2 (en) | 2006-09-22 | 2010-04-20 | Intel Corporation | Selective anisotropic wet etching of workfunction metal for semiconductor devices |

| US7538391B2 (en) * | 2007-01-09 | 2009-05-26 | International Business Machines Corporation | Curved FINFETs |

| US20080173942A1 (en) * | 2007-01-22 | 2008-07-24 | International Business Machines Corporation | STRUCTURE AND METHOD OF MANUFACTURING A STRAINED FinFET WITH STRESSED SILICIDE |

| US7709893B2 (en) * | 2007-01-31 | 2010-05-04 | Infineon Technologies Ag | Circuit layout for different performance and method |

| WO2009016778A1 (ja) * | 2007-07-27 | 2009-02-05 | Panasonic Corporation | 半導体装置及びその製造方法 |

| US7910994B2 (en) * | 2007-10-15 | 2011-03-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | System and method for source/drain contact processing |

| US8362566B2 (en) | 2008-06-23 | 2013-01-29 | Intel Corporation | Stress in trigate devices using complimentary gate fill materials |

| US8053838B2 (en) * | 2008-06-26 | 2011-11-08 | International Business Machines Corporation | Structures, fabrication methods, design structures for strained fin field effect transistors (FinFets) |

| US20100155801A1 (en) * | 2008-12-22 | 2010-06-24 | Doyle Brian S | Integrated circuit, 1T-1C embedded memory cell containing same, and method of manufacturing 1T-1C memory cell for embedded memory application |

| US7999298B2 (en) * | 2008-12-30 | 2011-08-16 | Intel Corporation | Embedded memory cell and method of manufacturing same |

| US9768305B2 (en) * | 2009-05-29 | 2017-09-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Gradient ternary or quaternary multiple-gate transistor |

| US20100308409A1 (en) * | 2009-06-08 | 2010-12-09 | Globalfoundries Inc. | Finfet structures with fins having stress-inducing caps and methods for fabricating the same |

| US7977174B2 (en) * | 2009-06-08 | 2011-07-12 | Globalfoundries Inc. | FinFET structures with stress-inducing source/drain-forming spacers and methods for fabricating the same |

| US8404592B2 (en) * | 2009-07-27 | 2013-03-26 | GlobalFoundries, Inc. | Methods for fabricating FinFET semiconductor devices using L-shaped spacers |

| US8629478B2 (en) * | 2009-07-31 | 2014-01-14 | Taiwan Semiconductor Manufacturing Company, Ltd. | Fin structure for high mobility multiple-gate transistor |

| CN102315269B (zh) * | 2010-07-01 | 2013-12-25 | 中国科学院微电子研究所 | 一种半导体器件及其形成方法 |

| CN103137671B (zh) * | 2011-12-02 | 2015-06-24 | 中芯国际集成电路制造(上海)有限公司 | 多栅极场效应晶体管及其制作方法 |

| CN103187446B (zh) * | 2011-12-31 | 2016-02-03 | 中芯国际集成电路制造(上海)有限公司 | 多栅极场效应晶体管及其制造方法 |

| EP2741337B1 (en) | 2012-12-07 | 2018-04-11 | IMEC vzw | Semiconductor heterostructure field effect transistor and method for making thereof |

| US9029835B2 (en) * | 2012-12-20 | 2015-05-12 | Intel Corporation | Epitaxial film on nanoscale structure |

| US8872225B2 (en) * | 2012-12-20 | 2014-10-28 | Intel Corporation | Defect transferred and lattice mismatched epitaxial film |

| US9391181B2 (en) * | 2012-12-21 | 2016-07-12 | Intel Corporation | Lattice mismatched hetero-epitaxial film |

| US8823060B1 (en) * | 2013-02-20 | 2014-09-02 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method for inducing strain in FinFET channels |

| US9214555B2 (en) | 2013-03-12 | 2015-12-15 | Taiwan Semiconductor Manufacturing Co., Ltd. | Barrier layer for FinFET channels |

| KR102252224B1 (ko) | 2014-03-24 | 2021-05-14 | 인텔 코포레이션 | 트랜지스터 채널 응용예들에 대한 대체 게이트 프로세스 동안의 핀 스컬프팅 및 클래딩 |

| US9589811B2 (en) * | 2015-06-24 | 2017-03-07 | Varian Semiconductor Equipment Associates, Inc. | FinFET spacer etch with no fin recess and no gate-spacer pull-down |

| US9755073B1 (en) | 2016-05-11 | 2017-09-05 | International Business Machines Corporation | Fabrication of vertical field effect transistor structure with strained channels |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003243667A (ja) * | 2002-02-22 | 2003-08-29 | Toshiba Corp | 半導体装置、半導体装置の製造方法、半導体基板の製造方法 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7163864B1 (en) * | 2000-10-18 | 2007-01-16 | International Business Machines Corporation | Method of fabricating semiconductor side wall fin |

| US6300182B1 (en) * | 2000-12-11 | 2001-10-09 | Advanced Micro Devices, Inc. | Field effect transistor having dual gates with asymmetrical doping for reduced threshold voltage |

| US6475869B1 (en) * | 2001-02-26 | 2002-11-05 | Advanced Micro Devices, Inc. | Method of forming a double gate transistor having an epitaxial silicon/germanium channel region |

| US20020167048A1 (en) * | 2001-05-14 | 2002-11-14 | Tweet Douglas J. | Enhanced mobility NMOS and PMOS transistors using strained Si/SiGe layers on silicon-on-insulator substrates |

| US6635909B2 (en) * | 2002-03-19 | 2003-10-21 | International Business Machines Corporation | Strained fin FETs structure and method |

| US6800910B2 (en) * | 2002-09-30 | 2004-10-05 | Advanced Micro Devices, Inc. | FinFET device incorporating strained silicon in the channel region |

| US6611029B1 (en) * | 2002-11-08 | 2003-08-26 | Advanced Micro Devices, Inc. | Double gate semiconductor device having separate gates |

-

2003

- 2003-01-23 US US10/349,042 patent/US6803631B2/en not_active Expired - Lifetime

-

2004

- 2004-01-15 JP JP2006502829A patent/JP2006516821A/ja active Pending

- 2004-01-15 WO PCT/US2004/000967 patent/WO2004068585A1/en not_active Ceased

- 2004-01-15 EP EP04702513.5A patent/EP1593161B1/en not_active Expired - Lifetime

- 2004-01-15 CN CNB200480002593XA patent/CN100521230C/zh not_active Expired - Fee Related

- 2004-01-15 KR KR1020057013666A patent/KR20050096155A/ko not_active Abandoned

- 2004-01-20 TW TW093101515A patent/TWI326489B/zh not_active IP Right Cessation

- 2004-04-28 US US10/833,112 patent/US6897527B2/en not_active Expired - Lifetime

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003243667A (ja) * | 2002-02-22 | 2003-08-29 | Toshiba Corp | 半導体装置、半導体装置の製造方法、半導体基板の製造方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101382846B1 (ko) * | 2012-06-15 | 2014-04-08 | 타이완 세미콘덕터 매뉴팩쳐링 컴퍼니 리미티드 | 높은 이동도 및 변형 채널을 갖는 FinFET |

| US8729634B2 (en) | 2012-06-15 | 2014-05-20 | Taiwan Semiconductor Manufacturing Company, Ltd. | FinFET with high mobility and strain channel |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200423405A (en) | 2004-11-01 |

| EP1593161A1 (en) | 2005-11-09 |

| TWI326489B (en) | 2010-06-21 |

| CN100521230C (zh) | 2009-07-29 |

| US6803631B2 (en) | 2004-10-12 |

| US20040195627A1 (en) | 2004-10-07 |

| KR20050096155A (ko) | 2005-10-05 |

| US6897527B2 (en) | 2005-05-24 |

| CN1742375A (zh) | 2006-03-01 |

| EP1593161B1 (en) | 2019-04-24 |

| WO2004068585A1 (en) | 2004-08-12 |

| US20040145019A1 (en) | 2004-07-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2006516821A (ja) | 歪みチャネルフィンfetの形成方法 | |

| US7541267B1 (en) | Reversed T-shaped finfet | |

| US6762483B1 (en) | Narrow fin FinFET | |

| US7390701B2 (en) | Method of forming a digitalized semiconductor structure | |

| US7427788B2 (en) | Multi bridge channel field effect transistors with nano-wire channels and methods of manufacturing the same | |

| US6787402B1 (en) | Double-gate vertical MOSFET transistor and fabrication method | |

| US7923314B2 (en) | Field effect transistor and method for manufacturing the same | |

| JP5270094B2 (ja) | 細型化されたボディを有する、狭いボディのダマシン・トライゲートFinFET | |

| US6812119B1 (en) | Narrow fins by oxidation in double-gate finfet | |

| US6855583B1 (en) | Method for forming tri-gate FinFET with mesa isolation | |

| JP4453967B2 (ja) | 均一なチャネル厚さと分離ゲートを有するひずみチャネルFinFET | |

| US6955969B2 (en) | Method of growing as a channel region to reduce source/drain junction capacitance | |

| US7084018B1 (en) | Sacrificial oxide for minimizing box undercut in damascene FinFET | |

| JP2006504267A (ja) | ダブルおよびトリプルゲートmosfetデバイス、およびこれらのmosfetデバイスを製造する方法 | |

| JP5270093B2 (ja) | ダマシンプロセスにより形成されるトライゲートFinFET | |

| US9911601B2 (en) | Epitaxial silicon germanium fin formation using sacrificial silicon fin templates | |

| JP2007165780A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070115 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070115 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20100421 |

|

| RD05 | Notification of revocation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7425 Effective date: 20100902 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101029 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110126 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110727 |