JP2005502202A - 電子デバイスおよび製造方法 - Google Patents

電子デバイスおよび製造方法 Download PDFInfo

- Publication number

- JP2005502202A JP2005502202A JP2003525884A JP2003525884A JP2005502202A JP 2005502202 A JP2005502202 A JP 2005502202A JP 2003525884 A JP2003525884 A JP 2003525884A JP 2003525884 A JP2003525884 A JP 2003525884A JP 2005502202 A JP2005502202 A JP 2005502202A

- Authority

- JP

- Japan

- Prior art keywords

- compound

- spin

- groove

- substrate

- solvent

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 238000004519 manufacturing process Methods 0.000 title abstract description 9

- 150000001875 compounds Chemical class 0.000 claims abstract description 92

- 239000000758 substrate Substances 0.000 claims abstract description 65

- 238000005229 chemical vapour deposition Methods 0.000 claims abstract description 57

- 238000000151 deposition Methods 0.000 claims abstract description 28

- 230000008021 deposition Effects 0.000 claims abstract description 19

- 238000000034 method Methods 0.000 claims description 143

- 239000002904 solvent Substances 0.000 claims description 40

- 238000004140 cleaning Methods 0.000 claims description 35

- 229910052710 silicon Inorganic materials 0.000 claims description 17

- 239000010703 silicon Substances 0.000 claims description 17

- 238000000576 coating method Methods 0.000 claims description 14

- 239000011877 solvent mixture Substances 0.000 claims description 13

- 229920003209 poly(hydridosilsesquioxane) Polymers 0.000 claims description 11

- 239000011248 coating agent Substances 0.000 claims description 10

- LZCLXQDLBQLTDK-UHFFFAOYSA-N ethyl 2-hydroxypropanoate Chemical compound CCOC(=O)C(C)O LZCLXQDLBQLTDK-UHFFFAOYSA-N 0.000 claims description 10

- 125000002496 methyl group Chemical group [H]C([H])([H])* 0.000 claims description 10

- WEVYAHXRMPXWCK-UHFFFAOYSA-N Acetonitrile Chemical compound CC#N WEVYAHXRMPXWCK-UHFFFAOYSA-N 0.000 claims description 9

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 claims description 9

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 claims description 7

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 claims description 7

- 229910000077 silane Inorganic materials 0.000 claims description 7

- BPQQTUXANYXVAA-UHFFFAOYSA-N Orthosilicate Chemical compound [O-][Si]([O-])([O-])[O-] BPQQTUXANYXVAA-UHFFFAOYSA-N 0.000 claims description 6

- 238000002955 isolation Methods 0.000 claims description 6

- YKYONYBAUNKHLG-UHFFFAOYSA-N n-Propyl acetate Natural products CCCOC(C)=O YKYONYBAUNKHLG-UHFFFAOYSA-N 0.000 claims description 6

- 229940090181 propyl acetate Drugs 0.000 claims description 6

- NQPDZGIKBAWPEJ-UHFFFAOYSA-N valeric acid Chemical compound CCCCC(O)=O NQPDZGIKBAWPEJ-UHFFFAOYSA-N 0.000 claims description 6

- 229940116333 ethyl lactate Drugs 0.000 claims description 5

- 238000001312 dry etching Methods 0.000 claims description 4

- 239000000126 substance Substances 0.000 claims description 4

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims description 4

- 150000001408 amides Chemical class 0.000 claims description 3

- 150000001412 amines Chemical class 0.000 claims description 3

- 150000002148 esters Chemical class 0.000 claims description 3

- 229930195733 hydrocarbon Natural products 0.000 claims description 3

- 150000002430 hydrocarbons Chemical class 0.000 claims description 3

- 150000002576 ketones Chemical class 0.000 claims description 3

- 238000001039 wet etching Methods 0.000 claims description 2

- 238000010438 heat treatment Methods 0.000 claims 2

- 150000002170 ethers Chemical class 0.000 claims 1

- 238000005406 washing Methods 0.000 claims 1

- 239000000463 material Substances 0.000 description 40

- 239000003989 dielectric material Substances 0.000 description 16

- 229910052751 metal Inorganic materials 0.000 description 16

- 239000002184 metal Substances 0.000 description 16

- 238000005530 etching Methods 0.000 description 15

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 13

- 235000012431 wafers Nutrition 0.000 description 13

- 229910052581 Si3N4 Inorganic materials 0.000 description 11

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 11

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 8

- 230000015572 biosynthetic process Effects 0.000 description 8

- 238000010304 firing Methods 0.000 description 8

- KFZMGEQAYNKOFK-UHFFFAOYSA-N Isopropanol Chemical compound CC(C)O KFZMGEQAYNKOFK-UHFFFAOYSA-N 0.000 description 6

- OKKJLVBELUTLKV-UHFFFAOYSA-N Methanol Chemical compound OC OKKJLVBELUTLKV-UHFFFAOYSA-N 0.000 description 6

- VLKZOEOYAKHREP-UHFFFAOYSA-N n-Hexane Chemical compound CCCCCC VLKZOEOYAKHREP-UHFFFAOYSA-N 0.000 description 6

- 239000002585 base Substances 0.000 description 5

- 239000000203 mixture Substances 0.000 description 5

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 5

- 239000004065 semiconductor Substances 0.000 description 5

- 239000004480 active ingredient Substances 0.000 description 4

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 4

- 239000001301 oxygen Substances 0.000 description 4

- 229910052760 oxygen Inorganic materials 0.000 description 4

- 229920000642 polymer Polymers 0.000 description 4

- 239000000377 silicon dioxide Substances 0.000 description 4

- 235000012239 silicon dioxide Nutrition 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- RTZKZFJDLAIYFH-UHFFFAOYSA-N ether Substances CCOCC RTZKZFJDLAIYFH-UHFFFAOYSA-N 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- -1 poly (arylene ether Chemical compound 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- NTIZESTWPVYFNL-UHFFFAOYSA-N Methyl isobutyl ketone Chemical compound CC(C)CC(C)=O NTIZESTWPVYFNL-UHFFFAOYSA-N 0.000 description 2

- 125000003118 aryl group Chemical group 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000012776 electronic material Substances 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- 239000003960 organic solvent Substances 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 229920006395 saturated elastomer Polymers 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 239000011800 void material Substances 0.000 description 2

- ARXJGSRGQADJSQ-UHFFFAOYSA-N 1-methoxypropan-2-ol Chemical compound COCC(C)O ARXJGSRGQADJSQ-UHFFFAOYSA-N 0.000 description 1

- 239000004215 Carbon black (E152) Substances 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- 238000005033 Fourier transform infrared spectroscopy Methods 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 150000007513 acids Chemical class 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 239000002318 adhesion promoter Substances 0.000 description 1

- 150000001298 alcohols Chemical class 0.000 description 1

- 239000011260 aqueous acid Substances 0.000 description 1

- 239000003125 aqueous solvent Substances 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 239000012298 atmosphere Substances 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 239000004643 cyanate ester Substances 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000011049 filling Methods 0.000 description 1

- 238000009472 formulation Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 230000002209 hydrophobic effect Effects 0.000 description 1

- 229910001867 inorganic solvent Inorganic materials 0.000 description 1

- 239000003049 inorganic solvent Substances 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 239000008204 material by function Substances 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 229940038032 nitrogen 20 % Drugs 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 229920000412 polyarylene Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 238000011417 postcuring Methods 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02126—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material containing Si, O, and at least one of H, N, C, F, or other non-metal elements, e.g. SiOC, SiOC:H or SiONC

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02282—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process liquid deposition, e.g. spin-coating, sol-gel techniques, spray coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02126—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material containing Si, O, and at least one of H, N, C, F, or other non-metal elements, e.g. SiOC, SiOC:H or SiONC

- H01L21/02134—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material containing Si, O, and at least one of H, N, C, F, or other non-metal elements, e.g. SiOC, SiOC:H or SiONC the material comprising hydrogen silsesquioxane, e.g. HSQ

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02112—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer

- H01L21/02123—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon

- H01L21/02164—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates characterised by the material of the layer the material containing silicon the material being a silicon oxide, e.g. SiO2

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02109—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates

- H01L21/02205—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition

- H01L21/02208—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si

- H01L21/02211—Forming insulating materials on a substrate characterised by the type of layer, e.g. type of material, porous/non-porous, pre-cursors, mixtures or laminates the layer being characterised by the precursor material for deposition the precursor containing a compound comprising Si the compound being a silane, e.g. disilane, methylsilane or chlorosilane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02263—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase

- H01L21/02271—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition

- H01L21/02274—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process deposition from the gas or vapour phase deposition by decomposition or reaction of gaseous or vapour phase compounds, i.e. chemical vapour deposition in the presence of a plasma [PECVD]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/312—Organic layers, e.g. photoresist

- H01L21/3121—Layers comprising organo-silicon compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/314—Inorganic layers

- H01L21/316—Inorganic layers composed of oxides or glassy oxides or oxide based glass

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/314—Inorganic layers

- H01L21/316—Inorganic layers composed of oxides or glassy oxides or oxide based glass

- H01L21/31604—Deposition from a gas or vapour

- H01L21/31608—Deposition of SiO2

- H01L21/31612—Deposition of SiO2 on a silicon body

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Element Separation (AREA)

- Formation Of Insulating Films (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Polyoxymethylene Polymers And Polymers With Carbon-To-Carbon Bonds (AREA)

- Physical Vapour Deposition (AREA)

Abstract

電子素子は、下部および上部を有する溝を備える基板を含む。溝の下部は、硬化したスピンオン化合物で充填され、一方、頂部は、化学気相成長法で堆積した化合物で充填される。化学気相成長法で堆積した化合物は、基板の表面と実質上同一面の表面を有することが好ましい。そのようなデバイスを製造する特に好ましい方法は、基板中に溝が形成され、第1の化合物が溝の中にスピンオン堆積で堆積されるステップを含む。第1の化合物は、基板の表面の下方のレベルまで、溝から部分的に除去され、さらなるステップで、第2の化合物が、第1の化合物の上部表面の上に、化学気相成長法によって堆積される。

Description

【技術分野】

【0001】

本発明の分野は、電子デバイスに関し、詳細には、マイクロエレクトロニクスデバイスに誘電体を堆積することに関する。

【背景技術】

【0002】

集積回路の能動デバイスおよび受動デバイスの誘電体分離は、そのようなデバイスの比較的高い密度を達成するのに必要であり、通常、浅溝分離(STI、Shallow Trench Isolation)構造を組み込むことによって達成される。STIを形成する多くの方法が、当業で知られている。

【0003】

STI構造を形成する一方法では、化学気相成長法(CVD)が用いられ、誘電体材料が堆積される(例えば、Chen等の米国特許第6,146,971号(2000年11月14日)を参照されたい)。典型的なプロセスは、基板上に熱酸化物を成長させ、続いて熱酸化物の上に窒化ケイ素を堆積することを含む。窒化ケイ素は、トレンチを形成するために、続いてパターン形成およびエッチングされる。熱酸化物層は、溝の中で成長し、二酸化ケイ素が、CVDによって堆積される。さらなるステップで、二酸化ケイ素は、逆マスクされ、活性表面から除去される。次いで化学機械研磨(CMP)を使用して表面を平坦化し、さらなるステップで、窒化ケイ素および熱酸化物層が、基板の表面からエッチングされる。

【0004】

CVD堆積の多くの利点にもかかわらず(例えば、CMPプロセスはよく理解されており、例えば、ULSI Technology、Chang and Sze、McGraw−Hill Co.Inc.、New York、NY、1996を参照されたい)、CVD本来の制約は、そのプロセスの有用性を低くしている。例えば、窒化ケイ素および熱酸化物層を活性表面から除去するときに、異なるエッチングによる表面形態の不均質性を避けるため、CVD酸化物および熱酸化物のエッチング速度は、一般に、比較的同様であることが必要であり、そのため、CVD酸化物の選択肢が、制限される。さらに、また特に、溝が比較的高いアスペクト比(深さ/幅)を有する場合、CVDの間に、溝中のボイド(void)の形成が、より頻繁に起きる。

【0005】

少なくともいくつかの問題を回避するために、高密度プラズマ(HDP)・CVDを用いることができる。他の利点の中でも、HDP・CVDは、堆積とエッチングを結びつけ、それによって、ボイドの形成が大きく低減される。しかし、一般に、HDP・CVDは、基板の処理量が少なくなる。さらに、HDP・CVDの使用は、角部の損傷(clipping)の危険性を高め、それによって、生産期間毎の全体歩留りが、さらに低くなる。

【0006】

別法として、スピンオン材料を使用することによって、CVDプロセスを全て回避することが知られている(例えば、Lou等の米国特許第6,171,928号(2001年1月9日)を参照されたい)。スピンオン材料は、CVD材料と比較して、しばしば優れた平坦性特性を示す。さらに、スピンオン材料は、一般に、望ましい間隙充填能力を有している。したがって、STI構造を形成する代替の方法は、基板上への熱酸化物の成長(パッド酸化物とも呼ばれる)、および熱酸化物上への窒化ケイ素の堆積を含む。窒化ケイ素は、続いてパターン形成およびエッチングされて、溝が形成される。熱酸化物層は、溝の中に成長し(下地酸化物とも呼ばれる)、スピンオン化合物が、基板上にスピン塗布され、引き続いて硬化される。続くCMPステップで、ウェーハは、平坦化され、窒化ケイ素/熱酸化物は、活性表面からエッチング除去される。

【0007】

スピンオン材料を使用する比較的単純なプロセスにもかかわらず、特に硬化ステップ間の溝内部のスピンオン材料の収縮を含めて、いくつかの欠点が残る。溝の中の低密度の硬化したスピンオン材料は、熱酸化物よりもはるかに高い(約3〜10倍)ウェットレート(wet rate)を有し、したがって、もはや硬化後のエッチングステップに、適合性がない(例えば、活性表面からの窒化ケイ素/熱酸化物のエッチング除去)。

【0008】

このように、電子デバイスを製造する多くの方法が従来技術に知られているが、それらの全てまたは大部分には、1つまたはそれ以上の欠点がある。したがって、やはり電子デバイスの改善された方法および装置を提供する必要がある。

【発明の開示】

【課題を解決するための手段】

【0009】

(発明の概要)

本発明は、下部および頂部を有する溝を備える基板を含む電子デバイスの構成および製造を目的とする。溝の下部は、スピンオン化合物で充填され、頂部は、CVD材料で充填される。CVD材料は、基板の表面と実質上と同一面の表面を有することが好ましい。

【0010】

本発明の主題の一態様において、溝は、熱酸化物被覆(下地)をさらに含み、特に企図されている溝は、5以上、より好ましくは8以上のアスペクト比(深さ/幅)を有する。好ましい溝の下部は、溝の高さの60%まで、より好ましくは80%まで延伸する。溝が浅溝分離構造(STI)の要素であることがさらに考えられている。

【0011】

本発明の主題の他の態様において、スピンオン化合物は、ケイ素を含み、好ましくはメチルシルセスキオキサン、ハイドロジェンシルセスキオキサン、メチルヒドリドシルセスキオキサン、シリケート、またはペルヒドロシラザンから形成される。好ましい化学気相成長法(CVD)化合物は、ケイ素を含み、特に好ましいCVD化合物は、シランまたはテトラエチルオルトシリケートから形成される。

【0012】

本発明の主題のさらなる態様において、それらの装置を製造する特に好ましい方法は、溝が基板の中に形成されるステップと、第1の化合物がスピンオン堆積によって堆積されるステップとを含む。第1の化合物は、基板の表面以下のレベルまで、溝から部分的に除去され、さらに次のステップで、第2の化合物が、化学気相成長によって、第1の化合物の上部面に堆積される。

【0013】

本発明の主題のさらに企図されている態様において、第1の化合物が、スピン洗浄プロセス、湿式エッチングプロセス、またはドライエッチングプロセスによって、部分的に除去される。企図されている第1の化合物は、メチルシルセスキオキサン、ハイドロジェンシルセスキオキサン、メチルヒドリドシルセスキオキサン、シリケート、およびペルヒドロシラザンを含み、企図されている第2の化合物は、テトラエチルオルトシリケートおよびシランを含む。

【0014】

本発明の種々の目的、特徴、態様および利点は、付随する図面と共に、以下の本発明の好ましい実施形態の詳細な説明から、より明らかになろう。

【発明を実施するための最良の形態】

【0015】

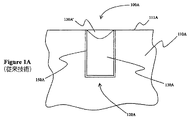

CVD化合物またはスピンオン化合物のみで充填されたSTI構造が、多くの欠点(上記)を示すことは当技術分野で知られている。比較的通常の欠点は、従来技術の図1Aに描かれており、そこでは、電子デバイス100Aが、表面111Aおよび溝120Aを備える基板110Aを有する。溝120Aは、熱酸化物被覆(下地)150Aをさらに有し、溝は、硬化したスピンオン化合物で充填されている。硬化中の寸法的な拘束のため、硬化スピンオン誘電体材料の下部(表面に対して)130Aは、硬化スピンオン誘電体材料の上部(表面に対して)130A’よりも密度が低く、その結果、一般に、後続のステップにおけるエッチング挙動が、異なってくる。

【0016】

発明者らは、スピンオン材料およびCVD材料の両方を用いて、誘電体材料を電子デバイスに堆積することができ、また、その堆積構造が周知の構造よりも多くの利点を示すことを見い出した。図1Bにおいて、電子デバイス100Bは、表面111Bおよび溝120Bを備える基板110Bを含む。溝120Bはさらに、熱酸化物被覆(下地)150Bで被覆されている。溝121Bの下部は、硬化スピンオン化合物130Bで充填され、一方、溝122Bの頂部は、CVD堆積化合物140Bで充填されている。CVD堆積化合物140Bは、表面141Bを有し、基板111Bの表面と同一面である。

【0017】

本発明の主題の特に好ましい態様において、電子デバイス100Bは、集積回路であり、基板110Bは、実質上平坦な表面111Bを備えるシリコンウェーハである。溝120Bは、基板の中にエッチングされ、さらに熱酸化物被覆150Bで被覆される。溝121Bの下部は、溝の底から上方へ、溝高さの60%の高さまで延伸し、基板110B上にスピン塗布された硬化ハイドロジェンシルセスキオキサン130Bで、充填される。溝122Bの上部(溝高さの残りの40%に相当する)は、CVD堆積シラン140Bから形成された二酸化ケイ素で、充填される。CVD堆積二酸化ケイ素140Bは、表面141Bを有し、実質上シリコン基板111Bの表面と同一面(すなわち最大縦段差20nmを有する)である。

【0018】

基板に関しては、シリコンウェーハおよび他のシリコン系半導体基板が、特に好ましいが、シリコンウェーハ以外の多くの基板を、使用でき、代替の基板には、非シリコン半導体材料(例えば、ゲルマニウム系またはガリウム系)および無機/有機誘電体材料(例えば、ポリシリケート、ポリ(アリーレンエーテル)など)が含まれることを理解されたい。

【0019】

基板110Bの実質上平坦な表面111Bは、シリコンウェーハの表面であることが企図されている。本明細書に使用される用語「表面(surface)」は、機能要素(例えば、伝導性配線またはビア)がその上に形成される基板の任意の領域を指す。さらに本明細書に使用される用語「実質上平坦な表面(substantially planar surface)」は、表面が平坦化プロセス(例えば化学的機械的平坦化(CMP))を受けて、不均一性が表面の最高点と最低点の間で約5nm〜20nm以下であることを意味する。本発明の主題の代替の態様では、表面は、機能性および非機能性材料を含めて、代替の材料をさらに含むことができる。例えば、機能性材料は、誘電体材料、熱酸化物、金属を含むことができ、一方、非機能性材料は、エッチング停止層(例えば、窒化ケイ素)または他のマスキング材料を含むことができる。

【0020】

また、適切な溝は、基板中にエッチングされ、一般に、約50nm〜500nmの幅、約400nm〜700nmの深さを有することが考えられる。しかし、約500nm〜5000nmまたはそれ以上のより大きな幅も、考えられる。同様に、企図されている溝は、特定の深さに制限される必要はなく、適切な溝は、約200nm〜2000nmまたはそれ以上の深さであることが考えられる。企図されている溝のアスペクト比(幅に対する深さ)は、特定の数値または範囲に制限されることはないが、好ましいアスペクト比は、5以上(例えば、5〜10)、より好ましくは8以上、最も好ましくは10以上(例えば、10〜15)であることが特に考えられる。同様に、企図されている溝のレイアウト(すなわち導路)は、大きく変化でき、企図されているレイアウトは、線状、円形状、曲線状、およびその妥当な組み合わせを含むことができることを理解されたい。適切な溝は、基板中にエッチングするのが一般に考えられるが、溝形成のやり方は、本発明の主題を制限するものではないことを理解されたい。従って、代替の方法で形成された溝も、考えられ、その方法は、アディティブ(すなわち、表面に壁を付加することによる溝形成)法およびサブトラクティブ(すなわち、表面から材料を除去することによる溝形成)法を含む。

【0021】

適切であれば、企図されている溝は、溝の床および/または側壁の少なくとも一部に結合した追加の層または被覆を、さらに含むことができる。例えば、考えられる追加の層または被覆は、熱酸化物被覆、1種またはそれ以上の有機および/または無機誘電体、金属、ポリシリコンなどを含むことができる。当分野に周知の、基板中に溝を形成する多くの方法があり、周知の方法の全ては、本明細書に示す教示と共に使用することが適切であると考えられる。

【0022】

スピンオン化合物に関しては、全ての周知のスピンオン誘電体は本発明に使用するのに適していると考えられ、誘電体を生成するのにさらに硬化ステップを必要とする、または必要としない無機および有機スピンオン化合物を含む。例えば、適切な有機スピンオン誘電体は、共役および非共役芳香族ポリマー(例えば、ポリイミド、ポリアリーレンなど)、および非芳香族ポリマー(例えば、エポキシ架橋、シアン酸エステル樹脂など)を含む。適切な無機スピンオン誘電体は、ケイ素を含む種々の化合物を含み、特に考えられる無機スピンオン化合物は、メチルシルセスキオキサン、ハイドロジェンシルセスキオキサン、メチルヒドリドシルセスキオキサン、シリケート、およびペルヒドロシラザンである。有用な有機ヒドリドシロキサンは、通例に譲渡された米国特許第6,143,855号および第6,043,330号に開示されており、本明細書に参照して組み込まれている。特に有用な1種の有機ヒドリドシロキサンは、Honeywell International Inc.から、HOSP(商標)スピンオン誘電体として、市場で入手可能である。特定の用途の特定のスピンオンおよび硬化の条件は、一般に、スピンオン化合物、溝深さ、必要な硬化程度に依存し、通常の技術者であれば、多くの実験を行うことなく容易に決定することができる。

【0023】

溝の下部をスピンオン化合物で充填することは一般に考えられる。本明細書で使用される用語「下部(lower portion)」は、溝の床(すなわち、基板の表面に関して溝の最下部)から基板の表面よりも下方にある任意の溝高さまで延伸する、溝の容積を指す。したがって、溝の下部は、溝の床から溝の深さの10%まで(すなわち、溝の床と基板表面間の最大縦距離)、好ましくは溝の深さの40%まで、より好ましくは60%まで、さらにより好ましくは80%まで、最も好ましくは80%〜95%まで延伸できることが考えられる。スピンオン化合物を使用して溝の中に誘電体を形成することは、溝が比較的高いアスペクト比(すなわち5より大きい)を有するときに、特に有用であることを理解されたい。なぜならば、アスペクト比の増大によって、典型的なCVDプロセスの間に、ボイドがしばしば形成されるからである。

【0024】

CVD堆積化合物が、熱酸化物に類似したエッチング抵抗性(すなわち、熱酸化物のエッチング速度の1〜3倍、好ましくは1〜2倍、より好ましくは1〜1.5倍のエッチング速度)を有することが好ましく、よく理解されたCMP条件を有するとさらに考えられる。例えば、適切なCVD堆積化合物は、ケイ素を含み、特に好ましいCVD堆積化合物は、シランまたはテトラエチルオルトシリケート(TEOS)から形成される。しかし、代替の態様では、ケイ素含有化合物以外の周知のCVD化合物も、本発明で使用するのに適していると考えられる。CVD化合物の堆積に関しては、特定の条件は、大きく変化することができ(すなわち、HDP・CVD、低圧(LP)・CVD、大気圧(AP)・CVD、プラズマ強化(PE)・CVD)、使用される特定の材料に依存することを認識されたい。溝の上部は、CVD堆積化合物で充填されることがさらに考えられている。本明細書で使用される用語である、溝の「上部(upper portion)」は、基板の表面と溝の下部との間の溝の容積を指す。1層またはそれ以上の追加の層を、硬化スピンオン化合物とCVD化合物との間に配設することができ、考えられる追加の層が、機能性(例えば、誘電体、伝導性、半導体性)および非機能性(例えば、接着促進剤)の層を含むことをさらに認識されたい。本発明の主題には重要ではないが、CVD化合物の上部表面は、基板表面と実質上同一面である(すなわち、50nmの最大縦段差)ことが特に好ましい。当分野で知られている多くの平坦化法があり、周知の方法の全てが、本発明に使用するのに適していると考えられる。特に好ましい方法は、CMPである。

【0025】

したがって、本発明の主題による電子デバイスの形成方法は、表面を有する基板中に溝が形成され、第1の化合物がスピンオン堆積を用いて溝の中に堆積される1つのステップを含む。さらなるステップにおいて、溝中の化合物の上部表面が、基板の表面よりも低くなるように、第1の化合物が、部分的に溝から除去される。さらに他のステップにおいて、第2の化合物が、表面および第1の化合物の上部表面上にCVDによって堆積される。基板、基板の表面、溝、スピンオン化合物(すなわち、第1の化合物)、CVD堆積化合物(すなわち、第2の化合物)に関しては、上で論じた同じ考えが適用される。

【0026】

スピンオン化合物を溝から部分的に除去する方法(例えば、湿式エッチングまたはドライエッチング)の全ては、適切であると考えられるが、スピン洗浄プロセス(以下)によって、部分除去を行うのが特に好ましい。企図されているスピン洗浄プロセスは、溶媒混合物を、部分的または完全に硬化したスピンオン膜(例えば、溝中のスピンオン化合物)上に、回転供給するステップを含む。溶媒混合物は、一般に、少なくとも1種の溶媒(すなわち、スピンオン膜を破壊および/または溶解する組成物、活性成分とも呼ばれる)と、少なくとも1種の非溶媒(すなわち、スピンオン膜に不活性であるか、またはスピンオン膜を溶媒より少なくとも10倍遅い速度で破壊および/または溶解する組成物)とを含む。溶媒および非溶媒の混和性は、重要ではないが、溶媒混合物が、非溶媒と混和性のある溶媒を含むことが好ましい。特定の溶媒の選択は、一般に、スピンオン膜の組成物および必要な除去速度に依存するであろう。しかし、全ての周知の溶媒は、本発明で使用するのに適していると一般に考えられ、考えられる溶媒は、水性および非水性溶媒、酸および塩基を含み、その全ては、例えば極性、疎水性、混和性などを含む種々の基準によって、選択することができる。

【0027】

したがって、スピンオン化合物を除去する方法は、スピンオン化合物を基板の表面上に堆積するステップを含む。さらなるステップで、スピンオン化合物は、溶媒混合物でスピン洗浄され、溶媒混合物は、第1のスピンオン化合物を溶解する第1の溶媒と、スピンオン化合物に不活性な第2の溶媒とを含む。特に考えられるスピンオン化合物は、ケイ素を含み、一方、第1の溶媒は、酢酸プロピルを含み、第2の溶媒は、乳酸エチルを含む。しかし、種々の代替溶媒も、考えられる。例えば、第1の溶媒は、ケトン(例えば、MIBK)、エステル(例えば、酢酸プロピル)、エーテル(例えば、PGMEA)、炭化水素(例えば、ヘキサン)であることができ、第2の溶媒は、水、アルコール(例えば、エタノール、メタノール)、アセトニトリル、アミン、またはアミドであることができる。適切な基板を、第1の温度に加熱して、溶媒混合物を除去し、次いで、第2の温度に加熱して、スピンオン化合物を硬化することがさらに考えられている。

【0028】

考えられているスピン洗浄プロセスにおいて、スピンオン膜の除去速度および平坦化の程度(DOP、degree of planarization)は、例えば溶媒の選択および比、スピン条件、温度、分注プロファイルおよび容量などを含む、種々のパラメーターによって、有利に制御することができることを特に理解されたい。例えば、溶媒混合物中の非溶媒に対する溶媒の比を、高くすることによって、一般に、より高い除去速度が得られる。DOPは、一般に、狭いフィーチャー内部のマイクロローディングを用いて制御することができる。活性成分が、新鮮な溶媒で置き換わるよりも速く、除去した材料で飽和されるときに、マイクロローディングは、狭く密集したフィーチャー(溝)の内部に起きる。マイクロローディング効果は、溝またはフィーチャーの内部の流体力学によって起こり、新鮮な溶媒の供給が、制限される。非溶媒に対する溶媒の比が、低い(すなわち、活性成分の濃度が低い)と、活性成分が、より急速に飽和されるので、効果が、大きくなる。マイクロローディングは、平坦な領域に比べて、狭いフィーチャーおよび密集したパターン領域の、除去速度比を効果的に小さくする。マイクロローディングによるDOPの改善は、静的用途の代わりに動的溶媒用途(すなわち、スピン洗浄)を使用することによって最善に用いられる。なぜならば、平坦な表面には、新鮮な溶媒が、常に供給され、他方、狭いフィーチャーの内部への溶媒供給は、妨げられ、したがって、減少するからである。最適スピン条件は、パターン設計およびフィーチャー密度に依存する。スピン洗浄プロセスは、STI構造の形成におけるスピンオン膜の部分除去以外の用途にも用いることができ、企図されているプロセスは、スピンオン膜または化合物を少なくとも部分的に除去する必要のある全てのプロセスを含むことも認識すべきである。例えば、考えられる代替のプロセスは、一般に部分的なエッチバック(例えば、IMD用途において、金属配線を備えるパターン形成されたウェーハ上の誘電体材料の除去)を必要とするプロセスを含む。

【0029】

また、スピン洗浄プロセスは、通常用いられているドライエッチングを用いるSOGエッチバックプロセスのコスト効果のある修正であり得ることもさらに考えられている。SOGエッチバックプロセスは、しばしば比較的高価である。なぜならば、以下のようないくつかのプロセスステップが、一般に、必要とされるからである。1)金属配線の形成、2)PECVD装置:CVDを用いる下地酸化物の堆積(このステップは省略することができる)、3)スピンコータ:間隙を充填し局部的な平坦化を改善するスピン、SOGの焼成および硬化、4)プラズマエッチャ:金属配線の頂部にSOGが少ないまたは残らないようにするSOGのエッチバック(これは「ビアの汚染(poisoned vias)」を避ける)、5)PECVD装置:酸化物キャップの堆積、6)CMP装置:酸化物キャップのCMP(このステップはSOGプロセスの能力および製造プロセスの平坦化要求度によって省略することができる)。したがって、企図されているプロセスは、時間のかかるエッチングステップ(5)を省略することができ、また、一般により良好な局部の平坦化を生じさせ、さらにCMPの必要性がなくなることを特に認識すべきである。したがって、企図されているプロセスは、スピンプロセス(4)を、4a)スピンコーティング、4b)任意選択的な部分焼成、4c)スピン洗浄を用いる部分除去および膜の平坦化、4d)焼成プロセス、4e)硬化プロセスに、修正することを理解されたい。スピン洗浄プロセスは、従来のスピンカップ(spin cup)を用いて市場で入手可能なスピン工程(spin tracks)に一体化することができ、したがって、新しいプロセス装置を必要としない。また、スピン洗浄プロセスは、上記のように平坦化を改善するので、後続のCMPプロセス(6)を、省略することができる。

【0030】

本発明の主題のさらに企図されている態様では、電子デバイスを形成する方法は、基板の表面とCVD堆積化合物の上部表面と間の同一面性を達成するために、平坦化ステップを追加して含むことができる。企図されている平坦化ステップは、一般に全ての知られている平坦化プロセスを含むが、平坦化は、CMPで行うことが特に好ましい。

(実施例)

(スピン洗浄プロセス)

この実施例に記載されている例示的スピン洗浄プロセスは、従来のエッチバック間隙充填(etch−back gap fill)プロセスの代替として、用いることができる。

【0031】

半導体デバイス構造を、標準的な製造技術を使用して、製造する。金属配線構造(2)を、半導体基板(1)の上に、構造1のように形成する。0.18ミクロン以下のデバイス寸法の相互配線金属は、通常、少量のドーパントを有するアルミニウムである。しかし、金属の選択は、本発明の主題を制限するものではなく、銅を含む他の金属も使用できることが考えられる。しかし、サブトラクティブプロセスには、アルミニウムが好ましい。

【0032】

【表1】

【0033】

第1レベルの金属線(2)の堆積の後に、任意選択的な酸化物下地(3)を、堆積する(構造2)。酸化物下地の厚さは、1〜200nmであり、50nmが、典型的な値である。酸化物下地は、PECVD TEOSを用いて堆積するのが好ましいが、PECVDシランなどの他の酸化物も、使用することができる。プロセスステップの数を削減するために、酸化物下地を使用しないことが、好ましい。

【0034】

【表2】

【0035】

次いでスピンオン材料(4、構造3を参照)を、配線間誘電体として堆積する。スピンオン誘電体の好ましい厚さは、スピンオン誘電体、金属の厚さ、および必要な平坦化の程度に依存する。例えば、HOSP(商標)(スピンオン誘電体は市場でHoneywell Electronic Materialsから入手可能である)の場合、幅500nmの最小間隙で、高さ800nmのアルミニウム線に関して、スピンオン材料の厚さは、一般に、被覆膜上で、200〜900nmであり、600nmが好ましい。

【0036】

この例では、HOSP(商標)誘電体材料は、標準的なスピンプロセスを用いて堆積するが、特定のスピンプロセスは、スピン洗浄プロセスの用途に大きな影響は与えない。しかし、スピン洗浄を使用するために、標準の焼成手順(標準は150℃、200℃、350℃で各1分である)は、スピン洗浄プロセスの前に用いる最高温度が300℃以下になるように、修正される。なぜならば、320℃以上の温度で焼成すると、HOSP(商標)誘電体材料は、有機溶媒に溶解できないからである。無論、最高温度は、他の材料では異なる。次いで、HOSP膜を、単一の熱板に対して、100℃〜200℃の温度で1分間露出するが、好ましい温度は、150℃である。焼成プロセスによって、材料は、溶融し再流動することができるので、平坦性が向上する。

【0037】

【表3】

【0038】

次いで、溶媒混合物を、スピン洗浄プロセスに分注して、金属線の頂部のスピンオン材料を除去し(構造4を参照されたい)、平坦性を改善する。スピン洗浄溶液は、スピンオン膜以外、基板上のいかなる材料も、除去しない。スピン洗浄プロセスは、通常のスピンコータで行うことができるが、スピンエッチャを使用することもできる。分注の間のスピン速度は、材料、溶媒、ウェーハサイズ、装置の幾何形状に依存し、20rpm〜6000rpmの範囲にすることができる。多くの用途で、1000rpmが、洗浄プロセス中の推奨スピン速度であり、この例で用いている。溶媒の分注速度は、材料、溶媒、ウェーハサイズ、装置の幾何形状に依存し、0.1mL/秒〜50mL/秒の範囲にすることができる。多くの用途で、2mL/秒が、洗浄プロセス中の推奨分注速度であり、この例で用いている。HOSPの溶媒のリストには、ケトン(例えばMIBK)、エステル(例えば酢酸プロピル(PACE)、グリコールエーテルPMアセテート(PGMEA))、炭化水素(例えばヘキサン)が含まれるが、制限されない。非溶媒には、水、アルコール(例えばメタノール、エタノール、イソプロピルアルコール(IPA)、乳酸エチル(EL))、アセトニトリル、アミン、アミドが含まれるが、制限されない。1種以上の溶媒と1種以上の非溶媒とのいくつかの組み合わせが可能であり、好ましい組み合わせは、材料、プロセス手順、および用途で必要な除去速度に、大きく依存する。この例では、2:1の乳酸エチルとPACEの混合物を、スピン洗浄プロセス用の推奨溶媒混合物として使用し、スピン洗浄プロセスを十分な時間実施した。スピン洗浄プロセスの間に、スピンオン誘電体は、狭い間隙の内部からよりも、金属線の頂部から、より速く除去され(先に説明したマイクロローディング)、それによって、ドライエッチバックプロセスまたは静的湿式エッチングに比べて、平坦性が向上する。下地酸化物は、スピン洗浄プロセスの影響を受けず、これは、下地酸化物も攻撃する従来のドライエッチングプロセスに比べて、有益である。スピン洗浄プロセスの終わりに、ウェーハを分注なしで、3000rpmの回転速度で30秒間回転して、膜を乾燥する。次いで、膜を、熱板の上で、350℃の温度で1分間焼成する。次いで、膜は、酸素レベル20ppm未満の窒素雰囲気中で、400℃の温度で1時間水平炉中で硬化する。スピン洗浄プロセスの終わりに、スピンオン材料(HOSP)は、金属線の頂部から除去され、一方、狭い間隙の間には、スピンオン材料が残る。

【0039】

【表4】

【0040】

次いで、CVD酸化物を、ビア(via)レベル用に堆積する(構造5を参照されたい)。CVD酸化物の厚さは、デバイス構造に依存し、500nm〜3000nmが、典型的である。一般に、PECVD TEOSが、このプロセスに使用される。

【0041】

【表5】

【0042】

次いで、任意選択的に、構造を、化学機械研磨(CMP、chemical mechanical polishing)プロセスにかける。CMPプロセスは、酸化物層の部分を除去し、平坦性を改善する(構造6)。

【0043】

【表6】

【0044】

(スピンエッチングプロセス)

スピンエッチングプロセスは、上記のスピン洗浄プロセスにある程度類似しているが、エッチング剤として無機溶媒を使用する。この例で用いたスピンオン材料は、市場でHoneywellから入手可能なAccuglass(登録商標)512Bである。処方および回転速度は、被覆膜上に500nmの厚さの膜を得るように選択する。Accuglass(登録商標) 512Bは、標準的なスピンプロセスおよび焼成プロセスを用いて堆積し、80℃、150℃、250℃で各1分間の焼成が、用いられる。次いで、ウェーハを、酸素レベル20ppm未満の窒素雰囲気中で、400℃の温度で1時間、水平炉中で硬化する(構造はこの時点で構造3に示したように見える)。

【0045】

別法の硬化プロセスは、400℃炉の硬化の代りに、酸素プラズマアッシング(10%窒素)を用いる。このプロセスは、厚さ500nmまでのAccuglass(登録商標) 512B被覆膜に使用できる。

【0046】

次いで、ウェーハを、スピンエッチング装置で処理する。好ましいエッチング剤は、エッチングすべき材料に依存する。Accuglass(登録商標)512Bスピンオン材料を用いるこの例では、10:1から500:1までのBOE(緩衝酸化物エッチング、buffer oxide etch)を使用することができ、50:1が好ましい。エッチングプロセス中の好ましい回転速度は、1000rpmに設定し、BOE流量は、0.8lpm(毎分リットル)に設定する。処理時間は、15秒に設定する。被覆エッチング速度は、140A/秒(毎秒オングストローム)であり、これは、下地材料として使用するTEOS酸化物のエッチング速度の約40倍である。スピンエッチングプロセスの終わりに、ウェーハを、DI(脱イオン)水を用いて15秒間洗浄し、次いで、回転速度3000rpmで30秒間回転して、膜を乾燥する。スピン洗浄プロセスは、金属線の頂部の材料を優先的に除去し、全体の平坦性を向上させる。スピンエッチングプロセスを用いる例では、金属線の頂部の512B材料は、完全に除去される。スピンオン材料Accuglass(登録商標)512Bに対するBOEの高い選択性によって、TEOS下地へのエッチングは、5nm未満であり、したがって無視できる。後続のステップは、上記のステップと同一である。

【0047】

(スピン洗浄プロセスおよび酸化物キャップを用いるSTIプロセス)

図1Bは、本発明の好ましい態様によるSTI構造を概略的に示す断面図である。プロセスは、熱酸化を用いてシリコン基板(構造7の(1))上に、パッド酸化物層(ステップ1)(構造7の(2))を形成することから開始する(構造7)。パッド酸化物の厚さは、2〜30nmが典型的であり、10nmが好ましい厚さである。

【0048】

【表7】

【0049】

次のプロセスステップ(ステップ2)は、パッド酸化物の頂部に、窒化ケイ素層(構造8の(3))を、堆積することである(構造8)。窒化物層の厚さは、50〜200nmが典型的であり、100nmが好ましい。

【0050】

【表8】

【0051】

次のステップ(ステップ3)は、半導体基板上に、フォトレジスト層を堆積することである。基板上にパターンを転写するために、フォトリソグラフィ(ステップ4)プロセスを実施する。次いで、異方性エッチング(ステップ5)を実施して、最初に、窒化ケイ素を開口し(構造9)、次いで、溝構造を形成する(構造10の(4))。

【0052】

【表9】

【0053】

【表10】

【0054】

次いで、熱酸化(ステップ6)を用いて、溝の側壁および底に、酸化物を成長する。溝の側壁の厚さは、5〜15nmが典型的であり、10nmが好ましい厚さである(構造11)。

【0055】

【表11】

【0056】

次いで、スピンオン材料を、溝の内部に堆積する(ステップ7)(構造12の(6))。スピンオン誘電体の好ましい厚さは、スピンオン誘電体の種類、溝の幅および高さ、ならびにアスペクト比の分布に、依存する。1ミクロン未満の溝深さのSTI構造では、HOSP(商標)スピンオン誘電体(市場でHoneywell Electronic Materialsから入手可能)は、適切な材料である。一般に、溝深さの60%〜80%の膜厚さで十分である。溝深さが600nmでは、被覆膜厚さは、400nmが好ましい。この例では、HOSP(商標)スピンオン誘電体は、標準的なスピンプロセスを用いて堆積するが、特定のスピンプロセスは、スピン洗浄プロセスの適用に大きな影響は与えない。しかし、HOSPは320℃以上の温度で焼成すると有機溶媒に溶解できないので、スピン洗浄を使用するために、スピン洗浄プロセスの前に用いる最高温度が300℃以下になるように、標準の焼成手順(標準は150℃、200℃、350℃で各1分である)を修正する。無論、最高温度は、他の材料では異なる。次いで、HOSP膜を、単一の熱板で、100℃〜200℃の温度で1分間露出するが、好ましい温度は、150℃である。焼成プロセスによって、材料は溶融し再流動することができるので、平坦性が向上する。

【0057】

【表12】

【0058】

次いで、スピン洗浄プロセスを用いてHOSP(商標)膜を、部分的に除去する(ステップ8)。溶媒混合物を、スピン洗浄プロセスに分注し、これは、窒素化物層の頂部から全てのHOSPポリマーを除去する(構造13)(上記のスピン洗浄プロセスで説明した同じ手順を用いる)。スピン洗浄時間は、HOSP膜の頂部表面が最も狭い溝より下で基板表面の20〜200nmとなるように、調節する。HOSP表面は、より広い溝では、より低い。

【0059】

【表13】

【0060】

次いで、膜を、熱板上で、350℃の温度で1分間焼成する(ステップ9)。次いで、膜を、酸素:窒素が20%:80%の雰囲気中、水平炉中で700℃で1時間硬化する(ステップ10)。硬化プロセス中に、HOSP膜の有機成分は、酸化して除去され、これはFTIR分光計を用いて実証することができる。次いで、CVD酸化物を、堆積する(ステップ11)(構造14の(5))。スピンオン・ポリマーを用いることによる向上した平坦性、およびスピン洗浄プロセスによる平坦化の恩恵で(標準的なCVDだけのプロセスと比べて)、必要なCVD酸化物の厚さは、より薄くて済む。酸化物CMPプロセスの後に必要な平坦性を達成するのに、一般に、溝深さの20〜90%の酸化物の厚さで、十分である(ステップ12)(構造15)。

【0061】

【表14】

【0062】

【表15】

【0063】

後続のステップにおいて、残りの酸化物および窒化物の層を、エッチングする(ステップ13)(構造16)。

【0064】

【表16】

【0065】

他の利点の中でも、企図されているプロセスを用いることによって、(1)比較的高価なHDP・CVDプロセスを省くことができ、(2)スピン洗浄プロセスの使用によって平坦性を大きく向上することができ、(3)酸化物の厚さを低減でき、それによってP、ECVDのコストおよびCMPに必要な時間を低減できることを認識すべきである。

【0066】

(スピンエッチングプロセスおよび酸化物キャップを用いるSTIプロセス)

この例のステップ1から6は、上記の例と同じである。ステップ7は、HOSP膜が全て標準的な焼成プロセス(150℃、200℃、350℃で各1分)によって処理されることを除き、例3とほとんど同じである。次いで、ウェーハを硬化する(前の例のステップ10)。硬化プロセスの後、スピンエッチングプロセスを用いる。スピンエッチングプロセスは、例2で説明した同じプロセスを用い、酸化物の堆積(ステップ11)、CMP(ステップ12)、エッチング(ステップ13)が続く。

【0067】

したがって、浅溝分離構造を形成する方法は、表面を有する基板に、溝を形成し、第1の化合物を、スピンオン堆積を用いて溝の中に堆積する1つのステップを含むことが考えられる。他のステップにおいて、化合物の上部表面が、基板の表面の下方になるように、第1の化合物を、少なくとも部分的に溝から除去し、さらなるステップにおいて、第2の化合物を、基板表面上および第1の化合物の上部表面に、化学気相成長法で堆積する。企図されている方法の例示的なフロー図は、図2に示されている。

【0068】

このように、電子デバイスおよびその形成の具体的な実施形態および用途を説明した。しかし、当業者であれば、本明細書の発明の概念から逸脱することなく、既に説明したもの以外に多くの修正が可能であることは明らかなはずである。したがって、本発明の主題は、付随する請求項の精神以外で制限されるものではない。さらに、明細書および請求項の解釈において、全ての用語は文脈に一致するように最も広い意味に解釈すべきである。特に、用語「備える」および「含む」は、要素、成分、またはステップを非制限的に指すものと解釈すべきであり、参照される要素、成分、またはステップが、存在し、または用いられ、または、明示的に参照されていない他の要素、成分、あるいはステップと組み合わせることができることを示唆するものである。

【図面の簡単な説明】

【0069】

【図1−A】従来技術の電子デバイスの縦断面概略図である。

【図1−B】本発明の主題による電子デバイスの縦断面概略図である。

【図2】本発明の主題による電子デバイスを製造する例示的方法のフロー図である。

【0001】

本発明の分野は、電子デバイスに関し、詳細には、マイクロエレクトロニクスデバイスに誘電体を堆積することに関する。

【背景技術】

【0002】

集積回路の能動デバイスおよび受動デバイスの誘電体分離は、そのようなデバイスの比較的高い密度を達成するのに必要であり、通常、浅溝分離(STI、Shallow Trench Isolation)構造を組み込むことによって達成される。STIを形成する多くの方法が、当業で知られている。

【0003】

STI構造を形成する一方法では、化学気相成長法(CVD)が用いられ、誘電体材料が堆積される(例えば、Chen等の米国特許第6,146,971号(2000年11月14日)を参照されたい)。典型的なプロセスは、基板上に熱酸化物を成長させ、続いて熱酸化物の上に窒化ケイ素を堆積することを含む。窒化ケイ素は、トレンチを形成するために、続いてパターン形成およびエッチングされる。熱酸化物層は、溝の中で成長し、二酸化ケイ素が、CVDによって堆積される。さらなるステップで、二酸化ケイ素は、逆マスクされ、活性表面から除去される。次いで化学機械研磨(CMP)を使用して表面を平坦化し、さらなるステップで、窒化ケイ素および熱酸化物層が、基板の表面からエッチングされる。

【0004】

CVD堆積の多くの利点にもかかわらず(例えば、CMPプロセスはよく理解されており、例えば、ULSI Technology、Chang and Sze、McGraw−Hill Co.Inc.、New York、NY、1996を参照されたい)、CVD本来の制約は、そのプロセスの有用性を低くしている。例えば、窒化ケイ素および熱酸化物層を活性表面から除去するときに、異なるエッチングによる表面形態の不均質性を避けるため、CVD酸化物および熱酸化物のエッチング速度は、一般に、比較的同様であることが必要であり、そのため、CVD酸化物の選択肢が、制限される。さらに、また特に、溝が比較的高いアスペクト比(深さ/幅)を有する場合、CVDの間に、溝中のボイド(void)の形成が、より頻繁に起きる。

【0005】

少なくともいくつかの問題を回避するために、高密度プラズマ(HDP)・CVDを用いることができる。他の利点の中でも、HDP・CVDは、堆積とエッチングを結びつけ、それによって、ボイドの形成が大きく低減される。しかし、一般に、HDP・CVDは、基板の処理量が少なくなる。さらに、HDP・CVDの使用は、角部の損傷(clipping)の危険性を高め、それによって、生産期間毎の全体歩留りが、さらに低くなる。

【0006】

別法として、スピンオン材料を使用することによって、CVDプロセスを全て回避することが知られている(例えば、Lou等の米国特許第6,171,928号(2001年1月9日)を参照されたい)。スピンオン材料は、CVD材料と比較して、しばしば優れた平坦性特性を示す。さらに、スピンオン材料は、一般に、望ましい間隙充填能力を有している。したがって、STI構造を形成する代替の方法は、基板上への熱酸化物の成長(パッド酸化物とも呼ばれる)、および熱酸化物上への窒化ケイ素の堆積を含む。窒化ケイ素は、続いてパターン形成およびエッチングされて、溝が形成される。熱酸化物層は、溝の中に成長し(下地酸化物とも呼ばれる)、スピンオン化合物が、基板上にスピン塗布され、引き続いて硬化される。続くCMPステップで、ウェーハは、平坦化され、窒化ケイ素/熱酸化物は、活性表面からエッチング除去される。

【0007】

スピンオン材料を使用する比較的単純なプロセスにもかかわらず、特に硬化ステップ間の溝内部のスピンオン材料の収縮を含めて、いくつかの欠点が残る。溝の中の低密度の硬化したスピンオン材料は、熱酸化物よりもはるかに高い(約3〜10倍)ウェットレート(wet rate)を有し、したがって、もはや硬化後のエッチングステップに、適合性がない(例えば、活性表面からの窒化ケイ素/熱酸化物のエッチング除去)。

【0008】

このように、電子デバイスを製造する多くの方法が従来技術に知られているが、それらの全てまたは大部分には、1つまたはそれ以上の欠点がある。したがって、やはり電子デバイスの改善された方法および装置を提供する必要がある。

【発明の開示】

【課題を解決するための手段】

【0009】

(発明の概要)

本発明は、下部および頂部を有する溝を備える基板を含む電子デバイスの構成および製造を目的とする。溝の下部は、スピンオン化合物で充填され、頂部は、CVD材料で充填される。CVD材料は、基板の表面と実質上と同一面の表面を有することが好ましい。

【0010】

本発明の主題の一態様において、溝は、熱酸化物被覆(下地)をさらに含み、特に企図されている溝は、5以上、より好ましくは8以上のアスペクト比(深さ/幅)を有する。好ましい溝の下部は、溝の高さの60%まで、より好ましくは80%まで延伸する。溝が浅溝分離構造(STI)の要素であることがさらに考えられている。

【0011】

本発明の主題の他の態様において、スピンオン化合物は、ケイ素を含み、好ましくはメチルシルセスキオキサン、ハイドロジェンシルセスキオキサン、メチルヒドリドシルセスキオキサン、シリケート、またはペルヒドロシラザンから形成される。好ましい化学気相成長法(CVD)化合物は、ケイ素を含み、特に好ましいCVD化合物は、シランまたはテトラエチルオルトシリケートから形成される。

【0012】

本発明の主題のさらなる態様において、それらの装置を製造する特に好ましい方法は、溝が基板の中に形成されるステップと、第1の化合物がスピンオン堆積によって堆積されるステップとを含む。第1の化合物は、基板の表面以下のレベルまで、溝から部分的に除去され、さらに次のステップで、第2の化合物が、化学気相成長によって、第1の化合物の上部面に堆積される。

【0013】

本発明の主題のさらに企図されている態様において、第1の化合物が、スピン洗浄プロセス、湿式エッチングプロセス、またはドライエッチングプロセスによって、部分的に除去される。企図されている第1の化合物は、メチルシルセスキオキサン、ハイドロジェンシルセスキオキサン、メチルヒドリドシルセスキオキサン、シリケート、およびペルヒドロシラザンを含み、企図されている第2の化合物は、テトラエチルオルトシリケートおよびシランを含む。

【0014】

本発明の種々の目的、特徴、態様および利点は、付随する図面と共に、以下の本発明の好ましい実施形態の詳細な説明から、より明らかになろう。

【発明を実施するための最良の形態】

【0015】

CVD化合物またはスピンオン化合物のみで充填されたSTI構造が、多くの欠点(上記)を示すことは当技術分野で知られている。比較的通常の欠点は、従来技術の図1Aに描かれており、そこでは、電子デバイス100Aが、表面111Aおよび溝120Aを備える基板110Aを有する。溝120Aは、熱酸化物被覆(下地)150Aをさらに有し、溝は、硬化したスピンオン化合物で充填されている。硬化中の寸法的な拘束のため、硬化スピンオン誘電体材料の下部(表面に対して)130Aは、硬化スピンオン誘電体材料の上部(表面に対して)130A’よりも密度が低く、その結果、一般に、後続のステップにおけるエッチング挙動が、異なってくる。

【0016】

発明者らは、スピンオン材料およびCVD材料の両方を用いて、誘電体材料を電子デバイスに堆積することができ、また、その堆積構造が周知の構造よりも多くの利点を示すことを見い出した。図1Bにおいて、電子デバイス100Bは、表面111Bおよび溝120Bを備える基板110Bを含む。溝120Bはさらに、熱酸化物被覆(下地)150Bで被覆されている。溝121Bの下部は、硬化スピンオン化合物130Bで充填され、一方、溝122Bの頂部は、CVD堆積化合物140Bで充填されている。CVD堆積化合物140Bは、表面141Bを有し、基板111Bの表面と同一面である。

【0017】

本発明の主題の特に好ましい態様において、電子デバイス100Bは、集積回路であり、基板110Bは、実質上平坦な表面111Bを備えるシリコンウェーハである。溝120Bは、基板の中にエッチングされ、さらに熱酸化物被覆150Bで被覆される。溝121Bの下部は、溝の底から上方へ、溝高さの60%の高さまで延伸し、基板110B上にスピン塗布された硬化ハイドロジェンシルセスキオキサン130Bで、充填される。溝122Bの上部(溝高さの残りの40%に相当する)は、CVD堆積シラン140Bから形成された二酸化ケイ素で、充填される。CVD堆積二酸化ケイ素140Bは、表面141Bを有し、実質上シリコン基板111Bの表面と同一面(すなわち最大縦段差20nmを有する)である。

【0018】

基板に関しては、シリコンウェーハおよび他のシリコン系半導体基板が、特に好ましいが、シリコンウェーハ以外の多くの基板を、使用でき、代替の基板には、非シリコン半導体材料(例えば、ゲルマニウム系またはガリウム系)および無機/有機誘電体材料(例えば、ポリシリケート、ポリ(アリーレンエーテル)など)が含まれることを理解されたい。

【0019】

基板110Bの実質上平坦な表面111Bは、シリコンウェーハの表面であることが企図されている。本明細書に使用される用語「表面(surface)」は、機能要素(例えば、伝導性配線またはビア)がその上に形成される基板の任意の領域を指す。さらに本明細書に使用される用語「実質上平坦な表面(substantially planar surface)」は、表面が平坦化プロセス(例えば化学的機械的平坦化(CMP))を受けて、不均一性が表面の最高点と最低点の間で約5nm〜20nm以下であることを意味する。本発明の主題の代替の態様では、表面は、機能性および非機能性材料を含めて、代替の材料をさらに含むことができる。例えば、機能性材料は、誘電体材料、熱酸化物、金属を含むことができ、一方、非機能性材料は、エッチング停止層(例えば、窒化ケイ素)または他のマスキング材料を含むことができる。

【0020】

また、適切な溝は、基板中にエッチングされ、一般に、約50nm〜500nmの幅、約400nm〜700nmの深さを有することが考えられる。しかし、約500nm〜5000nmまたはそれ以上のより大きな幅も、考えられる。同様に、企図されている溝は、特定の深さに制限される必要はなく、適切な溝は、約200nm〜2000nmまたはそれ以上の深さであることが考えられる。企図されている溝のアスペクト比(幅に対する深さ)は、特定の数値または範囲に制限されることはないが、好ましいアスペクト比は、5以上(例えば、5〜10)、より好ましくは8以上、最も好ましくは10以上(例えば、10〜15)であることが特に考えられる。同様に、企図されている溝のレイアウト(すなわち導路)は、大きく変化でき、企図されているレイアウトは、線状、円形状、曲線状、およびその妥当な組み合わせを含むことができることを理解されたい。適切な溝は、基板中にエッチングするのが一般に考えられるが、溝形成のやり方は、本発明の主題を制限するものではないことを理解されたい。従って、代替の方法で形成された溝も、考えられ、その方法は、アディティブ(すなわち、表面に壁を付加することによる溝形成)法およびサブトラクティブ(すなわち、表面から材料を除去することによる溝形成)法を含む。

【0021】

適切であれば、企図されている溝は、溝の床および/または側壁の少なくとも一部に結合した追加の層または被覆を、さらに含むことができる。例えば、考えられる追加の層または被覆は、熱酸化物被覆、1種またはそれ以上の有機および/または無機誘電体、金属、ポリシリコンなどを含むことができる。当分野に周知の、基板中に溝を形成する多くの方法があり、周知の方法の全ては、本明細書に示す教示と共に使用することが適切であると考えられる。

【0022】

スピンオン化合物に関しては、全ての周知のスピンオン誘電体は本発明に使用するのに適していると考えられ、誘電体を生成するのにさらに硬化ステップを必要とする、または必要としない無機および有機スピンオン化合物を含む。例えば、適切な有機スピンオン誘電体は、共役および非共役芳香族ポリマー(例えば、ポリイミド、ポリアリーレンなど)、および非芳香族ポリマー(例えば、エポキシ架橋、シアン酸エステル樹脂など)を含む。適切な無機スピンオン誘電体は、ケイ素を含む種々の化合物を含み、特に考えられる無機スピンオン化合物は、メチルシルセスキオキサン、ハイドロジェンシルセスキオキサン、メチルヒドリドシルセスキオキサン、シリケート、およびペルヒドロシラザンである。有用な有機ヒドリドシロキサンは、通例に譲渡された米国特許第6,143,855号および第6,043,330号に開示されており、本明細書に参照して組み込まれている。特に有用な1種の有機ヒドリドシロキサンは、Honeywell International Inc.から、HOSP(商標)スピンオン誘電体として、市場で入手可能である。特定の用途の特定のスピンオンおよび硬化の条件は、一般に、スピンオン化合物、溝深さ、必要な硬化程度に依存し、通常の技術者であれば、多くの実験を行うことなく容易に決定することができる。

【0023】

溝の下部をスピンオン化合物で充填することは一般に考えられる。本明細書で使用される用語「下部(lower portion)」は、溝の床(すなわち、基板の表面に関して溝の最下部)から基板の表面よりも下方にある任意の溝高さまで延伸する、溝の容積を指す。したがって、溝の下部は、溝の床から溝の深さの10%まで(すなわち、溝の床と基板表面間の最大縦距離)、好ましくは溝の深さの40%まで、より好ましくは60%まで、さらにより好ましくは80%まで、最も好ましくは80%〜95%まで延伸できることが考えられる。スピンオン化合物を使用して溝の中に誘電体を形成することは、溝が比較的高いアスペクト比(すなわち5より大きい)を有するときに、特に有用であることを理解されたい。なぜならば、アスペクト比の増大によって、典型的なCVDプロセスの間に、ボイドがしばしば形成されるからである。

【0024】

CVD堆積化合物が、熱酸化物に類似したエッチング抵抗性(すなわち、熱酸化物のエッチング速度の1〜3倍、好ましくは1〜2倍、より好ましくは1〜1.5倍のエッチング速度)を有することが好ましく、よく理解されたCMP条件を有するとさらに考えられる。例えば、適切なCVD堆積化合物は、ケイ素を含み、特に好ましいCVD堆積化合物は、シランまたはテトラエチルオルトシリケート(TEOS)から形成される。しかし、代替の態様では、ケイ素含有化合物以外の周知のCVD化合物も、本発明で使用するのに適していると考えられる。CVD化合物の堆積に関しては、特定の条件は、大きく変化することができ(すなわち、HDP・CVD、低圧(LP)・CVD、大気圧(AP)・CVD、プラズマ強化(PE)・CVD)、使用される特定の材料に依存することを認識されたい。溝の上部は、CVD堆積化合物で充填されることがさらに考えられている。本明細書で使用される用語である、溝の「上部(upper portion)」は、基板の表面と溝の下部との間の溝の容積を指す。1層またはそれ以上の追加の層を、硬化スピンオン化合物とCVD化合物との間に配設することができ、考えられる追加の層が、機能性(例えば、誘電体、伝導性、半導体性)および非機能性(例えば、接着促進剤)の層を含むことをさらに認識されたい。本発明の主題には重要ではないが、CVD化合物の上部表面は、基板表面と実質上同一面である(すなわち、50nmの最大縦段差)ことが特に好ましい。当分野で知られている多くの平坦化法があり、周知の方法の全てが、本発明に使用するのに適していると考えられる。特に好ましい方法は、CMPである。

【0025】

したがって、本発明の主題による電子デバイスの形成方法は、表面を有する基板中に溝が形成され、第1の化合物がスピンオン堆積を用いて溝の中に堆積される1つのステップを含む。さらなるステップにおいて、溝中の化合物の上部表面が、基板の表面よりも低くなるように、第1の化合物が、部分的に溝から除去される。さらに他のステップにおいて、第2の化合物が、表面および第1の化合物の上部表面上にCVDによって堆積される。基板、基板の表面、溝、スピンオン化合物(すなわち、第1の化合物)、CVD堆積化合物(すなわち、第2の化合物)に関しては、上で論じた同じ考えが適用される。

【0026】

スピンオン化合物を溝から部分的に除去する方法(例えば、湿式エッチングまたはドライエッチング)の全ては、適切であると考えられるが、スピン洗浄プロセス(以下)によって、部分除去を行うのが特に好ましい。企図されているスピン洗浄プロセスは、溶媒混合物を、部分的または完全に硬化したスピンオン膜(例えば、溝中のスピンオン化合物)上に、回転供給するステップを含む。溶媒混合物は、一般に、少なくとも1種の溶媒(すなわち、スピンオン膜を破壊および/または溶解する組成物、活性成分とも呼ばれる)と、少なくとも1種の非溶媒(すなわち、スピンオン膜に不活性であるか、またはスピンオン膜を溶媒より少なくとも10倍遅い速度で破壊および/または溶解する組成物)とを含む。溶媒および非溶媒の混和性は、重要ではないが、溶媒混合物が、非溶媒と混和性のある溶媒を含むことが好ましい。特定の溶媒の選択は、一般に、スピンオン膜の組成物および必要な除去速度に依存するであろう。しかし、全ての周知の溶媒は、本発明で使用するのに適していると一般に考えられ、考えられる溶媒は、水性および非水性溶媒、酸および塩基を含み、その全ては、例えば極性、疎水性、混和性などを含む種々の基準によって、選択することができる。

【0027】

したがって、スピンオン化合物を除去する方法は、スピンオン化合物を基板の表面上に堆積するステップを含む。さらなるステップで、スピンオン化合物は、溶媒混合物でスピン洗浄され、溶媒混合物は、第1のスピンオン化合物を溶解する第1の溶媒と、スピンオン化合物に不活性な第2の溶媒とを含む。特に考えられるスピンオン化合物は、ケイ素を含み、一方、第1の溶媒は、酢酸プロピルを含み、第2の溶媒は、乳酸エチルを含む。しかし、種々の代替溶媒も、考えられる。例えば、第1の溶媒は、ケトン(例えば、MIBK)、エステル(例えば、酢酸プロピル)、エーテル(例えば、PGMEA)、炭化水素(例えば、ヘキサン)であることができ、第2の溶媒は、水、アルコール(例えば、エタノール、メタノール)、アセトニトリル、アミン、またはアミドであることができる。適切な基板を、第1の温度に加熱して、溶媒混合物を除去し、次いで、第2の温度に加熱して、スピンオン化合物を硬化することがさらに考えられている。

【0028】

考えられているスピン洗浄プロセスにおいて、スピンオン膜の除去速度および平坦化の程度(DOP、degree of planarization)は、例えば溶媒の選択および比、スピン条件、温度、分注プロファイルおよび容量などを含む、種々のパラメーターによって、有利に制御することができることを特に理解されたい。例えば、溶媒混合物中の非溶媒に対する溶媒の比を、高くすることによって、一般に、より高い除去速度が得られる。DOPは、一般に、狭いフィーチャー内部のマイクロローディングを用いて制御することができる。活性成分が、新鮮な溶媒で置き換わるよりも速く、除去した材料で飽和されるときに、マイクロローディングは、狭く密集したフィーチャー(溝)の内部に起きる。マイクロローディング効果は、溝またはフィーチャーの内部の流体力学によって起こり、新鮮な溶媒の供給が、制限される。非溶媒に対する溶媒の比が、低い(すなわち、活性成分の濃度が低い)と、活性成分が、より急速に飽和されるので、効果が、大きくなる。マイクロローディングは、平坦な領域に比べて、狭いフィーチャーおよび密集したパターン領域の、除去速度比を効果的に小さくする。マイクロローディングによるDOPの改善は、静的用途の代わりに動的溶媒用途(すなわち、スピン洗浄)を使用することによって最善に用いられる。なぜならば、平坦な表面には、新鮮な溶媒が、常に供給され、他方、狭いフィーチャーの内部への溶媒供給は、妨げられ、したがって、減少するからである。最適スピン条件は、パターン設計およびフィーチャー密度に依存する。スピン洗浄プロセスは、STI構造の形成におけるスピンオン膜の部分除去以外の用途にも用いることができ、企図されているプロセスは、スピンオン膜または化合物を少なくとも部分的に除去する必要のある全てのプロセスを含むことも認識すべきである。例えば、考えられる代替のプロセスは、一般に部分的なエッチバック(例えば、IMD用途において、金属配線を備えるパターン形成されたウェーハ上の誘電体材料の除去)を必要とするプロセスを含む。

【0029】

また、スピン洗浄プロセスは、通常用いられているドライエッチングを用いるSOGエッチバックプロセスのコスト効果のある修正であり得ることもさらに考えられている。SOGエッチバックプロセスは、しばしば比較的高価である。なぜならば、以下のようないくつかのプロセスステップが、一般に、必要とされるからである。1)金属配線の形成、2)PECVD装置:CVDを用いる下地酸化物の堆積(このステップは省略することができる)、3)スピンコータ:間隙を充填し局部的な平坦化を改善するスピン、SOGの焼成および硬化、4)プラズマエッチャ:金属配線の頂部にSOGが少ないまたは残らないようにするSOGのエッチバック(これは「ビアの汚染(poisoned vias)」を避ける)、5)PECVD装置:酸化物キャップの堆積、6)CMP装置:酸化物キャップのCMP(このステップはSOGプロセスの能力および製造プロセスの平坦化要求度によって省略することができる)。したがって、企図されているプロセスは、時間のかかるエッチングステップ(5)を省略することができ、また、一般により良好な局部の平坦化を生じさせ、さらにCMPの必要性がなくなることを特に認識すべきである。したがって、企図されているプロセスは、スピンプロセス(4)を、4a)スピンコーティング、4b)任意選択的な部分焼成、4c)スピン洗浄を用いる部分除去および膜の平坦化、4d)焼成プロセス、4e)硬化プロセスに、修正することを理解されたい。スピン洗浄プロセスは、従来のスピンカップ(spin cup)を用いて市場で入手可能なスピン工程(spin tracks)に一体化することができ、したがって、新しいプロセス装置を必要としない。また、スピン洗浄プロセスは、上記のように平坦化を改善するので、後続のCMPプロセス(6)を、省略することができる。

【0030】

本発明の主題のさらに企図されている態様では、電子デバイスを形成する方法は、基板の表面とCVD堆積化合物の上部表面と間の同一面性を達成するために、平坦化ステップを追加して含むことができる。企図されている平坦化ステップは、一般に全ての知られている平坦化プロセスを含むが、平坦化は、CMPで行うことが特に好ましい。

(実施例)

(スピン洗浄プロセス)

この実施例に記載されている例示的スピン洗浄プロセスは、従来のエッチバック間隙充填(etch−back gap fill)プロセスの代替として、用いることができる。

【0031】

半導体デバイス構造を、標準的な製造技術を使用して、製造する。金属配線構造(2)を、半導体基板(1)の上に、構造1のように形成する。0.18ミクロン以下のデバイス寸法の相互配線金属は、通常、少量のドーパントを有するアルミニウムである。しかし、金属の選択は、本発明の主題を制限するものではなく、銅を含む他の金属も使用できることが考えられる。しかし、サブトラクティブプロセスには、アルミニウムが好ましい。

【0032】

【表1】

【0033】

第1レベルの金属線(2)の堆積の後に、任意選択的な酸化物下地(3)を、堆積する(構造2)。酸化物下地の厚さは、1〜200nmであり、50nmが、典型的な値である。酸化物下地は、PECVD TEOSを用いて堆積するのが好ましいが、PECVDシランなどの他の酸化物も、使用することができる。プロセスステップの数を削減するために、酸化物下地を使用しないことが、好ましい。

【0034】

【表2】

【0035】

次いでスピンオン材料(4、構造3を参照)を、配線間誘電体として堆積する。スピンオン誘電体の好ましい厚さは、スピンオン誘電体、金属の厚さ、および必要な平坦化の程度に依存する。例えば、HOSP(商標)(スピンオン誘電体は市場でHoneywell Electronic Materialsから入手可能である)の場合、幅500nmの最小間隙で、高さ800nmのアルミニウム線に関して、スピンオン材料の厚さは、一般に、被覆膜上で、200〜900nmであり、600nmが好ましい。

【0036】

この例では、HOSP(商標)誘電体材料は、標準的なスピンプロセスを用いて堆積するが、特定のスピンプロセスは、スピン洗浄プロセスの用途に大きな影響は与えない。しかし、スピン洗浄を使用するために、標準の焼成手順(標準は150℃、200℃、350℃で各1分である)は、スピン洗浄プロセスの前に用いる最高温度が300℃以下になるように、修正される。なぜならば、320℃以上の温度で焼成すると、HOSP(商標)誘電体材料は、有機溶媒に溶解できないからである。無論、最高温度は、他の材料では異なる。次いで、HOSP膜を、単一の熱板に対して、100℃〜200℃の温度で1分間露出するが、好ましい温度は、150℃である。焼成プロセスによって、材料は、溶融し再流動することができるので、平坦性が向上する。

【0037】

【表3】

【0038】

次いで、溶媒混合物を、スピン洗浄プロセスに分注して、金属線の頂部のスピンオン材料を除去し(構造4を参照されたい)、平坦性を改善する。スピン洗浄溶液は、スピンオン膜以外、基板上のいかなる材料も、除去しない。スピン洗浄プロセスは、通常のスピンコータで行うことができるが、スピンエッチャを使用することもできる。分注の間のスピン速度は、材料、溶媒、ウェーハサイズ、装置の幾何形状に依存し、20rpm〜6000rpmの範囲にすることができる。多くの用途で、1000rpmが、洗浄プロセス中の推奨スピン速度であり、この例で用いている。溶媒の分注速度は、材料、溶媒、ウェーハサイズ、装置の幾何形状に依存し、0.1mL/秒〜50mL/秒の範囲にすることができる。多くの用途で、2mL/秒が、洗浄プロセス中の推奨分注速度であり、この例で用いている。HOSPの溶媒のリストには、ケトン(例えばMIBK)、エステル(例えば酢酸プロピル(PACE)、グリコールエーテルPMアセテート(PGMEA))、炭化水素(例えばヘキサン)が含まれるが、制限されない。非溶媒には、水、アルコール(例えばメタノール、エタノール、イソプロピルアルコール(IPA)、乳酸エチル(EL))、アセトニトリル、アミン、アミドが含まれるが、制限されない。1種以上の溶媒と1種以上の非溶媒とのいくつかの組み合わせが可能であり、好ましい組み合わせは、材料、プロセス手順、および用途で必要な除去速度に、大きく依存する。この例では、2:1の乳酸エチルとPACEの混合物を、スピン洗浄プロセス用の推奨溶媒混合物として使用し、スピン洗浄プロセスを十分な時間実施した。スピン洗浄プロセスの間に、スピンオン誘電体は、狭い間隙の内部からよりも、金属線の頂部から、より速く除去され(先に説明したマイクロローディング)、それによって、ドライエッチバックプロセスまたは静的湿式エッチングに比べて、平坦性が向上する。下地酸化物は、スピン洗浄プロセスの影響を受けず、これは、下地酸化物も攻撃する従来のドライエッチングプロセスに比べて、有益である。スピン洗浄プロセスの終わりに、ウェーハを分注なしで、3000rpmの回転速度で30秒間回転して、膜を乾燥する。次いで、膜を、熱板の上で、350℃の温度で1分間焼成する。次いで、膜は、酸素レベル20ppm未満の窒素雰囲気中で、400℃の温度で1時間水平炉中で硬化する。スピン洗浄プロセスの終わりに、スピンオン材料(HOSP)は、金属線の頂部から除去され、一方、狭い間隙の間には、スピンオン材料が残る。

【0039】

【表4】

【0040】

次いで、CVD酸化物を、ビア(via)レベル用に堆積する(構造5を参照されたい)。CVD酸化物の厚さは、デバイス構造に依存し、500nm〜3000nmが、典型的である。一般に、PECVD TEOSが、このプロセスに使用される。

【0041】

【表5】

【0042】

次いで、任意選択的に、構造を、化学機械研磨(CMP、chemical mechanical polishing)プロセスにかける。CMPプロセスは、酸化物層の部分を除去し、平坦性を改善する(構造6)。

【0043】

【表6】

【0044】

(スピンエッチングプロセス)

スピンエッチングプロセスは、上記のスピン洗浄プロセスにある程度類似しているが、エッチング剤として無機溶媒を使用する。この例で用いたスピンオン材料は、市場でHoneywellから入手可能なAccuglass(登録商標)512Bである。処方および回転速度は、被覆膜上に500nmの厚さの膜を得るように選択する。Accuglass(登録商標) 512Bは、標準的なスピンプロセスおよび焼成プロセスを用いて堆積し、80℃、150℃、250℃で各1分間の焼成が、用いられる。次いで、ウェーハを、酸素レベル20ppm未満の窒素雰囲気中で、400℃の温度で1時間、水平炉中で硬化する(構造はこの時点で構造3に示したように見える)。

【0045】

別法の硬化プロセスは、400℃炉の硬化の代りに、酸素プラズマアッシング(10%窒素)を用いる。このプロセスは、厚さ500nmまでのAccuglass(登録商標) 512B被覆膜に使用できる。

【0046】

次いで、ウェーハを、スピンエッチング装置で処理する。好ましいエッチング剤は、エッチングすべき材料に依存する。Accuglass(登録商標)512Bスピンオン材料を用いるこの例では、10:1から500:1までのBOE(緩衝酸化物エッチング、buffer oxide etch)を使用することができ、50:1が好ましい。エッチングプロセス中の好ましい回転速度は、1000rpmに設定し、BOE流量は、0.8lpm(毎分リットル)に設定する。処理時間は、15秒に設定する。被覆エッチング速度は、140A/秒(毎秒オングストローム)であり、これは、下地材料として使用するTEOS酸化物のエッチング速度の約40倍である。スピンエッチングプロセスの終わりに、ウェーハを、DI(脱イオン)水を用いて15秒間洗浄し、次いで、回転速度3000rpmで30秒間回転して、膜を乾燥する。スピン洗浄プロセスは、金属線の頂部の材料を優先的に除去し、全体の平坦性を向上させる。スピンエッチングプロセスを用いる例では、金属線の頂部の512B材料は、完全に除去される。スピンオン材料Accuglass(登録商標)512Bに対するBOEの高い選択性によって、TEOS下地へのエッチングは、5nm未満であり、したがって無視できる。後続のステップは、上記のステップと同一である。

【0047】

(スピン洗浄プロセスおよび酸化物キャップを用いるSTIプロセス)

図1Bは、本発明の好ましい態様によるSTI構造を概略的に示す断面図である。プロセスは、熱酸化を用いてシリコン基板(構造7の(1))上に、パッド酸化物層(ステップ1)(構造7の(2))を形成することから開始する(構造7)。パッド酸化物の厚さは、2〜30nmが典型的であり、10nmが好ましい厚さである。

【0048】

【表7】

【0049】

次のプロセスステップ(ステップ2)は、パッド酸化物の頂部に、窒化ケイ素層(構造8の(3))を、堆積することである(構造8)。窒化物層の厚さは、50〜200nmが典型的であり、100nmが好ましい。

【0050】

【表8】

【0051】

次のステップ(ステップ3)は、半導体基板上に、フォトレジスト層を堆積することである。基板上にパターンを転写するために、フォトリソグラフィ(ステップ4)プロセスを実施する。次いで、異方性エッチング(ステップ5)を実施して、最初に、窒化ケイ素を開口し(構造9)、次いで、溝構造を形成する(構造10の(4))。

【0052】

【表9】

【0053】

【表10】

【0054】

次いで、熱酸化(ステップ6)を用いて、溝の側壁および底に、酸化物を成長する。溝の側壁の厚さは、5〜15nmが典型的であり、10nmが好ましい厚さである(構造11)。

【0055】

【表11】

【0056】

次いで、スピンオン材料を、溝の内部に堆積する(ステップ7)(構造12の(6))。スピンオン誘電体の好ましい厚さは、スピンオン誘電体の種類、溝の幅および高さ、ならびにアスペクト比の分布に、依存する。1ミクロン未満の溝深さのSTI構造では、HOSP(商標)スピンオン誘電体(市場でHoneywell Electronic Materialsから入手可能)は、適切な材料である。一般に、溝深さの60%〜80%の膜厚さで十分である。溝深さが600nmでは、被覆膜厚さは、400nmが好ましい。この例では、HOSP(商標)スピンオン誘電体は、標準的なスピンプロセスを用いて堆積するが、特定のスピンプロセスは、スピン洗浄プロセスの適用に大きな影響は与えない。しかし、HOSPは320℃以上の温度で焼成すると有機溶媒に溶解できないので、スピン洗浄を使用するために、スピン洗浄プロセスの前に用いる最高温度が300℃以下になるように、標準の焼成手順(標準は150℃、200℃、350℃で各1分である)を修正する。無論、最高温度は、他の材料では異なる。次いで、HOSP膜を、単一の熱板で、100℃〜200℃の温度で1分間露出するが、好ましい温度は、150℃である。焼成プロセスによって、材料は溶融し再流動することができるので、平坦性が向上する。

【0057】

【表12】

【0058】

次いで、スピン洗浄プロセスを用いてHOSP(商標)膜を、部分的に除去する(ステップ8)。溶媒混合物を、スピン洗浄プロセスに分注し、これは、窒素化物層の頂部から全てのHOSPポリマーを除去する(構造13)(上記のスピン洗浄プロセスで説明した同じ手順を用いる)。スピン洗浄時間は、HOSP膜の頂部表面が最も狭い溝より下で基板表面の20〜200nmとなるように、調節する。HOSP表面は、より広い溝では、より低い。

【0059】

【表13】

【0060】

次いで、膜を、熱板上で、350℃の温度で1分間焼成する(ステップ9)。次いで、膜を、酸素:窒素が20%:80%の雰囲気中、水平炉中で700℃で1時間硬化する(ステップ10)。硬化プロセス中に、HOSP膜の有機成分は、酸化して除去され、これはFTIR分光計を用いて実証することができる。次いで、CVD酸化物を、堆積する(ステップ11)(構造14の(5))。スピンオン・ポリマーを用いることによる向上した平坦性、およびスピン洗浄プロセスによる平坦化の恩恵で(標準的なCVDだけのプロセスと比べて)、必要なCVD酸化物の厚さは、より薄くて済む。酸化物CMPプロセスの後に必要な平坦性を達成するのに、一般に、溝深さの20〜90%の酸化物の厚さで、十分である(ステップ12)(構造15)。

【0061】

【表14】

【0062】

【表15】

【0063】

後続のステップにおいて、残りの酸化物および窒化物の層を、エッチングする(ステップ13)(構造16)。

【0064】

【表16】

【0065】

他の利点の中でも、企図されているプロセスを用いることによって、(1)比較的高価なHDP・CVDプロセスを省くことができ、(2)スピン洗浄プロセスの使用によって平坦性を大きく向上することができ、(3)酸化物の厚さを低減でき、それによってP、ECVDのコストおよびCMPに必要な時間を低減できることを認識すべきである。

【0066】

(スピンエッチングプロセスおよび酸化物キャップを用いるSTIプロセス)

この例のステップ1から6は、上記の例と同じである。ステップ7は、HOSP膜が全て標準的な焼成プロセス(150℃、200℃、350℃で各1分)によって処理されることを除き、例3とほとんど同じである。次いで、ウェーハを硬化する(前の例のステップ10)。硬化プロセスの後、スピンエッチングプロセスを用いる。スピンエッチングプロセスは、例2で説明した同じプロセスを用い、酸化物の堆積(ステップ11)、CMP(ステップ12)、エッチング(ステップ13)が続く。

【0067】

したがって、浅溝分離構造を形成する方法は、表面を有する基板に、溝を形成し、第1の化合物を、スピンオン堆積を用いて溝の中に堆積する1つのステップを含むことが考えられる。他のステップにおいて、化合物の上部表面が、基板の表面の下方になるように、第1の化合物を、少なくとも部分的に溝から除去し、さらなるステップにおいて、第2の化合物を、基板表面上および第1の化合物の上部表面に、化学気相成長法で堆積する。企図されている方法の例示的なフロー図は、図2に示されている。

【0068】

このように、電子デバイスおよびその形成の具体的な実施形態および用途を説明した。しかし、当業者であれば、本明細書の発明の概念から逸脱することなく、既に説明したもの以外に多くの修正が可能であることは明らかなはずである。したがって、本発明の主題は、付随する請求項の精神以外で制限されるものではない。さらに、明細書および請求項の解釈において、全ての用語は文脈に一致するように最も広い意味に解釈すべきである。特に、用語「備える」および「含む」は、要素、成分、またはステップを非制限的に指すものと解釈すべきであり、参照される要素、成分、またはステップが、存在し、または用いられ、または、明示的に参照されていない他の要素、成分、あるいはステップと組み合わせることができることを示唆するものである。

【図面の簡単な説明】

【0069】

【図1−A】従来技術の電子デバイスの縦断面概略図である。

【図1−B】本発明の主題による電子デバイスの縦断面概略図である。

【図2】本発明の主題による電子デバイスを製造する例示的方法のフロー図である。

Claims (23)

- 電子デバイスであって、該電子デバイスは、

下部および頂部を備える溝を有する基板を、

備え、

溝の下部が、硬化したスピンオン化合物で充填され、頂部が、化学気相成長法で堆積した化合物で充填される、電子デバイス。 - 請求項1に記載のデバイスであって、前記基板が、化学気相成長法で堆積した化合物の頂部表面と実質上同一面の表面を有する、デバイス。

- 請求項2に記載のデバイスであって、前記溝が、熱酸化物被覆をさらに含む、デバイス。

- 請求項3に記載のデバイスであって、前記溝が、5以上のアスペクト比(深さ/幅)を有する、デバイス。

- 請求項3に記載のデバイスであって、前記溝が、8以上のアスペクト比(深さ/幅)を有する、デバイス。

- 請求項1に記載のデバイスであって、前記スピンオン化合物が、ケイ素を含む、デバイス。

- 請求項1に記載のデバイスであって、前記スピンオン化合物が、メチルシルセスキオキサン、ハイドロジェンシルセスキオキサン、メチルヒドリドシルセスキオキサン、シリケート、及び、ペルヒドロシラザンからなる群から選択される少なくとも1種の化合物から、形成される、デバイス。

- 請求項1に記載のデバイスであって、前記化学気相成長法で堆積した化合物が、ケイ素を含む、デバイス。

- 請求項1に記載のデバイスであって、前記化学気相成長法で堆積した化合物が、シランまたはテトラエチルオルトシリケートから形成される、デバイス

- 請求項1に記載のデバイスであって、前記溝が、深さを有し、前記溝の下部が、深さの60%まで延伸する、デバイス。

- 請求項1に記載のデバイスであって、前記溝が、深さを有し、前記溝の下部が、深さの80%まで延伸する、デバイス。

- 浅溝分離構造を形成する方法であって、

表面を有する基板中に溝を形成し、第1の化合物を溝の中にスピンオン堆積を用いて堆積するステップと、

前記化合物の上部表面が前記基板の表面の下方にあるように、第1の化合物を前記溝から部分的に除去するステップと、

第2の化合物を前記基板の表面および前記第1の化合物の上部表面の上に化学気相成長法によって堆積するステップと、

を含む方法。 - 請求項12に記載の方法であって、

前期基板の表面および前記第2の化合物の上部表面が実質上同一面であるように、前記分離構造を平坦化するステップを、

さらに含む方法。 - 請求項12に記載の方法であって、前記基板表面および前記溝が、熱酸化物被覆をさらに含む、方法。

- 請求項13に記載の方法であって、前記溝が、5以上のアスペクト比(深さ/幅)を有する、方法。

- 請求項12に記載の方法であって、

酸化物を形成するために、前記第1の化合物を硬化するステップを、

さらに含む方法。 - 請求項12に記載の方法であって、部分的に除去する前記ステップが、スピン洗浄プロセス、湿式エッチングプロセス、及び、ドライエッチングプロセスからなる群から選択されるプロセスを含む、方法。

- 請求項12に記載の方法であって、前記第1の化合物が、メチルシルセスキオキサン、ハイドロジェンシルセスキオキサン、メチルヒドリドシルセスキオキサン、シリケート、及び、ペルヒドロシラザンからなる群から選択される少なくとも1種の化合物から、形成される、方法。

- 請求項12に記載の方法であって、前記第2の化合物が、テトラエチルオルトシリケートまたはシランから形成される、方法。

- スピンオン化合物を除去する方法であって、該方法は、

スピンオン化合物を基板の表面上にスピン堆積するステップと、

前記スピンオン化合物を溶媒混合物でスピン洗浄するステップと、

を含み、

溶媒混合物が、前記スピンオン化合物を溶解する第1の溶媒と、前記スピンオン化合物に不活性な第2の溶媒とを含む、方法。 - 請求項20に記載の方法であって、

前記基板を第1の温度に加熱して溶媒混合物を除去し、さらに前記基板を第2の温度に加熱してスピンオン化合物を硬化するステップを、

さらに含む方法。 - 請求項20に記載の方法であって、前記スピンオン化合物が、ケイ素を含み、前記第1の溶媒が、酢酸プロピルを含み、第2の溶媒が、乳酸エチルを含む、方法。

- 請求項20に記載の方法であって、前記スピンオン化合物が、ケイ素を含み、前記第1の溶媒が、ケトン、エステル、エーテル、及び、炭化水素からなる群から選択され、第2の溶媒が、水、アルコール、アセトニトリル、アミン、及び、アミドからなる群から選択される、方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/943,237 US20030054616A1 (en) | 2001-08-29 | 2001-08-29 | Electronic devices and methods of manufacture |

| PCT/US2002/026780 WO2003021636A2 (en) | 2001-08-29 | 2002-08-23 | Electronic devices and methods of manufacture |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005502202A true JP2005502202A (ja) | 2005-01-20 |

| JP2005502202A5 JP2005502202A5 (ja) | 2005-12-22 |

Family

ID=25479290

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003525884A Withdrawn JP2005502202A (ja) | 2001-08-29 | 2002-08-23 | 電子デバイスおよび製造方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US20030054616A1 (ja) |

| EP (1) | EP1421615A2 (ja) |

| JP (1) | JP2005502202A (ja) |

| KR (1) | KR20040033000A (ja) |

| CN (1) | CN1579016A (ja) |

| AU (1) | AU2002326737A1 (ja) |

| TW (1) | TW569340B (ja) |

| WO (1) | WO2003021636A2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017092457A (ja) * | 2015-10-23 | 2017-05-25 | 三星エスディアイ株式会社Samsung SDI Co., Ltd. | 膜構造物の製造方法およびパターン形成方法 |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TWI320214B (en) * | 2002-08-22 | 2010-02-01 | Method of forming a trench isolation structure | |

| US7348281B2 (en) * | 2003-09-19 | 2008-03-25 | Brewer Science Inc. | Method of filling structures for forming via-first dual damascene interconnects |

| JP2005150500A (ja) * | 2003-11-18 | 2005-06-09 | Toshiba Corp | 半導体装置および半導体装置の製造方法 |

| JP2005166700A (ja) | 2003-11-28 | 2005-06-23 | Toshiba Corp | 半導体装置及びその製造方法 |

| KR100562302B1 (ko) * | 2003-12-27 | 2006-03-22 | 동부아남반도체 주식회사 | 멀티 화학액 처리 단계를 이용한 랜덤 폴리머 제거 방법 |

| US7924778B2 (en) * | 2005-08-12 | 2011-04-12 | Nextel Communications Inc. | System and method of increasing the data throughput of the PDCH channel in a wireless communication system |

| EP2696660A4 (en) * | 2011-04-06 | 2014-10-22 | Konica Minolta Inc | METHOD FOR MANUFACTURING ORGANIC ELECTROLUMINESCENCE ELEMENT AND ORGANIC ELECTROLUMINESCENCE ELEMENT |

| KR102021484B1 (ko) * | 2014-10-31 | 2019-09-16 | 삼성에스디아이 주식회사 | 막 구조물 제조 방법, 막 구조물, 및 패턴형성방법 |

| KR101907499B1 (ko) * | 2015-11-20 | 2018-10-12 | 삼성에스디아이 주식회사 | 막 구조물 제조 방법 및 패턴형성방법 |

| KR102015406B1 (ko) * | 2016-01-25 | 2019-08-28 | 삼성에스디아이 주식회사 | 막 구조물 제조 방법 및 패턴형성방법 |

| TWI713679B (zh) * | 2017-01-23 | 2020-12-21 | 聯華電子股份有限公司 | 互補式金氧半導體元件及其製作方法 |

| KR102112737B1 (ko) * | 2017-04-28 | 2020-05-19 | 삼성에스디아이 주식회사 | 막 구조물 제조 방법 및 패턴형성방법 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4510176A (en) * | 1983-09-26 | 1985-04-09 | At&T Bell Laboratories | Removal of coating from periphery of a semiconductor wafer |

| US4732785A (en) * | 1986-09-26 | 1988-03-22 | Motorola, Inc. | Edge bead removal process for spin on films |

| US5296330A (en) * | 1991-08-30 | 1994-03-22 | Ciba-Geigy Corp. | Positive photoresists containing quinone diazide photosensitizer, alkali-soluble resin and tetra(hydroxyphenyl) alkane additive |

| JP2951504B2 (ja) * | 1992-06-05 | 1999-09-20 | シャープ株式会社 | シリル化平坦化レジスト及び平坦化方法並びに集積回路デバイスの製造方法 |

| JP3740207B2 (ja) * | 1996-02-13 | 2006-02-01 | 大日本スクリーン製造株式会社 | 基板表面に形成されたシリカ系被膜の膜溶解方法 |

| US5866481A (en) * | 1996-06-07 | 1999-02-02 | Taiwan Semiconductor Manufacturing Company Ltd. | Selective partial curing of spin-on-glass by ultraviolet radiation to protect integrated circuit dice near the wafer edge |

| DE69716218T2 (de) * | 1996-11-20 | 2003-04-17 | Jsr Corp., Tokio/Tokyo | Härtbare Harzzusammensetzung und gehärtete Produkte |

| US6485576B1 (en) * | 1996-11-22 | 2002-11-26 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method for removing coating bead at wafer flat edge |

| US5913979A (en) * | 1997-01-08 | 1999-06-22 | Taiwan Semiconductor Manufacturing Co., Ltd | Method for removing spin-on-glass at wafer edge |

| US6194283B1 (en) * | 1997-10-29 | 2001-02-27 | Advanced Micro Devices, Inc. | High density trench fill due to new spacer fill method including isotropically etching silicon nitride spacers |

| US6008109A (en) * | 1997-12-19 | 1999-12-28 | Advanced Micro Devices, Inc. | Trench isolation structure having a low K dielectric encapsulated by oxide |

| US6140254A (en) * | 1998-09-18 | 2000-10-31 | Alliedsignal Inc. | Edge bead removal for nanoporous dielectric silica coatings |

| JP2001181577A (ja) * | 1999-12-27 | 2001-07-03 | Sumitomo Chem Co Ltd | 多孔質有機膜形成用塗布液および多孔質有機膜の形成方法 |

| US6565920B1 (en) * | 2000-06-08 | 2003-05-20 | Honeywell International Inc. | Edge bead removal for spin-on materials containing low volatility solvents fusing carbon dioxide cleaning |

| US6444495B1 (en) * | 2001-01-11 | 2002-09-03 | Honeywell International, Inc. | Dielectric films for narrow gap-fill applications |

-

2001

- 2001-08-29 US US09/943,237 patent/US20030054616A1/en not_active Abandoned

-

2002

- 2002-08-23 EP EP02761473A patent/EP1421615A2/en not_active Withdrawn

- 2002-08-23 AU AU2002326737A patent/AU2002326737A1/en not_active Abandoned

- 2002-08-23 WO PCT/US2002/026780 patent/WO2003021636A2/en not_active Application Discontinuation

- 2002-08-23 KR KR10-2004-7003141A patent/KR20040033000A/ko not_active Application Discontinuation

- 2002-08-23 CN CNA028214544A patent/CN1579016A/zh active Pending

- 2002-08-23 JP JP2003525884A patent/JP2005502202A/ja not_active Withdrawn

- 2002-08-29 TW TW091119682A patent/TW569340B/zh active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017092457A (ja) * | 2015-10-23 | 2017-05-25 | 三星エスディアイ株式会社Samsung SDI Co., Ltd. | 膜構造物の製造方法およびパターン形成方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20030054616A1 (en) | 2003-03-20 |

| WO2003021636A2 (en) | 2003-03-13 |

| AU2002326737A1 (en) | 2003-03-18 |

| WO2003021636B1 (en) | 2003-12-04 |

| EP1421615A2 (en) | 2004-05-26 |

| TW569340B (en) | 2004-01-01 |

| WO2003021636A3 (en) | 2003-11-06 |

| CN1579016A (zh) | 2005-02-09 |

| KR20040033000A (ko) | 2004-04-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100568100B1 (ko) | 트렌치형 소자 분리막 형성 방법 | |

| US8828877B2 (en) | Etching solution and trench isolation structure-formation process employing the same | |

| US7557420B2 (en) | Low temperature process for polysilazane oxidation/densification | |

| US7052932B2 (en) | Oxygen doped SiC for Cu barrier and etch stop layer in dual damascene fabrication | |

| US6890865B2 (en) | Low k film application for interlevel dielectric and method of cleaning etched features | |

| US8420541B2 (en) | Method for increasing adhesion between polysilazane and silicon nitride | |

| JP2005502202A (ja) | 電子デバイスおよび製造方法 | |

| US7053005B2 (en) | Method of forming a silicon oxide layer in a semiconductor manufacturing process | |

| JP3992654B2 (ja) | 半導体装置の製造方法 | |

| KR100891401B1 (ko) | 반도체 소자의 화학적기계적 연마 방법 | |

| US20120276714A1 (en) | Method of oxidizing polysilazane | |

| US20070232062A1 (en) | Damascene interconnection having porous low k layer followed by a nonporous low k layer | |

| KR100656225B1 (ko) | 스핀-온 세라믹 막으로 구성된 패터닝층 | |

| KR100874429B1 (ko) | 반도체소자 제조시의 갭 매립방법 | |

| KR100518895B1 (ko) | 반도체 소자의 금속 배선 형성 방법 | |

| KR100481889B1 (ko) | 반도체 소자의 제조방법 | |

| US6720276B2 (en) | Methods of forming spin on glass layers by curing remaining portions thereof | |

| KR20050069427A (ko) | 소자 분리막 형성 방법 | |

| JP2005175394A (ja) | ダマシン法を用いた配線の形成方法及び該配線形成に用いるシリカ系被膜形成用塗布液 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050401 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050401 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20060605 |