JP2005301095A - 表示装置 - Google Patents

表示装置 Download PDFInfo

- Publication number

- JP2005301095A JP2005301095A JP2004119893A JP2004119893A JP2005301095A JP 2005301095 A JP2005301095 A JP 2005301095A JP 2004119893 A JP2004119893 A JP 2004119893A JP 2004119893 A JP2004119893 A JP 2004119893A JP 2005301095 A JP2005301095 A JP 2005301095A

- Authority

- JP

- Japan

- Prior art keywords

- signal

- gradation

- display

- video signal

- time ratio

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000011159 matrix material Substances 0.000 claims description 13

- 239000004973 liquid crystal related substance Substances 0.000 claims description 11

- 238000006243 chemical reaction Methods 0.000 claims description 8

- 238000012935 Averaging Methods 0.000 claims description 5

- 239000003990 capacitor Substances 0.000 description 11

- 238000010586 diagram Methods 0.000 description 8

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 7

- 230000001360 synchronised effect Effects 0.000 description 7

- 238000000034 method Methods 0.000 description 5

- 238000005070 sampling Methods 0.000 description 4

- 230000005525 hole transport Effects 0.000 description 3

- 238000002347 injection Methods 0.000 description 3

- 239000007924 injection Substances 0.000 description 3

- 230000006870 function Effects 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 230000000007 visual effect Effects 0.000 description 2

- 208000003443 Unconsciousness Diseases 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 230000004300 dark adaptation Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000020169 heat generation Effects 0.000 description 1

- 230000004301 light adaptation Effects 0.000 description 1

- 230000014759 maintenance of location Effects 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2018—Display of intermediate tones by time modulation using two or more time intervals

- G09G3/2022—Display of intermediate tones by time modulation using two or more time intervals using sub-frames

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2014—Display of intermediate tones by modulation of the duration of a single pulse during which the logic level remains constant

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2330/00—Aspects of power supply; Aspects of display protection and defect management

- G09G2330/02—Details of power systems and of start or stop of display operation

- G09G2330/021—Power management, e.g. power saving

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2360/00—Aspects of the architecture of display systems

- G09G2360/16—Calculation or use of calculated indices related to luminance levels in display data

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

- G09G3/3291—Details of drivers for data electrodes in which the data driver supplies a variable data voltage for setting the current through, or the voltage across, the light-emitting elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

Abstract

【解決手段】 1フレームの映像信号を1フレーム平均階調計算部5で求めた平均階調が一定値を越えると画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブル6の出力に基づいて表示手段1の画素の表示時間割合を制御する階調制御回路2を備える。表示時間割合テーブル6の出力信号に基づいて表示手段の画素に書き込まれた映像信号を消去することによって画素の表示時間を制御する。

平均階調が高い画像を表示すると、画面全体が明るく消費電力が上昇するが、1フレームの映像信号の平均階調がある一定値を越えると表示時間割合を下げることで消費電力をある一定値に抑えることができる。

【選択図】 図1

Description

EL素子は、一対の電極(陽極と陰極)間に発光層が挟まれる形で構成され、通常、積層構造を採用している。一例を挙げれば、「正孔輸送層・発光層・電子輸送層」という積層構造が挙げられる。また、これ以外にも、陽極上に「正孔注入層・正孔輸送層・発光層・電子輸送層」又は「正孔注入層・正孔輸送層・発光層・電子輸送層・電子注入層」の順に積層する構造のものも知られている(例えば、特許文献1参照)。

このLED表示装置の場合、階調表示は、発光データのパルス時間が全フィールドで等間隔であるため、階調数とフィールド数を等しくする必要があり、階調数を増やすためにはフィールド数を増やす必要があり、表示可能な階調数に限界があった。

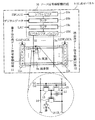

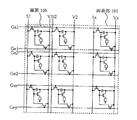

図23及び図24に示すように、EL表示装置は、基板上に形成されたTFT(薄膜トランジスタ)によってマトリクス状に配列された画素105を有する画素部101、画素部の周辺に配置されたソース信号線駆動回路102、書き込み用ゲート信号線駆動回路103、消去用ゲート信号線駆動回路104を有している。前記ソース信号線駆動回路102はシフトレジスタ102a、ラッチ102b、ラッチ102cを備えている。

前記スイッチング用TFT107のゲート電極は書き込み用ゲート信号線Gaに、ソース領域とドレイン領域は、一方がソース信号線Sに、他方がEL駆動用TFT108のゲート電極に、各画素が有するコンデンサ112及び消去用TFT109のソース領域又はドレイン領域にそれぞれ接続されている。ここでコンデンサ112はスイッチング用TFT107がオフ状態(非選択状態)にある時、EL駆動用TFT108のゲート電圧を保持するために設けられている。

前記書き込み用ゲート信号線駆動回路103から書き込み用選択信号が入力されると、1行目の書き込み用ゲート信号線Ga1に接続されている全ての画素のスイッチングTFT107がオン状態になる。同時にソース信号線S1〜Sxにラッチ102cからデジタル信号に変換された映像信号の1ビット目のデジタルデータ「0」又は「1」が入力される。このデジタルデータはスイッチング用TFTを介してEL駆動用TFT108のゲート電極に入力され、デジタルデータが「1」のときはEL駆動用TFT108はオンしてEL素子110は発光し、デジタルデータが「0」の時はEL駆動用TFT108はオフしてEL素子110は発光しないようになっている。

すると書き込み用ゲート信号線Ga2に接続されている全ての画素のスイッチング用TFT107がオン状態になり、2ライン目の画素にソース信号線S1〜Sxから1ビット目のデジタルデータが入力される。そして順次全ての書き込み用ゲート信号線(Ga1〜Gay)に書き込み用選択信号が入力されて全ての書き込み用ゲート信号線が選択され、全てのラインの画素に1ビット目のデジタルデータが入力されるまでの期間が書き込み期間Ta1である。

ここで、前記消去されてから画素が表示を行わない期間を図示のように非表示期間Tdであり、1行目の非表示期間はTd1である。

Tr1:Tr2:・・・Trn=20:21:・・・2(n-1)となるように設定する。この表示期間の組み合わせで2n階調のうち所望の階調表示を行うことができる。ここで1フレーム期間中にEL素子が発光した表示期間の総和を求めることによって、当該フレーム期間における画素の表示した階調が決まる。例えばn=8(256階調)の時、全部の表示期間で画素が発光した場合の輝度を100%とすると、Tr1とTr2において画素が発光した場合は1%の輝度が表現でき、Tr3とTr5とTr8を選択した場合は60%の輝度を表現できる。

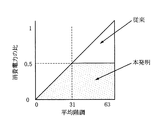

表示時間/(表示時間+非表示時間)=表示時間割合とし、最高階調での表示時間割合を表示時間割合の最高値とすると、図9に示すように階調を表現する際、表示時間割合の最高値を固定して階調表現を行っていると見ることができる。表示時間割合の最高値を固定すると、後述するように階調が増すにつれて表示手段(EL表示パネル)の消費電力の増大に繋がる。

また、図14(B)に示すように、階調を下げることで輝度を変えると表示階調数が減るることが実験的に分かった。図14(B)においてbitは階調レベル数に、dutyは前記表示時間割合に対応している。

ここで表示手段を構成する画素がELの場合は、ELは発光素子であるので、前記表示時間及び非表示時間は発光時間及び非発光時間と等価であるので図9では表示時間割合は発光時間割合である。

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段とを備える。

階調の制御を1フレームの映像信号の平均階調に応じて制御すると、表示時間割合を低減することができ、表示手段の消費電力が低減する。

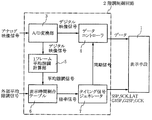

前記階調制御回路2は、アナログ映像信号をデジタル映像信号に変換するA/D変換部3、デジタル映像信号を取り込むデータコントローラ4、デジタル映像信号の各画素の階調を1フレーム分全画面で平均化した平均階調レベルを計算して平均階調信号を出力する1フレーム平均階調計算部5、平均階調信号を受けて後述する倍率信号を発生する表示時間割合テーブル6、該倍率信号が入力されるタイミング信号ジェネレータ7を備え、前記データコントローラ4の出力データ及びタイミング信号ジェネレータ7によって前記表示手段1の階調が制御される。

前記1フレーム平均階調計算部5は、デジタル映像信号の各画素の階調を1フレーム分全画面で平均化した平均階調を計算する。そして、後述するように全画素の階調の総和を加算器とメモリによって演算し、上位の数ビット、例えば上位4ビットを平均階調信号として出力する。前記1フレーム平均階調計算部5の回路例は後述する。

表1に示すテーブルに基づき前記1フレーム平均階調計算部5で計算した結果の上位の4ビットの入力に対して3ビットに変換して出力する。このテーブルの各欄において、階調は対象となる映像信号の1フレームの平均階調を示し、倍率は前記フレームメモリの保持時間の減衰率をそれぞれ示す。

また、前記表示手段は画素がEL素子や液晶で構成されデジタル映像信号又はアナログ映像信号が取り込まれて画像を表示する。

1フレーム期間において、表示時間/(表示時間+非表示時間)=表示時間割合とし、図8に示すように、階調と表示時間割合の関係を可変とし、最高階調での表示時間割合を低減させるものである。

前記テーブルは、表1に示す平均階調信号に応じて倍率を決め、その倍率によって階調と表示時間割合の関係を決定する。

ここで表示時間割合は前述したように、1フレーム期間において、表示時間/(表示時間+非表示時間)とする。

図5に示すように前記倍率は設計上の表示時間割合の最高値(図5では30.0%)を基準(倍率1.00倍)としている。この倍率信号は任意のビット数(テーブルでは3ビット)で表現する。

この倍率を使うことで、後述する消去開始信号発生回路(図3、図4)を用いて階調と倍率の関係から階調と表示時間割合の関係を調節する。

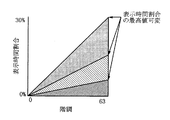

平均階調が高い画像を表示すると、画面全体が明るく消費電力が上昇する。この最高消費電力は平均階調が最高階調と同じ階調レベル(図7に示す例では0〜63階調の63階調)のときに発生する。ここで表示手段の製品の仕様の一つである消費電力や発熱量などは最高消費電力を基準として規定し、かつその条件での製品保証をしなければならない。 ところが実際の仕様条件では写真などの中間調の表示が多く、平均階調はそれほど高くならない。

例えば、図6に示すように、平均階調が0から31階調までは一定の表示時間割合(倍率1倍)とし、平均階調が31を越えて63階調では平均階調に応じて表示時間割合を減らす(倍率1倍から0.5倍まで、倍率=(0.5×63)/平均階調)ようにする。すると表示時間割合が低減されて表示手段は暗くなるため消費電力を一定値(従来例の0.5倍の消費電力)に抑えることができる。

図7には前記図6に示す平均階調と倍率との関係を使った場合の平均階調と表示手段の消費電力の関係を示している。

従来のように最高階調と表示時間割合(表示時間割合の最高値)の関係を固定すると、平均階調に比例して消費電力も増加する。もし最高消費電力が大きすぎるなら設計を変えてもっと暗い表示にする必要があるが、これでは平均階調が低く且つ一部に明るい発光の映像(例えば花火のような映像)も暗くなってしまう。

これに対し、本発明では平均階調が大きくなっても消費電力はある一定値に抑えることができる。そして、最高消費電力を抑えつつ、平均階調が低い映像での輝度を抑えることのない映像表現が可能となる。

図7では最高消費電力を従来の半分(0.5倍)に制限した場合を示したが、前記テーブルのデータを変えることで最高消費電力をさらに抑えることも可能である。

前記最高消費電力を従来のα倍(α≦1)とするには、平均階調が0から(α×最高階調)までは一定の表示割合(倍率1倍)とし、平均階調が(α×最高階調)を越えて最高階調までは、倍率=(α×最高階調)/平均階調となるようにすればよい。

なお、平均階調と倍率との関係は図6に示すものに限られるものではなく、例えば、平均階調が0から(α×最高階調)までは一定の表示割合(倍率1倍)とし、平均階調が(α×最高階調)を越えて最高階調までは、倍率=1+α−(平均階調/最高階調)としてもよい。

また、従来、液晶表示パネルでは、前記ブラウン管と同じ特性を得るためにバックライトの輝度を調節することで実現していた(例えば、特開2001−147667号公報参照)。しかしバックライトを高速に正確に制御することは困難であった。

従来の表示装置では最高階調と輝度の関係が固定であったため、明るい表示をしようとするとハイライト部分が白飛びを生じ、暗い表示をしようとすると影部分が潰れてしまう(黒潰れ)という問題があったが、前記テーブルを用いれば、階調と輝度の関係を平均階調によって動的に変化させることが可能なため、より人間の視覚特性に近いダイナミックレンジの広い表現が可能となる。例えば、ハイライト部分の表現力を高めたいなら前記倍率を1に近く設定し、影部分の表現力を高めたいなら前記倍率を低くすればよい。

前記テーブルを用いれば平均階調と表示時間割合の関係を変えることで輝度調節ができるので、デジタル処理を採用すると高速、正確且つ簡単に輝度調節が可能となる。

従来は図14(B)に示すように輝度を調節するために階調を下げると表示階調数が減ったが、本発明では図14(A)の本発明の実験データが示すように、前記テーブルに基づいて平均階調と表示時間割合の関係を変えることで輝度を調節すると表示階調数を維持したまま暗くすることが可能となる。

平均階調はデジタル映像信号の1フレーム全画素の累積階調から求められる。図2に示すように、1フレーム平均階調計算部5は加算器5aと累算器5bとから構成されている。

前記加算器5aにはデジタル映像信号と前記累算器5bの出力とが入力され、これら入力の和が前記累算器5bに入力される。

前記累算器5bはデジタル映像信号と同期したクロックのタイミングで前記加算器5aの出力を記録し、1フレームと同期したリセット信号によって初期化される。

前記累算器5bの記録するビット数は、デジタル映像信号のビット数と表示手段の画素数によって決定する。例えば、デジタル映像信号を6ビット、表示手段の画素数が320×240×3=230400画素<218のとき、6+18=24ビット記録できる累算器を利用する。

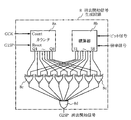

図3に示すように消去開始信号生成回路8は、カウンタ8aと積算器8bとEXNOR回路8cとAND回路8dで構成される。

前記カウンタ8aは、画素への書き込み走査開始信号G1SPをリセット信号として書き込みクロックGCKをカウントする。前記カウンタ8aの出力は前記G1SPが入力されてからの経過時間に比例する。

そして、前記積算器8bの出力は前記サブフレームSF1〜SF6の各サブフレームでの重みと倍率信号の積となる。

このように、前記各サブフレームでの重みと倍率信号の積により前記消去開始信号G2SPが生成されるタイミングを制御して画素の表示時間割合を制御する。

図12のタイミングチャートに示すように、1秒間の映像信号60フレーム中のそれぞれのフレームを、図示の例では第4フレームを複数のサブフレーム、例えば前記消去開始信号生成回路で説明したように6個のサブフレームSF1〜SF6に分割されている。

そして、前記各サブフレームSF1〜SF6において、書き込み開始信号G1SPと消去開始信号G2SPとの間隔(図12ではサブフレームSF2のみ例として示している)の比が2の階乗となるとき、階調ビット数はサブフレームの数と同じ6ビットとなり、表示階調レベル数が26=64となる。ここでサブフレームを増やすとそれだけ表示階調数が大きくなり、サブフレームの数をnとすれば、表示階調数は2n階調となり、前記テーブルの表示階調数は前記サブフレームの数を増やすことで変更することができる。

実施例の欄で説明するように、図1に示す表示手段はゲート信号線を選択するゲート信号線駆動回路及び選択されたゲート信号線に接続された画素に映像信号を供給するソース信号線駆動回路を有している。

ゲート信号線駆動回路のタイミング信号は、例えばタイミングチャートに一例として示す第2のサブフレームSF2について見ると、G1SPを書き込み走査開始信号としてクロックGCKに同期して画素アレイを一行目から最終行まで順次走査する。その後、クロックGCKに同期して前記G2SPを消去開始信号として画素アレイを一行目から最終行まで順次走査して非表示状態とする。

先に、消去開始信号G2SPの生成回路(図3)で説明したように、前記各サブフレームSF1〜SF6での重みと前記テーブルの倍率の積により消去開始信号G2SPが生成されるようにしたから、該消去開始信号G2SPが発生するタイミングを前記テーブルに基づいて制御することで、平均階調がある一定値を越えて表示時間割合の最高値を下げること(図6、図8)が可能となり、図7に示すように最高消費電力をある一定値に抑えることができ、表示手段の消費電力を低減することができる。

前記ソース信号線駆動回路10は、シフトレジスタ10a、ラッチ10b、ラッチ10c、レベルシフタ・バッファ10dを備え、ゲート信号線駆動回路11及び12はそれぞれシフトレジスタ11a、12aを備えている。

前記書き込みスイッチング用TFT13のゲート電極は書き込み用ゲート信号線G1に、ソース領域とドレイン領域は、一方がソース信号線Sに、他方が前記EL駆動用TFT14のゲート電極に接続されている。

さらに、前記書き込みスイッチング用TFT13は各画素が有するコンデンサ17及び前記消去用TFT15のソース領域又はドレイン領域にそれぞれ接続されている。

ここで前記コンデンサ17は前記書き込みスイッチング用TFT13がオフ状態(非選択状態)にある時、前記EL駆動用TFT14のゲート電圧を保持するために設けられている。

前記ソース信号線駆動回路10のシフトレジスタ10aは同期信号SCKに同期する走査開始信号SSPによって走査を開始するとソース信号線S1〜Snに対応するラッチ10bに前記データコントローラ4(図1)のフレームメモリに保持されているデジタル映像信号の一行分が取り込まれる。前記ラッチ10bに取り込まれたデジタル映像信号はラッチ信号LATが前記ラッチ10cに入力されて該ラッチ10cにラッチされるとともに前記レベルシフタ・バッファ10dで増幅されて前記ソース信号線S1〜Snに順次出力される。

前記書き込み用ゲート信号線が順次選択されると、選択された各書き込み用ゲート信号線の選択期間内にソース信号線S1〜Snから選択された前記書き込み用ゲート信号線に接続された画素に1行分ずつのデジタルデータが入力される。

前記書き込み用ゲート線駆動回路11に走査開始信号G1SPが入力されると、1行目の書き込み用ゲート信号線G11に接続されている全ての画素の書き込みスイッチングTFT13がオン状態になる。同時にソース信号線S1〜Snに前記ラッチ10cからデジタル映像信号の2ビット目のデジタルデータ「0」又は「1」が入力される。このデジタルデータは前記書き込みスイッチング用TFT13を介して前記EL駆動用TFT14のゲート電極に入力され、デジタルデータが「1」のときは前記EL駆動用TFT14はオンしてELは発光し、デジタルデータが「0」のときは前記EL駆動用TFT14はオフしてELは非発光になっている。

このように1行目に前記デジタルデータが入力されると、ELが発光または非発光を行い、1行目の画素は表示を行う。

次に、2行目の消去用ゲート信号線G22が選択されると、該消去用ゲート信号線G22に接続されている全ての画素の消去用TFT15がオンして、EL駆動用TFT14のソース領域とゲート電極が同電位となって前記EL駆動用TFT14はオフする。そして、順次全ての消去用ゲート信号線(G21〜G2m)が順次選択されて、サブフレームSF2において全ての行のELが順次非発光状態となる。

このように、各サブフレームにおける発光時間を前記テーブルが出力する倍率信号に基づいて制御すると、発光時間割合の最高値を低減することができるため、前記EL表示パネル9で消費される電力を低減することができる。

例えば、1フレームがn個のサブフレームで成るとき、前記選択された異なる任意の発光時間をそれぞれ20〜2n-1とすることで任意の2n階調の表示を行うことができる。

映像信号がアナログ信号の場合は、図1に示すブロック図において、データコントローラ4の内部に、前記A/D変換部3でデジタル信号に変換された映像信号をアナログ信号に変換するD/A変換部を設け、その他の構成要素はそのまま利用することができる。

そこで、前記表1に示すテーブルの倍率信号を利用するため、予め消去開始信号GSPを生成する消去開始信号発生回路を図4を参照しながら説明する。

図4に示すように消去開始信号生成回路は、カウンタ8aと積算器8bとEXNOR回路8cとAND回路8dとOR回路8eで構成されている。

前記カウンタ8aは画素への書き込み走査開始信号G1SPをリセット信号として書き込みクロックGCK(後述する図13に示すタイミングチャート)をカウントする。前記カウンタ8aの出力は前記書き込み走査開始信号G1SPが入力されてからの経過時間に比例する。

そして、前記G2SP及びG1SPをOR回路8eに入力して該OR回路8eの出力GSPを書き込み走査開始信号G1SP及び消去開始信号G2SPとして利用する。

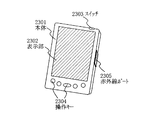

図11に示すように、アナログ信号入力アクティブマトリクス型のEL表示パネルは、マトリクス状に配列された画素18aを有する画素部18、該画素部18の周辺に配置されたソース信号線駆動回路19、ゲート信号線駆動回路20を有している。前記ソース信号線駆動回路19はシフトレジスタ19a、該シフトレジスタ19aの出力に基づいてアナログ映像信号をサンプリングするサンプリングスイッチSW1〜SWnを備え、前記ゲート信号線駆動回路20はシフトレジスタ20aを有している。

前記スイッチング用TFT21のゲート電極はゲート信号線Gに、ソース領域とドレイン領域は、一方がソース信号線Sに、他方がEL駆動用TFT22のゲート電極及びコンデンサ24にそれぞれ接続されている。

ここで前記コンデンサ24はスイッチング用TFT21がオフ状態(非選択状態)にある時、EL駆動用TFT22のゲート電圧を保持するために設けられている。

前記EL駆動用TFT22のソース領域とドレイン領域は、一方が電源供給線Vに接続され、他方はEL23のアノードに接続され、さらに電源供給線Vは前記コンデンサ24に接続されている。

前記ソース信号線駆動回路19のシフトレジスタ19aは同期信号SCKに同期した走査開始信号SSPが入力されると、ソース信号線S1〜Snに対応するサンプリングスイッチSW1〜SWnを順次選択する。前記シフトレジスタ19aによって選択されたサンプリングスイッチに対応するソース信号線S1〜Snに映像データが取り込まれる。

前記ゲート信号線駆動回路20に書き込み走査開始信号G1SPが入力されると、1行目のゲート信号線G1に接続されている全ての画素のスイッチングTFT21がオン状態になると同時にソース信号線S1〜Snからの映像信号がEL駆動用TFT22のゲート電極に入力され、映像信号に応じて一行目の各EL23は発光又は非発光を行い、1行目の画素は表示を行う。そして、全てのゲート信号線(G1〜Gm)が順次選択されて、全ての行の画素に映像信号のデータが入力される。

そして、前記倍率信号によって発生するタイミングが制御された消去開始信号G2SPを消去走査開始信号としてゲート信号線G1〜Gmを順次選択し、各ゲート信号線の選択期間内にソース信号線S1〜Snを順次選択し、且つ前記消去電位が入力され、ゲート信号線とソース信号線に選択された画素の映像信号が消去される。

このように前記テーブルの倍率信号に基づくタイミングで生成された消去開始信号G2SPを走査開始信号として画素に入力し、当該画素の有するEL23に供給されたアナログ映像信号を消去することで前記発光時間割合を制御することができる。

液晶を画素とする表示パネルは電圧駆動であるため、表示パネルに対応した電圧値にD/A変換して前記ソース信号線駆動回路19に取り込むことで、前記EL素子を液晶素子に代えて前記階調制御回路を用いることで同様に実施することができる。

本発明の表示装置を用いると、EL表示装置ではバックライトの必要がなく、また、液晶表示装置では、階調の制御にバックライトの輝度調整を必要としなくなる。この表示装置は、コンピュータ用、TV放送受信用、広告表示用等の全ての情報表示用表示装置に利用することができる。

充電型の電源を使用した場合、表示部の消費電力を低減できるため電源の長時間維持が可能となる。

充電型の電源を使用した場合、表示部の消費電力を低減できるため電源の長時間維持が可能となる。

充電型の電源を使用した場合、表示部の消費電力を低減できるため電源の長時間維持が可能となる。

充電型の電源を使用した場合、表示部の消費電力を低減できるため電源の長時間維持が可能となる。

充電型の電源を使用した場合、表示部の消費電力を低減できるため電源の長時間維持が可能となる。

Claims (18)

- 1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備えることを特徴とする表示装置。 - 1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備え、

前記表示時間割合テーブルの出力信号に基づいて前記表示手段の画素に書き込まれた映像信号を消去することによって階調を制御することを特徴とする表示装置。 - 1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調が一定値を越えると画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備えることを特徴とする表示装置。 - 1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調が一定値を越えると画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備え、

前記表示時間割合テーブルの出力信号に基づいて前記表示手段の画素に書き込まれた映像信号を消去することによって階調を制御することを特徴とする表示装置。 - 前記表示時間割合テーブルは、前記平均階調が一定値を越えると表示時間割合を低減する倍率信号を発生することを特徴とする請求項1、2、3又は4の表示装置。

- 前記表示時間割合テーブルは、前記平均階調が一定値を越えると表示時間割合を低減する倍率信号を発生し、該倍率信号に応じて前記表示手段の画素に書き込まれた映像信号を消去することを特徴とする請求項1、2、3又は4の表示装置。

- 1フレームのアナログ映像信号をデジタル映像信号に変換してデジタル映像信号を出力するA/D変換部と、

前記デジタル映像信号を取り込んで信号処理を行い、表示手段に前記デジタル映像信号を出力するデータコントローラと、

前記A/D変換部からのデジタル映像信号の各画素の階調を1フレーム分全画面で平均化した平均階調を求めて平均階調信号を出力する平均階調計算部と、

前記平均階調計算部からの平均階調信号を受けて、該平均階調が一定値を越えると表示時間割合を低減する倍率信号を出力する表示時間割合テーブルと、

前記倍率信号を受けて表示手段の画素に書き込まれた映像信号を消去する消去開始信号を生成するタイミングジェネレータと

を備えることを特徴とする表示装置。 - 1フレームのアナログ映像信号をデジタル映像信号に変換してデジタル映像信号を出力するA/D変換部と、

前記デジタル映像信号を取り込んで信号処理を行い、該デジタル映像信号をアナログ映像信号に変換して表示手段に前記アナログ映像信号を出力するデータコントローラと、

前記A/D変換部からのデジタル映像信号の各画素の階調を1フレーム分全画面で平均化した平均階調を求めて平均階調信号を出力する平均階調計算部と、

前記平均階調計算部からの平均階調信号を受けて、該平均階調が一定値を越えると表示時間割合を低減する倍率信号を出力する表示時間割合テーブルと、

前記倍率信号を受けて表示手段の画素に書き込まれた映像信号を消去する消去開始信号を生成するタイミングジェネレータと

を備えることを特徴とする表示装置。 - 前記表示手段は、画素がマトリクス状に配列されたEL素子でなることを特徴とする請求項1、2、3、4、5、6、7又は8の表示装置。

- 前記表示手段は、画素がマトリクス状に配列された液晶素子でなることを特徴とする請求項1、2、3、4、5、6、7又は8の表示装置。

- ソース信号線駆動回路と、第1のゲート信号線駆動回路と、第2のゲート信号線駆動回路と、画素部と、前記ソース信号線駆動回路に接続された複数のソース信号線と、前記第1のゲート信号線駆動回路に接続された複数の第1のゲート信号線と、前記第2のゲート信号線駆動回路に接続された複数の第2のゲート信号線と、電源供給線とを有し、

前記画素部は複数の画素を有しており、

前記複数の画素は、スイッチング用トランジスタ、EL駆動用トランジスタ、消去用トランジスタ及びEL素子をそれぞれ有しており、

前記スイッチング用トランジスタのゲート電極は前記第1のゲート信号線と接続されており、

前記スイッチング用トランジスタが有するソース領域とドレイン領域は、一方は前記複数のソース信号線と、他方は前記EL駆動用トランジスタが有するゲート電極と接続されており、

前記消去用トランジスタが有するゲート電極は前記第2のゲート信号線と接続されており、

前記消去用トランジスタが有するソース領域とドレイン領域は、一方は前記電源供給線と、他方は前記EL駆動用トランジスタが有するゲート電極と接続されており、

前記EL駆動用トランジスタが有するソース領域とドレイン領域は、一方は前記電源供給線に、他方は前記EL素子に接続されてなるアクティブマトリクス型表示手段と、

1フレームのアナログ映像信号をデジタル映像信号に変換してデジタル映像信号を出力するA/D変換部と、

前記デジタル映像信号を取り込んで信号処理を行い、表示手段に前記デジタル映像信号を出力するデータコントローラと、

前記A/D変換部からのデジタル映像信号の各画素の階調を1フレーム分全画面で平均化した平均階調を求めて平均階調信号を出力する平均階調計算部と、

前記平均階調計算部からの平均階調信号を受けて、該平均階調が一定値を越えると映像信号の表示時間割合を低減する倍率信号を出力する表示時間割合テーブルと、

前記倍率信号を受けて表示手段の画素に書き込まれた映像信号を消去する消去開始信号を生成するタイミングジェネレータと

を有する階調制御回路と

を備え、

前記消去開始信号を前記第2のゲート信号線駆動回路に供給して前記画素に書き込まれた映像信号を消去することを特徴とする表示装置。 - ソース信号線駆動回路と、ゲート信号線駆動回路と、画素部と、前記ソース信号線駆動回路に接続された複数のソース信号線と、前記ゲート信号線駆動回路に接続された複数のゲート信号線と、電源供給線とを有し、

前記画素部は複数の画素を有しており、

前記複数の画素は、スイッチング用トランジスタ、EL駆動用トランジスタ及びEL素子をそれぞれ有しており、

前記スイッチング用トランジスタのゲート電極は前記ゲート信号線と接続されており、

前記スイッチング用トランジスタが有するソース領域とドレイン領域は、一方は前記複数のソース信号線と、他方は前記EL駆動用トランジスタが有するゲート電極と接続されており、

前記EL駆動用トランジスタが有するソース領域とドレイン領域は、一方は前記電源供給線に、他方は前記EL素子に接続されてなるアクティブマトリクス型表示手段と、

1フレームのアナログ映像信号をデジタル映像信号に変換してデジタル映像信号を出力するA/D変換部と、

前記デジタル映像信号を取り込んで信号処理を行い、表示手段にアナログ映像信号を出力するデータコントローラと、

前記A/D変換部からのデジタル映像信号の各画素の階調を1フレーム分全画面で平均化した平均階調を求めて平均階調信号を出力する平均階調計算部と、

前記平均階調計算部からの平均階調信号を受けて、該平均階調が一定値を越えると表示時間割合を低減する倍率信号を出力する表示時間割合テーブルと、

前記倍率信号を受けて表示手段の画素に書き込まれた映像信号を消去する消去開始信号を生成するタイミングジェネレータと

を有する階調制御回路と

を備え、

前記消去開始信号を前記ゲート信号線駆動回路に供給して前記画素に書き込まれた映像信号を消去することを特徴とする表示装置。 - 請求項1、2、3、4、5、6、7、8、9、10、11又は12に記載の表示装置において、1フレームの映像信号を複数のサブフレームに分割し、サブフレーム毎に前記表示時間割合を制御して時分割階調表示を行うことを特徴とする表示装置。

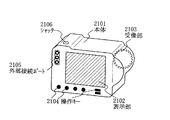

- 1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備えることを特徴とするデジタルスチルカメラ。 - 1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備えることを特徴とするコンピュータ。 - 1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備えことを特徴とする画像再生装置。 - 1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備えることを特徴とするビデオカメラ。 - 1フレームの映像信号の平均階調を求める平均階調計算手段と、

前記平均階調に基づいて画素の表示時間割合を低減するための階調制御信号を出力する表示時間割合テーブルと、

前記表示時間割合テーブルの出力に基づいて前記画素の階調が制御される表示手段と

を備えることを特徴とする携帯電話。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004119893A JP2005301095A (ja) | 2004-04-15 | 2004-04-15 | 表示装置 |

| US11/100,898 US7460137B2 (en) | 2004-04-15 | 2005-04-07 | Display device |

| CNB2005100666244A CN100485760C (zh) | 2004-04-15 | 2005-04-14 | 显示器件 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004119893A JP2005301095A (ja) | 2004-04-15 | 2004-04-15 | 表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005301095A true JP2005301095A (ja) | 2005-10-27 |

| JP2005301095A5 JP2005301095A5 (ja) | 2007-05-10 |

Family

ID=35095788

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004119893A Withdrawn JP2005301095A (ja) | 2004-04-15 | 2004-04-15 | 表示装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7460137B2 (ja) |

| JP (1) | JP2005301095A (ja) |

| CN (1) | CN100485760C (ja) |

Cited By (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006285235A (ja) * | 2005-03-31 | 2006-10-19 | Samsung Sdi Co Ltd | 発光表示装置及びその駆動方法 |

| JP2007147867A (ja) * | 2005-11-25 | 2007-06-14 | Sony Corp | 自発光表示装置、発光条件制御装置、発光条件制御方法及びプログラム |

| WO2008013201A1 (fr) * | 2006-07-25 | 2008-01-31 | Sony Corporation | Dispositif de régulation de puissance consommée, dispositif de traitement d'image, dispositif d'affichage auto-émetteur, dispositif électronique, procédé de régulation de puissance consommée et programme d'ordinateur |

| JP2008026762A (ja) * | 2006-07-25 | 2008-02-07 | Sony Corp | 発光条件制御装置、画像処理装置、自発光表示装置、電子機器、発光条件制御方法及びコンピュータプログラム |

| KR100858614B1 (ko) | 2007-03-08 | 2008-09-17 | 삼성에스디아이 주식회사 | 유기전계발광표시장치 및 그의 구동방법 |

| JP2008257171A (ja) * | 2007-04-05 | 2008-10-23 | Samsung Sdi Co Ltd | 有機電界発光表示装置及び映像補正方法 |

| WO2008143208A1 (ja) * | 2007-05-18 | 2008-11-27 | Sony Corporation | 表示装置、映像信号処理方法、およびプログラム |

| WO2008146742A1 (ja) * | 2007-05-25 | 2008-12-04 | Sony Corporation | 表示装置、映像信号処理方法、およびプログラム |

| WO2009008418A1 (ja) * | 2007-07-11 | 2009-01-15 | Sony Corporation | 表示装置、映像信号処理方法、およびプログラム |

| JP2009271493A (ja) * | 2008-05-09 | 2009-11-19 | Samsung Mobile Display Co Ltd | 有機電界発光表示装置及びその駆動方法 |

| JP2010156974A (ja) * | 2008-12-30 | 2010-07-15 | Samsung Electronics Co Ltd | 能動型有機発光ダイオードの電力制御方法及びその装置 |

| US9123284B2 (en) | 2008-05-23 | 2015-09-01 | Semiconductor Energy Laboratory Co., Ltd. | Display device having backlight |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20070029940A1 (en) * | 2005-06-16 | 2007-02-08 | Toshiba Matsushita Display Technology Co., Ltd | Driving method of display device using organic self-luminous element and driving circuit of same |

| JP4899447B2 (ja) * | 2005-11-25 | 2012-03-21 | ソニー株式会社 | 自発光表示装置、発光条件制御装置、発光条件制御方法及びプログラム |

| JP2007156045A (ja) * | 2005-12-05 | 2007-06-21 | Sony Corp | 自発光表示装置、消費電力検出装置及びプログラム |

| JP4238913B2 (ja) * | 2006-12-19 | 2009-03-18 | ソニー株式会社 | 表示装置の温度制御方法及び表示装置 |

| WO2008153055A1 (ja) * | 2007-06-13 | 2008-12-18 | Sony Corporation | 表示装置、映像信号処理方法、およびプログラム |

| KR101467496B1 (ko) * | 2008-09-11 | 2014-12-01 | 삼성디스플레이 주식회사 | 표시장치 및 이의 구동방법 |

| US20120022711A1 (en) * | 2009-12-10 | 2012-01-26 | Keiji Sakaguchi | Power information collecting apparatus, power measuring apparatus, power information collecting system, and power information collecting method |

| US20180061300A1 (en) * | 2016-08-31 | 2018-03-01 | Shenzhen China Star Optoelectronics Technology Co., Ltd. | Oled-pwm driving method |

| CN107613385B (zh) * | 2017-09-21 | 2018-05-01 | 高雪亚 | 一种预防儿童近视的平台 |

| US11087660B2 (en) * | 2018-10-03 | 2021-08-10 | Himax Technologies Limited | Timing controller and operating method thereof |

| CN113450719A (zh) | 2020-03-26 | 2021-09-28 | 聚积科技股份有限公司 | 扫描式显示器的驱动方法及其驱动装置 |

| US11348543B2 (en) | 2020-03-26 | 2022-05-31 | Macroblock, Inc. | Scan-type display apparatus, and driving device and driving method thereof |

| CN113450723A (zh) | 2020-03-26 | 2021-09-28 | 聚积科技股份有限公司 | 扫描式显示器及其驱动装置与驱动方法 |

| US11355057B2 (en) | 2020-03-26 | 2022-06-07 | Macroblock, Inc. | Scan-type display apparatus and driving device thereof |

| US11568793B2 (en) | 2020-03-26 | 2023-01-31 | Macroblock, Inc. | Scan-type display apparatus, and driving device and driving method thereof |

| CN113450721A (zh) * | 2020-03-26 | 2021-09-28 | 聚积科技股份有限公司 | 扫描式显示器及其驱动装置与驱动方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001060076A (ja) * | 1999-06-17 | 2001-03-06 | Sony Corp | 画像表示装置 |

| JP2001343933A (ja) * | 1999-11-29 | 2001-12-14 | Semiconductor Energy Lab Co Ltd | 発光装置 |

| WO2003091979A1 (fr) * | 2002-04-26 | 2003-11-06 | Toshiba Matsushita Display Technology Co., Ltd. | Procede de commande d'un dispositif d'affichage el |

| JP2004062134A (ja) * | 2002-06-03 | 2004-02-26 | Sharp Corp | 液晶表示装置 |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS59125176A (ja) * | 1982-12-30 | 1984-07-19 | インタ−ナシヨナル ビジネス マシ−ンズ コ−ポレ−シヨン | ビデオイメ−ジのシエ−ジング効果の補正装置 |

| US5247154A (en) * | 1991-01-17 | 1993-09-21 | Westinghouse Electric Corp. | Method and apparatus for monitoring the laser marking of a bar code label |

| JPH05341728A (ja) | 1992-06-11 | 1993-12-24 | Toshiba Corp | Led表示モジュール |

| US5351201A (en) * | 1992-08-19 | 1994-09-27 | Mtl Systems, Inc. | Method and apparatus for automatic performance evaluation of electronic display devices |

| US5572444A (en) * | 1992-08-19 | 1996-11-05 | Mtl Systems, Inc. | Method and apparatus for automatic performance evaluation of electronic display devices |

| EP0617312B1 (en) * | 1993-03-26 | 2002-10-02 | Matsushita Electric Industrial Co., Ltd. | A spatial light modulator and a method for driving the same |

| US5516572A (en) * | 1994-03-18 | 1996-05-14 | The Procter & Gamble Company | Low rewet topsheet and disposable absorbent article |

| US5910793A (en) * | 1996-11-01 | 1999-06-08 | Rockwell International Corporation | Method and apparatus for enhancing the select/nonselect ratio of a liquid crystal display |

| US7012600B2 (en) * | 1999-04-30 | 2006-03-14 | E Ink Corporation | Methods for driving bistable electro-optic displays, and apparatus for use therein |

| JP2001147667A (ja) | 1999-11-18 | 2001-05-29 | Hitachi Ltd | 液晶モニタ装置 |

| US6670983B2 (en) * | 2000-02-07 | 2003-12-30 | Fuji Photo Optical Co., Ltd. | Electric mask generating apparatus of electronic endoscope |

| US6633343B2 (en) * | 2000-03-14 | 2003-10-14 | Matsushita Electric Industrial Co., Ltd. | Dynamic gamma correction apparatus |

| TW518555B (en) * | 2000-04-21 | 2003-01-21 | Matsushita Electric Ind Co Ltd | Gray-scale image display device that can reduce power consumption when writing data |

| JP3796654B2 (ja) * | 2001-02-28 | 2006-07-12 | 株式会社日立製作所 | 表示装置 |

| JP3788916B2 (ja) * | 2001-03-30 | 2006-06-21 | 株式会社日立製作所 | 発光型表示装置 |

| US20020145584A1 (en) * | 2001-04-06 | 2002-10-10 | Waterman John Karl | Liquid crystal display column capacitance charging with a current source |

| JP4416959B2 (ja) | 2001-04-26 | 2010-02-17 | 富士通マイクロエレクトロニクス株式会社 | Xyアドレス型固体撮像装置のフリッカノイズ低減方法 |

| WO2003044765A2 (en) | 2001-11-20 | 2003-05-30 | E Ink Corporation | Methods for driving bistable electro-optic displays |

| US7528822B2 (en) * | 2001-11-20 | 2009-05-05 | E Ink Corporation | Methods for driving electro-optic displays |

| JP2003330420A (ja) * | 2002-05-16 | 2003-11-19 | Semiconductor Energy Lab Co Ltd | 発光装置の駆動方法 |

| US6995774B2 (en) * | 2002-07-10 | 2006-02-07 | L3 Communications Corporation | Display system and method of diminishing unwanted artifacts |

| US7027054B1 (en) * | 2002-08-14 | 2006-04-11 | Avaworks, Incorporated | Do-it-yourself photo realistic talking head creation system and method |

| US7397485B2 (en) * | 2002-12-16 | 2008-07-08 | Eastman Kodak Company | Color OLED display system having improved performance |

| US20070200803A1 (en) * | 2005-07-27 | 2007-08-30 | Semiconductor Energy Laboratory Co., Ltd. | Display device, and driving method and electronic device thereof |

-

2004

- 2004-04-15 JP JP2004119893A patent/JP2005301095A/ja not_active Withdrawn

-

2005

- 2005-04-07 US US11/100,898 patent/US7460137B2/en not_active Expired - Fee Related

- 2005-04-14 CN CNB2005100666244A patent/CN100485760C/zh not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001060076A (ja) * | 1999-06-17 | 2001-03-06 | Sony Corp | 画像表示装置 |

| JP2001343933A (ja) * | 1999-11-29 | 2001-12-14 | Semiconductor Energy Lab Co Ltd | 発光装置 |

| WO2003091979A1 (fr) * | 2002-04-26 | 2003-11-06 | Toshiba Matsushita Display Technology Co., Ltd. | Procede de commande d'un dispositif d'affichage el |

| JP2004062134A (ja) * | 2002-06-03 | 2004-02-26 | Sharp Corp | 液晶表示装置 |

Cited By (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006285235A (ja) * | 2005-03-31 | 2006-10-19 | Samsung Sdi Co Ltd | 発光表示装置及びその駆動方法 |

| JP2007147867A (ja) * | 2005-11-25 | 2007-06-14 | Sony Corp | 自発光表示装置、発光条件制御装置、発光条件制御方法及びプログラム |

| US9548017B2 (en) | 2006-07-25 | 2017-01-17 | Joled Inc. | Power consumption controller, image processor, self-luminous display apparatus, electronic equipment, power consumption control method and computer program |

| US9330594B2 (en) | 2006-07-25 | 2016-05-03 | Joled Inc. | Power consumption controller, image processor, self-luminous display apparatus, elelcrtonic equipment, power consumption control method and computer program |

| JP2008026762A (ja) * | 2006-07-25 | 2008-02-07 | Sony Corp | 発光条件制御装置、画像処理装置、自発光表示装置、電子機器、発光条件制御方法及びコンピュータプログラム |

| JP2008026761A (ja) * | 2006-07-25 | 2008-02-07 | Sony Corp | 消費電力制御装置、画像処理装置、自発光表示装置、電子機器、消費電力制御方法及びコンピュータプログラム |

| WO2008013201A1 (fr) * | 2006-07-25 | 2008-01-31 | Sony Corporation | Dispositif de régulation de puissance consommée, dispositif de traitement d'image, dispositif d'affichage auto-émetteur, dispositif électronique, procédé de régulation de puissance consommée et programme d'ordinateur |

| KR100858614B1 (ko) | 2007-03-08 | 2008-09-17 | 삼성에스디아이 주식회사 | 유기전계발광표시장치 및 그의 구동방법 |

| US8274453B2 (en) | 2007-03-08 | 2012-09-25 | Samsung Mobile Display Co., Ltd. | Organic electro luminescence display and driving method of the same |

| JP2008257171A (ja) * | 2007-04-05 | 2008-10-23 | Samsung Sdi Co Ltd | 有機電界発光表示装置及び映像補正方法 |

| US9035856B2 (en) | 2007-04-05 | 2015-05-19 | Samsung Display Co., Ld. | Organic light emitting display, and image modification method |

| US8947330B2 (en) | 2007-05-18 | 2015-02-03 | Sony Corporation | Display device, picture signal processing method, and program |

| KR101489016B1 (ko) * | 2007-05-18 | 2015-02-02 | 소니 주식회사 | 표시 장치, 영상 신호 처리 방법, 및 기록 매체 |

| US8654044B2 (en) | 2007-05-18 | 2014-02-18 | Sony Corporation | Display device, picture signal processing method, and program |

| JP5304646B2 (ja) * | 2007-05-18 | 2013-10-02 | ソニー株式会社 | 表示装置、映像信号処理方法、およびプログラム |

| US8471790B2 (en) | 2007-05-18 | 2013-06-25 | Sony Corporation | Display device, picture signal processing method, and program |

| WO2008143208A1 (ja) * | 2007-05-18 | 2008-11-27 | Sony Corporation | 表示装置、映像信号処理方法、およびプログラム |

| US8294642B2 (en) | 2007-05-25 | 2012-10-23 | Sony Corporation | Display device, picture signal processing method, and program |

| CN101681591B (zh) * | 2007-05-25 | 2012-07-18 | 索尼株式会社 | 显示设备及影像信号处理方法 |

| JP5321455B2 (ja) * | 2007-05-25 | 2013-10-23 | ソニー株式会社 | 表示装置、映像信号処理方法、およびプログラム |

| KR101471225B1 (ko) * | 2007-05-25 | 2014-12-09 | 소니 주식회사 | 표시 장치, 영상 신호 처리 방법 및 기록 매체 |

| WO2008146742A1 (ja) * | 2007-05-25 | 2008-12-04 | Sony Corporation | 表示装置、映像信号処理方法、およびプログラム |

| WO2009008418A1 (ja) * | 2007-07-11 | 2009-01-15 | Sony Corporation | 表示装置、映像信号処理方法、およびプログラム |

| US8514154B2 (en) | 2007-07-11 | 2013-08-20 | Sony Corporation | Display device, picture signal processing method, and program |

| JP5316408B2 (ja) * | 2007-07-11 | 2013-10-16 | ソニー株式会社 | 表示装置、映像信号処理方法、およびプログラム |

| CN101960508B (zh) * | 2007-07-11 | 2013-07-31 | 索尼公司 | 显示设备、影像信号处理方法 |

| CN101960508A (zh) * | 2007-07-11 | 2011-01-26 | 索尼公司 | 显示设备、影像信号处理方法和程序 |

| US8154482B2 (en) | 2008-05-09 | 2012-04-10 | Samsung Mobile Display Co., Ltd. | Organic light emitting display and method for driving the same |

| JP2009271493A (ja) * | 2008-05-09 | 2009-11-19 | Samsung Mobile Display Co Ltd | 有機電界発光表示装置及びその駆動方法 |

| US9123284B2 (en) | 2008-05-23 | 2015-09-01 | Semiconductor Energy Laboratory Co., Ltd. | Display device having backlight |

| US8730271B2 (en) | 2008-12-30 | 2014-05-20 | Samsung Electronics Co., Ltd. | Method and device for controlling power of active matrix organic light-emitting diode |

| US9514675B2 (en) | 2008-12-30 | 2016-12-06 | Samsung Electronics Co., Ltd. | Method and device for controlling power of active matrix organic light-emitting diode |

| JP2010156974A (ja) * | 2008-12-30 | 2010-07-15 | Samsung Electronics Co Ltd | 能動型有機発光ダイオードの電力制御方法及びその装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US7460137B2 (en) | 2008-12-02 |

| CN1684131A (zh) | 2005-10-19 |

| CN100485760C (zh) | 2009-05-06 |

| US20050231449A1 (en) | 2005-10-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7460137B2 (en) | Display device | |

| JP4642094B2 (ja) | 発光装置及び電子機器 | |

| KR100905270B1 (ko) | 신호선 구동회로 및 발광장치 | |

| JP4024557B2 (ja) | 発光装置、電子機器 | |

| KR100857517B1 (ko) | 유기 el 장치, 회로, 유기 el 장치의 구동 방법 및 전자 기기 | |

| KR100914186B1 (ko) | 신호선 구동회로, 발광장치 및 그 구동방법 | |

| KR100991444B1 (ko) | 표시장치 및 표시장치의 구동방법 | |

| JP4352893B2 (ja) | 電子装置の駆動方法、電子装置、半導体集積回路及び電子機器 | |

| JP2003271099A (ja) | 表示装置および表示装置の駆動方法 | |

| KR20020082114A (ko) | 표시장치 및 표시장치 구동방법 | |

| US20100039356A1 (en) | Driving Method of Display Device | |

| JP2007293264A (ja) | 電気光学装置及びその駆動方法並びに電子機器 | |

| JP2003330420A (ja) | 発光装置の駆動方法 | |

| JP2007163580A (ja) | 表示装置 | |

| JP4926469B2 (ja) | 表示装置 | |

| JP5116202B2 (ja) | 表示装置の駆動方法 | |

| JP4780121B2 (ja) | 表示駆動装置、表示装置及びその表示駆動方法 | |

| JP4397576B2 (ja) | 表示装置の駆動方法 | |

| JP4128601B2 (ja) | 表示装置および表示装置の駆動方法 | |

| JP3889310B2 (ja) | 表示装置および表示装置の駆動方法 | |

| JP4658016B2 (ja) | 半導体装置 | |

| JP5077390B2 (ja) | 表示駆動装置、表示装置及びその表示駆動方法 | |

| JP4688899B2 (ja) | 表示装置 | |

| JP2006284712A (ja) | 発光表示パネルの駆動方法および駆動装置 | |

| JP2005148085A (ja) | 表示装置及び表示装置の駆動方法並びに電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070319 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070319 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100720 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100726 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100922 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110222 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20110404 |