JP2005295636A - スイッチング電源回路及びdc−dcコンバータ - Google Patents

スイッチング電源回路及びdc−dcコンバータ Download PDFInfo

- Publication number

- JP2005295636A JP2005295636A JP2004104564A JP2004104564A JP2005295636A JP 2005295636 A JP2005295636 A JP 2005295636A JP 2004104564 A JP2004104564 A JP 2004104564A JP 2004104564 A JP2004104564 A JP 2004104564A JP 2005295636 A JP2005295636 A JP 2005295636A

- Authority

- JP

- Japan

- Prior art keywords

- resonance current

- circuit

- resonance

- current

- control signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Dc-Dc Converters (AREA)

Abstract

【課題】 共振電流のレベルを検出することにより高出力化と高信頼性を実現することが可能なスイッチング電源回路及びDC−DCコンバータを提供する。

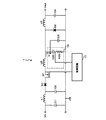

【解決手段】 本発明のスイッチング電源回路は、制御信号に基づき入力電圧Vinの導通を切り替え可能に制御するスイッチング素子Q1と、スイッチング素子Q1の出力側に接続され所定の共振周波数の共振電流Irを発生させる共振回路と、共振電流Irに応じて発生する出力電圧を半波整流して平滑化し直流出力電圧Voutを出力する直流化回路と、共振電流Irのレベルを検出する共振電流モニタ回路10と、共振電流モニタ回路10により検出された共振電流Irのレベルに基づき制御信号の波形を制御してスイッチング素子Q1に供給する制御回路11とを備えている。

【選択図】 図1

Description

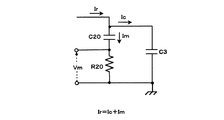

検出抵抗R20を十分小さい値とした場合には、検出コンデンサC20及び検出抵抗R20の合成インピーダンスにおける抵抗R20の寄与分を無視することができる。この場合、電流Icと電流Im(以下、検出電流Imと呼ぶ)との関係は、次の(2)式で表すことができる。

このように、電流Icと検出電流Imは、比例関係にあり、同様の波形を有することがわかる。ここで、検出抵抗R20の両端の電圧をVmとすると、検出電流Imは、次の(3)式で表される。

制御回路20においては電圧Vmが取得されるので、(3)式に従って検出電流Imを求めることができる。このように求めた検出電流Imに基づき、(2)式に従って電流Icを算出すると、電流Icに概ね一致する共振電流Irを推測できることになる。

C20=330pF

R20=100Ω

この条件の下、制御回路11にて電圧Vmのピーク値6Vが検出された場合を考える。このとき、検出コンデンサC20及び検出抵抗R21を流れる電流Imのピーク値は、(3)式に従って、

Im=6/100=0.06(A0-p)

と算出することができる。その算出結果と(2)式に基づき、コンデンサC3を流れる電流Icのピーク値は、

Ic=Im×0.198μF/330pF=0.06×600=36(A0-p)

と推定することができる。一方、(1)式において、検出電流Imが無視できる程度に小さいので、共振電流Irのピーク値もほぼ36(A0-p)になるものと推定することができる。

10…共振電流モニタ回路

11…制御回路

C1、C2、C3、C4、C20…コンデンサ

L1、L2、L3…コイル

D1、D2、D10…ダイオード

R10、R11、R20…抵抗

Vin…入力直流電圧

Vout…直流出力電圧

Ir…共振電流

Claims (10)

- 入力電圧を所定の周波数でスイッチング制御して直流出力電圧を発生し、負荷に前記直流出力電圧を供給するスイッチング電源回路であって、

制御信号に基づき前記入力電圧の導通を切り替え可能に制御するスイッチング素子と、

前記スイッチング素子の出力側に接続され、所定の共振周波数の共振電流を発生させる共振回路と、

前記共振電流に応じて発生する出力電圧を半波整流して平滑化し、前記直流出力電圧を出力する直流化回路と、

前記共振電流のレベルを検出する共振電流検出回路と、

前記共振電流検出回路により検出された前記共振電流のレベルに基づき前記制御信号の波形を制御して前記スイッチング素子に供給する制御回路と、

を備えることを特徴とするスイッチング電源回路。 - 前記共振電流検出回路は、1次巻線に前記共振電流を印加して2次巻線に前記共振電流に比例する電圧を誘起するカレントトランスを用いて構成されることを特徴とする請求項1に記載のスイッチング電源回路。

- 前記共振電流検出回路は、抵抗とコンデンサを組み合わせて前記共振電流を分流する分流回路を用いて構成されることを特徴とする請求項1に記載のスイッチング電源回路。

- 前記分流回路は、前記共振回路の出力側と接地間に接続されたコンデンサ及び抵抗の直列回路であり、前記抵抗の両端電圧に基づき前記共振電流のレベルを検出することを特徴とする請求項3に記載のスイッチング電源回路。

- 入力直流電圧を所定の周波数でスイッチング制御して直流出力電圧を発生し、負荷に前記直流出力電圧を供給するDC−DCコンバータであって、

制御信号に基づき前記入力直流電圧の導通を切り替え可能に制御するスイッチング素子と、

前記スイッチング素子の出力側に接続され、所定の共振周波数の共振電流を発生させる共振回路と、

前記共振電流に応じて発生する出力電圧を半波整流して平滑化し、前記直流出力電圧を出力する直流化回路と、

前記共振電流のレベルを検出する共振電流検出回路と、

前記共振電流検出回路により検出された前記共振電流のレベルに基づき前記制御信号の波形を制御して前記スイッチング素子に供給する制御回路と、

を備えることを特徴とするDC−DCコンバータ。 - 前記共振電流検出回路は、1次巻線に前記共振電流を印加して2次巻線に前記共振電流に比例する電圧を誘起するカレントトランスを用いて構成されることを特徴とする請求項5に記載のDC-DCコンバータ。

- 前記共振電流検出回路は、抵抗とコンデンサを組み合わせて前記共振電流を分流する分流回路を用いて構成されることを特徴とする請求項5に記載のDC-DCコンバータ。

- 前記分流回路は、前記共振回路の出力側と接地間に接続されたコンデンサ及び抵抗の直列回路であり、前記抵抗の両端電圧に基づき前記共振電流のレベルを検出することを特徴とする請求項7に記載のDC-DCコンバータ。

- 前記制御回路は、前記共振電流のレベル変化を参照して前記共振電流がゼロとなるタイミングを判別し、判別されたタイミングに基づき前記制御信号の波形を制御することを特徴とする請求項5から請求項8のいずれかに記載のDC-DCコンバータ。

- 前記制御回路は、前記共振電流がゼロとなるタイミングで前記スイッチング素子が非導通状態となるように前記制御信号を切り替え制御することを特徴とする請求項9に記載のDC-DCコンバータ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104564A JP2005295636A (ja) | 2004-03-31 | 2004-03-31 | スイッチング電源回路及びdc−dcコンバータ |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104564A JP2005295636A (ja) | 2004-03-31 | 2004-03-31 | スイッチング電源回路及びdc−dcコンバータ |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005295636A true JP2005295636A (ja) | 2005-10-20 |

Family

ID=35327974

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004104564A Pending JP2005295636A (ja) | 2004-03-31 | 2004-03-31 | スイッチング電源回路及びdc−dcコンバータ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005295636A (ja) |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02211054A (ja) * | 1989-02-07 | 1990-08-22 | Nec Corp | 電流共振型コンバータ |

| JPH02311168A (ja) * | 1989-05-26 | 1990-12-26 | Nec Corp | パルス幅制御方式電流共振型コンバータ |

| JPH0378465A (ja) * | 1989-08-17 | 1991-04-03 | Oki Electric Ind Co Ltd | 電流共振型電源の制御回路 |

| JPH09331673A (ja) * | 1996-06-10 | 1997-12-22 | Matsushita Electric Ind Co Ltd | 電流共振型dc−dcコンバータ |

| JP2001292571A (ja) * | 2000-04-07 | 2001-10-19 | Yokogawa Electric Corp | 同期整流回路 |

| JP2002058240A (ja) * | 2000-06-01 | 2002-02-22 | Auto Network Gijutsu Kenkyusho:Kk | Dc−dcコンバータ回路 |

-

2004

- 2004-03-31 JP JP2004104564A patent/JP2005295636A/ja active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02211054A (ja) * | 1989-02-07 | 1990-08-22 | Nec Corp | 電流共振型コンバータ |

| JPH02311168A (ja) * | 1989-05-26 | 1990-12-26 | Nec Corp | パルス幅制御方式電流共振型コンバータ |

| JPH0378465A (ja) * | 1989-08-17 | 1991-04-03 | Oki Electric Ind Co Ltd | 電流共振型電源の制御回路 |

| JPH09331673A (ja) * | 1996-06-10 | 1997-12-22 | Matsushita Electric Ind Co Ltd | 電流共振型dc−dcコンバータ |

| JP2001292571A (ja) * | 2000-04-07 | 2001-10-19 | Yokogawa Electric Corp | 同期整流回路 |

| JP2002058240A (ja) * | 2000-06-01 | 2002-02-22 | Auto Network Gijutsu Kenkyusho:Kk | Dc−dcコンバータ回路 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6528561B2 (ja) | 高効率力率改善回路およびスイッチング電源装置 | |

| KR100428329B1 (ko) | 전원공급장치 | |

| US7936152B2 (en) | Switching power source | |

| US8077488B2 (en) | Switching-type power-supply unit and a method of switching in power-supply unit | |

| JP2008535456A (ja) | 共振コンバータの制御 | |

| US10355610B2 (en) | LLC power converter and switching method thereof | |

| JP4104609B2 (ja) | スイッチモード電源ユニットの電流および電圧を制御する方法 | |

| JP4854556B2 (ja) | 電源装置 | |

| US7719139B2 (en) | Power supply unit | |

| JPH07241075A (ja) | 電力変換における電流検出装置及び方法 | |

| US6985369B2 (en) | DC-DC converter | |

| JP4352460B2 (ja) | 電源装置 | |

| JP5194665B2 (ja) | 電源装置 | |

| US6580624B2 (en) | Switching power circuit with a filter for controlling noise of a switching frequency and method of same | |

| CN100583615C (zh) | 谐振转换器及其控制装置和控制方法 | |

| JP2005295636A (ja) | スイッチング電源回路及びdc−dcコンバータ | |

| JP2010081779A (ja) | 電源装置及びこの電源装置のスイッチング方法 | |

| JPH09168281A (ja) | 直流電源装置 | |

| JP2002125367A (ja) | 電源装置 | |

| JP2003259642A (ja) | 無接点電源装置 | |

| JP3001057B1 (ja) | スイッチング電源装置及びその制御方法 | |

| JP3571959B2 (ja) | スイッチング電源装置 | |

| JP3056179B2 (ja) | 瞬断対策回路 | |

| JP2002142456A (ja) | 直流電源装置 | |

| JPH05336747A (ja) | スイッチング電源 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070201 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20081022 |

|

| A977 | Report on retrieval |

Effective date: 20091007 Free format text: JAPANESE INTERMEDIATE CODE: A971007 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091020 |

|

| A521 | Written amendment |

Effective date: 20091218 Free format text: JAPANESE INTERMEDIATE CODE: A523 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100202 |

|

| A02 | Decision of refusal |

Effective date: 20100601 Free format text: JAPANESE INTERMEDIATE CODE: A02 |

|

| RD02 | Notification of acceptance of power of attorney |

Effective date: 20100818 Free format text: JAPANESE INTERMEDIATE CODE: A7422 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20100818 |