JP2005295629A - 電源装置 - Google Patents

電源装置 Download PDFInfo

- Publication number

- JP2005295629A JP2005295629A JP2004104470A JP2004104470A JP2005295629A JP 2005295629 A JP2005295629 A JP 2005295629A JP 2004104470 A JP2004104470 A JP 2004104470A JP 2004104470 A JP2004104470 A JP 2004104470A JP 2005295629 A JP2005295629 A JP 2005295629A

- Authority

- JP

- Japan

- Prior art keywords

- mos transistor

- output

- output terminal

- power supply

- substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Dc-Dc Converters (AREA)

Abstract

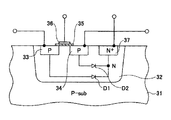

【解決手段】一端に電源電圧VDDが印加されるコイルLと、コイルLの他端と出力端子Toutとの間にドレイン−ソースが接続された第1のMOSトランジスタQ2と、出力端子Toutから出力される出力電圧Voutを検出し、出力端子Toutの電圧が所定の電圧となるようにコイルLの他端の接続を制御する制御回路112とを有する電源回路において、第1のMOSトランジスタQ2の基板とコイルLとの間に接続された第1の抵抗R11と、第1のMOSトランジスタQ2の基板と第2のMOSトランジスタQ12のゲートとの間に接続された第2の抵抗R12と、第2のMOSトランジスタQ12のゲートと第2の抵抗R12との接続点と基準電位GNDとの間に接続されたスイッチ手段Q11とを有する。

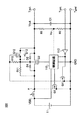

【選択図】図1

Description

図1は本発明の一実施例の回路構成図を示す。同図中、図3と同一構成部分には同一符号を付し、その説明は省略する。

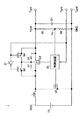

図2は本発明の一実施例の動作説明図を示す。図2(A)は昇圧動作時、図2(B)は昇圧停止時の要部の等価回路図を示す。

昇圧動作時には、コントロール端子Tcntに供給されるコントロール信号がローレベルとされる。ローレベルのコントロール信号は、インバータ113により反転されてハイレベルとされ、制御回路112及びMOSトランジスタQ11のゲートに供給される。

昇圧停止時には、コントロール端子Tcntに供給されるコントロール信号は、ハイレベルとされる。コントロール端子Tcntに供給されるコントロール信号がハイレベルとなると、インバータ113の出力はローレベルとなる。

L コイル、R1、R2、R11、R12 抵抗、C1 コンデンサ

Q1、Q2、Q11、Q12 MOSトランジスタ、D1、D2、D13 寄生ダイオード

100 電源装置、112 制御回路、113 インバータ

Claims (5)

- 一端に入力端子が接続されたコイルと、該コイルの他端と出力端子との間にドレイン−ソースが接続された第1のMOSトランジスタと、該出力端子から出力される出力電圧を検出し、該出力端子の電圧が所定の電圧となるように該コイルの他端の接続を制御する制御回路部とを有する電源回路において、

前記第1のMOSトランジスタの基板と前記出力端子との間に接続された第2のMOSトランジスタと、

前記第1のMOSトランジスタの基板と前記コイルとの間に接続された第1の抵抗と、

前記第1のMOSトランジスタの基板と前記第2のMOSトランジスタのゲートとの間に接続された第2の抵抗と、

前記第2のMOSトランジスタのゲートと前記第2の抵抗との接続点と基準電位との間に接続されたスイッチ手段とを有することを特徴とする電源装置。 - 前記第2のMOSトランジスタは、前記出力端子側から前記第1のMOSトランジスタの基板側に向かって順方向となるように寄生ダイオードが形成される構成とされたことを特徴とする請求項1記載の電源装置。

- 前記第2のMOSトランジスタは、PチャネルMOSトランジスタから構成され、基板が前記第1のMOSトランジスタの基板に接続されたことを特徴とする請求項2記載の電源装置。

- 前記スイッチ手段は、前記出力端子から電源を出力するときにオンされ、前記出力端子から電源の出力を停止する時にオフされることを特徴とする請求項1乃至3のいずれか一項記載の電源装置。

- 前記スイッチ手段は、MOSトランジスタから構成されたことを特徴とする請求項1乃至4のいずれか一項記載の電源装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104470A JP4289195B2 (ja) | 2004-03-31 | 2004-03-31 | 電源装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004104470A JP4289195B2 (ja) | 2004-03-31 | 2004-03-31 | 電源装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005295629A true JP2005295629A (ja) | 2005-10-20 |

| JP4289195B2 JP4289195B2 (ja) | 2009-07-01 |

Family

ID=35327967

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004104470A Expired - Fee Related JP4289195B2 (ja) | 2004-03-31 | 2004-03-31 | 電源装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4289195B2 (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2007010801A1 (ja) * | 2005-07-15 | 2007-01-25 | Rohm Co., Ltd. | 昇圧型、降圧型スイッチングレギュレータおよびその制御回路ならびにそれを用いた電子機器 |

| JP2008092639A (ja) * | 2006-09-29 | 2008-04-17 | Matsushita Electric Ind Co Ltd | 電源装置 |

| US7560910B2 (en) | 2006-09-19 | 2009-07-14 | Renesas Technology Corp. | Voltage converter and semiconductor integrated circuit |

| JP2009178033A (ja) * | 2007-12-26 | 2009-08-06 | Rohm Co Ltd | 昇圧型スイッチングレギュレータおよびその制御回路 |

| JP2010085328A (ja) * | 2008-10-01 | 2010-04-15 | Toyota Central R&D Labs Inc | ホールド回路 |

-

2004

- 2004-03-31 JP JP2004104470A patent/JP4289195B2/ja not_active Expired - Fee Related

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2007010801A1 (ja) * | 2005-07-15 | 2007-01-25 | Rohm Co., Ltd. | 昇圧型、降圧型スイッチングレギュレータおよびその制御回路ならびにそれを用いた電子機器 |

| US7560910B2 (en) | 2006-09-19 | 2009-07-14 | Renesas Technology Corp. | Voltage converter and semiconductor integrated circuit |

| JP2008092639A (ja) * | 2006-09-29 | 2008-04-17 | Matsushita Electric Ind Co Ltd | 電源装置 |

| JP2009178033A (ja) * | 2007-12-26 | 2009-08-06 | Rohm Co Ltd | 昇圧型スイッチングレギュレータおよびその制御回路 |

| JP2010085328A (ja) * | 2008-10-01 | 2010-04-15 | Toyota Central R&D Labs Inc | ホールド回路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4289195B2 (ja) | 2009-07-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7692474B2 (en) | Control circuit for a high-side semiconductor switch for switching a supply voltage | |

| JP5338387B2 (ja) | 電源切換え装置 | |

| JP6213136B2 (ja) | 半導体装置 | |

| KR0131161B1 (ko) | 정 전류 발생 장치 | |

| JPH07154962A (ja) | 定電圧発生回路 | |

| JP4022208B2 (ja) | 線形および飽和領域で動作可能なパワーmosfet用電流センス | |

| JP3912417B2 (ja) | 駆動回路 | |

| JP2016143799A (ja) | 異常検出回路 | |

| JP2009044304A (ja) | 半導体素子制御装置 | |

| JP4289195B2 (ja) | 電源装置 | |

| JP4494083B2 (ja) | スイッチング制御回路 | |

| JP4318511B2 (ja) | 昇圧回路 | |

| JP2010028522A (ja) | 半導体装置 | |

| JP2004072829A5 (ja) | ||

| US7692479B2 (en) | Semiconductor integrated circuit device including charge pump circuit capable of suppressing noise | |

| KR100834219B1 (ko) | 레벨 시프트 회로 및 이를 구비한 스위칭 레귤레이터 | |

| JP5009083B2 (ja) | スイッチング電源回路 | |

| US6762576B2 (en) | Motor driving device for supplying driving current to a three-phase motor through output transistors | |

| JP2020031390A (ja) | スイッチ回路 | |

| JP7294084B2 (ja) | 短絡判定装置 | |

| JP4105717B2 (ja) | ブートストラップ回路 | |

| JP2815744B2 (ja) | 誘導性負荷定電流駆動用集積回路 | |

| JP5918512B2 (ja) | H型ブリッジ回路およびモータ駆動装置 | |

| JP2003198277A (ja) | Mosトランジスタ出力回路 | |

| JP3540872B2 (ja) | 起動回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060626 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090203 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090310 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090323 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4289195 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120410 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150410 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |