JP2005294618A - 電子部品 - Google Patents

電子部品 Download PDFInfo

- Publication number

- JP2005294618A JP2005294618A JP2004108879A JP2004108879A JP2005294618A JP 2005294618 A JP2005294618 A JP 2005294618A JP 2004108879 A JP2004108879 A JP 2004108879A JP 2004108879 A JP2004108879 A JP 2004108879A JP 2005294618 A JP2005294618 A JP 2005294618A

- Authority

- JP

- Japan

- Prior art keywords

- plating layer

- electronic component

- layer

- plating

- solder

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Ceramic Capacitors (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

Abstract

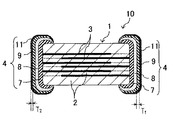

【解決手段】電子部品素体の表面に外部電気回路と半田接合される外部電極を有する電子部品において、前記外部電極が、下地導体層の表面に、少なくとも錫を含有する第1メッキ層と、該第1メッキ層よりも低融点の錫合金から成る第2メッキ層とを、前記第2メッキ層が前記第1メッキ層よりも表層側となるように両者を積層して形成また。前記下地導体層がNiメッキから成り、前記第2メッキ層の厚みを0.01μm〜0.05μmに設定した。

【選択図】図1

Description

(実験例)

2・・・誘電体層

3・・・内部電極

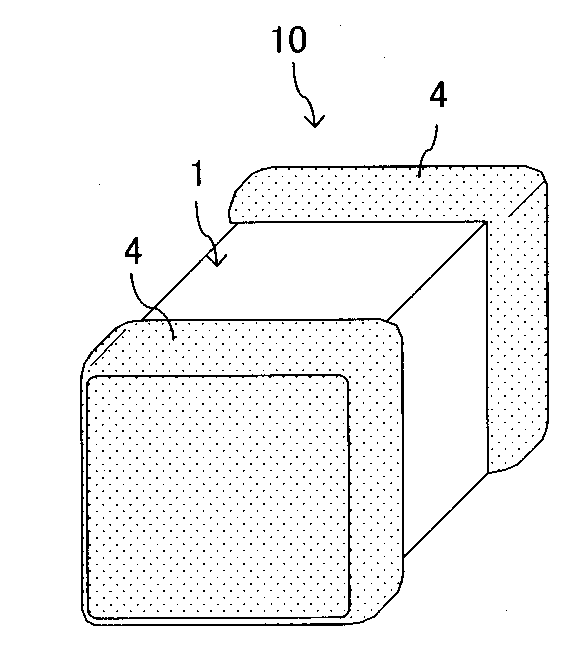

4・・・外部電極

7、8・・・下地導体層

9・・・第1メッキ層(Snメッキ層)

10・・・積層セラミックコンデンサ

11・・・第2メッキ層(Sn−Cuメッキ層)

Claims (6)

- 電子部品素体の表面に外部電気回路と半田接合される外部電極を有した電子部品において、

前記外部電極は、下地導体層と、下地導体層上に少なくとも錫を含有する第1メッキ層と、該第1メッキ層よりも低融点の錫合金から成る第2メッキ層とを、前記第2メッキ層が前記第1メッキ層よりも表層側となるように両者を積層して形成されていることを特徴とする電子部品。 - 前記下地導体層がNiメッキから成り、前記第2メッキ層の厚みT2が0.01μm〜0.05μmに設定されていることを特徴とする請求項1に記載の電子部品。

- 前記第1メッキ層の厚みT1が3μm以上であることを特徴とする請求項1または請求項2に記載の電子部品。

- 前記第1メッキ層の融点が前記第2メッキ層の融点よりも12〜18℃高温であることを特徴とする請求項1乃至請求項3のいずれかに記載の電子部品。

- 前記第1メッキ層金属成分がSnから成り、前記第2メッキ層金属成分がSn−Ag、Sn−Cu、Sn−Biのいずれかより成ることを特徴とする請求項1乃至請求項4のいずれかに記載の電子部品。

- 前記電子部品素体が複数個の誘電体層を、間に前記外部電極に電気的に接続される内部電極を介して積層してなるコンデンサ素体であることを特徴とする請求項1乃至請求項5のいずれかに記載の電子部品。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108879A JP4544896B2 (ja) | 2004-04-01 | 2004-04-01 | 電子部品 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004108879A JP4544896B2 (ja) | 2004-04-01 | 2004-04-01 | 電子部品 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005294618A true JP2005294618A (ja) | 2005-10-20 |

| JP4544896B2 JP4544896B2 (ja) | 2010-09-15 |

Family

ID=35327199

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004108879A Expired - Fee Related JP4544896B2 (ja) | 2004-04-01 | 2004-04-01 | 電子部品 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4544896B2 (ja) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013080875A (ja) * | 2011-10-05 | 2013-05-02 | Rohm Co Ltd | 電子部品の電極構造 |

| US20140321025A1 (en) * | 2012-01-23 | 2014-10-30 | Murata Manufacturing Co., Ltd. | Electronic component and manufacturing method therefor |

| JPWO2013132966A1 (ja) * | 2012-03-05 | 2015-07-30 | 株式会社村田製作所 | 電子部品および電子部品と接合対象物との接合構造体の形成方法 |

| JP2016105501A (ja) * | 2016-02-03 | 2016-06-09 | ローム株式会社 | 電子部品の電極構造 |

| US9530560B2 (en) | 2013-07-10 | 2016-12-27 | Murata Manufacturing Co., Ltd. | Ceramic electronic component with low equivalent series resistance and method for manufacturing the same |

| US20170069420A1 (en) * | 2014-02-19 | 2017-03-09 | Tdk Corporation | Coil component and terminal component used therein |

| CN112185704A (zh) * | 2019-07-04 | 2021-01-05 | 三星电机株式会社 | 多层陶瓷电容器 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02296314A (ja) * | 1989-05-10 | 1990-12-06 | Matsushita Electric Ind Co Ltd | チップ部品の製造方法 |

| JP2000280090A (ja) * | 1999-01-29 | 2000-10-10 | Fuji Electric Co Ltd | はんだ合金 |

| JP2001230151A (ja) * | 2000-02-16 | 2001-08-24 | Matsushita Electric Ind Co Ltd | リードレスチップ部品 |

| JP2001332165A (ja) * | 2000-03-16 | 2001-11-30 | Uchihashi Estec Co Ltd | ヒュ−ズ素子及びヒュ−ズ内蔵電気部品 |

| JP2002359105A (ja) * | 2001-05-31 | 2002-12-13 | Tdk Corp | ガラスダイオード型ntcサーミスタ |

| JP2003163135A (ja) * | 2001-11-28 | 2003-06-06 | Nec Tokin Corp | 積層チップ部品 |

-

2004

- 2004-04-01 JP JP2004108879A patent/JP4544896B2/ja not_active Expired - Fee Related

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02296314A (ja) * | 1989-05-10 | 1990-12-06 | Matsushita Electric Ind Co Ltd | チップ部品の製造方法 |

| JP2000280090A (ja) * | 1999-01-29 | 2000-10-10 | Fuji Electric Co Ltd | はんだ合金 |

| JP2001230151A (ja) * | 2000-02-16 | 2001-08-24 | Matsushita Electric Ind Co Ltd | リードレスチップ部品 |

| JP2001332165A (ja) * | 2000-03-16 | 2001-11-30 | Uchihashi Estec Co Ltd | ヒュ−ズ素子及びヒュ−ズ内蔵電気部品 |

| JP2002359105A (ja) * | 2001-05-31 | 2002-12-13 | Tdk Corp | ガラスダイオード型ntcサーミスタ |

| JP2003163135A (ja) * | 2001-11-28 | 2003-06-06 | Nec Tokin Corp | 積層チップ部品 |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013080875A (ja) * | 2011-10-05 | 2013-05-02 | Rohm Co Ltd | 電子部品の電極構造 |

| US20140321025A1 (en) * | 2012-01-23 | 2014-10-30 | Murata Manufacturing Co., Ltd. | Electronic component and manufacturing method therefor |

| US9437365B2 (en) * | 2012-01-23 | 2016-09-06 | Murata Manufacturing Co., Ltd. | Electronic component and manufacturing method therefor |

| JPWO2013132966A1 (ja) * | 2012-03-05 | 2015-07-30 | 株式会社村田製作所 | 電子部品および電子部品と接合対象物との接合構造体の形成方法 |

| US9530560B2 (en) | 2013-07-10 | 2016-12-27 | Murata Manufacturing Co., Ltd. | Ceramic electronic component with low equivalent series resistance and method for manufacturing the same |

| US20170069420A1 (en) * | 2014-02-19 | 2017-03-09 | Tdk Corporation | Coil component and terminal component used therein |

| US10186368B2 (en) * | 2014-02-19 | 2019-01-22 | Tdk Corporation | Coil component and terminal component used therein |

| JP2016105501A (ja) * | 2016-02-03 | 2016-06-09 | ローム株式会社 | 電子部品の電極構造 |

| CN112185704A (zh) * | 2019-07-04 | 2021-01-05 | 三星电机株式会社 | 多层陶瓷电容器 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP4544896B2 (ja) | 2010-09-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102408016B1 (ko) | 칩형 전자 부품 | |

| JP4957394B2 (ja) | セラミック電子部品及びその製造方法 | |

| KR101127870B1 (ko) | 세라믹 전자 부품 및 세라믹 전자 부품의 제조 방법 | |

| US9144166B2 (en) | Electronic component | |

| JP5958479B2 (ja) | 電子部品の実装構造体 | |

| JPH0684687A (ja) | セラミックチップ部品およびチップ部品実装構造 | |

| JP6919515B2 (ja) | 積層セラミックコンデンサ | |

| JP2019004080A (ja) | 電子部品、電子装置、及び電子部品の製造方法 | |

| JP5725678B2 (ja) | 積層セラミック電子部品、その製造方法及びその実装基板 | |

| US9320146B2 (en) | Electronic circuit module component | |

| JP4463045B2 (ja) | セラミック電子部品及びコンデンサ | |

| JP2020061468A (ja) | 積層セラミック電子部品およびその実装構造 | |

| JP4544896B2 (ja) | 電子部品 | |

| KR102816972B1 (ko) | 적층 세라믹 콘덴서 및 회로 기판 | |

| WO2023189448A1 (ja) | 積層セラミックコンデンサ、積層セラミックコンデンサの製造方法および積層セラミックコンデンサの実装構造 | |

| JP4715000B2 (ja) | チップ型電子部品の製造方法 | |

| JPH0737753A (ja) | チップ型部品 | |

| JP2001155955A (ja) | 外部端子電極具備電子部品及びその搭載電子用品 | |

| JPH05243074A (ja) | チップ状電子部品及びその端子電極形成方法 | |

| JP2006060148A (ja) | セラミック電子部品及びコンデンサ | |

| JP2005340699A (ja) | 表面実装型電子部品、電子部品の実装構造及び実装方法 | |

| JP6164228B2 (ja) | モジュールおよびその製造方法 | |

| KR20140013289A (ko) | 세라믹 전자 부품 및 그 제조 방법 | |

| US20090230596A1 (en) | Method of manufacturing multi-layered ceramic substrate | |

| JP2600477B2 (ja) | 積層セラミック電子部品 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070213 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20091030 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091109 |

|

| A521 | Written amendment |

Effective date: 20091226 Free format text: JAPANESE INTERMEDIATE CODE: A523 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Effective date: 20100601 Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100629 |

|

| FPAY | Renewal fee payment (prs date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130709 Year of fee payment: 3 |

|

| R150 | Certificate of patent (=grant) or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |