JP2005294444A - 半導体装置及びその製造方法、疑似ウェーハ及びその製造方法、並びに半導体装置の実装構造及びその実装方法 - Google Patents

半導体装置及びその製造方法、疑似ウェーハ及びその製造方法、並びに半導体装置の実装構造及びその実装方法 Download PDFInfo

- Publication number

- JP2005294444A JP2005294444A JP2004105835A JP2004105835A JP2005294444A JP 2005294444 A JP2005294444 A JP 2005294444A JP 2004105835 A JP2004105835 A JP 2004105835A JP 2004105835 A JP2004105835 A JP 2004105835A JP 2005294444 A JP2005294444 A JP 2005294444A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- chip component

- support

- manufacturing

- chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/01—Manufacture or treatment

- H10W72/0198—Manufacture or treatment batch processes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W46/00—Marks applied to devices, e.g. for alignment or identification

- H10W46/301—Marks applied to devices, e.g. for alignment or identification for alignment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W70/00—Package substrates; Interposers; Redistribution layers [RDL]

- H10W70/01—Manufacture or treatment

- H10W70/05—Manufacture or treatment of insulating or insulated package substrates, or of interposers, or of redistribution layers

- H10W70/08—Manufacture or treatment of insulating or insulated package substrates, or of interposers, or of redistribution layers by depositing layers on the chip or wafer, e.g. "chip-first" RDLs

- H10W70/09—Manufacture or treatment of insulating or insulated package substrates, or of interposers, or of redistribution layers by depositing layers on the chip or wafer, e.g. "chip-first" RDLs extending onto an encapsulation that laterally surrounds the chip or wafer, e.g. fan-out wafer level package [FOWLP] RDLs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

- H10W72/07202—Connecting or disconnecting of bump connectors using auxiliary members

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

- H10W72/07221—Aligning

- H10W72/07223—Active alignment, e.g. using optical alignment using marks or sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/071—Connecting or disconnecting

- H10W72/072—Connecting or disconnecting of bump connectors

- H10W72/07221—Aligning

- H10W72/07227—Aligning involving guiding structures, e.g. spacers or supporting members

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/241—Dispositions, e.g. layouts

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/20—Bump connectors, e.g. solder bumps or copper pillars; Dummy bumps; Thermal bumps

- H10W72/29—Bond pads specially adapted therefor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W72/00—Interconnections or connectors in packages

- H10W72/90—Bond pads, in general

- H10W72/941—Dispositions of bond pads

- H10W72/9413—Dispositions of bond pads on encapsulations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W74/00—Encapsulations, e.g. protective coatings

- H10W74/01—Manufacture or treatment

- H10W74/019—Manufacture or treatment using temporary auxiliary substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W90/00—Package configurations

- H10W90/701—Package configurations characterised by the relative positions of pads or connectors relative to package parts

- H10W90/721—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors

- H10W90/724—Package configurations characterised by the relative positions of pads or connectors relative to package parts of bump connectors between a chip and a stacked insulating package substrate, interposer or RDL

Landscapes

- Optical Couplings Of Light Guides (AREA)

- Photo Coupler, Interrupter, Optical-To-Optical Conversion Devices (AREA)

Abstract

【課題】 チップ部品の位置精度が良好に保たれた半導体装置及びその製造方法、その製造に用いる疑似ウェーハ及びその製造方法、並びに半導体装置の実装構造及び実装方法を提供すること。

【解決手段】 チップ部品3、3Aの支持体として透明なガラス基板30を用い、このガラス基板30で囲まれた狭い欠除部31の領域のみに樹脂4を配し、この領域に配置したチップ部品3、3Aを樹脂4で覆うことにより、変形し易い樹脂4の量が少なく硬化収縮による変形が小さいため、チップ部品3、3Aの位置精度が保たれ、ガラス基板30に接した感光性絶縁膜28a、28bの層間にアライメントマーク14を設けることにより、ガラス基板30を通して、アライメントマーク14をプリント配線板16のアライメントマーク25に対し、位置合せできることにより精度良く実装できる。

【選択図】 図1

【解決手段】 チップ部品3、3Aの支持体として透明なガラス基板30を用い、このガラス基板30で囲まれた狭い欠除部31の領域のみに樹脂4を配し、この領域に配置したチップ部品3、3Aを樹脂4で覆うことにより、変形し易い樹脂4の量が少なく硬化収縮による変形が小さいため、チップ部品3、3Aの位置精度が保たれ、ガラス基板30に接した感光性絶縁膜28a、28bの層間にアライメントマーク14を設けることにより、ガラス基板30を通して、アライメントマーク14をプリント配線板16のアライメントマーク25に対し、位置合せできることにより精度良く実装できる。

【選択図】 図1

Description

本発明は、例えばMCM(マルチチップモジュール)の構成に好適な半導体装置及びその製造方法、疑似ウェーハ及びその製造方法、並びに半導体装置の実装構造及びその実装方法に関するものである。

従来、携帯用電子機器の小型・軽量化、高速化の要求に対し、一つの方法として、ICの高集積化、微細化を図って複数の機能をワンチップ(システムLSI)化しているが、歩留低下等による製造コストの増大等の問題でシステムLSIを低コストで実現することが難しくなっている。一方で、複数の半導体チップをワンパッケージ化したMCM(Multi Chip Module )が提案されている。

MCMは多層配線基板に半導体チップを配置しているが、搭載する半導体チップの接続端子ピッチが狭くなると配線基板の製造が難しくなり、基板のコストアップとなる。また、バンプやワイヤボンディング、タブ等で接続するため、接続端子数に制限がある上、その平面視面積は搭載半導体チップの平面視面積の総和より大きくなってしまう。更に、信号伝達が遅くなり、性能低下等の問題がある。

MCMの製造技術については、厚さの異なる複数のチップの電極パッドを下にして接着剤を含んだシート上に配し、シートの周縁を型で囲んでこの型内に熱硬化性樹脂を充填し、硬化後に型とシートを剥離することにより、厚さの異なるチップで構成したモジュールを形成できることが開示されている(後述の特許文献1参照)。また、支持基板に良品チップを貼り付けた後に、保護物質を被着して剥離することで疑似ウェーハを作製し、その上に半導体プロセスにより配線することが開示されている(後述の特許文献2参照)。

このうち、本出願人が提起した特許文献2(以下、先願発明と称する。)は、自社製又は他社製の区別なく、ウェーハより半導体チップを切り出した後、オープン/ショート或いはDC(直流)電圧測定により良品と確認された半導体ベアチップのみを疑似ウェーハ上に再配置し、これに所定の製造工程を施してチップ状電子部品を作製するものであるが、その製造プロセスを図16に示す。

まず、図16(a)のように、仮の支持基板としての石英基板(加熱プロセスは400℃以下であるのでガラス基板でもよい。)1上に、紫外線を照射されると粘着力が低下する例えばアクリル系の粘着シート2を貼り付ける。

次に、図16(b)のように、良品と確認された複数の良品ベアチップ3のチップ表面(デバイス面)を下向きに配列して粘着シート2に貼り付ける。なお、良品ベアチップ3は、通常のウェーハ工程でダイシングして、使用したダイシングシート(図示せず)の延伸状態から取り出してもよく、チップトレイから移載してもよい。

次に、図16(c)のように、良品ベアチップ3上から有機系絶縁性樹脂、例えばエポキシ系等の樹脂4をスピンコート法か印刷法により、均一に塗布する。

次に、図16(d)のように、石英基板1の裏側より紫外線を照射して、粘着シート2の粘着力を弱め、樹脂4で側面及び裏面が連続して固められた複数の良品ベアチップ(以下、半導体チップ、チップ又はチップ部品と称することがある。)3を配した疑似ウェーハ29を石英基板1から剥離する。

次に図16(e)のように、良品ベアチップ表面(デバイス面)が上になるように疑似ウェーハ29をひっくり返す。

その後、無電解めっき法(図示省略)により、開口されたAl電極パッド5の上面のみに選択的にNiめっき層を形成し、この上に配したはんだペーストを加熱溶融してはんだバンプをウェーハ一括で形成後に、再度プローブ検査により電気的特性を測定することにより、更により確実に良品チップのみを選別する。

上記のように形成した半導体チップ3は、図17に示すように半導体装置39としてワンチップに個片化後、図示いないが、例えば、外部接続端子9にはんだバンプを配して回路基板にマウントしたり、複数のチップを並列又は上下に配してチップ間の再配置配線(半導体チップ内の配線をチップ上の任意の位置に引き出して行う配線)を行うことにより、平置構造又は積層構造のMCMを構成することができる。また、図16において配置する半導体チップ3は、同一種類のチップに限らず、種類の異なるチップを組み合わせた半導体装置を形成することもでき、これらを疑似ウェーハ29上で一括して行うことができる。

このように、先願発明によれば、半導体チップの電極面以外(即ち、チップの側面及び裏面)が連続した保護物質によって保護されるので、チップ化後のハンドリングにおいてチップが保護され、ハンドリングが容易となる。

また、半導体ウェーハから切出した良品のみを選択して再配置しているので、あたかも全品が良品チップからなる疑似ウェーハが得られ、配置した良品チップに対してウェーハ一括でのバンプ処理等が可能となり、低コストのバンプチップを形成できると共に、半導体チップを疑似ウェーハから切り出す際に、チップ間の保護物質の部分を切断することになるので、半導体チップ本体への悪影響(歪みやばり、亀裂等のダメージ)を抑えて容易に切断することができる。

しかも、保護物質によってチップの側面及び裏面が覆われているため、Ni無電解めっき処理も可能である。そして、自社製ウェーハのみならず、他社から購入したベアチップでも容易にはんだバンプ処理等が可能になる。

また、MCMに搭載される異種LSIチップを全て同一半導体メーカーから供給されるケースは少なく、SRAM、フラッシュメモリーやマイコン、更にCPU(中央演算処理ユニット)を、それぞれ得意とする半導体メーカーから別々にチップで供給してもらい、これらをMCM化することもできる等の優れた特徴を有している。

上記した先願発明の半導体装置は光導波路と組み合せて実装することもでき、この場合は、例えば図18に示すようにして実装することができる。

図18は、半導体チップ3とLD(レーザダイオード)又はLED(発光ダイオード)10との組み合せにより半導体装置42が形成され。この半導体装置42がプリント配線板16との間に光導波路20を挟んで実装される状態を示している。

図示の如く、実装基板であるプリント配線板16上には光導波路20(この図では後述の図12における半導体装置41側の半分を示す。)が所定位置に貼り付けられ、プリント配線板16は加熱ステージ等からなる支持台18上に固定される。一方、実装される半導体装置42は、配線7の開口部に形成された外部接続端子7aにはんだボール12Aが設けられ、真空チャック15に把持されながら下降し、実装される状態である。

光導波路20にはアライメントマーク19が設けられており、光導波路20の先端側の上面には、不図示の光入射部20aがアライメントマーク19に対してDの距離に設けられている。そして、後述する入射光は1点鎖線で示すように、この光入射部20aから入射し、45°に傾斜した反射面20bで反射してコア層22内を全反射しながら、反対側へ導波される。

また、半導体装置42のチップ部品の電極5の面側にはアライメントマーク14が設けられており、LDチップ10の発光部11との間に光導波路20側と同一の距離Dが形成されている。従って、半導体装置42のアライメントマーク14を光導波路20のアライメントマーク19の位置に合せて実装することにより、LDチップ10の発光部11が自動的に光導波路20の光入射部20aの位置に一致するようになっている。

また、図18に示すように、半導体装置42側のアライメントマーク14は絶縁膜8内に設けられ、光導波路20側のアライメントマーク19はコア層22の外側のクラッド層1内に設けられているが、絶縁膜8及びクラッド層21は光透過性の材料からなっているので、後述する光を透過させてアライメントマーク14、19で反射することができる。

実装時の半導体装置42の実装面(はんだボール12Aが形成されている側)とプリント配線板16の表面との間は、非常に離れた距離(例えば70mm)から徐々に近づけられ、双方のアライメントマーク14、19を位置合せしながら実装されるが位置ずれが生じ易い。

従って、図18に示すように、両者の間にカメラ36を配置し、カメラ36からの出射光(実線)L1が、光導波路20のアライメントマーク19で反射する反射光(破線)L2と、半導体装置42のアライメントマーク14で反射する反射光(破線)L2とを、カメラ36によって光学的に検出し、その画像を観察して位置合せしながら半導体装置42を下降させる。

なお、この図において、図の領域外の右側に示したマークは、それぞれのアライメントマークの平面形状を拡大図示したものである。即ち、例えば図示のように十文字状のアライメントマークが形成され、半導体装置42側のアライメントマーク14よりも光導波路20側のアライメントマーク19が一回り大きく、カメラ36の領域外に示したように、アライメントマーク19の中にアライメントマーク14がぴったり位置する状態に、カメラ36で観察しながら位置合せされる。

双方のアライメントマーク14、19の位置が合わされた後、カメラ36を外して半導体装置42を接近させ、はんだボール12Aをプリント配線板16の外部接続端子17に接触させる。これにより、外部接続端子17の表面に配された不図示のはんだペーストにはんだボール12Aが粘着し、仮固定される。そしてこの状態のプリント配線板16及び半導体装置42は、この両者を所定間隔を保持しながら挟み込む治具を用いて、不図示のリフロー炉に搬入される。

図19は、実装後の状態を示しており、実装された半導体装置42はリフロー後のはんだ12を介して、光導波路20との間に一定の間隔を保った状態でプリント配線板16に実装される。このように、半導体装置42側のアライメントマーク14と光導波路20側のアライメントマーク19とを位置合せすることにより、LDチップ10の発光部11と光導波路20の光入射部20aとの位置が一致する。

上記したように、先願発明の半導体装置は、良品チップのみを選んで再配置し、その側面及び裏面を樹脂で覆って一体化し、更に特性検査を行って100%良品チップが配された疑似ウェーハ上で再配置配線し、MCMを疑似ウェーハ段階で形成して、個片化後に光導波路と組み合せて実装することもできる等の優れた特長を有している。

しかしながら、先願発明においては、疑似ウェーハ材料としてエポキシ系樹脂を用いているため、成型時の硬化収縮により、半導体装置41内でのチップ部品の位置ずれや反り等が発生し、寸法安定性がないという問題がある。また、光導波路と組み合せる実装では、光学素子(PDやLD)10と光導波路20の位置精度を〜5μm程度に抑えて実装することが求められており、従来のアライメント方式では、光学素子10と光導波路20の位置精度がでないという問題がある。そして、これらの問題は特許文献1においても同様である。

そこで本発明の目的は、チップ部品の位置精度が十分に保たれた半導体装置及びその製造方法、その製造に用いる疑似ウェーハ及びその製造方法、並びに半導体装置の実装構造及びその実装方法を提供することにある。

即ち、本発明は、一方の面に電極が設けられたチップ部品と、このチップ部品の電極面以外の少なくとも側面を覆う保護物質とによって構成された半導体装置において、

前記チップ部品の側方に設けられた光透過性の支持体に、前記保護物質を介して前記 チップ部品が一体化されている

ことを特徴とする、半導体装置(以下、本発明の半導体装置と称する。)に係るものである。

前記チップ部品の側方に設けられた光透過性の支持体に、前記保護物質を介して前記 チップ部品が一体化されている

ことを特徴とする、半導体装置(以下、本発明の半導体装置と称する。)に係るものである。

また、本発明は、一方の面に電極が設けられたチップ部品と、このチップ部品の電極面以外の少なくとも側面を覆う保護物質とによって構成された半導体装置を製造する方法において、

光透過性の材料からなる支持体の近傍位置にチップ部品を配置する工程と、

前記チップ部品の少なくとも側面を覆うようにして前記支持体と前記チップ部品との 間を保護物質で一体化する工程と

を有することを特徴とする、半導体装置の製造方法(以下、本発明の半導体装置の製造方法と称する。)に係るものである。

光透過性の材料からなる支持体の近傍位置にチップ部品を配置する工程と、

前記チップ部品の少なくとも側面を覆うようにして前記支持体と前記チップ部品との 間を保護物質で一体化する工程と

を有することを特徴とする、半導体装置の製造方法(以下、本発明の半導体装置の製造方法と称する。)に係るものである。

また、本発明は、一方の面に電極が設けられたチップ部品と、このチップ部品の電極面以外の少なくとも側面を覆う保護物質と、この保護物質によって前記チップ部品と一体化された光透過性の支持体とによって構成されている、疑似ウェーハ(以下、本発明の疑似ウェーハと称する。)に係るものである。

また、本発明は、一方の面に電極が設けられたチップ部品と、このチップ部品の電極面以外の少なくとも側面を覆う保護物質とによって構成された半導体装置を製造するのに用いる疑似ウェーハの製造方法において、

光透過性の材料からなる支持体の近傍位置にチップ部品を配置する工程と、

前記チップ部品の少なくとも側面を覆うようにして前記支持体と前記チップ部品との 間を保護物質で一体化する工程と

によって、前記保護物質で前記チップ部品が前記支持体に一体化されてなる疑似ウェーハを得る、疑似ウェーハの製造方法(以下、本発明の疑似ウェーハの製造方法と称する。)に係るものである。

光透過性の材料からなる支持体の近傍位置にチップ部品を配置する工程と、

前記チップ部品の少なくとも側面を覆うようにして前記支持体と前記チップ部品との 間を保護物質で一体化する工程と

によって、前記保護物質で前記チップ部品が前記支持体に一体化されてなる疑似ウェーハを得る、疑似ウェーハの製造方法(以下、本発明の疑似ウェーハの製造方法と称する。)に係るものである。

また、本発明は、上記した半導体装置を回路基板に実装した実装構造であって、前記支持体を通して光学的に検出される位置合せ用のマークが、前記半導体装置と前記回路基板との双方に設けられている、実装構造(以下、本発明の実装構造と称する。)に係るものである。

また、本発明は上記した半導体装置を回路基板に実装する方法であって、前記半導体装置と前記回路基板との双方に位置合せ用のマークを設け、前記支持体を通して前記位置合せ用のマークを光学的に検出して、前記回路基板に対し前記半導体装置を位置合せして実装する、実装方法(以下、本発明の実装方法と称する。)に係るものである。

本発明によれば、チップ部品が、少なくともその側面を覆った保護物質を介して、光透過性の支持体に一体化されているので、前記保護物質の領域が小さく形成されるため、成型時の硬化収縮により保護物質の変形度合は小さくなる。これによって、前記チップ部品が位置変動することが少なくなると共に、配線等の形成を一括処理した疑似ウェーハから支持体を切断して個片化できるため、チップ部品がダメージを受けることがなく、また、チップ部品が保護物質によって保護されて支持体と一体化しているために、個片化後のハンドリングも容易である。

そして、光透過性の支持体を通して、光学的に検出される位置合せ用マークが半導体装置と回路基板との双方に設けられているので、回路基板上に半導体装置を載置した状態で光透過性の支持体に検出用の光を通じることにより、その反射光を検出して双方の位置合せ用マークを容易かつ高精度に検出することができ、半導体装置を位置精度良く実装することができる。

上記した本発明の半導体装置、半導体装置の製造方法、疑似ウェーハ、疑似ウェーハの製造方法、実装構造及び実装方法においては、前記支持体が前記チップ部品の外周囲の少なくとも2辺に設けられていてもよく、好ましくは前記支持体が前記チップ部品の外周囲全体に亘って設けられていることがチップ部品の位置精度保持の点で望ましい。

更に、前記支持体が耐熱性及び機械的強度の良好な材料からなり、低線膨張であると共に、熱変形が小さく、寸法安定性のある材料によって形成することが望ましく、好適な前記支持体の材料としてガラスを用いることが望ましい。

そして、基体上に前記支持体を固定すると共に、電極面を下にして前記チップ部品を固定し、前記保護物質を前記支持体と前記チップ部品との間に充填して前記チップ部品の少なくとも前記電極面以外を覆い、前記保護物質によって前記チップ部品が一体化された前記支持体からなる疑似ウェーハを前記基体から分離した後、前記疑似ウェーハを切断して各半導体装置に個片化することが望ましい。

この場合、前記基体上に粘着手段を介して前記支持体及び前記チップ部品を固定し、これらを前記保護物質で一体化した後に、前記疑似ウェーハを前記基体から分離することにより、それ以後の処理工程を疑似ウェーハ上で一括処理し易い点で望ましい。

更にこの場合、前記基体上に、前記チップ部品配置用のアライメントマークを形成した後に、前記粘着手段を介して前記支持体及び前記チップ部品を貼り付けて固定することが望ましい。

そして、前記支持体の領域に位置合せ用のマークを形成し、この位置合せ用のマークを前記チップ部品の前記電極から引き出された配線と同一の配線材料によって形成することが望ましい。

また、前記配線の上下に光透過性の絶縁層を形成することが望ましい。

そして、前記チップ部品として、光学素子チップを含む複数の半導体チップを配置し、これらのチップ部品を実装基板に接続する構造とすることが望ましい。

この場合、特性測定により良品と判定された前記チップ部品を搭載して前記疑似ウェーハを作製し、疑似ウェーハの状態において更に前記チップ部品の特性測定を行い、良品のチップ部品を選択することが歩留りを高める点で望ましい。

上記のようにして疑似ウェーハを作製することによって、位置精度良くチップ部品が搭載された半導体装置を製造することができる。

これにより、上記のようにして形成した半導体装置を回路基板に精度良く実装することができる。

この場合、前記チップ部品としての光学素子チップに対向して前記回路基板に光導波路を固定し、この光導波路に前記位置合せ用のマークを設けることにより、容易に実装することができる点で望ましい。

なお、前記回路基板上にスペーサを設け、このスペーサ材を介して前記半導体装置を実装することが、光導波路と実装される半導体装置との間の距離を一定に保つために望ましい。

スペーサ材として熱硬化性樹脂を用い、この熱硬化性樹脂を前記回路基板上に付着させ、前記半導体装置の実装時に前記熱硬化性樹脂を硬化させることが望ましい。

次に、上記した発明を実施するための最良の形態を図面参照下で具体的に説明する。

実施の形態1

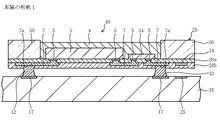

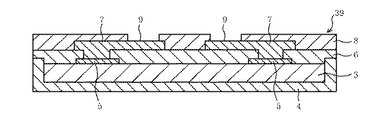

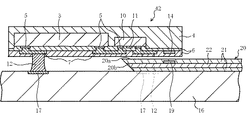

図1は、本実施の形態の半導体装置及びその実装構造の概略断面図を示す。図示の如く、個片化後の半導体装置40は、支持体がガラス基板30で形成され、これに囲まれて複数の異なるチップ部品3、3Aが配され、これらのチップ部品3、3Aの電極5の側以外の面が例えばエポキシ樹脂4で覆われ、このエポキシ樹脂4を介してチップ部品3、3Aがガラス基板30に一体化されている。

図1は、本実施の形態の半導体装置及びその実装構造の概略断面図を示す。図示の如く、個片化後の半導体装置40は、支持体がガラス基板30で形成され、これに囲まれて複数の異なるチップ部品3、3Aが配され、これらのチップ部品3、3Aの電極5の側以外の面が例えばエポキシ樹脂4で覆われ、このエポキシ樹脂4を介してチップ部品3、3Aがガラス基板30に一体化されている。

そして、チップ部品3、3Aの電極5から引き出された配線7が感光性絶縁膜28a、28bの層間に形成され、半導体装置40に設けられたアライメントマーク14がプリント配線板16上のアライメントマーク25に位置合せされた後、はんだ12を介して上記配線7の外部接続端子7aがプリント配線板16の外部接続端子17に接続され、実装された状態である。

このように、チップ部品3、3Aの搭載エリアとして、例えばくり貫き加工を行ったガラス基板30等の光透過性材料を支持体材料とし、硬化収縮等による寸法変化が起こり易い材料である樹脂4のエリアを小さくすることにより、寸法安定性のあるMCMを構成できると共に、ガラスを支持体材料とすることにより、光透過型アライメントを利用して位置精度良く実装できる。後述する他の実施の形態も同様。

図2〜図6によりその製造プロセスを説明する。

まず、図2(a)に示すように、従来と同様に仮の基板として例えば石英基板1を用い、その表面の所定位置にチップ部品を搭載するためのアライメントマーク13をプリント配置する。勿論、基板材料としては従来と同様にガラスを用いてもよい。

次に、図2(b)に示すように、上記のアライメントマーク13を形成した面側の石英基板1上に、チップ部品等の固定材として、例えば紫外線照射により粘着力が低下する粘着シート2を貼り付ける。

次に、図2(c)に示すように、搭載するチップ部品3、3Aの電極5を下向きにし、かつこれらの電極5を石英基板1上のアライメントマーク13に精度良く位置合せして、チップ部品3、3Aを粘着シート2に貼り付ける。なお、これらのチップ部品は予め検査により良品と確認されたものである。

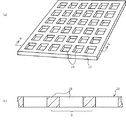

一方、上記したプロセスと平行して、光透過性の支持体となるガラス基板30を図5のように作製する。図5(a)は加工終了後のガラス基板30の概略斜視図、図5(b)は図5(a)のb−b線拡大断面図の一部分を示す。そして図5(b)におけるB部分として図3以降の各図を説明する。

光透過性の支持体として用いる材料は、耐熱性、機械的強度及び透明性に優れたものである。この材料としては例えば石英等のガラス系材料が好適であり、またポリカーボネート等も使用可能であるが、本実施の形態では青板ガラス(以下、ガラスと称する。)を材料に用い、上記プロセスと平行して、ガラス基板30に所定のパターンでチップ部品搭載エリアをくり貫いた欠除部31の加工を行う。穴加工方法としては、サンドブラスト法やケミカルエッチング法で行うことが可能である。ここで、ガラス基板30は低線膨張で熱変形が小さく、光透過性があることが重要であり、この要件を満たせば、ガラス基板でなくてもよい。

また、くり貫いた欠除部31のサイズは、搭載チップサイズに対して必要最低限の極力小さいサイズ(チップサイズ+0.4mmが目安サイズ)で開口することがポイントであり、これにより後述する充填材の塗布量を少なくすることができ、寸法安定性のあるMCMが達成できる。

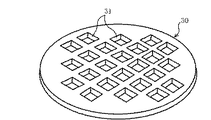

また、図6に示すように、ガラス基板30の形状は円形であってもよい。基板が円形であっても、欠如部31は図5に示した方形の基板の場合と同じである。

次に、図3(d)に示すように、ガラス基板30に形成した欠除部31の中にチップ部品3、3Aを精度良く位置させて、ガラス基板30と共に粘着シート2に貼り付ける。

次に、図3(e)に示すように、ガラス基板30の欠除部31に対して、チップ部品3、3Aの電極面以外を覆うように樹脂4を塗布する。この材料としては高フィラー充填のエポキシ樹脂やガラス系の材料を使用する。このように、限られた狭い領域の欠除部31のみに樹脂4を充填することにより、樹脂4の硬化収縮による変形が極めて小さいため、寸法安定性のあるチップ部品3、3Aを形成できると共に、ガラス基板30が疑似ウェーハ29として機能する。

次に、図3(f)に示すように、石英基板1の裏側から紫外線27を照射して、粘着シート2の粘着力を弱め、疑似ウェーハ29を粘着シート2から剥離する。この場合、紫外線27の照射に代えて、加熱により剥離することもできる。

次に、図4(g)に示すように、チップ部品3、3Aの電極5が上になるように疑似ウェーハ29をひっくり返す。そして感光性絶縁膜28aを全面に塗布し、しかる後、チップ部品3、3Aの電極5の上部を開口する。この場合、感光性絶縁膜28としては400nm(短波長)で光を吸収する感光性絶縁樹脂をスピンコートし、400nmの光を用いたフォトプロセスで開口し、後述する配線はセミアディティブ法で形成する。

即ち、全面にTi/Cu等のシードメタル(図示省略)を形成後、図4(h)に示すように、レジストマスク32を形成してCu電界めっきを行い配線7を形成する。しかる後に、レジストマスク32の除去及びシードメタル膜エッチング(いずれも図示省略)を行う。そして、配線7の形成と同時に、配線7と同じ材料を用いてアライメントマーク14を形成する。

次に、図4(i)に示すように、上記した感光性絶縁膜28aと同様の感光性絶縁樹脂を全面にスピンコートして感光性絶縁膜28bを形成し、更に上記と同様に400nmの光を用いたフォトプロセスにより、配線7の上部の感光性絶縁膜28bを開口して外部接続端子34を形成する。

これにより、400nmの光に感光されていない部分の感光性絶縁膜28aと28bとの層間に存在する形でアライメントマーク14が形成される。従って、透明なガラス基板30に接して感光性絶縁膜28a、28bが設けられ、この感光性絶縁膜28aと28bの中に位置するアライメントマーク14が、後述する位置合せの際に検出し易くなる。

以上のプロセスを経た後に、図4(i)における切断線33の位置で切断する。従って、チップ部品3、3Aは樹脂4で保護されており、ガラス基板30の位置で切断するので、チップ部品3、3Aにはダメージを与えることがなく、個片化後のハンドリングが容易となる。

このように、チップ部品3、3Aの支持体となる疑似ウェーハ29を光透過性の材料、即ちガラス基板30で形成し、アライメントマーク14を配線7と同一の材料を用いてこの配線7と同時に形成し、このアライメントマーク14の上下に400nmで感光する感光性絶縁膜28a28bを配することによって、光透過性の支持体及び感光性絶縁膜を通してアライメントが可能な光透過型アライメントを利用するのが本実施の形態(後述の実施の形態も同様。)の特長である。

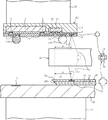

図7は、本実施の形態の実装方法を示す。図示の如く、図18に示した従来の実装方法とは異なり、位置合せ用のカメラ26を実装される半導体装置40のガラス基板30の上方に配置する。なお、本実施の形態においても、実装される半導体装置40は真空チャックで支持され、プリント配線板16も加熱ステージ上等に固定されるが図示省略する。

アライメントマークは従来と同様に十文字状に形成されている。即ち、カメラ26の領域の外側に示したように、半導体装置40のアライメントマーク14よりも一回り大きいマーク25がプリント配線板16に形成されており、カメラ26からの出射光L1が、一つは半導体装置40のアライメントマーク14に当たって反射する反射光L2をなし、他の一つはプリント配線板16のアライメントマーク25に当たって反射する反射光L2となり、これらの反射光L2によって双方のアライメントマーク14、25を光学的に検出して、補正しながら位置合せすることができる。勿論、図18に示した従来と同様な方法で位置合せすることも可能である。

図7(j)に示すように、実装に当っては半導体装置40の外部接続端子34にはんだボール12Aを形成し、不図示の真空チャックで半導体装置40を把持し、カメラ26からそれぞれのアライメントマーク14、25に対して光L1を出射してその反射光L2を検出しながら位置合せを行うが、既述したように、チップ部品3、3Aの支持体が透明なガラス基板30からなり、これに接する感光性絶縁膜28a、28bが400nmの短波長の光を吸収する感光性樹脂からなっている。

従って、位置合せ時には、約1μm(103nm)の長波長の赤外光L1をカメラ26から出射することにより、90%以上の透過率にて感光性絶縁膜28a、28bを通して、アライメント14及び15での赤外光L1の反射光L2を検出することができる。しかし、透過率は95〜96%が好ましいため、透過率が十分でない場合は、赤外光L1として更に長波長の光を選ぶか、若しくは感光性絶縁膜28a、28bの界面の調整又は材質の選択により透過率を高めることができる。

更に、本実施の形態は、従来のように位置合せ後にカメラを外すことなしで、双方のアライメントマーク14、25をカメラ26によって位置合せしながら半導体装置40を接近させ、はんだボール12Aをプリント配線板16の外部接続端子17に接触させ、外部接続端子17の表面に配された不図示のはんだペーストにはんだボール12Aが粘着し、仮固定後もカメラ26を用いて位置合せができるため、従来よりも更に精度良く位置合せができる。そして位置合せ終了後は、この状態のプリント配線板16及び半導体装置40は、従来と同様な治具を用いて不図示のリフロー炉に搬入される。

図7(k)は実装完了の状態を示しており、実装された半導体装置40はリフロー後のはんだ12を介して、半導体装置40の外部接続端子34とプリント配線板16の外部接続端子17とが接続される。

本実施の形態によれば、チップ部品3、3Aが樹脂4を介して、ガラス基板30の欠除部31においてこのガラス基板に一体化されているので、樹脂4の領域が小さく形成されるため、硬化収縮による樹脂4の変形は小さいことにより、チップ部品3、3Aの位置精度を保つことができると共に、配線7等の形成も疑似ウェーハレベルで一括処理後に、疑似ウェーハからガラス基板30の位置で切断して個片化できることにより、チップ部品3、3Aが樹脂4で保護され、ガラス基板30に一体化されているため、個片化の際にチップ部品3、3Aがダメージを受けることもなく、個片化後のハンドリングも容易である。

更に、半導体装置40をプリント配線板16上に仮固定した状態で、半導体装置40のアライメントマーク14とプリント配線板16のアライメントマーク25とを、ガラス基板30を通して、カメラ26からの出射光L1の各アライメントマーク14、25での反射光L2を検出し、双方のアライメントマーク14、25を容易かつ高精度に位置合せできるため、半導体装置40をプリント配線板16に対して位置精度良く実装できる。

実施の形態2

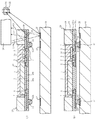

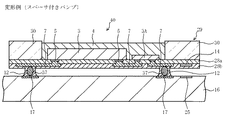

図8(a)は、本実施の形態の半導体装置及びその実装構造の概略断面図、図8(b)は同実施の形態の他の実装構造の概略断面図を示す。

図8(a)は、本実施の形態の半導体装置及びその実装構造の概略断面図、図8(b)は同実施の形態の他の実装構造の概略断面図を示す。

本実施の形態においても実施の形態1と同様に、支持体の材料としてガラスを使用していることにより、光学素子(PDやLD)を含むMCMの光実装においても、光透過型アライメントを利用して、半導体装置に形成されたアライメントマークと、光導波路に形成されたアライメントマークを透過アライメントして位置合せしながら、位置精度良くアライメントして実装することができる。

図示の如く、本実施の形態の半導体装置41及び半導体装置41Aも、その基本構造は実施の形態1と同様であり、記述した作製プロセス(図2〜図6参照)により形成されるので、半導体装置41、41Aの作製プロセスの説明は省略する。

しかし、本実施の形態において配置されているチップ部品が、半導体装置41は半導体チップ3に対して例えばLD(レーザダイオード)又はLED(発光ダイオード)10が配され、半導体装置41Aは半導体チップ3に対して例えばPD(フォトダイオード)23が配され、双方が光導波路20を介して光信号を送受信する平置構造のMCMとして構成されている。

従って、半導体装置41のLD又はLED(以下、LDと称する。)10の発光部11に対向する位置に光導波路20の光入射部20aが配され、入射光が反射面20bで反射し、光導波路20のコア層22内で導波されて反対側の反射面20bで反射し、この反射光が光導波路20の光出射部20cから出射して半導体装置41AのPD23の受光部24に入射するように、この受光部24に対向する位置に光導波路20の光出射部20cが配置されている。

このように、半導体装置41、41Aを光導波路20と組み合せたMCM構造においては、各半導体装置41、41Aの光導波路20に対する位置精度は極めて重要であるため、上記した実施の形態1と同様に形成された半導体装置41、41Aのアライメントマーク14と、光導波路20に形成されたアライメントマーク19との正確な位置合せが必要であり、この位置合せが実施の形態1と同様に光透過型アライメントを利用することにより、良好に実施することができる。

図8(a)は、このような構成の半導体装置41、41Aが、はんだ12を介してプリント配線板16の外部接続端子17に対して接続された状態であるが、これと同様な構成の半導体装置41、41Aをメタルポスト43及びはんだバンプ44を介してプリント配線板16の外部接続端子17に接続し、図8(b)のような構造で実装することもできる。いずれも、スペーサ35を介して半導体装置41、41Aとプリント配線板16との距離が100μmに規制されている構造となっている。

図9〜図11によりその実装プロセスを説明する。なお、本実施の形態の半導体装置41、41Aも、チップ部品3、10及び23も樹脂4で保護されており、ガラス基板30の位置で切断されるので、これらのチップ部品がダメージを受けることはなく、個片化後のハンドリングが容易である。

まず、図9(a)は実装基板としてのプリント配線板16及びその外部接続端子17を示し、このプリント配線板16の上面に、図9(b)に示すように光導波路20が不図示の接着剤を介して所定位置に貼り付けられる。なお、図9〜図11においては各部の構造を明示するために、上記した図8における左半分(即ち、半導体装置41側に対応する部分)を図示し、これとほぼ対称的な右半分は図示省略する。

次に、図10(a)に示すように、プリント配線板16上の所定場所にスペーサ35の材料として、熱硬化性樹脂(例えばエポキシ樹脂)を滴下する。図10(b)はこの平面図を示しており、この図において、大小の四角形に仮想線で示す領域30は実装する半導体装置41のガラス基板30の位置を示し、例えば内側の仮想線の角部(4ヶ所)に実線で示す符号35の位置に、図10(a)に示したスペーサ35は滴下されるものであるが、図10(a)においては簡略図示している。なお、このスペーサ35は図10(b)に仮想線にて示したように、例えば3ヶ所に設けてもよい。

次は図11(a)に示すように、実装する半導体装置41をこの上方から徐々に近づけ、カメラ26を用いて双方のアライメントマークを位置合せしながら位置合せ終了後にリフロー炉に搬入されるが、実施の形態1と同じ要領で行われるので、同様な位置合せ動作等の説明は省略する。

しかしこの場合、半導体装置41のアライメントマーク14は実施の形態1と同様に形成されているが、実施の形態1におけるプリント配線板16側のアライメントマークはなく、光導波路20に設けられたアライメントマーク19に対して半導体装置41のアライメントマーク14が位置合せされる。なお、この場合も図18で説明した従来の方法で位置合せすることも可能である。

本実施の形態の場合、光導波路20の光入射部20aを通して反射面20bとLDチップ10の発光部11との位置が一致することが最も重要であり、この位置決めの方法としては、従来(図18)と同様に、光導波路20のアライメントマーク19と、この光導波路20の先端側の上面の不図示の光入射部20aとの距離Dと、半導体装置41のアライメントマーク14とLDチップ10の発光部分11との距離Dとは同一であるので、双方のアライメントマーク14と19とを位置合せし、補正しながら実装することにより、LDチップ10の発光部11が自動的に光導波路20の光入射部20aの位置に一致する。

従って、光導波路20の光入射部20aから入射するLDチップ10の発光部11の出射光は、光導波路20のコア層22の45°傾斜の反射面20bで反射し、コア層22内を全反射しながら反対側の不図示の半導体装置41A側へ導波される。

プリント配線板16に滴下されたスペーサ35となる熱硬化性樹脂は、150〜200℃での数秒で硬化するため、半導体装置41の外部接続端子7aに設けられたはんだボール12Aのリフロー時の熱によっても変形せず、図11(b)に示すように実装を完了するまではスペーサ35として機能する。又、この熱硬化性樹脂はリフロー時のはんだボール12Aのセルフアライメント効果も抑えることにもなり、半導体装置41とプリント配線板16及び光導波路20の上面との距離、及び反射面20bとLDチップ10の発光部11との位置が一定に保たれた状態で、半導体装置41とプリント配線板16とは、はんだ12を介して接続され、不図示の右側の半導体装置41A側も同時にして実装を完了する。

本実施の形態によれば、上記した実施の形態1と同様に、チップ部品3、10、23が樹脂4を介して、ガラス基板30の欠除部31においてこのガラス基板30に一体化されているので、樹脂4の領域が小さく形成されるため、硬化収縮による樹脂4の変形は小さくなることにより、チップ部品3、10、23の位置精度を保つことができると共に、配線7等の形成も疑似ウェーハレベルで一括処理後に、疑似ウェーハからガラス基板30の位置で切断して個片化できることにより、チップ部品3、10、23が樹脂4で保護され、ガラス基板30に一体化されているため、個片化の際にチップ部品3、10、23がダメージを受けることもなく、個片化後のハンドリングも容易である。

更に、半導体装置41、41Aをプリント配線板16上に仮固定した状態で、半導体装置41、41Aのアライメントマーク14とプリント配線板16のアライメントマーク19とを、ガラス基板30を通して、カメラ26からの出射光L1の各アライメントマーク14、19での反射光L2を検出し、双方のアライメントマーク14、19を容易かつ高精度に位置合せできるため、半導体装置41、41Aをプリント配線板16に対して位置精度良く実装できる。

図12は、プリント配線板16に複数の半導体装置が実装された状態の一例を示す。上記した実施の形態1による半導体装置40及び実施の形態2による半導体41、41Aは、図示の如く、同一のプリント配線板16上に不図示の他の電子部品等と共に、混載して実装することもできる。

図13は、上記した実施の形態1による実装構造の変形例を示す。上記した各実施の形態における半導体装置とプリント配線板との接続方法としては、図示の如く、樹脂核37入りのはんだ12を用いてもよい。この場合、リフロー前のはんだボールは、内部に樹脂核37入りのはんだボールの直径を150μm程度とすることにより、リフロー後は半導体装置とプリント配線板との距離を100μmに形成することができる。これは実施の形態2にも適用できる。

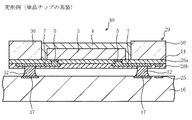

図14は他の変形例を示す。上記した各実施の形態は、種類の異なる複数のチップ部品をワンパッケージ化した半導体装置の実装であるが、図14に示すように、単品のチップ部品の実装にも上記実施の形態は適用することができる。

図15は、更に他の変形例を示すものであり、図5及び図6に示したガラス基板30は、一部分または全部を例えば図15に示すガラス基板30aのように作製してもよい。即ち、例えば図5における欠除部31を2個連続したような欠除部31a(図15(a)におけるA1、A2及びB1からB2に亘る領域の欠除部31a)、または図5における欠除部31を4個合せたような欠除部31b(図15(a)におけるC1からC2に亘る領域の欠除部31b)のように形成することもできる。

図15(a)において交差する直線の仮想線は切断線50を示し、実施の形態1に説明したプロセス(図3〜図4参照)を経て、この欠除部31a、31bに配したチップ部品を樹脂4で覆った後に、この切断線50で切断して個片化することにより、図15(a)におけるA1、A2、B1、B2領域のA及びB区域では、図15(b)に示すように、3辺がガラス基板30aで囲まれた半導体装置が得られる。

また、図15(a)におけるC1、C2領域のA及びB区域では、図15(c)に示すように、2辺がガラス基板30bで囲まれた半導体装置が得られ、いずれも樹脂4の塗布領域が小さくなることにより、樹脂4の硬化収縮によるチップ部品の位置ずれ等を抑えることができる。

上記した各実施の形態は、本発明の技術的思想に基づいて種々に変形できる。

例えば、半導体装置の作製プロセス終了後は、図4(i)に示すように、ガラス基板30の位置で切断し、半導体装置に個片化するとしたが、例えば、図8のように、光導波路20と組み合せて2個の半導体装置41、41Aを隣接して実装するものである場合、光導波路20との寸法関係等の条件が合えば、図5又は図6に示したガラス基板30の隣接した欠除部において、予め半導体装置41、41Aを配設しておくことにより、双方の間で切断することなしに、半導体装置41、41Aを連結して形成でき、連結された半導体装置41、41Aを用いて実装することもできる。また、これに限らず、他の半導体装置40同士でも条件が合えば適用可能である。

また、実施の形態に示した各部の構造や形状及び材料等も適宜に変更してもよい。

1…石英基板、2…粘着シート、3、3A…半導体チップ、4…樹脂、

5…電極パッド、7…配線、7a、17、34…外部接続端子、10…LD又はLED、

11…発光部、12…はんだ、12A…はんだボール、

13、14、19、25…アライメントマーク、16…プリント配線板、

20…光導波路、20a…光入射部、20b…反射面、20c…光出射部、

21…クラッド層、22…コア層、23…FD、24…受光部、26…カメラ、

27…紫外線、28a、28b…感光性絶縁膜、29…疑似ウェーハ、

30…ガラス基板、31…欠除部、32…レジストマスク、33…切断線、

35…スペーサ、37…樹脂核、40、41、41A…半導体装置、

43…メタルポスト、44…はんだバンプ、50…切断線、B…個片領域、D…距離、

L1…出射光、L2…反射光

5…電極パッド、7…配線、7a、17、34…外部接続端子、10…LD又はLED、

11…発光部、12…はんだ、12A…はんだボール、

13、14、19、25…アライメントマーク、16…プリント配線板、

20…光導波路、20a…光入射部、20b…反射面、20c…光出射部、

21…クラッド層、22…コア層、23…FD、24…受光部、26…カメラ、

27…紫外線、28a、28b…感光性絶縁膜、29…疑似ウェーハ、

30…ガラス基板、31…欠除部、32…レジストマスク、33…切断線、

35…スペーサ、37…樹脂核、40、41、41A…半導体装置、

43…メタルポスト、44…はんだバンプ、50…切断線、B…個片領域、D…距離、

L1…出射光、L2…反射光

Claims (55)

- 一方の面に電極が設けられたチップ部品と、このチップ部品の電極面以外の少なくとも側面を覆う保護物質とによって構成された半導体装置において、

前記チップ部品の側方に設けられた光透過性の支持体に、前記保護物質を介して前記 チップ部品が一体化されていることを特徴とする、半導体装置。 - 前記支持体が前記チップ部品の外周囲の少なくとも2辺に設けられている、請求項1に記載した半導体装置。

- 前記支持体が前記チップ部品の外周囲全体に亘って設けられている、請求項2に記載した半導体装置。

- 前記支持体が耐熱性及び機械的強度の良好な材料からなる、請求項1に記載した半導体装置。

- 前記支持体が、低線膨張であると共に、熱変形が小さく、寸法安定性のある材料からなっている、請求項4に記載した半導体装置。

- 前記支持体としてガラスが用いられている、請求項5に記載した半導体装置。

- 前記支持体の領域に位置合せ用のマークが形成されている、請求項1に記載した半導体装置。

- 前記位置合せ用のマークが、前記チップ部品の前記電極から引き出された配線と同一の配線材料によって形成されている、請求項7に記載した半導体装置。

- 前記配線の上下に設けられた絶縁層が光透過性である、請求項8に記載した半導体装置。

- 前記チップ部品が、光学素子チップを含む複数の半導体チップからなる、請求項1に記載した半導体装置。

- 前記チップ部品が、実装基板に接続される、請求項1に記載した半導体装置。

- 一方の面に電極が設けられたチップ部品と、このチップ部品の電極面以外の少なくとも側面を覆う保護物質とによって構成された半導体装置を製造する方法において、

光透過性の材料からなる支持体の近傍位置にチップ部品を配置する工程と、

前記チップ部品の少なくとも側面を覆うようにして前記支持体と前記チップ部品との 間を保護物質で一体化する工程と

を有することを特徴とする、半導体装置の製造方法。 - 基体上に前記支持体を固定すると共に電極面を下にして前記チップ部品を固定し、前記保護物質を前記支持体と前記チップ部品との間に充填して前記チップ部品の少なくとも前記電極面以外を覆い、前記保護物質によって前記チップ部品が一体化された前記支持体からなる疑似ウェーハを前記基体から分離した後、前記疑似ウェーハを切断して各半導体装置に個片化する、請求項12に記載した半導体装置の製造方法。

- 前記基体上に粘着手段を介して前記支持体及び前記チップ部品を固定し、これらを前記保護物質で一体化した後に、前記疑似ウェーハを前記基体から分離する、請求項13に記載した半導体装置の製造方法。

- 前記基体上に、前記チップ部品配置用のアライメントマークを形成した後に、前記粘着手段を介して前記支持体及び前記チップ部品を貼り付けて固定する、請求項14に記載した半導体装置の製造方法。

- 前記支持体を前記チップ部品の外周囲の少なくとも2辺に設ける、請求項12に記載した半導体装置の製造方法。

- 前記支持体を前記チップ部品の外周囲全体を囲むように設ける、請求項16に記載した半導体装置の製造方法。

- 前記支持体を耐熱性及び機械的強度の良好な材料によって形成する、請求項12に記載した半導体装置の製造方法。

- 前記支持体を、低線膨張であると共に、熱変形が小さく、寸法安定性のある材料によって形成する、請求項18に記載した半導体装置の製造方法。

- 前記支持体としてガラスを用いる、請求項19に記載した半導体装置の製造方法。

- 前記支持体の領域に位置合せ用のマークを形成する、半導体装置の製造方法。

- 前記位置合せ用のマークを、前記チップ部品の前記電極から引き出された配線と同一の配線材料によって形成する、請求項21に記載した半導体装置の製造方法。

- 前記配線の上下に光透過性の絶縁層を形成する、請求項22に記載した半導体装置の製造方法。

- 前記チップ部品として、光学素子チップを含む複数の半導体チップを配置する、請求項12に記載した半導体装置の製造方法。

- 前記チップ部品を実装基板に接続される構造とする、請求項12に記載した半導体装置の製造方法。

- 特性測定により良品と判定された前記チップ部品を有する前記疑似ウェーハを作製する、請求項12に記載した半導体装置の製造方法。

- 前記疑似ウェーハの状態において前記チップ部品の特性測定を行い、良品のチップ部品を選択する、請求項12に記載した半導体装置の製造方法。

- 一方の面に電極が設けられたチップ部品と、このチップ部品の電極面以外の少なくとも側面を覆う保護物質と、この保護物質によって前記チップ部品と一体化された光透過性の支持体とによって構成されている、疑似ウェーハ。

- 請求項2〜11のいずれか1項に記載した半導体装置を製造するのに用いられる、請求項28に記載した疑似ウェーハ。

- 一方の面に電極が設けられたチップ部品と、このチップ部品の電極面以外の少なくとも側面を覆う保護物質とによって構成された半導体装置を製造するのに用いる疑似ウェーハの製造方法において、

光透過性の材料からなる支持体の近傍位置にチップ部品を配置する工程と、

前記チップ部品の少なくとも側面を覆うようにして前記支持体と前記チップ部品との 間を保護物質で一体化する工程と

によって、前記保護物質で前記チップ部品が前記支持体と一体化されてなる疑似ウェーハを得る、疑似ウェーハの製造方法。 - 基体上に前記支持体を固定すると共に電極面を下にして前記チップ部品を固定し、前記保護物質を前記支持体と前記チップ部品との間に充填して前記チップ部品の少なくとも前記電極面以外を覆い、前記保護物質によって前記チップ部品が一体化された前記支持体からなる疑似ウェーハを前記基体から分離した後、前記疑似ウェーハを切断して各半導体装置に個片化する、請求項12に記載した疑似ウェーハの製造方法。

- 前記基体上に粘着手段を介して前記支持体及び前記チップ部品を固定し、これらを前記保護物質で一体化した後に、前記疑似ウェーハを前記基体から分離する、請求項31に記載した疑似ウェーハの製造方法。

- 前記基体上に、前記チップ部品配置用のアライメントマークを形成した後に、前記粘着手段を介して前記支持体及び前記チップ部品を貼り付けて固定する、請求項32に記載した疑似ウェーハの製造方法。

- 前記支持体を前記チップ部品の外周囲の少なくとも2辺に設ける、請求項30に記載した疑似ウェーハの製造方法。

- 前記支持体を前記チップ部品の外周囲全体に亘って設ける、請求項34に記載した疑似ウェーハの製造方法。

- 前記支持体を耐熱性及び機械的強度の良好な材料によって形成する、請求項30に記載した疑似ウェーハの製造方法。

- 前記支持体を、低線膨張であると共に、熱変形が小さく、寸法安定性のある材料によって形成する、請求項36に記載した疑似ウェーハの製造方法。

- 前記支持体としてガラスを用いる、請求項37に記載した疑似ウェーハの製造方法。

- 前記支持体の領域に位置合せ用のマークを形成する、請求項30に記載した疑似ウェーハの製造方法。

- 前記位置合せ用のマークを、前記チップ部品の前記電極から引き出された配線と同一の配線材料によって形成する、請求項39に記載した疑似ウェーハの製造方法。

- 前記配線の上下に光透過性の絶縁層を形成する、請求項40に記載した疑似ウェーハの製造方法。

- 前記チップ部品として、光学素子チップを含む複数の半導体チップを配置する、請求項30に記載した疑似ウェーハの製造方法。

- 前記チップ部品を実装基板に接続される構造とする、請求項30に記載した疑似ウェーハの製造方法。

- 特性測定により良品と判定された前記チップ部品を有する前記疑似ウェーハを作製する、請求項30に記載した疑似ウェーハの製造方法。

- 前記疑似ウェーハの状態において前記チップ部品の特性測定を行い、良品のチップ部品を選択する、請求項30に記載した疑似ウェーハの製造方法。

- 請求項1に記載した半導体装置を回路基板に実装した実装構造であって、前記支持体を通して光学的に検出される位置合せ用のマークが、前記半導体装置と前記回路基板との双方に設けられている、半導体装置の実装構造。

- 請求項2〜11のいずれか1項に記載した半導体装置が実装されている、請求項46に記載した半導体装置の実装構造。

- 前記チップ部品としての光学素子チップに対向して前記回路基板に光導波路が固定され、この光導波路に前記位置合せ用のマークが設けられている、請求項46に記載した半導体装置の実装構造。

- 前記回路基板上に設けられたスペーサ材を介して前記半導体装置が実装されている、請求項46に記載した半導体装置の実装構造。

- 前記スペーサ材が熱硬化性樹脂からなる、請求項49に記載した半導体装置の実装構造。

- 請求項1に記載した半導体装置を回路基板に実装する方法であって、前記半導体装置と前記回路基板との双方に位置合せ用のマークを設け、前記支持体を通して前記位置合せ用のマークを光学的に検出して、前記回路基板に対し前記半導体装置を位置合せして実装する、半導体装置の実装方法。

- 請求項2〜11のいずれか1項に記載した半導体装置を実装する、請求項41に記載した半導体装置の実装方法。

- 前記チップ部品としての光学素子チップに対向して前記回路基板に光導波路を固定し、この光導波路に前記位置合せ用のマークを設ける、請求項51に記載した半導体装置の実装方法。

- 前記回路基板上に設けられたスペーサ材を介して前記半導体装置を実装する、請求項51に記載した半導体装置の実装方法。

- 熱硬化性樹脂を前記回路基板上に付着させ、前記半導体装置の実装時に前記熱硬化性樹脂を硬化させる、請求項54に記載した半導体装置の実装方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004105835A JP2005294444A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置及びその製造方法、疑似ウェーハ及びその製造方法、並びに半導体装置の実装構造及びその実装方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004105835A JP2005294444A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置及びその製造方法、疑似ウェーハ及びその製造方法、並びに半導体装置の実装構造及びその実装方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005294444A true JP2005294444A (ja) | 2005-10-20 |

Family

ID=35327059

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004105835A Pending JP2005294444A (ja) | 2004-03-31 | 2004-03-31 | 半導体装置及びその製造方法、疑似ウェーハ及びその製造方法、並びに半導体装置の実装構造及びその実装方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005294444A (ja) |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007155562A (ja) * | 2005-12-07 | 2007-06-21 | Acrorad Co Ltd | 放射線画像検出モジュールおよび放射線画像検出装置 |

| JP2007155561A (ja) * | 2005-12-07 | 2007-06-21 | Acrorad Co Ltd | 放射線画像検出モジュールおよび放射線画像検出装置 |

| JP2008216794A (ja) * | 2007-03-06 | 2008-09-18 | Furukawa Electric Co Ltd:The | 光結合器 |

| JP2010105153A (ja) * | 2008-10-28 | 2010-05-13 | Honeywell Internatl Inc | Mems装置およびマイクロエレクトロメカニカルシステム(mems)を組み立てる方法 |

| JP2011176297A (ja) * | 2010-01-27 | 2011-09-08 | Ricoh Co Ltd | 撮像モジュール及びその製造方法並びに撮像装置 |

| JP2012188555A (ja) * | 2011-03-10 | 2012-10-04 | Sumitomo Bakelite Co Ltd | 半導体装置および半導体装置の製造方法 |

| WO2013042364A1 (ja) * | 2011-09-20 | 2013-03-28 | 日本電気株式会社 | 光伝送モジュール |

| JP2014089394A (ja) * | 2012-10-31 | 2014-05-15 | Kyocera Corp | 光装置用基板および光装置 |

| JP2016092220A (ja) * | 2014-11-05 | 2016-05-23 | 日立化成株式会社 | ケイ素を含む基板及びそれを用いた半導体装置並びに半導体装置の製造方法 |

| JP2020166189A (ja) * | 2019-03-29 | 2020-10-08 | 日東電工株式会社 | 光素子付き光電気混載基板およびその製造方法 |

-

2004

- 2004-03-31 JP JP2004105835A patent/JP2005294444A/ja active Pending

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007155562A (ja) * | 2005-12-07 | 2007-06-21 | Acrorad Co Ltd | 放射線画像検出モジュールおよび放射線画像検出装置 |

| JP2007155561A (ja) * | 2005-12-07 | 2007-06-21 | Acrorad Co Ltd | 放射線画像検出モジュールおよび放射線画像検出装置 |

| JP2008216794A (ja) * | 2007-03-06 | 2008-09-18 | Furukawa Electric Co Ltd:The | 光結合器 |

| JP2010105153A (ja) * | 2008-10-28 | 2010-05-13 | Honeywell Internatl Inc | Mems装置およびマイクロエレクトロメカニカルシステム(mems)を組み立てる方法 |

| JP2011176297A (ja) * | 2010-01-27 | 2011-09-08 | Ricoh Co Ltd | 撮像モジュール及びその製造方法並びに撮像装置 |

| JP2012188555A (ja) * | 2011-03-10 | 2012-10-04 | Sumitomo Bakelite Co Ltd | 半導体装置および半導体装置の製造方法 |

| WO2013042364A1 (ja) * | 2011-09-20 | 2013-03-28 | 日本電気株式会社 | 光伝送モジュール |

| JP2014089394A (ja) * | 2012-10-31 | 2014-05-15 | Kyocera Corp | 光装置用基板および光装置 |

| JP2016092220A (ja) * | 2014-11-05 | 2016-05-23 | 日立化成株式会社 | ケイ素を含む基板及びそれを用いた半導体装置並びに半導体装置の製造方法 |

| JP2020166189A (ja) * | 2019-03-29 | 2020-10-08 | 日東電工株式会社 | 光素子付き光電気混載基板およびその製造方法 |

| JP7408292B2 (ja) | 2019-03-29 | 2024-01-05 | 日東電工株式会社 | 光素子付き光電気混載基板およびその製造方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| USRE41369E1 (en) | Semiconductor device and method of manufacturing the same | |

| TWI353045B (ja) | ||

| US7534656B2 (en) | Image sensor device and method of manufacturing the same | |

| KR100657117B1 (ko) | 집적회로장치 및 그 제조방법 | |

| US4862249A (en) | Packaging system for stacking integrated circuits | |

| US5138145A (en) | Method for producing image sensors with current flow into chip and with simplified chip mounting | |

| JP6395600B2 (ja) | 撮像装置の製造方法および半導体装置の製造方法 | |

| US7457490B2 (en) | Micro-optics on optoelectronics | |

| CN1568546B (zh) | 半导体器件及其制造方法 | |

| US7443028B2 (en) | Imaging module and method for forming the same | |

| US20080191335A1 (en) | Cmos image sensor chip scale package with die receiving opening and method of the same | |

| JP2005033141A (ja) | 半導体装置及びその製造方法、疑似ウェーハ及びその製造方法、並びに半導体装置の実装構造 | |

| JP2002368160A (ja) | ウェーハレベルパッケージ及びその製造方法 | |

| TW201405764A (zh) | 晶圓堆疊之組裝 | |

| CN107808887A (zh) | 光学装置及其制造方法 | |

| EP1251557B1 (en) | Method of manufacturing semiconductor devices and semiconductor device | |

| US7615408B2 (en) | Method of manufacturing semiconductor device | |

| JP2005294444A (ja) | 半導体装置及びその製造方法、疑似ウェーハ及びその製造方法、並びに半導体装置の実装構造及びその実装方法 | |

| JP2004363279A (ja) | 光電変換装置の製造方法、並びにその製造に用いる疑似ウェーハの製造方法 | |

| JP2004342862A (ja) | 半導体装置及びその製造方法、疑似ウェーハ及びその製造方法、並びにマルチチップモジュール | |

| US7391576B2 (en) | Manufacturing of optical units for semiconductor packages with optical sensors | |

| JP4234270B2 (ja) | 半導体装置の製造方法 | |

| JP4020618B2 (ja) | 半導体装置およびその製造方法 | |

| JP2003197659A (ja) | チップ状電子部品及びその製造方法、並びにその製造に用いる疑似ウェーハ及びその製造方法 | |

| JP2574559B2 (ja) | イメージセンサの製造方法 |