JP2004228317A - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP2004228317A JP2004228317A JP2003013801A JP2003013801A JP2004228317A JP 2004228317 A JP2004228317 A JP 2004228317A JP 2003013801 A JP2003013801 A JP 2003013801A JP 2003013801 A JP2003013801 A JP 2003013801A JP 2004228317 A JP2004228317 A JP 2004228317A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- operation mode

- transistor

- external terminal

- detection circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 14

- 238000001514 detection method Methods 0.000 claims description 41

- 230000015556 catabolic process Effects 0.000 abstract description 17

- 229910021420 polycrystalline silicon Inorganic materials 0.000 abstract 1

- 229920005591 polysilicon Polymers 0.000 abstract 1

- 238000010586 diagram Methods 0.000 description 7

- 238000000034 method Methods 0.000 description 4

- 239000002184 metal Substances 0.000 description 3

- 230000000694 effects Effects 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 230000005685 electric field effect Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/08—Functional testing, e.g. testing during refresh, power-on self testing [POST] or distributed testing

- G11C29/12—Built-in arrangements for testing, e.g. built-in self testing [BIST] or interconnection details

- G11C29/46—Test trigger logic

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/50—Marginal testing, e.g. race, voltage or current testing

- G11C2029/5004—Voltage

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Tests Of Electronic Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Non-Volatile Memory (AREA)

- Semiconductor Memories (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

- Read Only Memory (AREA)

Abstract

【課題】テスト動作モードでの端子リーク電流を低減した半導体記憶装置の提供。

【解決手段】動作モードでの端子リーク電流を低減するために、テスト用外部端子に接続した静電気的なノイズが印加した時ICを保護するための保護トランジスタのゲート電極となるポリシリコン層をドレイン端にオーバーラップさせたレイアウトにし静電耐圧保護トランジスタのブレークダウン電圧を向上させることを特徴としている。

【選択図】 図1

【解決手段】動作モードでの端子リーク電流を低減するために、テスト用外部端子に接続した静電気的なノイズが印加した時ICを保護するための保護トランジスタのゲート電極となるポリシリコン層をドレイン端にオーバーラップさせたレイアウトにし静電耐圧保護トランジスタのブレークダウン電圧を向上させることを特徴としている。

【選択図】 図1

Description

【0001】

【発明の属する技術分野】

本発明は、半導体記憶装置に関し、特に、電気的に書き換え可能な不揮発性半導体メモリ集積回路(以下、EEPROMとする)に関する。また、通常動作モードとは異なるテスト用動作モードを備えており、所定の外部端子に通常動作モードで推奨する電圧以上の電圧を印加することでテスト用動作モードに切り替えることのできる回路を備えた半導体記憶装置に関する。

【0002】

【従来技術の説明】

半導体記憶装置において、外部端子に高電圧を印加することによってテスト用動作モードに切り替わる機能を有するものが存在する。ここで示した高電圧とは、通常動作モードで印加する範囲の電源電圧より高い電圧を示しており、たとえば該ICの最大動作電源電圧が5Vであるならば、5V超の電圧を示しており一般的には10V程度の電圧を印加するものである。

【0003】

該機能を実現するために、高電圧を検出するための電圧検出回路を内蔵している。前述の例においては該電圧検出回路の検出電圧を5V超10V未満(一般的には9V)となるよう設定することで所定の外部端子に10Vの電圧を印加することで電圧検出回路が検出信号を出力しテスト用動作モードに切り替えることができる。検出電圧は最大動作電源電圧の仕様、使用する半導体プロセスのデバイス特性により決定するため前述の例以外の電圧条件となることも考えられる。

【0004】

高電圧を印加する外部端子は、テスト用動作モードを検出することを唯一の目的とし他の機能を有しない専用の端子である。また、該外部端子は電源電圧印加端子であり、電源電圧印加の目的とテスト用動作モードに切り替えるための電圧検出機能を兼用する端子とすることも可能である。また、該外部端子は入力端子または出力端子または入出力端子であり、該端子に割り当てられた機能とテスト用動作モードに切り替えるための電圧検出機能を兼用する端子とすることも可能である(例えば、特許文献1参照。)。

【0005】

【特許文献1】

特開2002−15599号公報 (第2−4貢、第1図)

【0006】

【発明が解決しようとする課題】

従来のテスト用動作モード検出のため電圧検出回路は以下のような問題がある。

【0007】

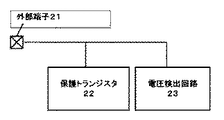

図2はテスト用動作モード検出機能を有した外部端子21、テスト用動作モード用電圧検出回路23、静電気的なノイズが印加した時にICを保護するための保護トランジスタ22を示したブロック図である。

【0008】

図3は一般的な従来の電圧検出回路を示す回路図である。テスト用動作モードに切り替えるために高電圧を印加するパッド31、n個のNMOSトランジスタ32、抵抗33、インバータ34から構成されている。パッド31とグランド電圧との間に直列にNMOSトランジスタ32と抵抗33が接続されており、抵抗33のハイ電圧側がインバータ34の入力となっている。この回路ではパッド31に直列接続されたn段分のNMOSトランジスタ32の閾値電圧の合計(n×Vth)よりも高い電圧が印加されるとインバータ34が反転し、出力はHレベルからLレベルに変化しテスト用動作モードに切り替わる。

【0009】

図2に示した保護トランジスタ22は、一般的にNMOSでありゲート電圧とソース電圧をグランド、ドレイン電圧をパッドに接続したオフトランジスタである。該保護トランジスタのMOS構造は電圧検出回路で用いたNMOSトランジスタよりもオフトランジスタのドレインブレークダウン耐圧が低いMOS構造のトランジスタを用いることによって、保護すべき内部トランジスタより先に保護トランジスタでブレークダウンし内部回路を保護する機能を有している。

【0010】

該保護トランジスタのドレイン電圧は、前述のとおり電圧検出回路のパッドに接続されたNMOSのドレインにも接続されている。

【0011】

このため保護トランジスタのドレインブレークダウン耐圧は、電圧検出回路の検出電圧よりも低い電圧に設定する必要がある。仮に検出電圧を保護トランジスタのドレインブレークダウン耐圧より高く設定した場合、該ブレークダウン耐圧以上の電圧を印加しても保護トランジスタでブレークダウンを起こし、ブレークダウン耐圧以上の電圧はかからないため電圧検出回路は検出することができず、それはすなわちテスト用動作モードに切り替えることができないことを示している。

【0012】

図4は、パッドに印加する電圧と電圧検出回路の直列に接続したNMOSトランジスタに流れる電流の関係を示したグラフである。

【0013】

パッドに電圧を印加する電圧を高くすると電圧に応じた電流が電圧検出回路に流れ、検出電圧(n×Vth)を印加すると前述のとおりテスト用動作モードに切り替わる。検出電圧より低い電圧では検出電流より少ない電流が電圧検出回路には流れる。

【0014】

通常動作モードの電源電圧範囲において、該電流は端子のリーク電流となり一般的に該リーク電流はEEPROMのIC仕様として一定電流値以下にする必要がある。特に低温時においてリーク電流は大きくなることから通常動作モードでの電源電圧範囲におけるリーク電流は製品として重要な要素となるものである。

【0015】

さらに検出電圧を高くすると最大動作電圧におけるリーク電流は少なくなり、検出電圧を低くすると最大動作電圧におけるリーク電流は多くなる。つまりリーク電流を少なくするためにはできる限り検出電圧を高く設定することが不可欠である。

【0016】

該電圧検出回路の設定可能な検出電圧の上限は、前記保護用オフトランジスタのドレインブレークダウン耐圧によって制限されるため該ドレインブレークダウン耐圧を高くする必要がある。

【0017】

しかし、該ドレインブレークダウン耐圧はMOSのゲート酸化膜厚やドレインの拡散濃度、フィールドの濃度をはじめとする半導体プロセスによって決定されるものであり、既に形成された半導体プロセスを使用する場合において容易にドレインブレークダウン耐圧のみを高くすることは不可能である。

【0018】

リーク電流が多くなる問題は、動作温度範囲が広く、特に低温で動作可能なICにおいて問題となる場合が多い。

【0019】

また、通常動作モードでの電源電圧範囲が広く、特に最大動作電圧の高いICにおいて問題になる場合が多い。

【0020】

また、保護トランジスタとして使用するオフトランジスタのドレインブレークダウン耐圧が低い場合、特に問題となる場合が多い。

【0021】

また、電圧検出回路を構成するNMOSトランジスタのサブスレッショルド電流が多い場合、特に問題になることが多い。

【0022】

【課題を解決するための手段】

そこで本発明は、上記問題を解決するために以下の手段を用いた。

本願発明にかかる半導体記憶装置は、テスト用動作モードに切り換える為の電圧が印加される外部端子と、前記外部端子と接地電位間に接続された保護トランジスタと、前記外部端子の電圧を検出し、テスト用動作モードに切り換える信号を出力する電圧検出回路と、を有し、前記保護トランジスタは、ドレイン領域がゲート電極で囲まれていることを特徴とする。

【0023】

さらに、前記電圧検出回路は、前記外部端子と接地電位の間に直列に接続された複数のMOSトランジスタを有し、前記直列に接続されたMOSトランジスタ間の接続点から前記信号を出力するものであり、前記外部端子に接続された前記MOSトランジスタは高耐圧MOSトランジスタであることを特徴とする。

【0024】

【本発明の実施の形態】

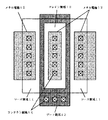

本発明の実施の形態を説明する。図1は、ドレインブレークダウン耐圧を高くすることを目的とした保護トランジスタの平面図である。

【0025】

図1に記したトランジスタは電気的にメタル電極12に接続されたゲート電極13により電気的に分離されたドレイン領域10とソース領域11にそれぞれコンタクト14を配置し、ドレイン領域10とソース領域11を、それぞれコンタクト14を介してメタル電極12に接続して所望の電気特性を得るものである。

【0026】

このトランジスタは外部端子に直接接続されているため、外部からのノイズが直接印加されノイズ耐性に優れた特性を有する。

【0027】

本発明ではドレイン領域10をゲート電極13で囲んだ構成とした。本構成を用いることによりドレイン領域10と素子分離領域との電気的な分離は、チャネル長方向端部のゲート電極13の電界効果を有するジャンクションダイオードで保たれているため、ノイズや静電気の電流経路の均一性が得られている。これによりドレインブレークダウン耐圧を向上させることができる。

【0028】

テスト用動作モードの切り替えを用とした電圧検出回路が備えられた外部端子の保護トランジスタに本発明によるトランジスタレイアウトを採用することにより、該電圧検出回路の検出電圧を高く設定することができ、延いては端子リーク電流を低減させた回路を実現することができるものである。

【0029】

本発明は、保護トランジスタのゲート領域となるレイアウトを変更する簡易な修正により、結果として端子リーク電流を容易な手段にて実現することが可能である。半導体プロセスのプロセスバイアスを一切変更することがなく目的を達成できる。

【0030】

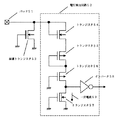

図5に、本発明を適用した実施例を示す。図5はテスト用動作モードに切り替えるための高電圧を印加する外部端子51、該外部端子51に接続した静電気的なノイズが印加した時ICを保護するための保護トランジスタ52、テスト用動作モードに切り替えるための高電圧を検出するための電圧検出回路53で構成している。

【0031】

電圧検出回路53は、外部端子にNMOSトランジスタ54のドレインが接続されており、該NMOSトランジスタ54のソースには飽和結線されたPMOSトランジスタ55が接続されており、該PMOSトランジスタ55のドレインにはPMOSトランジスタ56が接続されており、該PMOSトランジスタ56のゲート電圧はグランドである。該PMOSトランジスタ56のドレインはNMOSデプレッショントランジスタ57が接続され該NMOSデプレッショントランジスタ57のゲート電圧はグランドであり、一定電流59を流すことができる。PMOSトランジスタ56は、NMOSトランジスタ54とPMOSトランジスタ55とによって発生する電圧分がバックゲート電圧となりPMOSトランジスタ56の閾値電圧は高くなる。外部端子にバックゲート効果分を考慮したPMOSトランジスタ56の閾値以上の電圧を印加するとPMOSトランジスタ56にオン電流が流れる。該オン電流が前記一定電流59よりも大きくなると、インバータ58の出力はHレベルからLレベルに変化し、テスト用動作モードに切り替わる。

【0032】

NMOSトランジスタ54は高耐圧MOSで構成されており、該トランジスタのドレインジャンクションブレークダウン耐圧は一般的に20V程度と高い。

【0033】

前記保護トランジスタ52は低耐圧MOSで構成されており、一般的には該トランジスタのドレインジャンクションブレークダウン耐圧は12V程度である。本発明によるレイアウト構成を使用した保護トランジスタを用いることによりドレインジャンクションブレークダウン耐圧は1Vあるいは3V程度向上させることができる。

【0034】

【発明の効果】

以上、本願発明によれば、テスト動作モードでの端子リーク電流を低減した半導体記憶装置の提供が可能となる。

【図面の簡単な説明】

【図1】本発明の保護トランジスタ平面図を示す図である。

【図2】本発明の構成するブロック図を示す図である。

【図3】従来の電圧検出回路を示す図である。

【図4】電圧検出回路の特性グラフを示す図である。

【図5】本発明の実施の形態1の構成を示す図である。

【符号の説明】

11 ソース領域

12 メタル電極

13 ゲート領域

14 コンタクト領域

【発明の属する技術分野】

本発明は、半導体記憶装置に関し、特に、電気的に書き換え可能な不揮発性半導体メモリ集積回路(以下、EEPROMとする)に関する。また、通常動作モードとは異なるテスト用動作モードを備えており、所定の外部端子に通常動作モードで推奨する電圧以上の電圧を印加することでテスト用動作モードに切り替えることのできる回路を備えた半導体記憶装置に関する。

【0002】

【従来技術の説明】

半導体記憶装置において、外部端子に高電圧を印加することによってテスト用動作モードに切り替わる機能を有するものが存在する。ここで示した高電圧とは、通常動作モードで印加する範囲の電源電圧より高い電圧を示しており、たとえば該ICの最大動作電源電圧が5Vであるならば、5V超の電圧を示しており一般的には10V程度の電圧を印加するものである。

【0003】

該機能を実現するために、高電圧を検出するための電圧検出回路を内蔵している。前述の例においては該電圧検出回路の検出電圧を5V超10V未満(一般的には9V)となるよう設定することで所定の外部端子に10Vの電圧を印加することで電圧検出回路が検出信号を出力しテスト用動作モードに切り替えることができる。検出電圧は最大動作電源電圧の仕様、使用する半導体プロセスのデバイス特性により決定するため前述の例以外の電圧条件となることも考えられる。

【0004】

高電圧を印加する外部端子は、テスト用動作モードを検出することを唯一の目的とし他の機能を有しない専用の端子である。また、該外部端子は電源電圧印加端子であり、電源電圧印加の目的とテスト用動作モードに切り替えるための電圧検出機能を兼用する端子とすることも可能である。また、該外部端子は入力端子または出力端子または入出力端子であり、該端子に割り当てられた機能とテスト用動作モードに切り替えるための電圧検出機能を兼用する端子とすることも可能である(例えば、特許文献1参照。)。

【0005】

【特許文献1】

特開2002−15599号公報 (第2−4貢、第1図)

【0006】

【発明が解決しようとする課題】

従来のテスト用動作モード検出のため電圧検出回路は以下のような問題がある。

【0007】

図2はテスト用動作モード検出機能を有した外部端子21、テスト用動作モード用電圧検出回路23、静電気的なノイズが印加した時にICを保護するための保護トランジスタ22を示したブロック図である。

【0008】

図3は一般的な従来の電圧検出回路を示す回路図である。テスト用動作モードに切り替えるために高電圧を印加するパッド31、n個のNMOSトランジスタ32、抵抗33、インバータ34から構成されている。パッド31とグランド電圧との間に直列にNMOSトランジスタ32と抵抗33が接続されており、抵抗33のハイ電圧側がインバータ34の入力となっている。この回路ではパッド31に直列接続されたn段分のNMOSトランジスタ32の閾値電圧の合計(n×Vth)よりも高い電圧が印加されるとインバータ34が反転し、出力はHレベルからLレベルに変化しテスト用動作モードに切り替わる。

【0009】

図2に示した保護トランジスタ22は、一般的にNMOSでありゲート電圧とソース電圧をグランド、ドレイン電圧をパッドに接続したオフトランジスタである。該保護トランジスタのMOS構造は電圧検出回路で用いたNMOSトランジスタよりもオフトランジスタのドレインブレークダウン耐圧が低いMOS構造のトランジスタを用いることによって、保護すべき内部トランジスタより先に保護トランジスタでブレークダウンし内部回路を保護する機能を有している。

【0010】

該保護トランジスタのドレイン電圧は、前述のとおり電圧検出回路のパッドに接続されたNMOSのドレインにも接続されている。

【0011】

このため保護トランジスタのドレインブレークダウン耐圧は、電圧検出回路の検出電圧よりも低い電圧に設定する必要がある。仮に検出電圧を保護トランジスタのドレインブレークダウン耐圧より高く設定した場合、該ブレークダウン耐圧以上の電圧を印加しても保護トランジスタでブレークダウンを起こし、ブレークダウン耐圧以上の電圧はかからないため電圧検出回路は検出することができず、それはすなわちテスト用動作モードに切り替えることができないことを示している。

【0012】

図4は、パッドに印加する電圧と電圧検出回路の直列に接続したNMOSトランジスタに流れる電流の関係を示したグラフである。

【0013】

パッドに電圧を印加する電圧を高くすると電圧に応じた電流が電圧検出回路に流れ、検出電圧(n×Vth)を印加すると前述のとおりテスト用動作モードに切り替わる。検出電圧より低い電圧では検出電流より少ない電流が電圧検出回路には流れる。

【0014】

通常動作モードの電源電圧範囲において、該電流は端子のリーク電流となり一般的に該リーク電流はEEPROMのIC仕様として一定電流値以下にする必要がある。特に低温時においてリーク電流は大きくなることから通常動作モードでの電源電圧範囲におけるリーク電流は製品として重要な要素となるものである。

【0015】

さらに検出電圧を高くすると最大動作電圧におけるリーク電流は少なくなり、検出電圧を低くすると最大動作電圧におけるリーク電流は多くなる。つまりリーク電流を少なくするためにはできる限り検出電圧を高く設定することが不可欠である。

【0016】

該電圧検出回路の設定可能な検出電圧の上限は、前記保護用オフトランジスタのドレインブレークダウン耐圧によって制限されるため該ドレインブレークダウン耐圧を高くする必要がある。

【0017】

しかし、該ドレインブレークダウン耐圧はMOSのゲート酸化膜厚やドレインの拡散濃度、フィールドの濃度をはじめとする半導体プロセスによって決定されるものであり、既に形成された半導体プロセスを使用する場合において容易にドレインブレークダウン耐圧のみを高くすることは不可能である。

【0018】

リーク電流が多くなる問題は、動作温度範囲が広く、特に低温で動作可能なICにおいて問題となる場合が多い。

【0019】

また、通常動作モードでの電源電圧範囲が広く、特に最大動作電圧の高いICにおいて問題になる場合が多い。

【0020】

また、保護トランジスタとして使用するオフトランジスタのドレインブレークダウン耐圧が低い場合、特に問題となる場合が多い。

【0021】

また、電圧検出回路を構成するNMOSトランジスタのサブスレッショルド電流が多い場合、特に問題になることが多い。

【0022】

【課題を解決するための手段】

そこで本発明は、上記問題を解決するために以下の手段を用いた。

本願発明にかかる半導体記憶装置は、テスト用動作モードに切り換える為の電圧が印加される外部端子と、前記外部端子と接地電位間に接続された保護トランジスタと、前記外部端子の電圧を検出し、テスト用動作モードに切り換える信号を出力する電圧検出回路と、を有し、前記保護トランジスタは、ドレイン領域がゲート電極で囲まれていることを特徴とする。

【0023】

さらに、前記電圧検出回路は、前記外部端子と接地電位の間に直列に接続された複数のMOSトランジスタを有し、前記直列に接続されたMOSトランジスタ間の接続点から前記信号を出力するものであり、前記外部端子に接続された前記MOSトランジスタは高耐圧MOSトランジスタであることを特徴とする。

【0024】

【本発明の実施の形態】

本発明の実施の形態を説明する。図1は、ドレインブレークダウン耐圧を高くすることを目的とした保護トランジスタの平面図である。

【0025】

図1に記したトランジスタは電気的にメタル電極12に接続されたゲート電極13により電気的に分離されたドレイン領域10とソース領域11にそれぞれコンタクト14を配置し、ドレイン領域10とソース領域11を、それぞれコンタクト14を介してメタル電極12に接続して所望の電気特性を得るものである。

【0026】

このトランジスタは外部端子に直接接続されているため、外部からのノイズが直接印加されノイズ耐性に優れた特性を有する。

【0027】

本発明ではドレイン領域10をゲート電極13で囲んだ構成とした。本構成を用いることによりドレイン領域10と素子分離領域との電気的な分離は、チャネル長方向端部のゲート電極13の電界効果を有するジャンクションダイオードで保たれているため、ノイズや静電気の電流経路の均一性が得られている。これによりドレインブレークダウン耐圧を向上させることができる。

【0028】

テスト用動作モードの切り替えを用とした電圧検出回路が備えられた外部端子の保護トランジスタに本発明によるトランジスタレイアウトを採用することにより、該電圧検出回路の検出電圧を高く設定することができ、延いては端子リーク電流を低減させた回路を実現することができるものである。

【0029】

本発明は、保護トランジスタのゲート領域となるレイアウトを変更する簡易な修正により、結果として端子リーク電流を容易な手段にて実現することが可能である。半導体プロセスのプロセスバイアスを一切変更することがなく目的を達成できる。

【0030】

図5に、本発明を適用した実施例を示す。図5はテスト用動作モードに切り替えるための高電圧を印加する外部端子51、該外部端子51に接続した静電気的なノイズが印加した時ICを保護するための保護トランジスタ52、テスト用動作モードに切り替えるための高電圧を検出するための電圧検出回路53で構成している。

【0031】

電圧検出回路53は、外部端子にNMOSトランジスタ54のドレインが接続されており、該NMOSトランジスタ54のソースには飽和結線されたPMOSトランジスタ55が接続されており、該PMOSトランジスタ55のドレインにはPMOSトランジスタ56が接続されており、該PMOSトランジスタ56のゲート電圧はグランドである。該PMOSトランジスタ56のドレインはNMOSデプレッショントランジスタ57が接続され該NMOSデプレッショントランジスタ57のゲート電圧はグランドであり、一定電流59を流すことができる。PMOSトランジスタ56は、NMOSトランジスタ54とPMOSトランジスタ55とによって発生する電圧分がバックゲート電圧となりPMOSトランジスタ56の閾値電圧は高くなる。外部端子にバックゲート効果分を考慮したPMOSトランジスタ56の閾値以上の電圧を印加するとPMOSトランジスタ56にオン電流が流れる。該オン電流が前記一定電流59よりも大きくなると、インバータ58の出力はHレベルからLレベルに変化し、テスト用動作モードに切り替わる。

【0032】

NMOSトランジスタ54は高耐圧MOSで構成されており、該トランジスタのドレインジャンクションブレークダウン耐圧は一般的に20V程度と高い。

【0033】

前記保護トランジスタ52は低耐圧MOSで構成されており、一般的には該トランジスタのドレインジャンクションブレークダウン耐圧は12V程度である。本発明によるレイアウト構成を使用した保護トランジスタを用いることによりドレインジャンクションブレークダウン耐圧は1Vあるいは3V程度向上させることができる。

【0034】

【発明の効果】

以上、本願発明によれば、テスト動作モードでの端子リーク電流を低減した半導体記憶装置の提供が可能となる。

【図面の簡単な説明】

【図1】本発明の保護トランジスタ平面図を示す図である。

【図2】本発明の構成するブロック図を示す図である。

【図3】従来の電圧検出回路を示す図である。

【図4】電圧検出回路の特性グラフを示す図である。

【図5】本発明の実施の形態1の構成を示す図である。

【符号の説明】

11 ソース領域

12 メタル電極

13 ゲート領域

14 コンタクト領域

Claims (2)

- 動作モードを切り換える為の電圧が印加される外部端子と、

前記外部端子と接地電位間に接続された保護トランジスタと、

前記外部端子の電圧を検出し、所定の電圧以上であれば第1の動作モードから第2の動作モードに切り換える信号を出力する電圧検出回路と、を有し、

前記保護トランジスタは、ドレイン領域がゲート電極で囲まれていることを特徴とする半導体記憶装置。 - 前記電圧検出回路は、前記外部端子と接地電位の間に直列に接続された複数のMOSトランジスタを有し、

前記直列に接続されたMOSトランジスタ間の接続点から前記信号を出力するものであり、前記外部端子に接続された前記MOSトランジスタは高耐圧MOSトランジスタであることを特徴とする請求項1に記載の半導体記憶装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003013801A JP2004228317A (ja) | 2003-01-22 | 2003-01-22 | 半導体記憶装置 |

| CNB2004100059035A CN100538911C (zh) | 2003-01-22 | 2004-01-21 | 半导体存储器件 |

| US10/761,954 US6980475B2 (en) | 2003-01-22 | 2004-01-21 | Semiconductor memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003013801A JP2004228317A (ja) | 2003-01-22 | 2003-01-22 | 半導体記憶装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2004228317A true JP2004228317A (ja) | 2004-08-12 |

Family

ID=32866192

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003013801A Withdrawn JP2004228317A (ja) | 2003-01-22 | 2003-01-22 | 半導体記憶装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6980475B2 (ja) |

| JP (1) | JP2004228317A (ja) |

| CN (1) | CN100538911C (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009210448A (ja) * | 2008-03-05 | 2009-09-17 | Toshiba Corp | 半導体装置 |

| CN101930982A (zh) * | 2010-07-07 | 2010-12-29 | 中国电子科技集团公司第五十八研究所 | 基于flotox结构的抗辐射eeprom存储单元结构 |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009141278A (ja) * | 2007-12-10 | 2009-06-25 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US9082739B2 (en) | 2013-05-16 | 2015-07-14 | Samsung Electronics Co., Ltd. | Semiconductor device having test structure |

| KR102124628B1 (ko) * | 2013-05-16 | 2020-06-19 | 삼성전자주식회사 | 반도체 장치의 테스트 구조체 |

| JP2019054102A (ja) * | 2017-09-14 | 2019-04-04 | 東芝メモリ株式会社 | 記憶装置およびその製造方法 |

| CN110364522B (zh) * | 2018-03-26 | 2021-10-08 | 瑞昱半导体股份有限公司 | 能保护低电压元件的电路架构 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS55149871A (en) * | 1978-07-31 | 1980-11-21 | Fujitsu Ltd | Line voltage detector |

| KR100272164B1 (ko) * | 1997-12-30 | 2000-11-15 | 윤종용 | 모드레지스터셋회로를갖는반도체장치 |

| US6081466A (en) * | 1998-10-30 | 2000-06-27 | Stmicroelectronics, Inc. | Stress test mode entry at power up for low/zero power memories |

| JP2002033000A (ja) * | 2000-07-14 | 2002-01-31 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP4257486B2 (ja) * | 2002-02-14 | 2009-04-22 | Okiセミコンダクタ株式会社 | Dramの電源制御装置 |

-

2003

- 2003-01-22 JP JP2003013801A patent/JP2004228317A/ja not_active Withdrawn

-

2004

- 2004-01-21 US US10/761,954 patent/US6980475B2/en not_active Expired - Lifetime

- 2004-01-21 CN CNB2004100059035A patent/CN100538911C/zh not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009210448A (ja) * | 2008-03-05 | 2009-09-17 | Toshiba Corp | 半導体装置 |

| CN101930982A (zh) * | 2010-07-07 | 2010-12-29 | 中国电子科技集团公司第五十八研究所 | 基于flotox结构的抗辐射eeprom存储单元结构 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20040165451A1 (en) | 2004-08-26 |

| CN100538911C (zh) | 2009-09-09 |

| CN1542859A (zh) | 2004-11-03 |

| US6980475B2 (en) | 2005-12-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6573566B2 (en) | Low-voltage-triggered SOI-SCR device and associated ESD protection circuit | |

| JP4402109B2 (ja) | 低電圧nmos型静電気放電クランプ | |

| US5341003A (en) | MOS semiconductor device having a main unit element and a sense unit element for monitoring the current in the main unit element | |

| JP3639596B2 (ja) | 保護形スイッチ | |

| US5760630A (en) | Input protection circuit having load resistor implemented by p-channel MIS transistor | |

| JP3164065B2 (ja) | 半導体装置 | |

| US20080246345A1 (en) | Semiconductor Switch Arrangement and an Electronic Device | |

| US6469352B2 (en) | Two-terminal semiconductor overcurrent limiter | |

| US20130076400A1 (en) | Comparator circuit | |

| US6778366B2 (en) | Current limiting protection circuit | |

| US7733133B2 (en) | Power switch circuit having variable resistor coupled between input terminal and output transistor and changing its resistance based on state of output transistor | |

| US20030043517A1 (en) | Electro-static discharge protecting circuit | |

| JP2004228317A (ja) | 半導体記憶装置 | |

| CN110085583B (zh) | 半导体器件和操作方法 | |

| US9293451B2 (en) | Integrated circuit electrical protection device | |

| US5942931A (en) | Circuit for protecting an IC from noise | |

| CN101236965B (zh) | 半导体集成电路装置 | |

| JP3431127B2 (ja) | 電子装置および電子スイッチ装置 | |

| US7723794B2 (en) | Load driving device | |

| US20250015075A1 (en) | Semiconductor apparatus | |

| JP2007095848A (ja) | 半導体装置 | |

| US20090302397A1 (en) | Field-Effect Transistor | |

| JP2003338555A (ja) | 電子スイッチ装置及びその製造方法 | |

| JP3187773B2 (ja) | 入力保護素子を備えた半導体装置 | |

| JP2004032251A (ja) | アナログスイッチ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050809 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080313 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090324 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20090512 |