CN1210773C - 除去剩余光致抗蚀剂和残留侧壁钝化物的原位后蚀刻方法 - Google Patents

除去剩余光致抗蚀剂和残留侧壁钝化物的原位后蚀刻方法 Download PDFInfo

- Publication number

- CN1210773C CN1210773C CNB008191689A CN00819168A CN1210773C CN 1210773 C CN1210773 C CN 1210773C CN B008191689 A CNB008191689 A CN B008191689A CN 00819168 A CN00819168 A CN 00819168A CN 1210773 C CN1210773 C CN 1210773C

- Authority

- CN

- China

- Prior art keywords

- etching

- substrate

- chamber

- containing layer

- metal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000002161 passivation Methods 0.000 title claims abstract description 72

- 238000000034 method Methods 0.000 title claims abstract description 28

- 230000008569 process Effects 0.000 title claims description 8

- 229920002120 photoresistant polymer Polymers 0.000 title description 13

- 239000007789 gas Substances 0.000 claims abstract description 63

- 229910052751 metal Inorganic materials 0.000 claims abstract description 49

- 239000002184 metal Substances 0.000 claims abstract description 49

- 239000001301 oxygen Substances 0.000 claims abstract description 21

- 229910052760 oxygen Inorganic materials 0.000 claims abstract description 21

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 claims abstract description 20

- 238000005530 etching Methods 0.000 claims description 163

- 239000000758 substrate Substances 0.000 claims description 39

- 238000005260 corrosion Methods 0.000 claims description 28

- 230000007797 corrosion Effects 0.000 claims description 28

- 238000001816 cooling Methods 0.000 claims description 13

- 230000015572 biosynthetic process Effects 0.000 claims description 7

- VIKNJXKGJWUCNN-XGXHKTLJSA-N norethisterone Chemical compound O=C1CC[C@@H]2[C@H]3CC[C@](C)([C@](CC4)(O)C#C)[C@@H]4[C@@H]3CCC2=C1 VIKNJXKGJWUCNN-XGXHKTLJSA-N 0.000 claims description 5

- 102100029469 WD repeat and HMG-box DNA-binding protein 1 Human genes 0.000 claims description 4

- 101710097421 WD repeat and HMG-box DNA-binding protein 1 Proteins 0.000 claims description 4

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 abstract description 14

- 229910052786 argon Inorganic materials 0.000 abstract description 7

- 239000000203 mixture Substances 0.000 abstract 1

- 239000000126 substance Substances 0.000 description 30

- 239000004065 semiconductor Substances 0.000 description 20

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 10

- 229910052782 aluminium Inorganic materials 0.000 description 10

- 239000004411 aluminium Substances 0.000 description 9

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 4

- PNEYBMLMFCGWSK-UHFFFAOYSA-N Alumina Chemical compound [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 3

- VEXZGXHMUGYJMC-UHFFFAOYSA-M Chloride anion Chemical compound [Cl-] VEXZGXHMUGYJMC-UHFFFAOYSA-M 0.000 description 3

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical group Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 3

- 239000000654 additive Substances 0.000 description 3

- 230000000996 additive effect Effects 0.000 description 3

- 239000001307 helium Substances 0.000 description 3

- 229910052734 helium Inorganic materials 0.000 description 3

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 3

- 238000009616 inductively coupled plasma Methods 0.000 description 3

- 238000001020 plasma etching Methods 0.000 description 3

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Chemical compound O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 3

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- 206010071232 Protuberant ear Diseases 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 239000001257 hydrogen Substances 0.000 description 2

- 229910052739 hydrogen Inorganic materials 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 239000003595 mist Substances 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- FAQYAMRNWDIXMY-UHFFFAOYSA-N trichloroborane Chemical compound ClB(Cl)Cl FAQYAMRNWDIXMY-UHFFFAOYSA-N 0.000 description 2

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical group F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 1

- OLBVUFHMDRJKTK-UHFFFAOYSA-N [N].[O] Chemical compound [N].[O] OLBVUFHMDRJKTK-UHFFFAOYSA-N 0.000 description 1

- AZDRQVAHHNSJOQ-UHFFFAOYSA-N alumane Chemical group [AlH3] AZDRQVAHHNSJOQ-UHFFFAOYSA-N 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 235000019628 coolness Nutrition 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- -1 oxygen free radical Chemical class 0.000 description 1

- SFZCNBIFKDRMGX-UHFFFAOYSA-N sulfur hexafluoride Chemical compound FS(F)(F)(F)(F)F SFZCNBIFKDRMGX-UHFFFAOYSA-N 0.000 description 1

- 229960000909 sulfur hexafluoride Drugs 0.000 description 1

- TXEYQDLBPFQVAA-UHFFFAOYSA-N tetrafluoromethane Chemical compound FC(F)(F)F TXEYQDLBPFQVAA-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/3065—Plasma etching; Reactive-ion etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02041—Cleaning

- H01L21/02057—Cleaning during device manufacture

- H01L21/02068—Cleaning during device manufacture during, before or after processing of conductive layers, e.g. polysilicon or amorphous silicon layers

- H01L21/02071—Cleaning during device manufacture during, before or after processing of conductive layers, e.g. polysilicon or amorphous silicon layers the processing being a delineation, e.g. RIE, of conductive layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31127—Etching organic layers

- H01L21/31133—Etching organic layers by chemical means

- H01L21/31138—Etching organic layers by chemical means by dry-etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02041—Cleaning

- H01L21/02043—Cleaning before device manufacture, i.e. Begin-Of-Line process

- H01L21/02054—Cleaning before device manufacture, i.e. Begin-Of-Line process combining dry and wet cleaning steps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32133—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only

- H01L21/32135—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only

- H01L21/32136—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only using plasmas

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Power Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Plasma & Fusion (AREA)

- Drying Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Removal Of Specific Substances (AREA)

Abstract

一种在单个蚀刻室内进行金属蚀刻、蚀刻掩模剥离以及除去残留侧壁钝化物的方法。晶片放置在蚀刻室内。对晶片进行金属蚀刻。将例如氧气和氩气的混合气体的剥离气体提供到蚀刻室,并激发形成氧等离子体。氧等离子体从晶片剥离掉蚀刻掩模并除去残留侧壁钝化物。氧等离子体也清洁了蚀刻室。

Description

发明背景

本发明涉及半导体器件的制造。具体地,本发明涉及金属蚀刻和剥离剩余光致抗蚀剂和残留侧壁钝化物的改进技术。

在某些类型的半导体器件,例如使用铝互连的半导体器件的制造中,在金属蚀刻装置中蚀刻例如铝或钛等的金属层,留下残留的侧壁钝化物和剩余光致抗蚀剂。

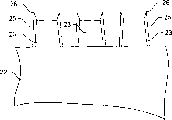

为便于讨论,图1为现有技术蚀刻工具10的示意图,包括负载锁定12,金属蚀刻室14,剥离室16以及冷却台18。

具有设置在蚀刻掩模(例如光致抗蚀剂掩模或硬模)下金属层的半导体晶片放置在负载锁定12中,负载锁定12能使半导体晶片进入蚀刻工具10同时保持蚀刻工具10中的真空。在本例中,蚀刻掩模为光致抗蚀剂掩模。晶片从负载锁定12传送到金属蚀刻室14,室14用于金属蚀刻。这种蚀刻室,例如反应离子蚀刻室,通常产生等离子体进行蚀刻。在金属蚀刻期间,蚀刻室14例如使用Cl2和BCl3(三氯化硼)作为蚀刻气体。根据蚀刻的特性也可以添加例如N2或CHF3等的添加剂。

在一些现有技术的反应离子金属蚀刻室14中,使与晶片相邻的电极偏置在晶片上产生电位,将等离子体静电吸引到晶片,增强了蚀刻。这种蚀刻室往往具有1到20毫乇(mT)数量级的内部压力。等离子体蚀刻掉没有被蚀刻掩模保护的那部分金属层,形成金属互连。蚀刻方法由重新沉积的蚀刻产物形成的残留侧壁钝化物。

然后半导体晶片由蚀刻室14传送到剥离室16。剥离室16可以是后续等离子体装置,距晶片较远地产生等离子体,并用等离子体产生的离子蚀刻半导体晶片。剥离室16往往工作在1乇数量级的压力下,通常远高于金属蚀刻室14中的压力。剥离室16除去光致抗蚀剂掩模。在现有技术中,一些剥离室通过将晶片暴露到水蒸气等离子体形成腐蚀保护提供腐蚀钝化。

图2为半导体晶片22的部分剖面图,为已蚀刻铝层形成铝互连23之后,并且半导体晶片22已进行了蚀刻掩模剥离和腐蚀钝化之后形成的衬底。重新沉积的蚀刻金属残留物沉积在铝互连23和光致抗蚀剂掩模的侧面形成残留侧壁钝化物25。对于铝互连,残留侧壁钝化物由重新沉积的蚀刻残留物形成,为氯化物或氟化物形式的铝。当铝残留物暴露到氧,形成氧化铝,在常规的剥离室中很难除去。剥离光致抗蚀剂掩模之后,与光致抗蚀剂掩模相邻的部分残留侧壁钝化物保留,形成“蝙蝠耳”26。在其它工序中,“蝙蝠耳”很薄以至掉下来形成“遮盖物”。

由于残留侧壁钝化物25主要由例如铝或钛的无机材料组成,因此在许多情况中,剥离室16不能除去残留侧壁钝化物25。

然后半导体晶片22由剥离室16传送到冷却台18,在此半导体晶片22冷却。然后半导体晶片22由冷却台18再回到负载锁定12,以便将半导体晶片22从蚀刻工具10移走,同时保持蚀刻工具10中的真空。半导体晶片22从蚀刻工具10传送到湿化学槽20,在槽20中晶片接触蚀刻性化学药品除去了部分残留侧壁钝化物25。EKC265和ACT935为在湿化学槽中使用以剥离残留侧壁钝化物25的化学药品的例子。

湿化学槽维护很昂贵。消耗的化学药品和操作和处理时对环境的考虑也增加了化学槽的成本。随着要除去的残留量的增加,消耗的化学药品的量也增加。

目前的蚀刻工具,例如可以由California的Fremont的LAMResearch Corp.买到的TCPTM9600PTX金属蚀刻系统,将两个感应耦合等离子体蚀刻室与两个微波剥离室组合在一起。每个蚀刻室需要等离子体源,每个剥离室需要等离子体源,这增加了蚀刻工具的成本和复杂性。在TCPTM9600PTX金属蚀刻系统中,可取的是,在剥离室中,对于氧氮剥离,剥离工艺为60秒,对于90秒的整个工艺时间,水蒸气等离子体腐蚀钝化为30秒。

在现有技术中,蚀刻工具和湿化学槽中的处理时间包括蚀刻室中的蚀刻时间、剥离室中蚀刻掩模的剥离时间、剥离室中腐蚀钝化的时间、蚀刻室和剥离室之间的传送时间、以及在湿化学槽中除去残留侧壁钝化物的时间的总和。两个蚀刻室和两个剥离室之间的传送时间增加了处理时间。在现有技术中,在湿化学槽中除去残留侧壁钝化物的时间约20分钟。

由于BCl3与氧反应产生不易挥发的残留物,会污染蚀刻室,通常希望将氧从使用BCl3的蚀刻室中排除。

鉴于以上内容,希望提供一种改进的残留侧壁钝化物的除去方法。还希望提供一种较便宜的蚀刻工具。同时希望增加蚀刻工具的产量。

发明概述

在一个实施例中,本发明涉及一种方法,在蚀刻工具中的蚀刻室中,蚀刻金属层,剥离有机材料的蚀刻掩模,以及除去残留侧壁钝化物。通过在蚀刻室中氧等离子体或其它剥离等离子体进行剥离蚀刻掩模和除去侧壁钝化物。蚀刻室能在约30秒内剥离蚀刻掩模层和除去残留侧壁钝化物。在腐蚀钝化室中进行腐蚀钝化,腐蚀钝化室将晶片暴露到高温环境中的水蒸气。

在第二实施例中,本发明涉及蚀刻至少部分通过设置在衬底上的含金属层的方法,其中部分所述含金属层设置在蚀刻掩模下,部分所述含金属层没有设置在蚀刻掩模下,包括以下步骤:将衬底放置在蚀刻室中;使蚀刻气体流入蚀刻室内;由蚀刻室内的蚀刻气体产生等离子体;蚀刻掉没有设置在蚀刻掩模下那部分含金属层并形成残留侧壁钝化物;终止蚀刻气体流;使蚀刻掩模剥离气体流入蚀刻室内;由蚀刻室内的蚀刻掩模剥离气体产生等离子体;剥离掉蚀刻掩模并除去一些残留侧壁钝化物,同时衬底位于蚀刻室内;以及从蚀刻室移走衬底。

下面结合附图更详细地介绍本发明的这些和其它特点。

附图简介

在附图中,通过例子而不是限定性地图示本发明,其中类似的参考数字表示类似的元件,其中:

图1为现有技术的蚀刻工具的示意图;

图2为部分半导体晶片的剖面图;

图3为本发明优选实施例的示意图;以及

图4A和4B为本发明优选实施例中使用的工艺流程图。

优选实施例的详细描述

现在参考附图中示出的几个优选实施例详细地介绍本发明。在下面的说明中,陈述了大量的具体细节以便更彻底地理解本发明。然而,显然对于本领域的技术人员,可以不使用一些或全部具体细节也可以实施本发明。此外,公知的工艺步骤和/或结构没有详细地介绍以避免不必要地混淆本发明。

为便于讨论,图3示出了本发明的蚀刻工具30的示意图,包括一负载锁定32,一蚀刻室34,一腐蚀钝化室36以及一冷却台38。图4A和4B为下面介绍工艺的流程图。

在蚀刻工具30的操作中,衬底44放置在负载锁定32中,能使半导体晶片进入蚀刻工具30同时保持蚀刻工具30中的真空(步骤402)。在图3所示的本例中,衬底44为带有含金属层45的半导体晶片,其中部分含金属层设置在蚀刻掩模46下。晶片从负载锁定32传送到金属蚀刻室34(步骤404)。在优选实施例中,室34为反应离子蚀刻室。本发明的其它实施例可以使用具有等离子体产生装置的其它类型的蚀刻室。在优选实施例中,蚀刻室中的压力保持在1到80毫乇之间。更优选,蚀刻室中的压力保持在1到40毫乇之间。最好,蚀刻室中的压力保持在5到20毫乇之间。该压力比许多现有技术的剥离室中保持的压力都低。

蚀刻室34的蚀刻周期期间,蚀刻气体流入蚀刻室34内(步骤406)。在本发明的优选实施例中,蚀刻气体包括Cl2和BCl3(三氯化硼)。在其它实施例中,根据蚀刻的特性,也可以添加例如N2或CHF3等的添加剂。使用的蚀刻气体的量在现有技术中公知。

提供到蚀刻气体的电源为射频电源,感应地耦合到蚀刻气体产生等离子体(步骤408)。在优选实施例中,提供到蚀刻气体的电源在300和3,000瓦之间。更优选,提供到蚀刻气体的电源在300和1,500瓦之间。最好,提供到蚀刻气体的电源在600和1,000瓦之间。其它实施例使用其它方法将蚀刻气体转变为等离子体,例如使用微波电源或容性耦合。

偏置电压提供到吸盘,吸盘支撑衬底并在晶片设置有电位,由此将蚀刻气体产生的等离子体静电吸引到晶片(步骤410)。在优选实施例中,偏置电压在-10和-1,000伏之间。更优选,偏置电压在-25和-600伏之间。最好,偏置电压在-50和-400伏之间。由于偏置电压取决于多种因素,因此很容易测量偏置电源。在本发明的优选实施例中,偏置电源在10和800瓦之间。更优选,偏置电源在25和500瓦之间。最好,偏置电源在50和250瓦之间。

晶片温度保持在10到100℃(步骤412)。更优选,晶片保持在20到80℃的温度范围。最好,晶片保持在40到60℃的温度范围。

蚀刻气体的等离子体撞击晶片的表面,蚀刻掉没有在蚀刻掩模下面的那部分含金属层(步骤414)。蚀刻掉的部分含金属层的一些残留物重新沉积在含金属层上,形成残留侧壁钝化层。此外,来自蚀刻气体的残留物,例如碳基残留物和其它残留物,性质为有机,沉积在蚀刻室34的壁上。当含金属层充分蚀刻时,停止流动蚀刻气体(步骤416),蚀刻停止,完成了蚀刻周期。

然后开始剥离周期。在剥离周期期间,将蚀刻掩模剥离气体引入蚀刻室34内(步骤418)。在本发明的优选实施例中,剥离气体包括0到100%的氩气和0到100%的氧气。更优选,剥离气体包括0到50%的氩气和50到100%的氧气。最好,剥离气体包括0到10%的氩气和90到100%的氧气,例如,5%的氩气和95%的氧气。在一个实施例中,剥离气体包括氧气、氩气、四氟化碳、氦气、氦气、六氟化硫、氮气、氢气和氖气的单独气体或混合气体。剥离气体的优选混合气体为约70%到80%的氦气和约20到30%氧气或氮气与氢气。

在优选实施例中,提供到剥离气体的电源为射频电源,感应地耦合到剥离气体,由蚀刻室中的剥离气体产生等离子体(步骤420)。射频电源激发并电离氧,将氧转变为氧等离子体。在优选实施例中,提供到剥离气体的电源在300和3,000瓦之间。更优选,提供到剥离气体的电源在300和1,500瓦之间。最好,提供到剥离气体的电源在600和1,000瓦之间。在本发明的优选实施例中,泵入蚀刻气体中的电源量与泵入到剥离气体中的电源量相同,简化了工序。然而,在其它优选实施例中,泵入蚀刻气体中的电源量与泵入到剥离气体中的电源量不同。

偏置电压提供到支撑衬底的吸盘,由此将剥离气体产生的等离子体静电吸引到晶片(步骤422)。在优选实施例中,偏置电压在-10和-1,000伏之间。更优选,偏置电压在-100和-800伏之间。最好,偏置电压在-200和-600伏之间。由于偏置电压取决于多种因素,因此很容易测量偏置电源。在本发明的优选实施例中,偏置电源在50和1,500瓦之间。更优选,偏置电源在100和1,000瓦之间。最好,偏置电源在500和800瓦之间。在本发明的优选实施例中,蚀刻期间使用的偏置电压和偏置电源与剥离期间使用的偏置电压和偏置电源不同。然而,在其它的优选实施例中,蚀刻期间使用的偏置电压和偏置电源与剥离期间使用的偏置电压和偏置电源相同。

剥离期间,晶片温度优选保持在10到100℃(步骤424)。更优选,晶片保持在20到80℃的温度范围。最好,晶片保持在40到60℃的温度范围。在本发明的优选实施例中,蚀刻期间的晶片温度保持在约等于剥离期间的晶片温度,以简化工序。然而,在其它实施例中,蚀刻期间的晶片温度与剥离期间的晶片温度不同。

通过剥离气体产生的等离子体剥离掉蚀刻掩模,在本例中蚀刻掩模为光致抗蚀剂掩模(步骤426),以及大多数或所有的残留侧壁钝化物(步骤428)。由蚀刻室的等离子体源产生的激活氧自由基为剥离有机光致抗蚀剂层的主要成分。现已发现,氧等离子体从蚀刻室34的壁上清除掉了碳基残留物(步骤430),由此蚀刻室34自身清洁了同时光致抗蚀剂从蚀刻室34中的晶片上剥离。这种清洁减少了对附加清洁的需要。然后停止流动剥离气体。

接着晶片由蚀刻室34(步骤434)传送到腐蚀钝化室36(步骤436)。通过将晶片暴露到高温非等离子体水蒸气形成蚀刻保护提供腐蚀钝化(步骤S438)。本发明的一个方面提供了腐蚀钝化同时不使用等离子体源。现已发现,高温非等离子体水蒸气提供腐蚀钝化与利用后续等离子体源的腐蚀钝化基本相同的产量。腐蚀钝化室36的水蒸气和氯化物残留物形成HCl。高温驱走HCl,在氯化物与铝反应之前从铝表面除去氯化物,由此提供了腐蚀钝化。其它实施例采用使用水蒸气等离子体的腐蚀钝化室。

然后,晶片从腐蚀钝化室36传送到冷却台38(步骤440),在其中半导体晶片冷却(步骤442)。然后,半导体晶片由冷却台38传送回负载锁定32,同时保持蚀刻工具30中的真空。然后,半导体晶片由蚀刻工具30的负载锁定32(步骤446)传送到湿化学槽40(步骤448),在此晶片接触蚀刻性化学药品除去了任何残留侧壁钝化物。EKC265和ACT935为在湿化学槽中使用以剥离残留侧壁钝化物25的化学药品的例子。由于在蚀刻室中除去了大多数或所有的残留侧壁钝化物,因此晶片放置在化学槽中的时间比现有技术短很多。然后晶片从湿槽移走(步骤450)并进一步处理完成器件。

在本发明的优选实施例中,蚀刻工具和湿化学槽中的处理时间包括,蚀刻室中的蚀刻时间、蚀刻室中蚀刻掩模剥离和除去残留侧壁钝化物的时间、腐蚀钝化室中的腐蚀钝化时间、蚀刻室和腐蚀钝化室之间的传送时间、以及在湿化学槽中时间的总和。使用蚀刻室的优选实施例中的蚀刻掩模剥离时间小于现有技术剥离室中蚀刻掩模剥离时间。优选实施例的蚀刻室中的残留侧壁钝化物的除去时间通常远小于现有技术中湿化学槽中残留侧壁钝化物的除去时间。例如,优选实施例的蚀刻室中的残留侧壁钝化物的除去时间为30秒到1分钟的数量级,而现有技术中湿化学槽中残留侧壁钝化物的除去时间为20分钟的数量级。由于使用蚀刻室剥离残留侧壁钝化物,因此优选实施例的湿化学槽中的时间远小于现有技术中湿化学槽中的时间。例如,在优选实施例中,湿化学槽中的时间为5到10分钟的数量级,而现有技术中湿化学槽中的时间为20分钟的数量级。湿化学槽中时间缩短不仅增加了产量,而且减少了每个晶片消耗的化学药品量,可以不用频繁地补充化学药品或使用较小的槽尺寸。优选实施例的腐蚀钝化室中的腐蚀钝化时间与现有技术的剥离室中腐蚀钝化时间为相同数量级。

在本发明的优选实施例中,每个蚀刻工具30包括一单个负载锁定,一单个腐蚀钝化室、一单个冷却台以及至少三个蚀刻工具室。在本发明的另一实施例中,在蚀刻掩模剥离中使用纯氧。此外,使用单种气体可以更简化工艺。在另一实施例中,可以使用其它的添加剂代替氩气。

在其它实施例中,蚀刻工具包括一负载锁定,一蚀刻室和一冷却台,而没有腐蚀钝化室。在本发明的另一实施例中,不使用湿化学槽,除去残留侧壁钝化物的全部都在蚀刻室中进行。省却了湿化学槽提供了所需的干蚀刻方法,不再需要有害、缓慢并且昂贵的湿化学槽。

虽然参考几个优选实施例介绍了本发明,但在本发明的范围内可以修改、置换和等效。还应该注意有许多其它的方式能够实现本发明的方法和装置。因此,下面后附的权利要求书解释为包括所有落入本发明精神和范围内的所有这种修改、置换和等效。

Claims (16)

1.一种至少部分通过设置在衬底上的含金属层的蚀刻方法,其中部分所述含金属层设置在蚀刻掩模下,部分所述含金属层没有设置在蚀刻掩模下,包括以下步骤:

将衬底放置在蚀刻室中;

使蚀刻气体流入蚀刻室内;

由蚀刻室内的蚀刻气体产生等离子体;

蚀刻掉没有设置在蚀刻掩模下那部分含金属层,其中一些蚀刻掉的含金属层重新淀积,以形成残留侧壁钝化物,而衬底位于蚀刻室内;

使蚀刻气体停止流入蚀刻室;

使蚀刻掩模剥离气体流入蚀刻室内;

由蚀刻室内的蚀刻掩模剥离气体产生等离子体;

剥离蚀刻掩模,去除由经重新淀积的含金属层的部分形成的残留侧壁钝化物,而衬底位于蚀刻室内,其中,由蚀刻掩模剥离气体产生的等离子体剥离蚀刻掩模,并去除侧壁钝化物;以及

从蚀刻室移走衬底。

2.根据权利要求1的方法,还包括以下步骤:

将等离子体从蚀刻气体静电吸引到蚀刻室内的衬底;以及

将等离子体从蚀刻掩模剥离气体静电吸引到蚀刻室内的衬底。

3.根据权利要求1和2中任何一个的方法,其中蚀刻室为金属蚀刻室。

4.根据权利要求1的方法,其中剥离掉蚀刻掩模并除去残留侧壁钝化物的步骤还从蚀刻室壁上除去残留物。

5.根据权利要求4的方法,其中蚀刻掩模剥离气体包括氧气。

6.根据权利要求5的方法,还包括以下步骤:

将衬底放置在负载锁定中;以及

从负载锁定除去衬底将衬底放置在蚀刻室内。

7.根据权利要求6的方法,还包括以下步骤:

将衬底从蚀刻室移走之后将衬底放入腐蚀钝化室内;以及

将晶片暴露到非等离子体高温水蒸气。

8.根据权利要求7的方法,还包括以下步骤:

将衬底从腐蚀钝化室传送到冷却台;

在冷却台中冷却衬底;以及

将衬底从冷却台传送到负载锁定。

9.根据权利要求4的方法,还包括蚀刻和剥离步骤期间将压力保持在1和80毫乇之间的步骤。

10.根据权利要求9的方法,还包括蚀刻和剥离步骤期间将衬底温度保持在10℃和100℃之间的步骤。

11.根据权利要求10的方法,其中从蚀刻气体静电吸引等离子体的步骤包括将支撑衬底的吸盘偏置到-10和-1,000伏之间的偏置电源的步骤,其中从蚀刻掩模剥离气体静电吸引等离子体的步骤包括将支撑衬底的吸盘偏置到-10和-1,000伏之间的偏置电源的步骤。

12.根据权利要求1的方法,其中剥离包括将氧等离子体加速到衬底以除去重新沉积形成残留侧壁钝化物的部分含金属层的步骤。

13.根据权利要求1的方法,其中剥离去除了大部分残留侧壁钝化物。

14.根据权利要求1的方法,其中剥离去除了所有残留侧壁钝化物。

15.一种至少部分通过设置在衬底上的含金属层的蚀刻方法,其中部分所述含金属层设置在蚀刻掩模下,部分所述含金属层没有设置在蚀刻掩模下,包括以下步骤:

将衬底放置在蚀刻室中;

蚀刻掉没有设置在蚀刻掩模下那部分含金属层,其中一些蚀刻掉的部分含金属层重新沉积以在衬底上形成侧壁钝化物,同时衬底位于蚀刻室内;

剥离掉蚀刻掩模并除去部分重新沉积形成残留侧壁钝化物的含金属层,同时衬底位于蚀刻室内;以及

从蚀刻室移走衬底。

16.一种至少部分通过设置在衬底上的含金属层的蚀刻设备,其中部分所述含金属层设置在蚀刻掩模下,部分所述含金属层没有设置在蚀刻掩模下,包括:

将衬底放置在蚀刻室中的装置;

使蚀刻气体流入蚀刻室内的装置;

由蚀刻室内的蚀刻气体产生等离子体的装置;

蚀刻掉没有设置在蚀刻掩模下那部分含金属层的装置,其中一些蚀刻掉的部分含金属层重新沉积以在衬底上形成残留侧壁钝化物,同时衬底位于蚀刻室内;

使蚀刻气体停止流入蚀刻室的装置;

使蚀刻掩模剥离气体流入蚀刻室内的装置;

由蚀刻室内的蚀刻掩模剥离气体产生等离子体的装置;

剥离掉蚀刻掩模并除去部分含金属层的装置,所述部分含金属层重新沉积形成残留侧壁钝化物,同时衬底位于蚀刻室内;以及

从蚀刻室移走衬底的装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/472,757 | 1999-12-27 | ||

| US09/472,757 US6852636B1 (en) | 1999-12-27 | 1999-12-27 | Insitu post etch process to remove remaining photoresist and residual sidewall passivation |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1434978A CN1434978A (zh) | 2003-08-06 |

| CN1210773C true CN1210773C (zh) | 2005-07-13 |

Family

ID=23876824

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB008191689A Expired - Fee Related CN1210773C (zh) | 1999-12-27 | 2000-12-21 | 除去剩余光致抗蚀剂和残留侧壁钝化物的原位后蚀刻方法 |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US6852636B1 (zh) |

| EP (1) | EP1243023B1 (zh) |

| JP (2) | JP2003518768A (zh) |

| KR (1) | KR100794538B1 (zh) |

| CN (1) | CN1210773C (zh) |

| AT (1) | ATE431964T1 (zh) |

| AU (1) | AU2737301A (zh) |

| DE (1) | DE60042246D1 (zh) |

| TW (1) | TW471060B (zh) |

| WO (1) | WO2001048808A1 (zh) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1320128B1 (en) * | 2001-12-17 | 2006-05-03 | AMI Semiconductor Belgium BVBA | Method for making interconnect structures |

| US6943039B2 (en) * | 2003-02-11 | 2005-09-13 | Applied Materials Inc. | Method of etching ferroelectric layers |

| CN100444025C (zh) * | 2004-07-12 | 2008-12-17 | 北京北方微电子基地设备工艺研究中心有限责任公司 | 光刻胶修整方法 |

| US7597816B2 (en) * | 2004-09-03 | 2009-10-06 | Lam Research Corporation | Wafer bevel polymer removal |

| JP4518986B2 (ja) * | 2005-03-17 | 2010-08-04 | 東京エレクトロン株式会社 | 大気搬送室、被処理体の処理後搬送方法、プログラム及び記憶媒体 |

| US20070032081A1 (en) * | 2005-08-08 | 2007-02-08 | Jeremy Chang | Edge ring assembly with dielectric spacer ring |

| US7479457B2 (en) * | 2005-09-08 | 2009-01-20 | Lam Research Corporation | Gas mixture for removing photoresist and post etch residue from low-k dielectric material and method of use thereof |

| US20070227555A1 (en) * | 2006-04-04 | 2007-10-04 | Johnson Michael R | Method to manipulate post metal etch/side wall residue |

| JP2014212310A (ja) * | 2013-04-02 | 2014-11-13 | 東京エレクトロン株式会社 | 半導体デバイスの製造方法及び製造装置 |

| JP6844083B2 (ja) * | 2015-05-27 | 2021-03-17 | サムコ株式会社 | アフターコロージョン抑制処理方法 |

| CN107464750B (zh) * | 2017-08-23 | 2019-12-13 | 成都海威华芯科技有限公司 | 一种去除光刻胶底膜的工艺方法 |

| US11749532B2 (en) | 2021-05-04 | 2023-09-05 | Applied Materials, Inc. | Methods and apparatus for processing a substrate |

| KR20240086974A (ko) * | 2022-12-12 | 2024-06-19 | 피에스케이 주식회사 | 기판 처리 장치 및 기판 처리 방법 |

Family Cites Families (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4804431A (en) | 1987-11-03 | 1989-02-14 | Aaron Ribner | Microwave plasma etching machine and method of etching |

| JP2831646B2 (ja) * | 1988-03-25 | 1998-12-02 | 株式会社東芝 | 半導体装置の製造方法 |

| US4985113A (en) | 1989-03-10 | 1991-01-15 | Hitachi, Ltd. | Sample treating method and apparatus |

| US5186718A (en) * | 1989-05-19 | 1993-02-16 | Applied Materials, Inc. | Staged-vacuum wafer processing system and method |

| JPH0341728A (ja) * | 1989-07-07 | 1991-02-22 | Fujitsu Ltd | 半導体装置の製造方法 |

| EP0809283A3 (en) | 1989-08-28 | 1998-02-25 | Hitachi, Ltd. | Method of treating wafers |

| US5198634A (en) | 1990-05-21 | 1993-03-30 | Mattson Brad S | Plasma contamination removal process |

| JP2998173B2 (ja) * | 1990-06-01 | 2000-01-11 | 松下電器産業株式会社 | Alエッチング方法 |

| US5397432A (en) | 1990-06-27 | 1995-03-14 | Fujitsu Limited | Method for producing semiconductor integrated circuits and apparatus used in such method |

| US5174856A (en) | 1991-08-26 | 1992-12-29 | Applied Materials, Inc. | Method for removal of photoresist over metal which also removes or inactivates corrosion-forming materials remaining from previous metal etch |

| JPH05275325A (ja) * | 1992-03-26 | 1993-10-22 | Fujitsu Ltd | 半導体装置の製造方法 |

| US5462892A (en) | 1992-06-22 | 1995-10-31 | Vlsi Technology, Inc. | Semiconductor processing method for preventing corrosion of metal film connections |

| US5931721A (en) | 1994-11-07 | 1999-08-03 | Sumitomo Heavy Industries, Ltd. | Aerosol surface processing |

| JPH08213366A (ja) * | 1995-02-07 | 1996-08-20 | Hitachi Ltd | パターン形成方法およびパターン形成装置、ならびに半導体集積回路装置の製造方法および半導体製造装置 |

| US5705443A (en) | 1995-05-30 | 1998-01-06 | Advanced Technology Materials, Inc. | Etching method for refractory materials |

| WO1997011482A2 (en) | 1995-09-05 | 1997-03-27 | Lsi Logic Corporation | Removal of halogens and photoresist from wafers |

| US5573961A (en) | 1995-11-09 | 1996-11-12 | Taiwan Semiconductor Manufacturing Company Ltd. | Method of making a body contact for a MOSFET device fabricated in an SOI layer |

| US5780359A (en) * | 1995-12-11 | 1998-07-14 | Applied Materials, Inc. | Polymer removal from top surfaces and sidewalls of a semiconductor wafer |

| US5824604A (en) | 1996-01-23 | 1998-10-20 | Mattson Technology, Inc. | Hydrocarbon-enhanced dry stripping of photoresist |

| US5712207A (en) | 1996-02-29 | 1998-01-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | Profile improvement of a metal interconnect structure on a tungsten plug |

| WO1997033300A1 (en) | 1996-03-06 | 1997-09-12 | Mattson Technology, Inc. | Icp reactor having a conically-shaped plasma-generating section |

| KR19990008362A (ko) | 1996-03-06 | 1999-01-25 | 얀 드'해머,헤르베르트 볼만 | 리프트-오프 이미징 프로파일을 얻기 위한 방법 |

| US5908319A (en) | 1996-04-24 | 1999-06-01 | Ulvac Technologies, Inc. | Cleaning and stripping of photoresist from surfaces of semiconductor wafers |

| US5882489A (en) | 1996-04-26 | 1999-03-16 | Ulvac Technologies, Inc. | Processes for cleaning and stripping photoresist from surfaces of semiconductor wafers |

| US5776832A (en) | 1996-07-17 | 1998-07-07 | Taiwan Semiconductor Manufacturing Company Ltd. | Anti-corrosion etch process for etching metal interconnections extending over and within contact openings |

| US5779929A (en) | 1996-10-07 | 1998-07-14 | Lucent Technologies Inc. | Thin film metallization for barium nanotitanate substrates |

| US5744395A (en) | 1996-10-16 | 1998-04-28 | Taiwan Semiconductor Manufacturing Company, Ltd. | Low resistance, self-aligned, titanium silicide structures, using a single rapid thermal anneal procedure |

| US5795831A (en) | 1996-10-16 | 1998-08-18 | Ulvac Technologies, Inc. | Cold processes for cleaning and stripping photoresist from surfaces of semiconductor wafers |

| US5899716A (en) | 1997-05-19 | 1999-05-04 | Vanguard International Semiconductor Corporation | Oxygen ion implantation procedure to increase the surface area of an STC structure |

| JPH10335313A (ja) * | 1997-06-03 | 1998-12-18 | Hitachi Ltd | プラズマエッチング方法 |

| JPH113881A (ja) * | 1997-06-11 | 1999-01-06 | Fujitsu Ltd | アッシング方法及び装置 |

| US5846884A (en) | 1997-06-20 | 1998-12-08 | Siemens Aktiengesellschaft | Methods for metal etching with reduced sidewall build up during integrated circuit manufacturing |

| US5946589A (en) | 1997-10-09 | 1999-08-31 | Chartered Semiconductor Manufacturing, Ltd. | Elimination of void formation in aluminum based interconnect structures |

| US5849639A (en) | 1997-11-26 | 1998-12-15 | Lucent Technologies Inc. | Method for removing etching residues and contaminants |

-

1999

- 1999-12-27 US US09/472,757 patent/US6852636B1/en not_active Expired - Fee Related

-

2000

- 2000-12-19 TW TW089127266A patent/TW471060B/zh not_active IP Right Cessation

- 2000-12-21 DE DE60042246T patent/DE60042246D1/de not_active Expired - Lifetime

- 2000-12-21 JP JP2001548428A patent/JP2003518768A/ja not_active Withdrawn

- 2000-12-21 AU AU27373/01A patent/AU2737301A/en not_active Abandoned

- 2000-12-21 EP EP00990333A patent/EP1243023B1/en not_active Expired - Lifetime

- 2000-12-21 CN CNB008191689A patent/CN1210773C/zh not_active Expired - Fee Related

- 2000-12-21 KR KR1020027008271A patent/KR100794538B1/ko not_active IP Right Cessation

- 2000-12-21 AT AT00990333T patent/ATE431964T1/de not_active IP Right Cessation

- 2000-12-21 WO PCT/US2000/035165 patent/WO2001048808A1/en active Application Filing

-

2011

- 2011-09-08 JP JP2011196141A patent/JP2012023385A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| WO2001048808A1 (en) | 2001-07-05 |

| US6852636B1 (en) | 2005-02-08 |

| JP2012023385A (ja) | 2012-02-02 |

| KR20020081234A (ko) | 2002-10-26 |

| EP1243023B1 (en) | 2009-05-20 |

| ATE431964T1 (de) | 2009-06-15 |

| KR100794538B1 (ko) | 2008-01-17 |

| AU2737301A (en) | 2001-07-09 |

| JP2003518768A (ja) | 2003-06-10 |

| EP1243023A1 (en) | 2002-09-25 |

| DE60042246D1 (de) | 2009-07-02 |

| CN1434978A (zh) | 2003-08-06 |

| TW471060B (en) | 2002-01-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN107068556B (zh) | 原子层蚀刻3D结构:水平和竖直表面上Si和SiGe和Ge平滑度 | |

| CN1210773C (zh) | 除去剩余光致抗蚀剂和残留侧壁钝化物的原位后蚀刻方法 | |

| US8058181B1 (en) | Method for post-etch cleans | |

| CN103258729B (zh) | 硅结构的制造和带有形貌控制的深硅蚀刻 | |

| US5849639A (en) | Method for removing etching residues and contaminants | |

| US6893893B2 (en) | Method of preventing short circuits in magnetic film stacks | |

| US7344993B2 (en) | Low-pressure removal of photoresist and etch residue | |

| EP1324374B1 (en) | Etching System for an insulation-film | |

| US7320942B2 (en) | Method for removal of metallic residue after plasma etching of a metal layer | |

| EP1081751A3 (en) | Methods of pre-cleaning dielectric layers of substrates | |

| EP1198829A1 (en) | Multiple stage cleaning process for plasma etching chambers | |

| JPH05267256A (ja) | 反応室の洗浄方法 | |

| CN101882595A (zh) | 阻挡层的去除方法和装置 | |

| CN1148789C (zh) | 腐蚀半导体晶片的方法和装置 | |

| US20050066994A1 (en) | Methods for cleaning processing chambers | |

| US6458648B1 (en) | Method for in-situ removal of side walls in MOM capacitor formation | |

| Winters et al. | Coatings and surface modification using low pressure non-equilibrium plasmas | |

| CN1906753A (zh) | 铜表面的表面还原、钝化、防止腐蚀及活化用的系统与方法 | |

| CN110634739A (zh) | 一种用于铝基片的等离子体刻蚀方法 | |

| CN1330395A (zh) | 去除光致抗蚀剂后残留物质的清除方法 | |

| CN102903667A (zh) | 半导体器件的形成方法 | |

| CN1932652A (zh) | 光致抗蚀剂剥离方法 | |

| CN1773681A (zh) | 去除蚀刻残余的聚合物的方法 | |

| TW451345B (en) | Cleaning method of the residual material after removing photoresist | |

| CN1186804C (zh) | 金属薄膜干蚀刻后处理方法及蚀刻与去光刻胶的整合系统 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20050713 Termination date: 20161221 |

|

| CF01 | Termination of patent right due to non-payment of annual fee |