CN114651534A - 布线电路基板和其制造方法 - Google Patents

布线电路基板和其制造方法 Download PDFInfo

- Publication number

- CN114651534A CN114651534A CN202080077832.7A CN202080077832A CN114651534A CN 114651534 A CN114651534 A CN 114651534A CN 202080077832 A CN202080077832 A CN 202080077832A CN 114651534 A CN114651534 A CN 114651534A

- Authority

- CN

- China

- Prior art keywords

- wiring

- terminal

- layer

- thickness direction

- circuit board

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/24—Reinforcing the conductive pattern

- H05K3/244—Finish plating of conductors, especially of copper conductors, e.g. for pads or lands

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/117—Pads along the edge of rigid circuit boards, e.g. for pluggable connectors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0296—Conductive pattern lay-out details not covered by sub groups H05K1/02 - H05K1/0295

- H05K1/0298—Multilayer circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B5/00—Recording by magnetisation or demagnetisation of a record carrier; Reproducing by magnetic means; Record carriers therefor

- G11B5/48—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed

- G11B5/58—Disposition or mounting of heads or head supports relative to record carriers ; arrangements of heads, e.g. for scanning the record carrier to increase the relative speed with provision for moving the head for the purpose of maintaining alignment of the head relative to the record carrier during transducing operation, e.g. to compensate for surface irregularities of the latter or for track following

- G11B5/60—Fluid-dynamic spacing of heads from record-carriers

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

- H05K3/18—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern using precipitation techniques to apply the conductive material

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/28—Applying non-metallic protective coatings

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

- H05K3/4652—Adding a circuit layer by laminating a metal foil or a preformed metal foil pattern

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/03—Use of materials for the substrate

- H05K1/05—Insulated conductive substrates, e.g. insulated metal substrate

- H05K1/056—Insulated conductive substrates, e.g. insulated metal substrate the metal substrate being covered by an organic insulating layer

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09654—Shape and layout details of conductors covering at least two types of conductors provided for in H05K2201/09218 - H05K2201/095

- H05K2201/09672—Superposed layout, i.e. in different planes

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/07—Treatments involving liquids, e.g. plating, rinsing

- H05K2203/0703—Plating

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

- Structure Of Printed Boards (AREA)

Abstract

布线电路基板(1)具备:基底绝缘层(2);第1布线(7),其配置于基底绝缘层(2)的厚度方向上的一侧的面;中间绝缘层(3),其以覆盖第1布线(7)的方式配置于基底绝缘层(2)的厚度方向上的一侧的面;第2布线(12),其配置于中间绝缘层(3)的厚度方向上的一侧的面;第1端子(8),其为1层,该第1端子(8)配置于基底绝缘层(2)的厚度方向上的一侧的面且与第1布线(7)电连接;以及第2端子(10),其为1层,该第2端子(10)配置于基底绝缘层(2)的厚度方向上的一侧的面且与第2布线(12)电连接。第1端子(8)与第1布线(7)连续。第2端子(10)不与第2布线(12)连续。布线电路基板(1)还具备连接部(11),该连接部(11)配置于基底绝缘层(2)的厚度方向上的一侧的面且与第2端子(10)连续。连接部(11)在厚度方向上与第2布线(12)电连接。

Description

技术领域

本发明涉及布线电路基板和其制造方法。

背景技术

以往,提出一种具备布线端子部的悬挂用基板(例如参照下述专利文献1。)。在布线端子部安装有其他的电子设备。

另外,专利文献1所记载的布线端子部具备形成于基底绝缘层之上的第1导体端子和形成于该第1导体端子之上的第2导体端子。第1导体端子由第1导体层构成。第2导体端子由第2导体层构成。第1导体层的长度方向上的一端部是第1导体端子,第2导体层的长度方向上的一端部是第2导体端子,在第1导体层的长度方向上的中间部与第2导体层的长度方向上的中间部之间存在中间绝缘层。

现有技术文献

专利文献

专利文献1:日本特开2012-198957号公报

发明内容

发明要解决的问题

近年来,谋求布线端子部的薄型化。但是,专利文献1所记载的布线端子部包括由第1导体构成的第1导体端子和由第2导体构成的第2导体端子这两层,因此薄型化存在极限。

本发明提供具备较薄的第1端子和较薄的第2端子的布线电路基板和其制造方法。

用于解决问题的方案

本技术方案(1)包含一种布线电路基板,其中,该布线电路基板具备:基底绝缘层;第1布线,其配置于所述基底绝缘层的厚度方向上的一侧的面;中间绝缘层,其以覆盖所述第1布线的方式配置于所述基底绝缘层的所述厚度方向上的一侧的面;第2布线,其配置于所述中间绝缘层的厚度方向上的一侧的面;第1端子,其为1层,该第1端子配置于所述基底绝缘层的所述厚度方向上的一侧的面且与所述第1布线电连接;以及第2端子,其为1层,该第2端子配置于所述基底绝缘层的所述厚度方向上的一侧的面且与所述第2布线电连接,所述第1端子与所述第1布线连续,所述第2端子不与所述第2布线连续,该布线电路基板还具备连接部,该连接部配置于所述基底绝缘层的所述厚度方向上的一侧的面且与所述第2端子连续,所述连接部在厚度方向上与所述第2布线电连接。

该布线电路基板具备配置于基底绝缘层的厚度方向上的一侧的面的、1层的第1端子和1层的第2端子。由于第1端子和第2端子均配置于基底绝缘层的厚度方向上的一侧的面,因此能够实现它们的薄型化。另外,由于第1端子和第2端子均为1层,因此能够实现它们的薄型化。

本技术方案(2)在包含技术方案(1)所述的布线电路基板的基础上,该布线电路基板还具备镀层,该镀层配置于所述第1布线的厚度方向上的一侧的面和侧面。

在该布线电路基板中,由于镀层覆盖第1布线,因此能够保护第1布线。

本技术方案(3)在包含技术方案(1)或技术方案(2)所述的布线电路基板的基础上,所述第2端子的厚度与所述第1端子的厚度相同。

在该布线电路基板中,第2端子的厚度与第1端子的厚度相同,因此,结构简单。

本技术方案(4)在包含技术方案(1)~技术方案(3)中任一项所述的布线电路基板的基础上,所述第2端子的厚度为20μm以下。

在该布线电路基板中,由于第2端子的厚度为20μm以下,因此,能够可靠地使第2端子较薄。

本技术方案(5)在包含技术方案(1)~技术方案(4)中任一项所述的布线电路基板的基础上,所述第2布线比所述第2端子厚。

在该布线电路基板中,能够使第2端子较薄,且能够降低较厚的第2布线的电阻。

本技术方案(6)在包含技术方案(1)~技术方案(5)中任一项所述的布线电路基板的基础上,所述第2布线比所述第1布线厚。

在该布线电路基板中,利用较薄的第1布线来传输电流值较低的电信号,另一方面,能够利用较厚的第2布线来传输电流值较高的电流。

本技术方案(7)在包含技术方案(1)~技术方案(6)中任一项所述的布线电路基板的基础上,该布线电路基板还具备辅助布线,该辅助布线配置于所述基底绝缘层的所述厚度方向上的一侧的面且与所述连接部连续。

在该布线电路基板中,第2布线和辅助布线能够构成电源布线,能够增大它们的合计截面积。因此,能够降低电流值较高的电源布线的电阻。其结果,能够高效地传输电流值较高的电源电流。

本技术方案(8)包含一种布线电路基板的制造方法,其中,该布线电路基板的制造方法具备以下工序:准备基底绝缘层;在所述基底绝缘层的厚度方向上的一侧的面形成包含第1布线、与所述第1布线连续的第1端子、与所述第1端子连续的引线、连接部、以及与所述连接部连续的第2端子的第1导体层;通过使用所述引线进行的镀敷,从而在所述第1布线的厚度方向上的一侧的面和侧面形成镀层;使中间绝缘层以覆盖所述镀层的方式形成于所述基底绝缘层的厚度方向上的一侧的面;以及使包含不与所述第2端子连续的第2布线的第2导体层以所述第2布线与所述连接部的厚度方向上的一侧的面接触的方式,形成于所述中间绝缘层的厚度方向上的一侧的面。

根据该布线电路基板的制造方法,通过使用引线的镀敷,能够在第1布线的厚度方向上的一侧的面和侧面形成镀层。

发明的效果

在本发明的布线电路基板中,能够实现第1端子和第2端子的薄型化。

根据本发明的布线电路基板的制造方法,能够使镀层形成于第1布线的厚度方向上的一侧的面和侧面。

附图说明

图1是本发明的布线电路基板的一个实施方式的放大俯视图。

图2中的图2A~图2D是图1所示的布线电路基板的剖视图,图2A是沿着图1的A-A线的剖视图,图2B是沿着图1的B-B线的剖视图,图2C是沿着图1的C-C线且沿着图2A~图2B的X-X线的剖视图,图2D是沿着图1的D-D线且沿着图2A~图2B的Y-Y线的剖视图。

图3中的图3A~图3E表示图2A所示的布线电路基板的制造方法的工序的剖视图,图3A表示第1工序~第2工序,图3B表示第3工序,图3C表示第6工序,图3D表示第7工序,图3E表示第8工序。

图4中的图4A~图4G是图2B所示的布线电路基板的制造方法的工序的剖视图,图4A表示第1工序~第2工序,图4B表示第3工序,图4C表示第4工序,图4D表示第5工序,图4E表示第6工序,图4F表示第7工序,图4G表示第8工序。

图5中的图5A~图5D表示本发明的布线电路基板的变形例(第2布线较厚的变形例),另外是与图1对应的剖视图,图5A是沿着图1的A-A线的剖视图,图5B是沿着图1的B-B线的剖视图,图5C是沿着图1的C-C线且沿着图5A~图5B的X-X线的剖视图,图5D是沿着图1的D-D线且沿着图5A~图5B的Y-Y线的剖视图。

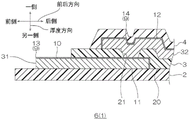

图6是图2B所示的布线电路基板的进一步的变形例(还具备辅助布线的变形例)的剖视图。

图7是图6所示的布线电路基板的进一步的变形例(第2布线较厚的变形例)的剖视图。

图8是图2B所示的布线电路基板的进一步的变形例(第2布线经由中间通路与连接部连接的变形例)的剖视图。

图9是图8所示的布线电路基板的进一步的变形例(还具备辅助布线的变形例)的剖视图。

图10是图1所示的布线电路基板的变形例(第1图案部和第2图案部在俯视时局部地重叠且第1布线弯折的变形例)的俯视图。

图11中的图11A~图11D是图10所示的布线电路基板的剖视图,图11A是沿着图10的A-A线的剖视图,图11B是沿着图10的B-B线的剖视图,图11C是沿着图10的C-C线且沿着图11A~图11B的X-X线的剖视图,图11D是沿着图10的D-D线且沿着图11A~图11B的Y-Y线的剖视图。

图12是图1所示的布线电路基板的变形例(第1图案部和第2图案部在俯视时局部地重叠且第2布线弯折的变形例)的俯视图。

图13中的图13A~图13C是图12所示的布线电路基板的剖视图,图13A是沿着图12的A-A线的剖视图,图13B是沿着图12的B-B线的剖视图,图13C是沿着图12的C-C线且沿着图13A~图13B的X-X线的剖视图,图13D是沿着图12的D-D线且沿着图13A~图13B的Y-Y线的剖视图。

图14中的图14A~图14F是比较例1的布线电路基板的制造方法的工序的剖视图,图14A是形成第1布线的工序,图14B是形成中间绝缘层的工序,图14C是形成第1端子和第2连接部的工序,图14D是形成镀层的工序,图14E是形成覆盖绝缘层的工序,图14F是去除第2引线和金属支承层的工序。

具体实施方式

<一个实施方式>

参照图1~图4G来说明本发明的布线电路基板和其制造方法的一个实施方式。此外,在图1中,为了明确示出第1图案部5和第2图案部6(后述)的相对位置,省略覆盖绝缘层4(后述)。

如图1~图2D所示,布线电路基板1具有预定厚度,具有在前后方向(是图1中的纸面上下方向且是图2C和图2D中的纸面进深方向)上较长地延伸的平带形状。布线电路基板1朝向厚度方向上的一侧去依次具备基底绝缘层2、中间绝缘层3和覆盖绝缘层4。

基底绝缘层2具有在俯视时与布线电路基板1相同的外形形状。基底绝缘层2的厚度方向上的一侧的面平坦。

中间绝缘层3配置于基底绝缘层2的厚度方向上的一侧的面。详细而言,中间绝缘层3配置于比基底绝缘层2的厚度方向上的一侧的面的前侧部靠后侧的区域。也就是说,中间绝缘层3未配置于基底绝缘层2的厚度方向上的一侧的面的前侧部。另外,中间绝缘层3的厚度方向上的一侧的面包含平坦面。

覆盖绝缘层4配置于中间绝缘层3的厚度方向上的一侧的面和基底绝缘层2的在厚度方向上不与中间绝缘层3重叠的部分的厚度方向上的一侧的面。

作为基底绝缘层2、中间绝缘层3和覆盖绝缘层4的材料,例如,可举出聚酰亚胺等绝缘树脂。基底绝缘层2、中间绝缘层3和覆盖绝缘层4的厚度分别例如为5μm以上,另外例如为30μm以下。

另外,布线电路基板1具备第1图案部5和第2图案部6。第1图案部5是布线电路基板1的宽度方向(与厚度方向和前后方向正交的方向)上的一侧部,第2图案部6是布线电路基板1的宽度方向上的另一侧部。

如图1所示,第1图案部5在布线电路基板1中沿前后方向延伸。如图2A所示,第1图案部5具备基底绝缘层2、第1布线7、第1端子8、中间绝缘层3和覆盖绝缘层4。

如图2A和图2C所示,第1布线7配置于基底绝缘层2的厚度方向上的一侧的面。具体而言,第1布线7的厚度方向上的另一侧的整个面与基底绝缘层2的厚度方向上的一侧的面接触。如图1所示,第1布线7具有在俯视时沿前后方向延伸的大致直线形状。

第1端子8在俯视时与第1布线7的前端缘连续。由此,第1布线7和第1端子8朝向前侧去依次连续地配置。第1端子8与第1布线7电连接。第1端子8具有在俯视时宽度比第1布线7的宽度大的大致矩形连接盘形状。

另外,第1端子8配置于基底绝缘层2的厚度方向上的一侧的面。具体而言,第1端子8的厚度方向上的另一侧的整个面与基底绝缘层2的厚度方向上的一侧的面接触。那样一来,第1端子8与第1布线7配置于同一基底绝缘层2的厚度方向上的一侧的面。

另外,如图2A和图2D所示,第1端子8为1层。换言之,由多个层在厚度方向上层叠而成的层叠体(多层体)构成的层叠型端子不是本发明的第1端子。此外,上述多个层中的各层的厚度为1μm以上。

作为第1布线7和第1端子8的材料,例如,可举出铜、铬、以及它们的合金等导体。

如图2A所示,第1布线7的厚度T1和第1端子8的厚度T2例如相同或不同,优选相同。具体而言,第1布线7的厚度T1和第1端子8的厚度T2例如为3μm以上,优选为5μm以上,另外例如为100μm以下,优选为50μm以下,更优选为20μm以下。若第1端子8的厚度T2为上述上限以下,则能够使第1端子8较薄。

第1布线7的宽度例如为5μm以上,另外例如为50μm以下。第1端子8的宽度和前后方向长度分别例如为10μm以上,另外例如为100μm以下。

如图1、图2A和图2C所示,第1图案部5的中间绝缘层3未覆盖第1布线7的前侧部和后侧部(未图示),而是覆盖第1布线7的前后方向上的中间部。中间绝缘层3覆盖第1布线7的前后方向上的中间部的厚度方向上的一侧的面和宽度方向上的两侧面。

第1图案部5的覆盖绝缘层4配置于中间绝缘层3的厚度方向上的一侧的面。

如图1所示,第2图案部6与第1图案部5的宽度方向上的另一侧相邻。第2图案部6在布线电路基板1中沿前后方向延伸。如图2B所示,第2图案部6具备基底绝缘层2、第2端子10、连接部11、中间绝缘层3、第2布线12、覆盖绝缘层4。

如图1、图2C和图2D所示,第2图案部6的基底绝缘层2在宽度方向上与第1图案部5的基底绝缘层2连续,是同一层。

第2端子10相对于第1端子8在宽度方向上的另一侧隔开间隔地相对配置。第2端子10配置于基底绝缘层2的厚度方向上的一侧的面。具体而言,第2端子10的厚度方向上的另一侧的整个面与基底绝缘层2的厚度方向上的一侧的面接触。第2端子10具有在俯视时呈大致矩形连接盘的形状。第2端子10的厚度T4、宽度和前后方向长度分别与第1端子8的厚度T2、宽度和前后方向长度相同。具体而言,第2端子10的厚度T4例如为3μm以上,优选为5μm以上,另外例如为100μm以下,优选为50μm以下,更优选为20μm以下。若第2端子10的厚度T4为上述上限以下,则能够使第2端子10较薄。

另外,第2端子10为1层。换言之,由多个层在厚度方向上层叠而成的层叠体(多层体)构成的层叠型端子不是本发明的第2端子。此外,上述多个层中的各层的厚度为1μm以上。

连接部11在俯视时与第2端子10的后端缘连续,且具有沿前后方向延伸的大致直线形状。详细而言,连接部11在俯视时具有在前后方向上较长且宽度较狭的大致矩形形状。另外,连接部11相对于第1布线7的前侧部在宽度方向上的另一侧隔开间隔地相对配置。连接部11的厚度和宽度与后述的第2布线12的宽度相同。连接部11的前后方向长度并未特别限定,例如为100μm以上,优选为1000μm以上,另外例如为100000μm以下,优选为10000μm以下。

另外,连接部11配置于基底绝缘层2的厚度方向上的一侧的面。具体而言,连接部11的厚度方向上的另一侧的整个面与基底绝缘层2的厚度方向上的一侧的面接触。那样一来,连接部11和第2端子10配置于同一基底绝缘层2的厚度方向上的一侧的面。连接部11为1层。

如图2B和图2C所示,第2图案部6的中间绝缘层3在宽度方向上与第1图案部5的中间绝缘层3连续,是同一层。中间绝缘层3在沿厚度方向投影时配置于基底绝缘层2的不与连接部11重叠的部分的厚度方向上的一侧的面、连接部11的后端部的厚度方向上的一侧的面、连接部11的后端部的宽度方向上的两侧面和连接部11的后端部的后侧面(后端面)。由此,中间绝缘层3未覆盖连接部11的前端部和前后方向上的中间部,而是覆盖连接部11的后端部。

如图1所示,第2布线12具有沿前后方向延伸的大致直线形状。详细而言,第2布线12在俯视时具有在前后方向上较长且宽度较狭的大致矩形形状。第2布线12的前端部在厚度方向上与连接部11的后侧部重叠。详细而言,第2布线12的前端部的厚度方向上的另一侧的面同连接部11的后侧部的不与中间绝缘层3重叠的部分的厚度方向上的一侧的面接触。由此,第2布线12在厚度方向上与连接部11电连接。另外,第2布线12经由连接部11与第2端子10电连接。

另一方面,第2布线12不与第2端子10连续。第2布线12在俯视时与第2端子10隔开间隔。

另外,如图2B和图2C所示,第2布线12的前后方向上的中间部和后侧部配置于中间绝缘层3的厚度方向上的一侧的面。详细而言,第2布线12的前后方向上的中间部和后侧部的厚度方向上的另一侧的整个面与中间绝缘层3的厚度方向上的一侧的面接触。

如图2C所示,第2布线12的厚度T3与第1布线7的厚度T1例如相同或不同,优选相同。第2布线12的宽度与第1布线7的宽度例如相同。另外,如图2B所示,第2布线12的厚度T3例如也与第2端子10的厚度T4相同。

作为第2端子10、连接部11和第2布线12的材料,例如,可举出与第1布线7和第1端子8相同的材料。

如图2C所示,第2图案部6的覆盖绝缘层4在宽度方向上与第1图案部5的覆盖绝缘层4连续,是同一层。覆盖绝缘层4以覆盖第2布线12的方式配置于中间绝缘层3的厚度方向上的一侧的面。覆盖绝缘层4覆盖第2布线12的厚度方向上的一侧的面和宽度方向上的两侧面、以及中间绝缘层3的在厚度方向上不与第2布线12重叠的部分的厚度方向上的一侧的面。

另外,如图3E和图4G所示,该布线电路基板1还具备镀层9。镀层9形成于第1布线7、第1端子8、第2端子10、连接部11和第2布线12的表面。镀层9保护第1布线7、第1端子8、第2端子10、连接部11和第2布线12的表面。镀层9包含第1镀层13和第2镀层14。

第1镀层13形成于第1布线7、第1端子8、第2端子10和连接部11的表面。具体而言,第1镀层13形成于第1布线7的厚度方向上的一侧的面和宽度方向上的两侧面、第1端子8的厚度方向上的一侧的面和宽度方向上的两侧面、连接部11的厚度方向上的一侧的面、连接部11的宽度方向上的两侧面和连接部11的后侧面、以及第2端子10的厚度方向上的一侧的面和宽度方向上的两侧面。作为第1镀层13的材料,例如,可举出镍、金、以及它们的合金等金属材料。第1镀层13的厚度例如为0.01μm以上,优选为0.02μm以上,另外例如小于1μm,优选为0.5μm以下。此外,如图3E和图4G所示,能够明确地视觉识别出第1镀层13与第1布线7、第1端子8、第2端子10、连接部11之间的界面,但例如,也可以是,如图2C~图2D的单点划线所示,所述界面不清晰,第1镀层13与第1布线7、第1端子8、第2端子10、连接部11一体形成(第1镀层13包含于第1布线7、第1端子8、第2端子10和连接部11的表层)。此外,第1镀层13也可以是多个层。

如图4G所示,第2镀层14形成于第2布线12的表面。具体而言,第2镀层14形成于第2布线12的厚度方向上的一侧的面、前侧面(前端面)和宽度方向上的两侧面。作为第2镀层14的材料,例如,可举出与第1镀层13的材料相同的材料。自第1镀层13的厚度所例示的范围中选择出第2镀层14的厚度。此外,如图4G所示,能明确地视觉识别出第2镀层14与第2布线12之间的界面,但例如,也可以是,如图2C的单点划线所示,该界面不清晰,第2镀层14和第2布线12一体形成(第2镀层14包含于第2布线12的表层)。此外,第2镀层14也可以是多个层。

接下来,说明布线电路基板1的制造方法。如图3A~图4G所示,布线电路基板1的制造方法具备准备基底绝缘层2的第1工序、形成包含第1布线7、第1端子8、第2端子10和连接部11的第1导体层31的第2工序、形成第1镀层13的第3工序、形成中间绝缘层3的第4工序、形成包含第2布线12的第2导体层32的第5工序、形成第2镀层14的第6工序、形成覆盖绝缘层4的第7工序、以及去除第1引线17、第2引线18和金属支承层15的第8工序。第1工序~第8工序依次实施。

在第1工序中,如参照图3A和图4A那样,首先,使基底绝缘层2形成于金属支承层15的厚度方向上的一侧的面。

金属支承层15是支承基底绝缘层2的支承构件。另外,金属支承层15也是后述的第3工序和第6工序中的化学镀(参照图3B和图4B)时的接地构件、和/或后述的第3工序和第6工序中的电镀(参照图3B和图4B)时的导电构件。金属支承层15具有沿面方向延伸的片形形状。作为金属支承层15的材料,例如,可举出铁、铜、合金(不锈钢、铜合金等)等金属。金属支承层15的厚度并未特别限定。

对于基底绝缘层2,例如,对感光性的绝缘树脂组合物进行光刻而在金属支承层15的厚度方向上的一侧的面形成基底绝缘层2。此时,在基底绝缘层2的前端部形成通孔19。通孔19在基底绝缘层2的厚度方向上贯通基底绝缘层2。通孔19使金属支承层15的厚度方向上的一侧的面的一部分暴露。

在第2工序中,一次形成包含第1布线7、第1端子8、第2端子10和连接部11的第1导体层31。另外,此时,一并形成作为引线的一个例子的第1引线17和第2引线18。第1引线17包含在第1导体层31。第1引线17和第2引线18相互独立(参照图1的单点划线)或为一体。第1导体层31为1层。使第1引线17形成为与第1端子8的前端缘连续且填充通孔19。使第2引线18形成为与第2端子10的前端缘连续且填充通孔19。

例如,通过加成法、减成法等图案形成法、优选通过加成法来一次形成第1导体层31。

如图3B和图4B所示,在第3工序中,形成第1镀层13。

例如,通过化学镀和/或电镀,从而在第1导体层31的表面一次形成第1镀层13。

如图3B所示,在化学镀中,一边通过第1引线17使第1端子8和第1布线7接地,一边在第1端子8和第1布线7的表面形成均匀的第1镀层13。此外,在第1引线17的表面也形成第1镀层13。

另外,如图4B所示,在化学镀中,一边经由第2引线18使第2端子10和连接部11接地,一边在第2端子10和连接部11的表面形成均匀的第1镀层13。此外,在第2引线18的表面也形成第1镀层13。

另外,如图3B所示,在电镀中,利用第1引线17对第1端子8和第1布线7供电,在第1端子8和第1布线7的表面形成第1镀层13。此外,在第1引线17的表面也形成第1镀层13。

另外,如图4B所示,在化学镀中,通过第2引线18对第2端子10和连接部11供电,在第2端子10和连接部11的表面形成第1镀层13。此外,在第2引线18的表面也形成第1镀层13。

如图3C和图4C所示,在第4工序中,形成中间绝缘层3。中间绝缘层3以与第1工序中的基底绝缘层2的形成方法相同的方法来形成。使中间绝缘层3以覆盖第1镀层13的与第1布线7的前后方向上的中间部对应的部分和第1镀层13的与连接部11的后端部对应的部分的方式形成于基底绝缘层2的厚度方向上的一侧的面。

如图4D所示,在第5工序中,形成包含第2布线12的第2导体层32。第2导体层32为1层。利用与第2工序中的第1导体层31的形成方法相同的方法来形成第2导体层32。使包含第2布线12的第2导体层32连续地形成于中间绝缘层3的厚度方向上的一侧的面和第1镀层13的与连接部11对应的部分的厚度方向上的一侧的面。

如图4E所示,在第6工序中,形成第2镀层14。第2镀层14利用与第1镀层13相同的方法来形成。利用例如与第3工序相同的方法来形成第2镀层14。

在化学镀中,一边通过第2引线18、第2端子10和连接部11使第2布线12接地,一边在第2布线12的表面形成均匀的第2镀层14。

另一方面,在电镀中,通过第2引线18、第2端子10和连接部11对第2布线12供电,从而在第2布线12的表面形成第2镀层14。在第1引线17的表面也形成第2镀层14。

如图2C、图3D和图4F所示,在第7工序中,形成覆盖绝缘层4。覆盖绝缘层4利用与第1工序中的基底绝缘层2相同的方法来形成。使覆盖绝缘层4以覆盖第2镀层14的方式形成于中间绝缘层3的厚度方向上的一侧的面。

在第8工序中,如图3E的实线和图4G的实线所示,首先,去除第1引线17和第2引线18。例如,对第1引线17和第2引线18进行蚀刻。

在第8工序中,之后,如图3E的假想线和图4G的假想线所示,去除金属支承层15(第8工序)。例如,对金属支承层15进行蚀刻、剥离等。

由此,得到布线电路基板1。

此外,能够根据需要,通过外形加工来去除基底绝缘层2的包含通孔19的区域。

(第1实施方式的作用效果)

并且,该布线电路基板1具备配置于基底绝缘层2的厚度方向上的一侧的面的、1层的第1端子8和1层的第2端子10。由于第1端子8和第2端子10均配置于基底绝缘层2的厚度方向上的一侧的面,因此能够实现它们的薄型化。另外,由于第1端子8和第2端子10均为1层,因此能够实现它们的薄型化。

另外,在该布线电路基板1中,由于第1镀层13覆盖第1布线7,因此能够保护第1布线7。

如图2D所示,在该布线电路基板1中,由于第2端子10的厚度T4与第1端子8的厚度T2相同,因此,例如,在将在厚度方向上的另一侧的面具备两个电极35的外部基板33安装于布线电路基板1的前端部时,能够简单且可靠地使处于相同的高度(水平)的两个电极35接触于相同厚度的第1端子8和第2端子10的厚度方向上的一侧的面。

另外,在该布线电路基板1中,若第2端子10的厚度T4为20μm以下,则能够可靠地使第2端子10较薄。

(变形例)

在以下的各变形例中,对于与上述一个实施方式相同的构件和工序,标注相同的附图标记并省略其详细的说明。另外,各变形例除了特别记载之外,能够起到与一个实施方式相同的作用效果。并且,能够适当组合一个实施方式和其变形例。

在该变形例中,如图5B和图5C所示,第2布线12的厚度T3比第2端子10的厚度T4厚。具体而言,第2布线12的厚度T3相对于第2端子10的厚度T4的比(T3/T4)例如为1.1以上,优选为1.5以上,更优选为2以上,另外例如为10以下。

在该变形例中,第2布线12例如传输电源电流(例如10mA以上、乃至100mA以上的大电流)。

在该变形例中,能够使第2端子10较薄,并且能够利用较厚的第2布线12来传输电流值较高的电源电流。并且,若比(T3/T4)为上述下限以上,则能够提高上述效果。此外,在该情况下,能够使与第2端子10连续的连接部11的宽度较大。

另外,第2布线12的厚度T3比第1布线7的厚度T1厚。第2布线12的厚度T3相对于第1布线7的厚度T1的比(T3/T1)例如为1.1以上,优选为1.5以上,更优选为2以上,另外例如为10以下。

具体而言,第1布线7传输电信号(例如小于10mA、乃至小于1mA的弱电流)。

在该变形例中,能够利用较薄的第1布线7来传输微弱的电信号,另一方面,能够利用较厚的第2布线12来传输电流值较高的电源电流。并且,若比(T3/T1)为上述下限以上,则能够提高上述效果。

如图6所示,布线电路基板1还具备辅助布线20。

在该变形例中,第2图案部6包含辅助布线20。

辅助布线20配置于基底绝缘层2的厚度方向上的一侧的面,且与连接部11连续。辅助布线20包含在第1导体层31中。辅助布线20具有从连接部11的后端缘起朝向前侧延伸的直线形状。在该变形例中,在沿厚度方向投影时,辅助布线20与第2布线12重叠。在辅助布线20与第2布线12之间存在中间绝缘层3。

在该变形例中,在将第2端子10作为电源端子时,输入到第2端子10的电流值较高的电源电流向第2布线12和辅助布线20分支。第2布线12和辅助布线20作为电源布线发挥功能。

另一方面,在一个实施方式中,仅第2布线12作为电源布线发挥功能。因此,电源布线的截面积(与电流的传输方向正交的截面的面积)较小。

另一方面,在该变形例中,第2布线12和辅助布线20的合计截面积大于一个实施方式中的第2布线12的截面积。因此,能够降低电源布线的电阻。其结果,能够高效地传输电流值较高的电源电流。

另外,如图7所示,能够使图6所示的变形例的第2布线12的厚度T3较厚,具体而言,能够使第2布线12的厚度T3比第2端子10的厚度T4和第1布线7的厚度T1厚(参照图5A)。

由此,能够进一步增大由第2布线12和辅助布线20构成的电源布线的合计截面积,因此能够进一步降低电源布线的电阻。其结果,能够进一步高效地传输电流值较高的电源电流。

如图8所示,第2布线12的前侧部能够经由中间通路21与连接部11电连接。

中间通路21是在厚度方向上贯通中间绝缘层3的通孔。在中间通路21填充有第2布线12的前侧部的一部分。在中间通路21内,第2布线12的厚度方向上的另一侧的面与连接部11的厚度方向上的一侧的面接触。

如图9所示,图8所示的连接部11也可以与辅助布线20连续。

如图10和图12所示,第1图案部5和第2图案部6在俯视时局部地重叠。具体而言,第1布线7的一部分和第2布线12的一部分在沿厚度方向投影时重叠。

在图10~图11D所示的变形例中,第1布线7具有第1非重叠部22和第1重叠部23。

第1非重叠部22具有在俯视时呈大致字母L的形状。具体而言,第1非重叠部22在俯视时从第1端子8的后端缘起以与第2布线12平行的方式朝向后侧延伸,之后,朝向第2布线12侧(宽度方向上的另一侧)弯折,并到达第2布线12的跟前。

在俯视时,第1重叠部23自第1非重叠部22的宽度方向另一端缘到达第2布线12,与第2布线12重叠,并朝向后侧延伸。

另一方面,在图12~图13D所示的变形例中,第2布线12具有在俯视时呈大致字母L的形状,具有第2非重叠部24和第2重叠部25。

在俯视时,第2非重叠部24在厚度方向上不与第1布线7重叠,第2重叠部25与第1布线7重叠。

在俯视时,第2非重叠部24自中间通路21朝向第1布线7侧(宽度方向上的一侧)延伸,并到达第1布线7的跟前。

在俯视时,第2重叠部25自第2非重叠部24的宽度方向一端缘到达第1布线7,之后,与第1布线7重叠,并朝向后侧延伸。

在图10~图13D所示的变形例中,第1图案部5和第2图案部6在俯视时重叠。

在图10~图13D所示的变形例中,由于第1布线7和第2布线12局部地重叠,因此能够在狭小的空间中引绕第1布线7和第2布线12。

接下来,为了有助于本发明的理解,参照图14A~图14F来说明比较例1的布线电路基板1。

在比较例1中,如图14F所示,与一个实施方式(参照图2A)不同,第1端子8不与第1布线7连续。此外,第1端子8经由第2连接部30与第1布线7电连接。第2连接部30与第1端子8的后端缘连续,并自第1端子8的后端缘起朝向后侧延伸,跨上由第1布线7的前端部形成的台阶,并与第1端子8的前端部的厚度方向上的一侧的面接触。

为了制造比较例1的布线电路基板1,首先,如图14A所示,使包含第1布线7的第1导体层31形成于基底绝缘层2的厚度方向上的一侧的面。此外,此时,第1布线7不位于基底绝缘层2的前侧部(通孔19附近区域)。

接着,如图14B的实线所示,使中间绝缘层3以覆盖第1布线7的方式形成于基底绝缘层2的厚度方向上的一侧的面,接着,如图14C所示,使包含第1端子8和第2连接部30的第2导体层32形成于基底绝缘层2的厚度方向上的一侧的面和第1布线7的前端部的厚度方向上的一侧的面。此时,一并形成第2引线18。

接着,如图14D所示,使镀层9形成于包含第1端子8和第2连接部30的第2导体层32的表面。但是,镀层9不形成于包含第1布线7的第1导体层31的表面。

之后,如图14E所示,形成覆盖绝缘层4,接着,如图14F所示,依次去除第2引线18和金属支承层15。

并且,在比较例1的制造方法中,如图14B所示,在包含第1布线7的自中间绝缘层3暴露的部分的第1导体层31的表面,无法利用通孔19和金属支承层15实施稳定的镀敷,因此无法形成均匀的镀层9(假想线)。也就是说,如图14A所示,在形成第1布线7时,为了确保之后形成的第1端子8的空间,第1引线17的形成空间受限,难以形成第1引线17,因此,无法使上述镀层9形成于第1导体层31的表面。

与此相对,在一个实施方式中,如图3A所示,在形成包含相互连续的第1端子8和第1布线7的第1导体层31之际,一并形成第1引线17。因此,在第3工序中,如图3B所示,在第1布线7的表面,能够利用通孔19和金属支承层15来实施稳定的镀敷,能够形成均匀的镀层9。

此外,即使想要如图14B的假想线所示那样在未使用引线的情况下在第1布线7的表面进行镀敷,若采用电镀,则由于没有引线,因此,无法向第1布线7供电,无法在第1布线7的表面形成电镀层。另一方面,若为化学镀,则由于第1布线7未通过引线而接地,因此,成为极其不均匀的化学镀层,那样一来,无法充分地保护第1端子8。

另外,也可以是,不进行如图3E和图4G所示那样地去除金属支承层15这一工序,布线电路基板1具备金属支承层15。

另外,也能够是,镀层9仅具有第1镀层13和第2镀层14中的任一者。并且,布线电路基板1也可以不具备镀层9。

此外,提供了上述发明作为本发明的例示的实施方式,但这仅是例示,并不能限定性地解释本发明。对于该技术领域的技术人员而言明显的本发明的变形例包含于前述的权利要求书中。

产业上的可利用性

布线电路基板能够用于各种电子用途。

附图标记说明

1、布线电路基板;2、基底绝缘层;3、中间绝缘层;7、第1布线;8、第1端子;9、镀层;10、第2端子;11、连接部;12、第2布线;17、第1引线;18、第2引线;20、辅助布线;31、第1导体层;32、第2导体层;T2、第1端子的厚度;T3、第2布线的厚度;T4、第2端子的厚度。

Claims (8)

1.一种布线电路基板,其特征在于,

该布线电路基板具备:

基底绝缘层;

第1布线,其配置于所述基底绝缘层的厚度方向上的一侧的面;

中间绝缘层,其以覆盖所述第1布线的方式配置于所述基底绝缘层的所述厚度方向上的一侧的面;

第2布线,其配置于所述中间绝缘层的厚度方向上的一侧的面;

第1端子,其为1层,该第1端子配置于所述基底绝缘层的所述厚度方向上的一侧的面且与所述第1布线电连接;以及

第2端子,其为1层,该第2端子配置于所述基底绝缘层的所述厚度方向上的一侧的面且与所述第2布线电连接,

所述第1端子与所述第1布线连续,

所述第2端子不与所述第2布线连续,

该布线电路基板还具备连接部,该连接部配置于所述基底绝缘层的所述厚度方向上的一侧的面且与所述第2端子连续,

所述连接部在厚度方向上与所述第2布线电连接。

2.根据权利要求1所述的布线电路基板,其特征在于,

该布线电路基板还具备镀层,该镀层配置于所述第1布线的厚度方向上的一侧的面和侧面。

3.根据权利要求1所述的布线电路基板,其特征在于,

所述第2端子的厚度与所述第1端子的厚度相同。

4.根据权利要求1所述的布线电路基板,其特征在于,

所述第2端子的厚度为20μm以下。

5.根据权利要求1所述的布线电路基板,其特征在于,

所述第2布线比所述第2端子厚。

6.根据权利要求1所述的布线电路基板,其特征在于,

所述第2布线比所述第1布线厚。

7.根据权利要求1所述的布线电路基板,其特征在于,

该布线电路基板还具备辅助布线,该辅助布线配置于所述基底绝缘层的所述厚度方向上的一侧的面且与所述连接部连续。

8.一种布线电路基板的制造方法,其特征在于,

该布线电路基板的制造方法具备以下工序:

准备基底绝缘层;

在所述基底绝缘层的厚度方向上的一侧的面形成包含第1布线、与所述第1布线连续的第1端子、与所述第1端子连续的引线、连接部、以及与所述连接部连续的第2端子的第1导体层;

通过使用所述引线进行的镀敷,从而在所述第1布线的厚度方向上的一侧的面和侧面形成镀层;

使中间绝缘层以覆盖所述镀层的方式形成于所述基底绝缘层的厚度方向上的一侧的面;以及

使包含不与所述第2端子连续的第2布线的第2导体层以所述第2布线与所述连接部的厚度方向上的一侧的面接触的方式,形成于所述中间绝缘层的厚度方向上的一侧的面。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2019-204942 | 2019-11-12 | ||

| JP2019204942A JP2021077806A (ja) | 2019-11-12 | 2019-11-12 | 配線回路基板およびその製造方法 |

| PCT/JP2020/038643 WO2021095421A1 (ja) | 2019-11-12 | 2020-10-13 | 配線回路基板およびその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN114651534A true CN114651534A (zh) | 2022-06-21 |

Family

ID=75898316

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202080077832.7A Pending CN114651534A (zh) | 2019-11-12 | 2020-10-13 | 布线电路基板和其制造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US20220386459A1 (zh) |

| JP (2) | JP2021077806A (zh) |

| KR (1) | KR20220098735A (zh) |

| CN (1) | CN114651534A (zh) |

| TW (1) | TW202133284A (zh) |

| WO (1) | WO2021095421A1 (zh) |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009129490A (ja) * | 2007-11-21 | 2009-06-11 | Nitto Denko Corp | 配線回路基板 |

| JP5699311B2 (ja) * | 2009-10-06 | 2015-04-08 | 大日本印刷株式会社 | 配線回路基板、サスペンション、ヘッド付サスペンション、ハードディスクドライブおよび配線回路基板の製造方法 |

| JP5712717B2 (ja) | 2011-03-18 | 2015-05-07 | 大日本印刷株式会社 | サスペンション用基板、サスペンション、ヘッド付サスペンション、およびハードディスクドライブ |

| JP6151654B2 (ja) * | 2014-02-25 | 2017-06-21 | 日東電工株式会社 | 配線回路基板およびその製造方法 |

-

2019

- 2019-11-12 JP JP2019204942A patent/JP2021077806A/ja active Pending

-

2020

- 2020-10-13 CN CN202080077832.7A patent/CN114651534A/zh active Pending

- 2020-10-13 KR KR1020227015155A patent/KR20220098735A/ko unknown

- 2020-10-13 WO PCT/JP2020/038643 patent/WO2021095421A1/ja active Application Filing

- 2020-10-13 US US17/775,797 patent/US20220386459A1/en active Pending

- 2020-10-15 TW TW109135621A patent/TW202133284A/zh unknown

-

2024

- 2024-07-17 JP JP2024114216A patent/JP2024128157A/ja active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| WO2021095421A1 (ja) | 2021-05-20 |

| US20220386459A1 (en) | 2022-12-01 |

| JP2024128157A (ja) | 2024-09-20 |

| KR20220098735A (ko) | 2022-07-12 |

| TW202133284A (zh) | 2021-09-01 |

| JP2021077806A (ja) | 2021-05-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100531513C (zh) | 印刷布线板的连接装置 | |

| CN100536637C (zh) | 导电连接方法 | |

| CN105493639B (zh) | 印刷布线板以及连接该布线板的连接器 | |

| US11723153B2 (en) | Printed circuit board and method of fabricating the same | |

| JP2018125414A (ja) | インダクタ装置及びその製造方法 | |

| JP2011040420A (ja) | 配線回路基板およびその製造方法 | |

| US20110048791A1 (en) | Printed circuit board and method of manufacturing the same | |

| CN106304662A (zh) | 电路板及其制作方法 | |

| JP4470935B2 (ja) | 多心同軸ケーブルおよびその製造方法 | |

| CN103338590B (zh) | 软性电路板及其制造方法 | |

| JP2009176893A (ja) | プリント配線板 | |

| CN101325840A (zh) | 防氧化印刷电路板及其金手指和该印刷电路板的制造方法 | |

| CN207766638U (zh) | 多层基板、电子设备 | |

| CN108389701A (zh) | 柔性电感器 | |

| CN114651534A (zh) | 布线电路基板和其制造方法 | |

| JP5677475B2 (ja) | プリント配線基板 | |

| JPH10233563A (ja) | プリント配線基板及びその製造方法 | |

| JP2024065885A (ja) | 配線基板 | |

| JPH10233568A (ja) | プリント配線基板の製造方法及びこれに用いるメッキ用治具 | |

| JP2002118333A (ja) | ノイズ防止回路とその形成方法 | |

| CN114651531A (zh) | 布线电路基板和其制造方法 | |

| CN114642085A (zh) | 布线电路基板 | |

| CN114830838A (zh) | 布线电路基板 | |

| JP3929302B2 (ja) | 大型回路基板 | |

| JP2016082152A (ja) | 配線板およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination |