WO2021124653A1 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- WO2021124653A1 WO2021124653A1 PCT/JP2020/038148 JP2020038148W WO2021124653A1 WO 2021124653 A1 WO2021124653 A1 WO 2021124653A1 JP 2020038148 W JP2020038148 W JP 2020038148W WO 2021124653 A1 WO2021124653 A1 WO 2021124653A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- semiconductor

- substrate

- semiconductor device

- electrode

- semiconductor substrate

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 611

- 239000000758 substrate Substances 0.000 claims abstract description 397

- 241000269800 Percidae Species 0.000 claims description 85

- 239000011347 resin Substances 0.000 claims description 26

- 229920005989 resin Polymers 0.000 claims description 26

- 239000004020 conductor Substances 0.000 claims description 23

- 238000007789 sealing Methods 0.000 claims description 5

- 238000004519 manufacturing process Methods 0.000 description 116

- 230000004048 modification Effects 0.000 description 59

- 238000012986 modification Methods 0.000 description 59

- 238000000034 method Methods 0.000 description 41

- 125000006850 spacer group Chemical group 0.000 description 28

- 239000000463 material Substances 0.000 description 19

- 239000010949 copper Substances 0.000 description 17

- 239000000853 adhesive Substances 0.000 description 10

- 230000001070 adhesive effect Effects 0.000 description 10

- 239000000919 ceramic Substances 0.000 description 9

- 238000001816 cooling Methods 0.000 description 8

- 230000000694 effects Effects 0.000 description 7

- 238000005304 joining Methods 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 6

- 238000003466 welding Methods 0.000 description 6

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 230000002093 peripheral effect Effects 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 229910000881 Cu alloy Inorganic materials 0.000 description 3

- 229920000106 Liquid crystal polymer Polymers 0.000 description 3

- 239000004977 Liquid-crystal polymers (LCPs) Substances 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 230000000149 penetrating effect Effects 0.000 description 3

- 229910000679 solder Inorganic materials 0.000 description 3

- 239000011521 glass Substances 0.000 description 2

- 238000003384 imaging method Methods 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- 230000035515 penetration Effects 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/38—Cooling arrangements using the Peltier effect

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3114—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed the device being a chip scale package, e.g. CSP

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/07—Structure, shape, material or disposition of the bonding areas after the connecting process

- H01L24/08—Structure, shape, material or disposition of the bonding areas after the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14618—Containers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/07—Structure, shape, material or disposition of the bonding areas after the connecting process

- H01L2224/08—Structure, shape, material or disposition of the bonding areas after the connecting process of an individual bonding area

- H01L2224/081—Disposition

- H01L2224/08113—Disposition the whole bonding area protruding from the surface of the body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/1605—Shape

- H01L2224/16052—Shape in top view

- H01L2224/16055—Shape in top view being circular or elliptic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48145—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

- H01L2224/48149—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked the wire connector connecting to a bonding area protruding from the surface

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N10/00—Thermoelectric devices comprising a junction of dissimilar materials, i.e. devices exhibiting Seebeck or Peltier effects

- H10N10/10—Thermoelectric devices comprising a junction of dissimilar materials, i.e. devices exhibiting Seebeck or Peltier effects operating with only the Peltier or Seebeck effects

- H10N10/17—Thermoelectric devices comprising a junction of dissimilar materials, i.e. devices exhibiting Seebeck or Peltier effects operating with only the Peltier or Seebeck effects characterised by the structure or configuration of the cell or thermocouple forming the device

Definitions

- This disclosure relates to semiconductor devices.

- an airtight sealing package containing a Pelche element As a means for cooling the solid-state imaging device, an airtight sealing package containing a Pelche element is known (see, for example, Patent Document 1).

- a Perche element is arranged between the solid-state image sensor and the protruding portion on the surface of the base.

- a semiconductor device in which a perche element is arranged on one surface side of a solid-state imaging device, such as the airtight sealing package disclosed in Patent Document 1, has dimensions in the thickness direction as compared with a semiconductor device in which the perche element is not arranged. Increases.

- a semiconductor device including a Perche element reduction in dimensions in the thickness direction (hereinafter referred to as miniaturization) is desired.

- the present disclosure has been made in view of such circumstances, and an object of the present disclosure is to provide a semiconductor device including a Perche element, which can be miniaturized.

- One aspect of the present disclosure includes a semiconductor substrate and a Perche element arranged so as to face the semiconductor substrate, and the Perche element is arranged between the first substrate, the first substrate, and the semiconductor substrate.

- the semiconductor substrate has a first electrode provided on the surface side facing the first substrate, and the first substrate is provided on the surface side facing the semiconductor substrate. It is a semiconductor device having a second electrode, and the first electrode and the second electrode are each connected to the thermoelectric semiconductor.

- the semiconductor substrate is used as the second substrate of the Pelche element (the substrate which is arranged on the opposite side of the first substrate with the thermoelectric semiconductor sandwiched between them and sandwiches the thermoelectric semiconductor with the first substrate).

- the Perche element can be integrated with the semiconductor substrate, and the number of parts of the semiconductor device can be reduced. As a result, the thickness of the semiconductor device can be reduced (reduced in height), and the size of the semiconductor device can be reduced. Further, by integrating the semiconductor substrate and the Perche element, the heat exhaust efficiency from the semiconductor substrate to the Perche element is improved. As a result, the Pelche element can improve the cooling performance of the semiconductor substrate.

- Another aspect of the present disclosure comprises a semiconductor substrate, a wiring board facing the semiconductor substrate, and a pelche element arranged between the semiconductor substrate and the wiring board, wherein the pelche element is a second substrate.

- the second substrate has a first electrode provided on a surface side facing the wiring board, and has a thermoelectric semiconductor arranged between the wiring board and the second substrate.

- the wiring board is a semiconductor device having a second electrode provided on the surface side facing the second board, and the first electrode and the second electrode are each connected to the thermoelectric semiconductor.

- the wiring board is used as the first substrate of the Pelche element (the substrate which is arranged on the opposite side of the second substrate with the thermoelectric semiconductor sandwiched between them and sandwiches the thermoelectric semiconductor with the second substrate).

- the Perche element can be integrated with the wiring board, and the number of parts of the semiconductor device can be reduced. As a result, the thickness of the semiconductor device can be reduced (reduced in height), and the size of the semiconductor device can be reduced. Further, by integrating the Perche element and the wiring board, the heat exhaust efficiency from the Perche element to the wiring board is improved. As a result, the Pelche element can improve the cooling performance of the semiconductor substrate.

- Yet another aspect of the present disclosure comprises a semiconductor substrate, a wiring board facing the semiconductor substrate, and a Perche element disposed between the semiconductor substrate and the wiring board, wherein the Perche element is the semiconductor substrate.

- the semiconductor substrate has a thermoelectric semiconductor arranged between the semiconductor substrate and the wiring substrate, the semiconductor substrate has a first electrode provided on a surface side facing the wiring substrate, and the wiring substrate faces the semiconductor substrate. It is a semiconductor device having a second electrode provided on the surface side, and the first electrode and the second electrode are each connected to a thermoelectric semiconductor.

- a wiring board can also be used as the first substrate of the Pelche element, and a semiconductor substrate can also be used as the second substrate of the Pelche element.

- the semiconductor substrate, the Perche element, and the wiring board can be integrated, and the number of parts of the semiconductor device can be reduced.

- the thickness of the semiconductor device can be reduced (reduced in height), and the size of the semiconductor device can be reduced.

- the heat exhaust efficiency from the semiconductor substrate to the wiring board is improved by integrating the semiconductor substrate and the Perche element with the wiring board.

- the Pelche element can improve the cooling performance of the semiconductor substrate.

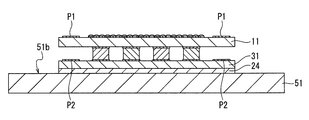

- FIG. 1 is a plan view showing a configuration example of a semiconductor device according to the first embodiment of the present disclosure.

- FIG. 2 is a cross-sectional view showing a configuration example of the semiconductor device according to the first embodiment of the present disclosure.

- FIG. 3 is a cross-sectional view showing a configuration example of the Perche element according to the first embodiment of the present disclosure.

- FIG. 4A is a cross-sectional view showing a method of manufacturing the semiconductor device according to the first embodiment of the present disclosure.

- FIG. 4B is a cross-sectional view showing a method of manufacturing the semiconductor device according to the first embodiment of the present disclosure.

- FIG. 4C is a cross-sectional view showing a method of manufacturing the semiconductor device according to the first embodiment of the present disclosure.

- FIG. 4A is a cross-sectional view showing a method of manufacturing the semiconductor device according to the first embodiment of the present disclosure.

- FIG. 4B is a cross-sectional view showing a method of manufacturing the semiconductor device according to the first embodiment of

- FIG. 4D is a cross-sectional view showing a method of manufacturing the semiconductor device according to the first embodiment of the present disclosure.

- FIG. 4E is a cross-sectional view showing a method of manufacturing the semiconductor device according to the first embodiment of the present disclosure.

- FIG. 5 is a cross-sectional view showing the configuration of the semiconductor device according to the first modification of the first embodiment of the present disclosure.

- FIG. 6A is a cross-sectional view showing the manufacturing method of the semiconductor device according to the first modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 6B is a cross-sectional view showing the manufacturing method of the semiconductor device according to the first modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 6C is a cross-sectional view showing the manufacturing method of the semiconductor device according to the first modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 6D is a cross-sectional view showing the manufacturing method of the semiconductor device according to the first modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 6E is a cross-sectional view showing the manufacturing method of the semiconductor device according to the first modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 7 is a cross-sectional view showing the configuration of the semiconductor device according to the second modification of the first embodiment of the present disclosure.

- FIG. 8A is a cross-sectional view showing the manufacturing method of the semiconductor device according to the second modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 8B is a cross-sectional view showing the manufacturing method of the semiconductor device according to the second modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 8C is a cross-sectional view showing the manufacturing method of the semiconductor device according to the second modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 8D is a cross-sectional view showing the manufacturing method of the semiconductor device according to the second modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 9 is a cross-sectional view showing the configuration of the semiconductor device according to the third modification of the first embodiment of the present disclosure.

- FIG. 10A is a cross-sectional view showing the manufacturing method of the semiconductor device according to the third modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 10B is a cross-sectional view showing the manufacturing method of the semiconductor device according to the third modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 10C is a cross-sectional view showing the manufacturing method of the semiconductor device according to the third modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 10D is a cross-sectional view showing the manufacturing method of the semiconductor device according to the third modification of the first embodiment of the present disclosure in the order of processes.

- FIG. 11 is a cross-sectional view showing the configuration of the semiconductor device according to the fourth modification of the first embodiment of the present disclosure.

- FIG. 12A is a cross-sectional view showing the manufacturing method of the semiconductor device according to the modified example 4 of the first embodiment of the present disclosure in the order of processes.

- FIG. 12B is a cross-sectional view showing the manufacturing method of the semiconductor device according to the modified example 4 of the first embodiment of the present disclosure in the order of processes.

- FIG. 12C is a cross-sectional view showing the manufacturing method of the semiconductor device according to the modified example 4 of the first embodiment of the present disclosure in the order of processes.

- FIG. 12D is a cross-sectional view showing the manufacturing method of the semiconductor device according to the modified example 4 of the first embodiment of the present disclosure in the order of processes.

- FIG. 12E is a cross-sectional view showing the manufacturing method of the semiconductor device according to the modified example 4 of the first embodiment of the present disclosure in the order of processes.

- FIG. 12C is a cross-sectional view showing the manufacturing method of the semiconductor device according to the modified example 4 of the first embodiment of the present disclosure in the order of processes.

- FIG. 12D is a cross-sectional view showing the manufacturing method of the semiconductor device according to the modified example 4 of the first embodiment of the present disclosure in the order of processes.

- FIG. 12F is a cross-sectional view showing the manufacturing method of the semiconductor device according to the modified example 4 of the first embodiment of the present disclosure in the order of processes.

- FIG. 13 is a cross-sectional view showing the configuration of the semiconductor device according to the fifth modification of the first embodiment of the present disclosure.

- FIG. 14 is a plan view showing the arrangement of the conductor according to the modified example 5 of the first embodiment of the present disclosure.

- FIG. 15 is a cross-sectional view showing the configuration of the semiconductor device according to the sixth modification of the first embodiment of the present disclosure.

- FIG. 16 is a cross-sectional view showing the configuration of the semiconductor device according to the modified example 7 of the first embodiment of the present disclosure.

- FIG. 17 is a cross-sectional view showing the configuration of the semiconductor device according to the modified example 8 of the first embodiment of the present disclosure.

- FIG. 18 is a cross-sectional view showing the configuration of the semiconductor device according to the ninth modification of the first embodiment of the present disclosure.

- FIG. 19 is a cross-sectional view showing the configuration of the semiconductor device according to the modified example 10 of the first embodiment of the present disclosure.

- FIG. 20 is a cross-sectional view showing the configuration of the semiconductor device according to the modified example 11 of the first embodiment of the present disclosure.

- FIG. 21 is a cross-sectional view showing a configuration example of the semiconductor device according to the second embodiment of the present disclosure.

- FIG. 22A is a cross-sectional view showing a method of manufacturing the semiconductor device according to the second embodiment of the present disclosure.

- FIG. 22A is a cross-sectional view showing a method of manufacturing the semiconductor device according to the second embodiment of the present disclosure.

- FIG. 22B is a cross-sectional view showing a method of manufacturing the semiconductor device according to the second embodiment of the present disclosure.

- FIG. 22C is a cross-sectional view showing a method of manufacturing the semiconductor device according to the second embodiment of the present disclosure.

- FIG. 22D is a cross-sectional view showing a method of manufacturing the semiconductor device according to the second embodiment of the present disclosure.

- FIG. 23 is a cross-sectional view showing the configuration of the semiconductor device according to the first modification of the second embodiment of the present disclosure.

- FIG. 24A is a cross-sectional view showing the manufacturing method of the semiconductor device according to the first modification of the second embodiment of the present disclosure in the order of processes.

- FIG. 24A is a cross-sectional view showing the manufacturing method of the semiconductor device according to the first modification of the second embodiment of the present disclosure in the order of processes.

- FIG. 24B is a cross-sectional view showing the manufacturing method of the semiconductor device according to the first modification of the second embodiment of the present disclosure in the order of processes.

- FIG. 24C is a cross-sectional view showing the manufacturing method of the semiconductor device according to the first modification of the second embodiment of the present disclosure in the order of processes.

- FIG. 24D is a cross-sectional view showing the manufacturing method of the semiconductor device according to the first modification of the second embodiment of the present disclosure in the order of processes.

- FIG. 25 is a cross-sectional view showing the configuration of the semiconductor device according to the second modification of the second embodiment of the present disclosure.

- FIG. 26 is a cross-sectional view showing a configuration example of the semiconductor device according to the third embodiment of the present disclosure.

- FIG. 27 is a cross-sectional view showing the configuration of the semiconductor device according to the modified example of the third embodiment of the present disclosure.

- the definition of the vertical direction in the following description is merely a definition for convenience of explanation, and does not limit the technical idea of the present disclosure. For example, if the object is rotated by 90 ° and observed, the top and bottom are converted to left and right and read, and if the object is rotated by 180 ° and observed, the top and bottom are reversed and read.

- the direction may be explained by using the wording in the X-axis direction, the Y-axis direction, and the Z-axis direction.

- the Z-axis direction is the thickness direction of the semiconductor substrate 11 described later, and is the normal direction of the lower surface 11a of the semiconductor substrate 11.

- the X-axis direction and the Y-axis direction are directions orthogonal to the Z-axis direction.

- the X-axis direction, the Y-axis direction, and the Z-axis direction are orthogonal to each other.

- planear view means viewing from the Z-axis direction.

- FIG. 1 is a plan view showing a configuration example of the semiconductor device 100 according to the first embodiment of the present disclosure.

- FIG. 2 is a cross-sectional view showing a configuration example of the semiconductor device 100 according to the first embodiment of the present disclosure.

- FIG. 2 shows a cross section of FIG. 1 cut along the X1-X'1 line.

- the semiconductor device 100 shown in FIGS. 1 and 2 is, for example, a sensor device, and includes a sensor element 10 and a perche element 30.

- the sensor element 10 is, for example, a CMOS (Complementary Metal Oxide Semiconductor) image sensor or a CCD (Charge Coupled Device) image sensor.

- the sensor element 10 may be called a sensor chip.

- the sensor element 10 is provided inside the semiconductor substrate 11, the first electrode 12 provided on the lower surface 11a side of the semiconductor substrate 11, the external connection terminal 14 provided on the upper surface 11b side of the semiconductor substrate 11, and the inside of the semiconductor substrate 11. It includes a plurality of wirings 13 provided in multiple layers, a color filter layer 15 provided on the upper surface 11b of the semiconductor substrate 11, and a microlens layer 16 provided on the color filter layer 15.

- the semiconductor substrate 11 is, for example, a silicon substrate.

- the first electrode 12 is made of, for example, copper (Cu) or a Cu alloy containing Cu as a main component.

- the sensor element 10 detects light by photoelectric conversion in the pixel region AR1 in which the color filter layer 15 and the microlens layer 16 are arranged.

- the light detected by the sensor element 10 is not limited to visible light, and may be, for example, infrared rays or ultraviolet rays.

- the external connection terminal 14 is provided outside the pixel area AR1.

- the external connection terminal 14 is, for example, a bonding pad, to which a wire such as a gold wire is connected.

- the external connection terminal 14 is connected to the perche element 30 via a wiring 13 provided inside the semiconductor substrate.

- the sensor element 10 has a pair of external connection terminals 14. Of the pair of external connection terminals 14, one external connection terminal 14 is used as a positive electrode side terminal for applying a positive potential to the Pelche element 30, and the other external connection terminal 14 applies a ground potential or a negative potential to the Pelche element 30. It is used as a negative electrode side terminal. When a voltage is applied between the pair of external connection terminals 14, a current flows from one external connection terminal 14 to the other external connection terminal 14 through a thermoelectric semiconductor 33 described later of the Pelche element 30.

- the Perche element 30 has a lower substrate 31 (an example of the "first substrate” of the present disclosure) and a thermoelectric semiconductor 33 arranged between the lower substrate 31 and the semiconductor substrate 11.

- the lower substrate 31 is, for example, a ceramic substrate.

- the lower substrate 31 has a second electrode 32 provided on the upper surface 31b side facing the semiconductor substrate 11.

- the region AR2 in which the thermoelectric semiconductor 33 is arranged overlaps with the pixel region AR1 in a plan view.

- the region AR2 in which the thermoelectric semiconductor 33 is arranged overlaps the pixel region AR1 and its peripheral region AR3 in a plan view.

- the second electrode 32 is made of, for example, Cu or a Cu alloy.

- the first electrode 12 of the semiconductor substrate 11 and the second electrode 32 of the lower substrate 31 are connected to the thermoelectric semiconductor 33, respectively.

- the semiconductor substrate 11 is not only used as a substrate of the semiconductor device 100, but is also a substrate arranged on the opposite side of the lower substrate 31 with the thermoelectric semiconductor 33 interposed therebetween, and the lower substrate 31. It is also used as a substrate that sandwiches the thermoelectric semiconductor 33 between the two.

- FIG. 3 is a cross-sectional view showing a configuration example of the perche element 30 according to the first embodiment of the present disclosure.

- the thermoelectric semiconductor 33 includes a plurality of P-type thermoelectric semiconductors 34 and a plurality of N-type thermoelectric semiconductors 35.

- the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 are arranged between the semiconductor substrate 11 and the lower substrate 31, respectively.

- the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 are arranged side by side alternately at intervals in one direction.

- the first electrode 12 of the semiconductor substrate 11 is connected to the upper end of the P-type thermoelectric semiconductor 34 and the upper end of the N-type thermoelectric semiconductor 35.

- the second electrode 32 of the lower substrate 31 is connected to the lower end of the P-type thermoelectric semiconductor 34 and the lower end of the N-type thermoelectric semiconductor 35.

- the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 are alternately connected in series via the first electrode 12 of the semiconductor substrate 11 and the second electrode 32 of the lower substrate 31.

- the Perche element 30 when a direct current is passed from the N-type thermoelectric semiconductor 35, the semiconductor substrate 11 absorbs (endothermics) heat T1 and the lower substrate 31 releases heat T2. (Dissipate heat).

- the perche element 30 can release the heat generated by the sensor element 10 to the outside of the semiconductor device 100 via the lower substrate 31.

- the manufacturing method of the semiconductor device 100 shown in FIGS. 1 and 2 will be described.

- various devices such as a device for forming the first electrode 12, a device for attaching the thermoelectric semiconductor 33, and a wire bonding device are used.

- these devices are collectively referred to as manufacturing devices.

- at least a part of the work performed by the manufacturing apparatus may be performed by a worker.

- FIG. 4A to 4E are cross-sectional views showing a method of manufacturing the semiconductor device 100 according to the first embodiment of the present disclosure.

- the manufacturing apparatus manufactures the sensor wafer 10'.

- the sensor wafer 10' is a substrate before dicing in which the sensor element 10 is formed by multi-imposition.

- the first electrode 12 (see FIG. 2) is not formed.

- the first electrode 12 is formed in the process of FIG. 4C described later.

- the manufacturing apparatus attaches the support substrate 21 to the upper surface 11b side of the semiconductor substrate 11.

- the support substrate 21 protects the upper surface 11b side of the semiconductor substrate 11 including the color filter layer 15 and the microlens layer 16.

- the manufacturing apparatus uses a vapor deposition method, a sputtering method, or a CVD method to form a copper (Cu) film on the lower surface 11a side of the semiconductor substrate 11.

- the manufacturing apparatus uses photolithography to form a resist pattern having a predetermined shape on the Cu film.

- the manufacturing apparatus etches the Cu film using the resist pattern as a mask.

- the manufacturing apparatus forms the first electrode 12 from the Cu film.

- the manufacturing apparatus may form the first electrode 12 from the Cu film by using the lift-off method.

- the manufacturing apparatus may form the first electrode 12 by any method.

- the manufacturing apparatus mounts the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 on the first electrode 12.

- a sheet to which the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 are previously attached is pressed against the lower surface 11a side of the semiconductor substrate 11, and the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor are pressed against the first electrode 12.

- the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 are mounted on the first electrode 12 by joining the semiconductors 35 to each other and then removing only the sheet.

- the manufacturing apparatus may mount the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 on the first electrode 12.

- the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 may be mounted one by one on the first electrode 12.

- the manufacturing apparatus the upper surface 31b side of the lower substrate 31 is directed downward, and the second electrode 32 of the lower substrate 31 is formed into the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35. Join each.

- the manufacturing apparatus dices the sensor wafer 10'and the lower substrate 31 to separate the semiconductor apparatus 100 into pieces. After that, the manufacturing apparatus detaches the support substrate 21 from the upper surface 11b side of the semiconductor substrate 11. Through the above steps, the semiconductor device 100 shown in FIGS. 1 and 2 is completed.

- the semiconductor device 100 includes a semiconductor substrate 11 and a Perche element 30 arranged to face the semiconductor substrate 11.

- the perche element 30 has a lower substrate 31 and a thermoelectric semiconductor 33 arranged between the lower substrate 31 and the semiconductor substrate 11.

- the semiconductor substrate 11 has a first electrode 12 provided on the lower surface 11a side facing the lower substrate 31.

- the lower substrate 31 has a second electrode 32 provided on the upper surface 31b side facing the semiconductor substrate 11.

- the first electrode 12 and the second electrode 32 are each connected to the thermoelectric semiconductor 33.

- the thermoelectric semiconductor 33 has a plurality of P-type thermoelectric semiconductors 34 and a plurality of N-type thermoelectric semiconductors 35.

- the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 are alternately connected in series via the first electrode 12 and the second electrode 32.

- the Perche element 30 As an upper substrate of the Perche element 30 (a substrate arranged on the opposite side of the lower substrate 31 with the thermoelectric semiconductor 33 sandwiched between them, and a substrate sandwiching the thermoelectric semiconductor 33 with the lower substrate 31).

- the semiconductor substrate 11 can also be used.

- the Perche element 30 can be integrated with the semiconductor substrate 11, and the number of parts of the semiconductor device 100 can be reduced. As a result, the thickness of the semiconductor device 100 can be reduced (reduced in height), and the semiconductor device 100 can be miniaturized.

- the heat exhaust efficiency from the semiconductor substrate 11 to the Perche element 30 is improved. Since there is no substrate (upper substrate) for supporting the thermoelectric semiconductor 33 between the semiconductor substrate 11 and the Perche element 30, heat is efficiently exhausted from the semiconductor substrate 11 to the Perche element 30. As a result, the Perche element 30 can improve the cooling performance of the semiconductor substrate 11.

- the input and output of the current to the Perche element 30 are performed not through the lead-out wiring dedicated to the Perche element drawn out to the outside of the semiconductor substrate 11, but through the wiring such as a gold wire connected to the external connection terminal 14. Since the drawer wiring dedicated to the Pelche element is not required, the space can be further reduced. As a result, the semiconductor device 100 can be further miniaturized.

- the upper substrate of the Pelche element 30, the drawer wiring dedicated to the Pelche element, and the adhesive for joining the upper substrate and the semiconductor substrate are not required, and the number of parts can be reduced. As a result, the cost of the semiconductor device 100 can be reduced.

- the warp of the semiconductor substrate 11 can be suppressed. That is, since a general resin has a coefficient of linear expansion larger than that of an adhesive base material or a device, it expands and contracts or its elastic modulus changes depending on the temperature. Therefore, it tends to cause the semiconductor substrate 11 to warp. However, in the semiconductor device 100, since there is no resin for adhesion between the semiconductor substrate 11 and the thermoelectric semiconductor 33, the warp of the semiconductor substrate 11 can be suppressed.

- FIG. 5 is a cross-sectional view showing the configuration of the semiconductor device 100A according to the first modification of the first embodiment of the present disclosure.

- the semiconductor substrate 11 of the semiconductor device 100A may be provided with a through electrode 22 (an example of the “first through electrode” of the present disclosure) penetrating the semiconductor substrate 11 in the thickness direction.

- the through silicon via 22 penetrates between the lower surface 11a and the upper surface 11b of the semiconductor substrate 11.

- the through electrode 22 is made of a metal such as Cu.

- the through electrode 22 may be used as an external connection terminal for applying an electric potential to the perche element 30.

- the sensor element 10 has a pair of through electrodes 22 provided in a peripheral region AR3 (see FIG. 1) located outside the pixel region AR1 (see FIG. 1).

- the upper end of the through electrode 22 is used as a bonding pad exposed on the upper surface 11b side of the semiconductor substrate 11.

- a wire such as a gold wire is connected to the bonding pad.

- the lower end of the through electrode 22 is connected to the first electrode 12 of the sensor element 10. Even with such a configuration, the semiconductor device 100A has the same effect as the above-mentioned semiconductor device 100.

- the semiconductor device 100A shown in FIG. 5 may also be provided with an external connection terminal 14 as shown in FIG. 2 in addition to the through electrode 22. Further, although not shown in FIG. 5, the wiring 13 may be provided inside the semiconductor substrate 11.

- FIG. 6A to 6E are cross-sectional views showing the manufacturing method of the semiconductor device 100A according to the first modification of the first embodiment of the present disclosure in the order of processes.

- the manufacturing method described with reference to FIGS. 4A and 4B is the same up to the step of attaching the support substrate 21 to the upper surface 11b side of the semiconductor substrate 11.

- the manufacturing apparatus turns the semiconductor substrate 11 upside down so that the lower surface 11a side of the semiconductor substrate 11 faces upward. Then, the manufacturing apparatus forms a through hole (via) H1 penetrating between the lower surface 11a and the upper surface 11b of the semiconductor substrate 11 from the lower surface 11a side of the semiconductor substrate 11. Next, the manufacturing apparatus forms the through electrode 22 inside the through hole H1. Next, as shown in FIG. 6C, the manufacturing apparatus forms the first electrode 12 on the lower surface 11a side of the semiconductor substrate 11. The lower end portion of the through electrode 22 (the upper end portion in FIG. 6C) is covered with the first electrode 12.

- the manufacturing apparatus mounts the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 on the first electrode 12.

- the manufacturing apparatus has a P-type thermoelectric semiconductor 34 and an N-type thermoelectric semiconductor 35 on the second electrode 32 of the lower substrate 31 with the upper surface 31b side of the lower substrate 31 facing downward. Join each.

- the manufacturing apparatus dices the sensor wafer 10'and the lower substrate 31 to separate the semiconductor apparatus 100A into pieces. After that, the manufacturing apparatus detaches the support substrate 21 from the upper surface 11b side of the semiconductor substrate 11.

- the semiconductor device 100A shown in FIG. 5 is completed.

- FIG. 7 is a cross-sectional view showing the configuration of the semiconductor device 100B according to the second modification of the first embodiment of the present disclosure.

- the semiconductor device 100B includes a package main body 50 and a lid 60 attached to the upper surface side of the package main body 50.

- the package body 50 and the lid 60 constitute a package 70 that houses the sensor element 10 and the perche element 30 and seals them airtightly.

- a bonding pad P1 connected to the sensor element 10 is provided on the upper surface 111b side of the semiconductor substrate 11.

- a wire 23 is bonded to the bonding pad P1.

- the sensor element 10 can input and output a power source and a signal via the bonding pad P1 and the wire 23.

- a bonding pad P2 for inputting and outputting a current to the Pelche element 30 is provided on the upper surface 111b side of the lower substrate 11.

- the bonding pad P2 is connected to a second electrode 32 provided on the upper surface 111b side of the lower substrate 11. Further, a wire 123 is bonded to the bonding pad P2. A current is applied to the perche element 30 via the wire 123 and the bonding pad P2.

- the bonding pads P1 and P2 are composed of, for example, an Al alloy containing aluminum (Al) or Al as a main component, or a Cu alloy containing copper (Cu) or Cu as a main component.

- the wires 32 and 132 are, for example, gold wires.

- the package body 50 has a bottom portion 51 to which the lower substrate 31 of the Pelche element 30 is attached via the die bond material 24, and a wall portion 52 arranged around the bottom portion 51.

- the bottom portion 51 and the wall portion 52 are integrally formed.

- the sensor element 10 and the Pelche element 30 are arranged in the space 53 inside the package 70 surrounded by the bottom portion 51 and the wall portion 52.

- the package body 50 is made of, for example, ceramic.

- the lid 60 is made of a material that transmits light detected by the sensor element 10, and is made of, for example, a translucent glass material or a translucent resin.

- the lid 60 may have a frame (not shown) that is joined to the wall of the package body 50 without gaps.

- the frame is made of, for example, ceramic or metal.

- a bonding pad (not shown) is provided to which one end of each of the wires 23 and 123 such as a gold wire is connected.

- the bonding pad to which the wire 23 is connected and the bonding pad to which the wire 123 is connected are separated from each other and are electrically separated from each other.

- a plurality of wirings (not shown) are provided in multiple layers inside the bottom portion 51. These wirings are connected to a bonding pad provided on the upper surface 51b side of the bottom portion and a plurality of terminals (not shown) provided on the lower surface 51a side of the bottom portion 51.

- the plurality of terminals provided on the lower surface 51a side of the bottom portion 51 may be pin-shaped terminals protruding in the normal direction of the lower surface 51a, or ball-shaped terminals.

- the through electrode 22 of the sensor element 10 includes a wire 23, a bonding pad provided on the upper surface 51b side of the bottom portion 51, wiring provided inside the bottom portion 51, and a terminal provided on the lower surface 51a side of the bottom portion. It is pulled out to the outside of the package 70 via.

- the sensor element 10 and the Pelche element 30 are arranged in the space 53 inside the package 70 and are hermetically sealed.

- the semiconductor device 100B can suppress the adhesion of foreign matter to the sensor element 10, and can reduce the possibility that the operation of the sensor element 10 is affected by the foreign matter.

- FIG. 8A to 8D are cross-sectional views showing the manufacturing method of the semiconductor device 100B according to the second modification of the first embodiment of the present disclosure in the order of processes.

- the thermoelectric semiconductor 33 is attached to the lower surface 11a side of the semiconductor substrate 11, the semiconductor device 100A is separated by dicing, and then the support substrate 21 is detached with reference to FIGS. 6A to 6E. It is the same as the manufacturing method described.

- the manufacturing apparatus applies the die bond material 24 to the upper surface 51b side of the bottom portion 51 of the package body 50, as shown in FIG. 8B.

- the manufacturing apparatus attaches the lower substrate 31 to the upper surface 51b side of the bottom 51 via the die bond material 24.

- the manufacturing apparatus connects the bonding pad P1 of the sensor element 10 and the bonding pad (not shown) provided on the upper surface 51b side of the bottom portion 51 with a wire 23.

- a bonding pad provided on the upper surface 31b side of the lower substrate 31 and a bonding pad (not shown) provided on the upper surface 51b side of the bottom portion 51 are connected by a wire 123.

- the manufacturing apparatus attaches the lid 60 to the wall portion 52 of the package body 50 by means such as seam welding in a state where the lid 60 and the package body 50 are aligned with each other. As a result, the space 53 between the lid 60 and the package body 50 is airtightly sealed.

- Seam welding is a type of resistance welding, and is a method of continuous welding by rotating the electrodes while applying pressure and energizing using roller electrodes.

- the atmosphere inside the package that is, the space 53

- the atmosphere inside the package can be kept in dry air, nitrogen, or vacuum by creating an atmosphere such as dry air, nitrogen, or vacuum in the chamber provided in the seam welding apparatus. ..

- the joining between the lid 60 and the package body 50 is not limited to seam welding.

- the joining of the lid 60 and the package body 50 may be, for example, joining using an adhesive.

- FIG. 9 is a cross-sectional view showing the configuration of the semiconductor device 100C according to the third modification of the first embodiment of the present disclosure.

- the package body 50 included in the semiconductor device 100C has a bottom portion 51 to which the lower substrate 31 of the Pelche element 30 is attached via the die bond material 24, and a wall portion 52A arranged around the bottom portion 51.

- the bottom portion 51 and the wall portion 52A are formed separately, and are made of, for example, different materials from each other.

- the bottom 51 is made of ceramic, while the wall 52A is made of resin or metal.

- the bottom portion 51 and the wall portion 52A are joined to each other via, for example, an adhesive (not shown).

- the semiconductor device 100C has the same effect as the semiconductor device 100B. Further, as will be described in the manufacturing method described later, before the wall portion 52A is attached around the bottom portion 51, the perche element 30 and the sensor element 10 are attached to the upper surface 51b side of the bottom portion 51, or wire bonding is performed. be able to. When the sensor element 10 is attached to the package body 50, there is no wall portion 52A on the upper surface 51b side of the bottom portion 51, and the upper surface 51b of the bottom portion 51 is flat. Is easy. Therefore, the semiconductor device 100C may be able to improve the productivity as compared with the semiconductor device 100B.

- FIG. 10A to 10D are cross-sectional views showing the manufacturing method of the semiconductor device 100C according to the third modification of the first embodiment of the present disclosure in the order of processes.

- the manufacturing method described with reference to FIGS. 8A and 8B is the same up to the step of applying the die bond material 24 to the upper surface 51b side of the bottom portion 51 of the package body 50A.

- the manufacturing apparatus After applying the die bond material 24, as shown in FIG. 10B, the manufacturing apparatus attaches the lower substrate 31 to the upper surface 51b side of the bottom portion 51 via the die bond material 24.

- the manufacturing apparatus connects the bonding pad P1 of the sensor element 10 and the bonding pad (not shown) provided on the upper surface 51b side of the bottom portion 51 with a wire 23 (first). Wire bonding process).

- the manufacturing apparatus connects the bonding pad P2 of the lower substrate 31 and the bonding pad (not shown) provided on the upper surface 51b side of the bottom portion 51 with a wire 123 (second wire bonding step).

- the manufacturing apparatus attaches the wall portion 52A to the upper surface 51b side of the bottom portion 51 via an adhesive or the like.

- the first wire bonding step and the second wire bonding step may be performed after the wall portion 52A mounting step is performed.

- the manufacturing apparatus attaches the lid 60 to the wall portion 52A of the package body 50, and airtightly seals the space 53 between the lid 60 and the package body 50.

- the semiconductor device 100C shown in FIG. 9 is completed.

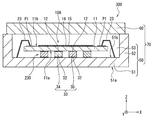

- FIG. 11 is a cross-sectional view showing the configuration of the semiconductor device 100D according to the fourth modification of the first embodiment of the present disclosure.

- the package format of the semiconductor device 100D is a wafer level chip size package.

- an insulating first spacer 25 is provided between the semiconductor substrate 11 and the lower substrate 31 and outside the region AR2 in which the thermoelectric semiconductor 33 is arranged.

- the first spacer 25 is an insulating frame that surrounds the region AR2 in which the thermoelectric semiconductor 33 is arranged without any gap in a plan view.

- the first spacer 25 may be made of an insulating resin or a ceramic.

- the upper end of the first spacer 25 is bonded to the lower surface 11a of the semiconductor substrate 11, and the lower end of the first spacer 25 is bonded to the upper surface 31b of the lower substrate 31.

- a through wiring 26 that penetrates the first spacer 25 in the Z-axis direction (thickness direction of the semiconductor device 100) is provided.

- the through wiring 26 is made of a metal such as Cu.

- the through wiring 26 is connected to a wiring 13 provided inside the semiconductor substrate 11 and a through electrode 36 penetrating between the lower surface 31a and the upper surface 31b of the lower substrate 31, respectively.

- the through electrode 36 is made of a metal such as Cu.

- a rewiring layer 37 (an example of the "second rewiring layer” of the present disclosure) is provided on the lower surface 31a side, which is the opposite side of the surface facing the semiconductor substrate 11.

- the rewiring layer 37 has, for example, a wiring 38 provided in multiple layers and an insulating layer 39 that insulates between the wiring 38 of one layer and the wiring 38 of the other layer.

- the wiring 38 is made of a metal such as Cu.

- the insulating layer 39 is made of, for example, a solder resist.

- a plurality of bump electrodes 40 are provided on the lowermost surface of the rewiring layer 37.

- the bump electrode 40 is connected to the wiring 38.

- the bump electrode 40 is made of, for example, a solder ball.

- a second spacer 45 is provided between the upper surface 11b of the semiconductor substrate 11 and the lid 60 and outside the region where the color filter layer 15 and the microlens layer 16 are arranged.

- the second spacer 45 is an insulating frame that surrounds the region where the color filter layer 15 and the microlens layer 16 are arranged without any gap in a plan view.

- the second spacer 45 is provided so as to overlap the first spacer 25 in the Z-axis direction via the semiconductor substrate 11.

- the second spacer 45 may be made of an insulating resin or a ceramic.

- the upper end of the second spacer 45 is bonded to the lid 60, and the lower end of the second spacer 45 is bonded to the upper surface 11b of the semiconductor substrate 11.

- the space between the semiconductor substrate 11 and the lower substrate 31 is hermetically sealed by the frame-shaped first spacer 25. Further, the space between the semiconductor substrate 11 and the lid 60 is hermetically sealed with a frame-shaped second spacer 45.

- the electrical connection between the semiconductor substrate 11 and the lower substrate 31 is made not through a wire such as a gold wire, but through a through wiring 26 in the first spacer 25. Since the semiconductor device 100D is a wafer level chip size package and does not require wires, it can be further thinned and miniaturized.

- the space between the semiconductor substrate 11 and the lid 60 and surrounded by the second spacer 45 may be hollow and may be filled with a translucent resin (that is, a transparent resin). May be good.

- FIG. 12A to 12F are cross-sectional views showing the manufacturing method of the semiconductor device 100D according to the fourth modification of the first embodiment of the present disclosure in the order of processes.

- the manufacturing method described with reference to FIGS. 6A and 6B is the same up to the step of forming the sensor wafer 10'formed by the sensor element 10 by multi-imposition and forming the through electrode 22 on the sensor wafer 10'. Is.

- the manufacturing apparatus After forming the through silicon via 22, the manufacturing apparatus forms the second spacer 45 on the upper surface 11b side of the sensor wafer 10'.

- the second spacer 45 may be formed by using a wafer process, or the second spacer 45 prepared in advance may be attached to the upper surface 11b side via an adhesive or the like.

- the manufacturing apparatus mounts the lid 60 on the second spacer 45. As a result, the space between the semiconductor substrate 11 and the lid 60 is hermetically sealed.

- the semiconductor substrate 11 is turned upside down so that the lid 60 faces downward, and the first electrode 12 is placed on the lower surface 11a side (upper side in FIG. 12C) of the semiconductor substrate 11.

- the manufacturing apparatus forms a first spacer 25 on the lower surface 11a side of the semiconductor substrate 11, and joins the through wiring 26 located inside the first spacer 25 to the through electrode 22 of the semiconductor substrate 11.

- the manufacturing apparatus mounts the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 on the first electrode 12.

- the upper surface 31b side of the lower substrate 31 is directed downward, and the second electrode 32 of the lower substrate 31 is formed into the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35.

- the through electrode 36 of the lower substrate 31 is joined to the through wiring 26 located inside the first spacer 25.

- the manufacturing apparatus forms a rewiring layer 37 on the lower surface 31a side of the lower substrate 31.

- the manufacturing apparatus uses, for example, a semi-additive method or a subtractive method to form the rewiring layer 37.

- the manufacturing apparatus connects the wiring 38 to the through electrode 36 of the lower substrate 31.

- the manufacturing apparatus forms a plurality of bump electrodes 40 (see FIG. 11) on the lowermost surface (the uppermost surface in FIG. 12F) of the rewiring layer 37.

- the sensor wafer 10' is diced together with the lower substrate 31.

- FIG. 13 is a cross-sectional view showing the configuration of the semiconductor device 100E according to the fifth modification of the first embodiment of the present disclosure.

- FIG. 14 is a plan view showing the arrangement of the conductor 80 according to the fifth modification of the first embodiment of the present disclosure.

- the semiconductor device 100E is arranged between the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35, and is electrically separated from the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35, respectively.

- the conductor 80 is provided.

- the conductor 80 is arranged adjacent to the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 at intervals.

- the conductor 80 is a connection terminal for connecting the semiconductor substrate 11 and the rewiring layer 37.

- the conductor 80 penetrates between the upper surface 31b and the lower surface 31a of the lower substrate 31.

- the lower end of the conductor 80 is connected to the wiring 38 of the rewiring layer 37.

- an electrode 18 is provided on the lower surface 11a side of the semiconductor substrate 11.

- the electrode 18 is provided at a position away from the first electrode 12, and is electrically separated from the first electrode 12.

- the upper end of the conductor 80 is connected to the electrode 18.

- the conductor 80 connects the semiconductor substrate 11 and the rewiring layer 37 via the electrode 18.

- the conductor 80 is used as a signal line or a power supply line between the semiconductor substrate 11 and the rewiring layer 37.

- the conductor 80 connects the semiconductor substrate 11 and the rewiring layer 37 without bypassing the Perche element 30. Since the semiconductor device 100E can shorten the wiring length between the semiconductor substrate 11 and the rewiring layer 37, it is possible to reduce the impedance.

- an insulating resin may be filled between the semiconductor substrate 11 and the lower substrate 31. Since the conductor 80 is supported from the horizontal direction (direction parallel to the XY plane) by the resin between the semiconductor substrate 11 and the lower substrate 31, the conductor 80 with respect to the semiconductor substrate 11 and the lower substrate 31 Bond strength is improved.

- the space between the semiconductor substrate 11 and the lid 60 and surrounded by the second spacer 45 may be hollow or filled with a transparent resin. It may have been done.

- the semiconductor device is a sensor device including the color filter layer 15 and the microlens layer 16 has been described.

- the semiconductor device is not limited to the sensor device.

- the semiconductor device according to the first embodiment may be an integrated circuit (IC) or a large-scale integrated circuit (LSI) that executes an arbitrary function.

- FIG. 15 is a cross-sectional view showing the configuration of the semiconductor device 100F according to the sixth modification of the first embodiment of the present disclosure.

- the semiconductor device 100F shown in FIG. 15 is an IC or an LSI, and includes an IC element 10A and a Perche element 30.

- the IC element 10A may be called an IC chip.

- the IC element 10A is provided inside the semiconductor substrate 11, the first electrode 12 provided on the lower surface 11a side of the semiconductor substrate 11, the external connection terminal 14 provided on the upper surface 11b side of the semiconductor substrate 11, and the inside of the semiconductor substrate 11.

- a plurality of wirings 13 provided in multiple layers are provided.

- the perche element 30 has a lower substrate 31 and a thermoelectric semiconductor 33 arranged between the lower substrate 31 and the semiconductor substrate 11.

- the first electrode 12 of the semiconductor substrate 11 and the second electrode 32 of the lower substrate 31 are connected to the thermoelectric semiconductor 33, respectively.

- the semiconductor substrate 11 is used not only as a substrate of the semiconductor device 100F, but also as an upper substrate of the Perche element 30.

- the semiconductor substrate 11 is also used as the upper substrate of the Perche element 30.

- the perche element 30 is integrated with the semiconductor substrate 11, and the number of parts can be reduced. As a result, the thickness of the semiconductor device 100F can be reduced, and the size of the semiconductor device 100F can be reduced.

- FIG. 16 is a cross-sectional view showing the configuration of the semiconductor device 100G according to the modified example 7 of the first embodiment of the present disclosure.

- the thermoelectric semiconductor 33 is arranged below the central portion of the semiconductor substrate 11, but the thermoelectric semiconductor 33 is not arranged below the outer peripheral portion of the semiconductor substrate 11. ..

- the thermoelectric semiconductor 33 is unevenly arranged below the central portion of the semiconductor substrate 11.

- thermoelectric semiconductor 33 when the semiconductor substrate 11 is a silicon substrate, silicon has excellent thermal conductivity, so that a sufficient cooling effect can be obtained.

- the thermoelectric semiconductor 33 unevenly below the central portion of the semiconductor substrate 11, an empty space is created below the outer peripheral portion of the semiconductor substrate 11.

- the conductor 80 shown in FIG. 13 may be provided in this empty space.

- FIG. 17 is a cross-sectional view showing the configuration of the semiconductor device 100H according to the modified example 8 of the first embodiment of the present disclosure.

- the semiconductor device 100H shown in FIG. 17 is an embodiment in which the rewiring layer 37 and the bump electrode 40 are provided on the semiconductor device 100F shown in FIG.

- the rewiring layer 137 (the "first rewiring layer” of the present disclosure) is on the upper surface 11b side opposite to the surface facing the lower substrate 31. An example) is provided.

- the rewiring layer 137 has, for example, a wiring 138 provided in multiple layers and an insulating layer 139 that insulates between the wiring 138 of one layer and the wiring 138 of the other layer. Further, a plurality of bump electrodes 140 are provided on the uppermost surface of the rewiring layer 137. The bump electrode 140 is connected to the wiring 138. The bump electrode 140 is made of, for example, a solder ball. In the semiconductor device 100H, a current can be passed through the Pelche element 30 via the bump electrode 140.

- FIG. 18 is a cross-sectional view showing the configuration of the semiconductor device 100I according to the ninth modification of the first embodiment of the present disclosure.

- an insulating resin 61 is filled between the semiconductor substrate 11 and the lower substrate 31.

- the resin 61 seals the semiconductor substrate 11 and the lower substrate 31 without a gap.

- the resin 61 is in close contact with the side surface of the thermoelectric semiconductor 33, and prevents the thermoelectric semiconductor from being exposed to the outside air or moisture. Further, the resin 61 supports the thermoelectric semiconductor 33 from the horizontal direction (direction parallel to the XY plane). As a result, the bonding strength of the thermoelectric semiconductor 33 with respect to the semiconductor substrate 11 and the lower substrate 31 is improved.

- FIG. 19 is a cross-sectional view showing the configuration of the semiconductor device 100J according to the modified example 10 of the first embodiment of the present disclosure.

- the semiconductor device 100J shown in FIG. 19 is an embodiment in which the rewiring layer 137 and the bump electrode 140 are provided on the semiconductor device 100I shown in FIG.

- a current can be passed through the Perche element 30 via the bump electrode 140.

- FIG. 20 is a cross-sectional view showing the configuration of the semiconductor device 100K according to the modified example 11 of the first embodiment of the present disclosure.

- the semiconductor device 100K includes a package main body 50 and a lid 60 attached to the upper surface side of the package main body 50.

- the package 70 is composed of the package body 50 and the lid 60.

- the semiconductor device 100K the IC element 10A and the Pelche element 30 are arranged in the space 53 inside the package 70 and are hermetically sealed. As a result, the semiconductor device 100K can suppress the adhesion of foreign matter to the IC element 10A, and can reduce the possibility that the operation of the IC element 10A is affected by the foreign matter.

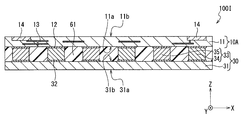

- FIG. 21 is a cross-sectional view showing a configuration example of the semiconductor device 200 according to the second embodiment of the present disclosure.

- the semiconductor device 200 shown in FIG. 21 is, for example, a sensor device, and includes a sensor element 10, a perche element 130, and a package 70.

- the sensor element 10 is, for example, a CMOS image sensor or a CCD image sensor.

- the perche element 130 has an upper substrate 111 (an example of the "second substrate” of the present disclosure) and a thermoelectric semiconductor 33 arranged between the upper substrate 111 and the wiring substrate.

- the upper substrate 111 is, for example, a ceramic substrate.

- the first electrode 12 is provided on the lower surface 111a side of the upper substrate 111.

- the upper surface 111b of the upper substrate 111 is fixed to the lower surface 11a of the semiconductor substrate 11 via the die bond material 124.

- a bonding pad P1 connected to the sensor element 10 is provided on the upper surface 111b side of the semiconductor substrate 11.

- a wire 23 is bonded to the bonding pad P1.

- the sensor element 10 can input and output a power source and a signal via the bonding pad P1 and the wire 23.

- the package 70 includes a package body 50 and a lid 60 attached to the upper surface side of the package body 50.

- the sensor element 10 and the Pelche element 130 are hermetically sealed by the package body 50 and the lid 60.

- the package body 50 has a bottom portion 51 (an example of the “wiring board” of the present disclosure) to which the thermoelectric semiconductor 33 of the Pelche element 130 is attached, and a wall portion 52 arranged around the bottom portion 51.

- the bottom portion 51 and the wall portion 52 are integrally formed.

- the sensor element 10 and the Pelche element 130 are arranged in the space 53 inside the package 70 surrounded by the bottom portion 51 and the wall portion 52.

- the second electrode 32 is provided on the upper surface 51b side of the bottom portion 51 of the package body 50.

- the first electrode 12 provided on the upper substrate 111 and the second electrode 32 provided on the bottom 51 are connected to the thermoelectric semiconductor 33, respectively.

- the bottom portion 51 is not only used as a part of the package body 50, but is also a substrate arranged on the lower substrate of the Pelche element 30A (a substrate arranged on the opposite side of the upper substrate 111 with the thermoelectric semiconductor 33 interposed therebetween, and with the upper substrate 111. It is also used as a substrate that sandwiches the thermoelectric semiconductor 33 between them).

- wiring for inputting and outputting a current to the Pelche element 130 is provided.

- This wiring is connected to the second electrode 32.

- This wiring is formed at the same time as, for example, the second electrode 32 in the same process.

- 22A to 22D are cross-sectional views showing a method of manufacturing the semiconductor device 200 according to the second embodiment of the present disclosure.

- the manufacturing apparatus has a second electrode 32 on the upper surface 51b side of the bottom portion 51 of the package body 50, and wiring (not shown) for inputting and outputting a current to the Pelche element 130.

- the manufacturing apparatus mounts the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35 on the second electrode 32.

- the manufacturing apparatus mounts the upper substrate 111 on the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35.

- the first electrode 12 provided on the lower surface 111a side of the upper substrate 111 is joined to the P-type thermoelectric semiconductor 34 and the N-type thermoelectric semiconductor 35, respectively.

- the manufacturing apparatus prepares the color filter layer 15, the microlens layer 16, and the semiconductor substrate 11 on which the bonding pad P1 is formed on the upper surface 11b side. Then, the manufacturing apparatus attaches the lower surface 11a side of the semiconductor substrate 11 to the upper surface 111b side of the upper substrate 111 via the die bond material 124. Next, the manufacturing apparatus connects the bonding pad P1 of the sensor element 10 and the bonding pad (not shown) provided on the upper surface 51b side of the bottom portion 51 with a wire 23.

- the manufacturing apparatus attaches the lid 60 to the wall portion 52 of the package body 50. As a result, the space 53 between the lid 60 and the package body 50 is airtightly sealed. Through the above steps, the semiconductor device 200 shown in FIG. 21 is completed.

- the semiconductor device 200 includes a semiconductor substrate 11 and a Perche element 130 arranged to face the semiconductor substrate 11.

- the perche element 130 has an upper substrate 111 and a thermoelectric semiconductor 33 arranged between the bottom 51 of the package body 50 and the upper substrate 111.

- the upper substrate 111 has a first electrode 12 provided on the lower surface 111a side facing the bottom 51 of the package body 50.

- the bottom portion 51 of the package main body 50 has a second electrode 32 provided on the upper surface 111b side facing the upper substrate 111.

- the first electrode 12 and the second electrode 32 are each connected to the thermoelectric semiconductor 33.

- the package main body is used as a lower substrate of the Pelche element 130 (a substrate arranged on the opposite side of the upper substrate 111 with the thermoelectric semiconductor interposed therebetween and sandwiching the thermoelectric semiconductor with the upper substrate 111).

- the bottom 51 of 50 can also be used.