KR890004998B1 - 마이크로 콤퓨터 시스템용 게이트회로 - Google Patents

마이크로 콤퓨터 시스템용 게이트회로 Download PDFInfo

- Publication number

- KR890004998B1 KR890004998B1 KR1019850000791A KR850000791A KR890004998B1 KR 890004998 B1 KR890004998 B1 KR 890004998B1 KR 1019850000791 A KR1019850000791 A KR 1019850000791A KR 850000791 A KR850000791 A KR 850000791A KR 890004998 B1 KR890004998 B1 KR 890004998B1

- Authority

- KR

- South Korea

- Prior art keywords

- gate

- circuit

- transistor

- gate circuit

- stage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

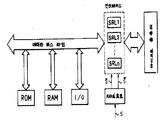

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

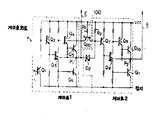

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/003—Modifications for increasing the reliability for protection

- H03K19/00307—Modifications for increasing the reliability for protection in bipolar transistor circuits

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/003—Modifications for increasing the reliability for protection

- H03K19/00346—Modifications for eliminating interference or parasitic voltages or currents

- H03K19/00353—Modifications for eliminating interference or parasitic voltages or currents in bipolar transistor circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

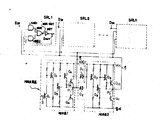

- H03K19/01—Modifications for accelerating switching

- H03K19/013—Modifications for accelerating switching in bipolar transistor circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/15—Arrangements in which pulses are delivered at different times at several outputs, i.e. pulse distributors

- H03K5/151—Arrangements in which pulses are delivered at different times at several outputs, i.e. pulse distributors with two complementary outputs

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- Mathematical Physics (AREA)

- Theoretical Computer Science (AREA)

- Nonlinear Science (AREA)

- General Physics & Mathematics (AREA)

- Logic Circuits (AREA)

- Pulse Circuits (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP59-022966 | 1984-02-13 | ||

| JP59022966A JPS60172821A (ja) | 1984-02-13 | 1984-02-13 | Ttl回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR850006088A KR850006088A (ko) | 1985-09-28 |

| KR890004998B1 true KR890004998B1 (ko) | 1989-12-04 |

Family

ID=12097318

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019850000791A Expired KR890004998B1 (ko) | 1984-02-13 | 1985-02-08 | 마이크로 콤퓨터 시스템용 게이트회로 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US4703202A (enExample) |

| EP (1) | EP0156477B1 (enExample) |

| JP (1) | JPS60172821A (enExample) |

| KR (1) | KR890004998B1 (enExample) |

| DE (1) | DE3568117D1 (enExample) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4939391A (en) * | 1986-05-30 | 1990-07-03 | Advanced Micro Devices, Inc. | Programmable logic device with observability and preload circuitry for buried state registers |

| US4839537A (en) * | 1986-11-29 | 1989-06-13 | Kabushiki Kaisha Toshiba | BicMO logic circuit |

| US4777391A (en) * | 1987-07-17 | 1988-10-11 | Signetics Corporation | Bipolar multiplexer having a select buffer circuit with a charging and discharging circuit |

| US4973862A (en) * | 1989-03-07 | 1990-11-27 | National Semiconductor Corporation | High speed sense amplifier |

| US5027010A (en) * | 1989-10-04 | 1991-06-25 | Motorola, Inc. | TTL output driver having an increased high output level |

| JPH05122017A (ja) * | 1991-10-29 | 1993-05-18 | Mitsubishi Electric Corp | シユミツトトリガ入力バツフア回路 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3962589A (en) * | 1975-02-10 | 1976-06-08 | National Semiconductor Corporation | Inverter with minimum skew |

| JPS5378159A (en) * | 1976-12-22 | 1978-07-11 | Fujitsu Ltd | Logic circuit |

| JPS544560A (en) * | 1977-06-14 | 1979-01-13 | Nec Corp | Semiconductor inverter circuit |

| JPS5592040A (en) * | 1978-12-29 | 1980-07-12 | Fujitsu Ltd | Ttl gate circuit |

| DE3279782D1 (en) * | 1982-03-24 | 1989-07-27 | Ibm | True/complement generator |

| US4424455A (en) * | 1982-04-22 | 1984-01-03 | Motorola, Inc. | Glitch eliminating data selector |

-

1984

- 1984-02-13 JP JP59022966A patent/JPS60172821A/ja active Granted

-

1985

- 1985-02-08 KR KR1019850000791A patent/KR890004998B1/ko not_active Expired

- 1985-02-11 US US06/700,413 patent/US4703202A/en not_active Expired - Fee Related

- 1985-02-13 EP EP85300929A patent/EP0156477B1/en not_active Expired

- 1985-02-13 DE DE8585300929T patent/DE3568117D1/de not_active Expired

Also Published As

| Publication number | Publication date |

|---|---|

| EP0156477A1 (en) | 1985-10-02 |

| JPH0318770B2 (enExample) | 1991-03-13 |

| JPS60172821A (ja) | 1985-09-06 |

| KR850006088A (ko) | 1985-09-28 |

| DE3568117D1 (en) | 1989-03-09 |

| US4703202A (en) | 1987-10-27 |

| EP0156477B1 (en) | 1989-02-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100239099B1 (ko) | 전자 플립-플롭 회로 | |

| US4841233A (en) | Semiconductor integrated circuit adapted to carry out operation test | |

| US4800529A (en) | Semiconductive memory device with current control and comparison means to reduce power consumption and increase operating speed | |

| US5459421A (en) | Dynamic-static master slave flip-flop circuit | |

| KR100284985B1 (ko) | 인에이블제어회로를갖춘집적회로 | |

| KR910000388B1 (ko) | 메모리셀 블록의 선택적 동작이 가능한 반도체 메모리장치 | |

| US3953746A (en) | Selector latch gate | |

| US4334157A (en) | Data latch with enable signal gating | |

| KR890004998B1 (ko) | 마이크로 콤퓨터 시스템용 게이트회로 | |

| US4970693A (en) | Semiconductor memory device with internal control signal based upon output timing | |

| US4845681A (en) | GaAs SCFL RAM | |

| US6998878B2 (en) | Semiconductor integrated circuit and semiconductor logic circuit used in the integrated circuit | |

| US4274017A (en) | Cascode polarity hold latch having integrated set/reset capability | |

| US4733377A (en) | Asynchronous semiconductor memory device | |

| EP0311102B1 (en) | Semiconductor ic including circuit for preventing erroneous operation caused by power source noise | |

| KR100247472B1 (ko) | 반도체기억장치및반도체집적회로장치 | |

| US4800552A (en) | Semiconductor memory device with reset signal generating circuit | |

| JP2760431B2 (ja) | メモリ | |

| KR940008285B1 (ko) | 최소의 잡음을 가지는 데이타출력 드라이버 | |

| JPS62271296A (ja) | 半導体集積回路 | |

| JPH05315902A (ja) | Eclラッチ回路 | |

| JPH0417197A (ja) | 半導体メモリ装置 | |

| JPH06232726A (ja) | 入力回路、及び半導体集積回路 | |

| KR890007290A (ko) | 레벨변환기를 구비한 반도체 메모리 장치 | |

| KR19990057925A (ko) | 출력버퍼 제어회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| G160 | Decision to publish patent application | ||

| PG1605 | Publication of application before grant of patent |

St.27 status event code: A-2-2-Q10-Q13-nap-PG1605 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 7 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 8 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 9 |

|

| FPAY | Annual fee payment |

Payment date: 19981116 Year of fee payment: 10 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 10 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| LAPS | Lapse due to unpaid annual fee | ||

| PC1903 | Unpaid annual fee |

St.27 status event code: A-4-4-U10-U13-oth-PC1903 Not in force date: 19991205 Payment event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE |

|

| PC1903 | Unpaid annual fee |

St.27 status event code: N-4-6-H10-H13-oth-PC1903 Ip right cessation event data comment text: Termination Category : DEFAULT_OF_REGISTRATION_FEE Not in force date: 19991205 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |