KR20210122100A - 상판 및 그 제조 방법 - Google Patents

상판 및 그 제조 방법 Download PDFInfo

- Publication number

- KR20210122100A KR20210122100A KR1020210034972A KR20210034972A KR20210122100A KR 20210122100 A KR20210122100 A KR 20210122100A KR 1020210034972 A KR1020210034972 A KR 1020210034972A KR 20210034972 A KR20210034972 A KR 20210034972A KR 20210122100 A KR20210122100 A KR 20210122100A

- Authority

- KR

- South Korea

- Prior art keywords

- top plate

- coating

- blank

- region

- central region

- Prior art date

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 9

- 239000011248 coating agent Substances 0.000 claims abstract description 71

- 238000000576 coating method Methods 0.000 claims abstract description 71

- 239000011324 bead Substances 0.000 claims abstract description 56

- 238000004528 spin coating Methods 0.000 claims abstract description 20

- 238000000034 method Methods 0.000 claims description 31

- 239000000758 substrate Substances 0.000 claims description 27

- 239000000203 mixture Substances 0.000 claims description 6

- 238000012545 processing Methods 0.000 claims description 4

- 235000012431 wafers Nutrition 0.000 description 37

- 239000000463 material Substances 0.000 description 22

- 239000010410 layer Substances 0.000 description 14

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 10

- 239000004926 polymethyl methacrylate Substances 0.000 description 10

- 238000000926 separation method Methods 0.000 description 9

- 230000000052 comparative effect Effects 0.000 description 7

- -1 poly(methyl methacrylate) Polymers 0.000 description 7

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 6

- 230000008569 process Effects 0.000 description 6

- 230000007547 defect Effects 0.000 description 5

- 238000005530 etching Methods 0.000 description 5

- 229920000642 polymer Polymers 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 4

- 239000005350 fused silica glass Substances 0.000 description 4

- 239000008199 coating composition Substances 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 239000010408 film Substances 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 239000007788 liquid Substances 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 239000011253 protective coating Substances 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 239000004065 semiconductor Substances 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 238000005520 cutting process Methods 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 229920002313 fluoropolymer Polymers 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000002904 solvent Substances 0.000 description 2

- 239000011029 spinel Substances 0.000 description 2

- 229910052596 spinel Inorganic materials 0.000 description 2

- 238000005406 washing Methods 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- 230000003044 adaptive effect Effects 0.000 description 1

- 239000005399 alkali-barium silicate glass Substances 0.000 description 1

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 1

- 239000005354 aluminosilicate glass Substances 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000003618 dip coating Methods 0.000 description 1

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 239000012530 fluid Substances 0.000 description 1

- 239000004811 fluoropolymer Substances 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 229920000592 inorganic polymer Polymers 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910001092 metal group alloy Inorganic materials 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 239000000178 monomer Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 229920000620 organic polymer Polymers 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 229920000139 polyethylene terephthalate Polymers 0.000 description 1

- 239000005020 polyethylene terephthalate Substances 0.000 description 1

- 229920006254 polymer film Polymers 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 150000004756 silanes Chemical class 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000005361 soda-lime glass Substances 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 238000000427 thin-film deposition Methods 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/687—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches

- H01L21/68714—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support

- H01L21/68757—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using mechanical means, e.g. chucks, clamps or pinches the wafers being placed on a susceptor, stage or support characterised by a coating or a hardness or a material

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/0015—Production of aperture devices, microporous systems or stamps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/67005—Apparatus not specifically provided for elsewhere

- H01L21/67011—Apparatus for manufacture or treatment

- H01L21/6715—Apparatus for applying a liquid, a resin, an ink or the like

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B05—SPRAYING OR ATOMISING IN GENERAL; APPLYING FLUENT MATERIALS TO SURFACES, IN GENERAL

- B05D—PROCESSES FOR APPLYING FLUENT MATERIALS TO SURFACES, IN GENERAL

- B05D1/00—Processes for applying liquids or other fluent materials

- B05D1/002—Processes for applying liquids or other fluent materials the substrate being rotated

- B05D1/005—Spin coating

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/0002—Lithographic processes using patterning methods other than those involving the exposure to radiation, e.g. by stamping

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

- H01L21/02225—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer

- H01L21/0226—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process

- H01L21/02282—Forming insulating materials on a substrate characterised by the process for the formation of the insulating layer formation by a deposition process liquid deposition, e.g. spin-coating, sol-gel techniques, spray coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/31051—Planarisation of the insulating layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76804—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics by forming tapered via holes

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Application Of Or Painting With Fluid Materials (AREA)

Abstract

상판은 상판 블랭크 및 상판 블랭크의 외부 표면 위에 놓인 코팅을 포함할 수 있다. 상판 블랭크는 중심 영역 및 테이퍼진 에지 영역을 포함할 수 있고; 테이퍼진 에지 영역은 상판 블랭크의 길이방향에 대해 20도 이하의 평균 테이퍼 각도를 갖는다. 일 실시예에서, 상판의 코팅은 스핀 코팅에 의해 도포될 수 있고 중심 영역 내의 코팅 표면의 평면 아래에 에지 비드를 가질 수 있다.

Description

본 개시내용은 코팅을 포함하는 상판(superstrate) 및 상판의 제조 방법에 관한 것이다.

잉크젯 적응 평탄화(Inkjet Adaptive Planarization)(IAP)는 작업 표면의 평탄도가 높은 상판의 사용을 필요로 한다. IAP 프로세스용으로 설계된 상판은 결함을 감소시키고 처리량을 증가시키며 그 수명을 연장하기 위해 얇은 폴리머 막으로 코팅되는 경우가 많다. 코팅은 통상적으로 스핀 코팅에 의해 도포된다. 스핀 코팅에서 흔히 관찰되는 문제는, 에지 비드(edge bead)라고도 명명되는, 코팅 외부 단부의 두께 증가이다. 에지 비드는 생산 결함 또는 평탄화에 사용 가능한 전체 작업 영역의 감소를 초래할 수 있다. 후속 처리 작업에 의해 에지 비드를 제거하는 것이 공지되어 있지만, 이는 추가적인 작업 노력을 필요로 하고 다른 결함이 발생할 수 있다.

특히, 상판의 품질을 개선하는 것이, 구체적으로 결함이 없는 높은 표면 평탄도, 높은 처리량으로 긴 수명, 및 실제 작업 표면적의 높은 비율과 같은 특성을 결합하는 것이 요구된다. 그러한 상판의 제조 효율을 개선시키는 것이 더욱 바람직하다.

일 실시예에서, 상판은 상판 블랭크 및 상판 블랭크의 외부 표면 위에 놓인 코팅을 포함할 수 있으며, 상판 블랭크는 중심 영역 및 테이퍼진 에지 영역을 포함할 수 있고; 테이퍼진 에지 영역은 상판 블랭크의 반경방향에 대해 20도 이하의 테이퍼 각도를 가질 수 있으며; 코팅은 상판 블랭크의 중심 영역 및 테이퍼진 에지 영역의 적어도 일부 위에 놓일 수 있다.

일 양태에서, 상판의 코팅은 테이퍼진 에지 영역 내에 에지 비드를 포함할 수 있으며, 에지 비드의 정점은 상판의 중심 영역에서 코팅의 외부 표면의 평면 아래에 있을 수 있다.

추가 양태에서, 상판 블랭크의 표면적 비율 Sc:St는 적어도 15일 수 있고, Sc는 중심 영역의 표면적이고 St는 테이퍼진 에지 영역의 표면적이다.

다른 양태에서, 상판 블랭크의 높이 방향에 대한 상판 블랭크의 중심 영역의 외부 표면의 레벨로부터 상판 블랭크의 외부 에지에서의 테이퍼의 깊이(Td)는 적어도 20 미크론, 400 미크론 이하일 수 있다.

추가 양태에서, 상판의 반경방향으로 테이퍼진 에지 영역의 길이(Tl)는 적어도 1.0 mm일 수 있다.

또 추가 양태에서, 상판 블랭크는 중심 영역 내에서 적어도 100 미크론, 5000 미크론 이하의 평균 두께를 가질 수 있다.

다른 양태에서, 상판의 코팅은 중심 영역 내에서 적어도 0.1 미크론, 10 미크론 이하의 평균 두께를 가질 수 있다.

또 다른 특정 양태에서, 테이퍼진 에지 영역은 10도 이하의 테이퍼 각도를 가질 수 있다.

다른 실시예에서, 상판의 형성 방법은, 중심 영역 및 테이퍼진 에지 영역을 포함하는 상판 블랭크를 준비하는 단계로서, 상판 블랭크의 반경방향에 대한 테이퍼진 에지 영역의 테이퍼 각도는 20도 이하일 수 있는, 단계; 및 상판 블랭크의 외부 표면 상에 코팅을 도포하는 단계를 포함하고, 코팅은 중심 영역 전체 및 테이퍼진 에지 영역의 적어도 일부 위에 놓인다.

방법의 일 양태에서, 상판 블랭크 상에 코팅을 도포하는 단계는 스핀 코팅을 포함할 수 있다.

방법의 또 다른 양태에서, 스핀 코팅은 상판 블랭크의 테이퍼진 에지 영역 내에 에지 비드를 형성하는 것을 포함할 수 있다.

일 양태에서, 방법은 에지 비드를 제거하는 단계를 더 포함할 수 있다. 특정 양태에서, 에지 비드의 제거는 용매로 세정하는 단계를 포함할 수 있다.

방법의 일 양태에서, 상판 블랭크의 표면적 비율 Sc:St는 적어도 15일 수 있고, Sc는 중심 영역의 표면적이고 St는 테이퍼진 에지 영역의 표면적이다.

방법의 또 다른 양태에서, 스핀 코팅은 상판 블랭크 상에 에지 비드를 형성하는 단계를 포함하지 않을 수 있다.

방법의 추가 양태에서, 상판의 반경방향으로 테이퍼진 에지 영역의 길이(Tl)는 적어도 1.0 mm일 수 있다.

방법의 또 다른 양태에서, 코팅은 중심 영역 내에서 적어도 0.1 미크론, 10 미크론 이하의 평균 두께를 가질 수 있다.

방법의 다른 양태에서, 상판 블랭크의 높이 방향에 대한 상판 블랭크의 중심 영역의 외부 표면의 레벨로부터 상판 블랭크의 외부 에지에서의 테이퍼의 깊이(Td)는 적어도 20 미크론, 400 미크론 이하일 수 있다.

추가 양태에서, 테이퍼진 에지 영역의 테이퍼 각도는 10도 이하일 수 있다.

일 실시예에서, 물품의 제조 방법은, 기판 상에 형성 가능한 조성물의 층을 도포하는 단계; 형성 가능한 조성물을 상판과 접촉시키는 단계로서, 상판은 상판 블랭크 및 상판 블랭크의 외부 표면 위에 놓인 코팅을 포함하고, 상판 블랭크는 중심 영역 및 테이퍼진 에지 영역을 포함하며, 테이퍼진 에지 영역은 상판 블랭크의 길이방향에 대해 20도 이하의 테이퍼 각도를 갖고, 코팅은 상판 블랭크의 중심 영역 및 테이퍼진 에지 영역의 적어도 일부 위에 놓이는, 단계; 형성 가능한 조성물을 광 또는 열로 경화시켜 경화된 층을 형성하는 단계; 경화된 층으로부터 상판을 제거하는 단계; 및 경화된 층으로 기판을 처리하여 물품을 제조하는 단계를 포함한다.

실시예는 예로서 예시되며 첨부 도면에서 제한되지 않는다.

도 1은 일 실시예에 따른 상판을 형성하는 방법을 설명하는 방식을 포함한다.

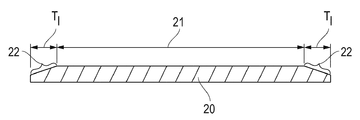

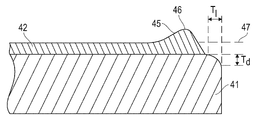

도 2a는 일 실시예에 따른 상판 블랭크의 측면도를 예시한다.

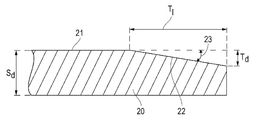

도 2b는 일 실시예에 따른 도 2a에 도시된 상판 블랭크의 일부의 확대 측면도를 예시한다.

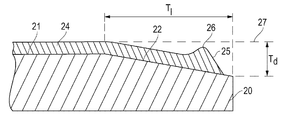

도 3a는 일 실시예에 따른 상판의 일부의 측면도를 예시한다.

도 3b는 비교 상판의 일부의 측면도를 예시한다.

도 3c는 비교 코팅된 웨이퍼의 일부의 측면도를 예시한다.

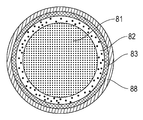

도 4a는 일 실시예에 따른 상판의 평면도를 예시한다.

도 4b는 비교 상판의 평면도를 예시한다.

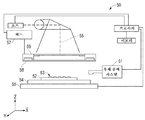

도 5는 일 실시예에 따른 상판을 포함하는 장치를 예시한다.

도 6은 일 실시예에 따른 예 1의 상판의 테이퍼진 에지 영역 내에 코팅의 형상 및 상판 블랭크의 대응하는 형상을 예시하는 그래프를 포함한다.

숙련자라면 도면의 요소가 단순성과 명료성을 위해 예시되었으며 반드시 실척으로 작성되지 않았음을 인식한다. 예를 들어, 도면에서 일부 요소의 치수는 본 발명의 실시예의 이해를 증진시키는 데 도움을 주도록 다른 요소에 비해 과장될 수 있다.

도 1은 일 실시예에 따른 상판을 형성하는 방법을 설명하는 방식을 포함한다.

도 2a는 일 실시예에 따른 상판 블랭크의 측면도를 예시한다.

도 2b는 일 실시예에 따른 도 2a에 도시된 상판 블랭크의 일부의 확대 측면도를 예시한다.

도 3a는 일 실시예에 따른 상판의 일부의 측면도를 예시한다.

도 3b는 비교 상판의 일부의 측면도를 예시한다.

도 3c는 비교 코팅된 웨이퍼의 일부의 측면도를 예시한다.

도 4a는 일 실시예에 따른 상판의 평면도를 예시한다.

도 4b는 비교 상판의 평면도를 예시한다.

도 5는 일 실시예에 따른 상판을 포함하는 장치를 예시한다.

도 6은 일 실시예에 따른 예 1의 상판의 테이퍼진 에지 영역 내에 코팅의 형상 및 상판 블랭크의 대응하는 형상을 예시하는 그래프를 포함한다.

숙련자라면 도면의 요소가 단순성과 명료성을 위해 예시되었으며 반드시 실척으로 작성되지 않았음을 인식한다. 예를 들어, 도면에서 일부 요소의 치수는 본 발명의 실시예의 이해를 증진시키는 데 도움을 주도록 다른 요소에 비해 과장될 수 있다.

다음 설명은 본 명세서에 개시된 교시를 이해하는 것을 돕기 위해 제공되며 교시의 특정 구현 및 실시예에 초점을 맞출 것이다. 이 초점은 교시를 설명하는 데 도움이 되도록 제공되며 교시의 범위 또는 적용 가능성에 대한 제한으로서 해석되어서는 안된다.

달리 정의되지 않는 한, 본 명세서에서 사용된 모든 기술적 및 과학적 용어는 본 발명이 속하는 기술 분야의 숙련자에 의해 일반적으로 이해되는 것과 동일한 의미를 갖는다. 재료, 방법, 및 예는 예시일 뿐이며 제한하려는 의도는 없다. 본 명세서에 설명되지 않은 한, 특정 재료 및 처리 동작에 관한 많은 세부 사항은 통상적이며 임프린트 및 리소그래피 분야 내의 교과서 및 기타 소스에서 찾을 수 있다.

본 명세서에서 사용될 때, 용어 "구비한다", "구비하는", "포함한다", "포함하는", "갖는다", "갖는" 또는 그 임의의 다른 변형은 비배타적 포함을 포괄하도록 의도된다. 예를 들어, 피처의 목록을 포함하는 프로세스, 방법, 물품, 또는 장치는 반드시 이들 피처로만 제한되지 않고, 명시적으로 나열되지 않았거나 그러한 프로세스, 방법, 물품, 또는 장치에 고유하지 않은 다른 피처를 포함할 수 있다.

본 명세서에서 사용될 때, 그리고 달리 명시적으로 언급되지 않는 한, "또는"은 포괄적 또는을 지칭하고 배타적 또는을 지칭하지 않는다. 예를 들어, 조건 A 또는 B는 다음 중 임의의 하나에 의해 충족된다: A는 참(또는 존재함)이고 B는 거짓(또는 존재하지 않음)이며, A는 거짓(또는 존재하지 않음)이고 B는 참(또는 존재함)이며, A와 B가 모두 참(또는 존재함)이다.

또한, "a" 또는 "an"의 사용은 본 명세서에 설명된 요소 및 구성요소를 설명하는 데 사용된다. 이는 단지 편의를 위해 그리고 본 발명의 범위에 대한 일반적인 의미를 제공하도록 행해진다. 이 설명은 하나 또는 적어도 하나를 포함하도록 읽어야 하며, 단수는 또한 달리 의도하는 것이 명백하지 않는 한 복수를 포함한다.

본 개시내용은 상판 블랭크 및 상판 블랭크의 외부 표면 위에 놓인 코팅을 포함하는 상판에 관한 것이다. 상판 블랭크는 중심 영역 및 테이퍼진 에지 영역을 포함하도록 설계된다. 일 실시예에서, 테이퍼진 에지 영역은 상판 블랭크 상의 코팅의 스핀 코팅 동안 형성된 에지 비드를 위한 위치일 수 있으며, 코팅의 에지 비드의 정점은 상판의 중심 영역에서 코팅의 외부 표면의 평면 아래에 있을 수 있다. 다른 실시예에서, 스핀 코팅 동안 에지 비드의 형성이 완전히 방지될 수 있다.

도 1에 예시된 바와 같이, 본 개시내용의 상판을 형성하는 방법은 다음의 단계를 포함할 수 있다: 11) 중심 영역 및 테이퍼진 에지 영역을 포함하는 상판 블랭크를 형성하는 단계로서, 상판 블랭크의 길이방향에 대한 테이퍼진 에지 영역의 테이퍼 각도는 20도 이하인 단계, 및 12) 상판 블랭크의 외부 표면 상에 코팅을 도포하는 단계로서, 코팅은 중심 영역 전체 및 테이퍼진 에지 영역의 적어도 일부 위에 놓이는, 단계.

상판 블랭크의 형성 단계(11)는 표준 상업용 웨이퍼, 예를 들어 원형 웨이퍼 잉곳으로부터 절단된 얇은 슬라이스를 사용하고, 웨이퍼 재료를 제거하도록 웨이퍼를 제어된 절단 및/또는 연마를 받게 하여 웨이퍼의 에지 영역에 평활한 감소 테이퍼를 형성함으로써 수행될 수 있다. 특정 실시예에서, 테이퍼는 제어된 연마에 의해 형성될 수 있다. 다른 양태에서, 웨이퍼의 테이퍼는 제어된 에칭에 의해 제조될 수 있다.

도 2a는 상판 블랭크의 중심 영역(21) 및 테이퍼진 에지 영역(22)을 보여주는, 본 개시내용의 실시예에 따른 상판 블랭크(20)의 측면도의 예시를 포함한다.

도 2b는 도 2a에 도시된 상판의 확대된 섹션을 예시하는 것으로, 전체 테이퍼진 에지 영역(22) 및 중심 영역(21)의 일부를 보여준다. 중심 영역(21)으로부터 테이퍼진 에지 영역(22)으로의 평활한 천이를 볼 수 있다. 테이퍼진 에지 영역(22) 전체에 걸친 테이퍼의 평균 테이퍼 각도(23)는 20도 이하일 수 있다. 특정 양태에서, 도 2b에 예시된 바와 같이, 테이퍼 각도는 테이퍼진 에지 영역 전체에 걸쳐 동일할 수 있다. 다른 특정 양태(도시되지 않음)에서, 테이퍼 각도는 테이퍼진 에지 영역 내에서 달라질 수 있으며, 예를 들어 테이퍼 각도는 외부 에지를 향해 증가할 수 있다. 양태에서, 테이퍼진 에지 영역 전체에 걸친 평균 테이퍼 각도는 18도 이하, 예를 들어 15도 이하, 10도 이하, 8도 이하, 7도 이하, 6도 이하, 5도 이하, 또는 3도 이하일 수 있다.

특정 양태에서, 중심 영역(21) 및 테이퍼진 에지 영역(22)을 포함하는 상판 블랭크의 직경은 적어도 50 mm, 예를 들어 적어도 100 mm, 적어도 150 mm, 적어도 200 mm, 적어도 250 mm, 적어도 280 mm, 또는 적어도 290 mm일 수 있다. 다른 양태에서, 중심 영역의 직경은 600 nm 이하, 예를 들어 500 mm 이하, 450 mm 이하, 또는 400 mm 이하일 수 있다. 상판 블랭크의 직경은 위에서 언급한 임의의 최소값과 최대값 사이의 값일 수 있다.

일 양태에서, 상판 블랭크의 표면적 비율 Sc:St(Sc는 중심 영역(21)의 표면적이고, St는 테이퍼진 에지 영역(21)의 표면적임)는 적어도 15, 예를 들어 적어도 20, 적어도 30, 적어도 40, 적어도 45, 또는 적어도 50일 수 있다.

또 다른 양태에서, 중심 영역(21)에서 상판 블랭크의 두께(Sd)는 적어도 100 미크론, 예를 들어 적어도 150 미크론, 적어도 200 미크론, 적어도 300 미크론, 적어도 500 미크론, 적어도 1000 미크론, 또는 적어도 2000 미크론일 수 있다. 다른 양태에서, 두께는 5000 미크론 이하, 4000 미크론 이하, 또는 3000 미크론 이하일 수 있다. 중심 영역에서 상판 블랭크의 두께는 위에서 언급한 임의의 최소값과 최대값 사이의 값일 수 있다.

본 개시내용의 상판 블랭크의 테이퍼진 에지 영역(22)은 적어도 1.0 mm, 예를 들어 적어도 1.5 mm, 적어도 1.8 mm, 적어도 2.0 mm, 적어도 2.3 mm, 적어도 2.5 mm, 또는 적어도 3.0 mm의 반경방향(x-축)으로의 길이(Tl)를 가질 수 있다. 다른 양태에서, 테이퍼진 에지 영역(Tl)은 5.0 mm 이하, 예를 들어 4.5 mm 이하, 4.0 mm 이하, 또는 3.5 mm 이하일 수 있다. 테이퍼진 에지 영역의 Tl는 위에서 언급한 임의의 최소 수 및 최대 수 사이의 값일 수 있다는 것이 이해될 것이다.

추가 양태에서, 상판 블랭크의 높이 방향(y-축)으로 상판 블랭크의 중심 영역의 외부 표면의 레벨로부터 상판 블랭크의 외부 에지에서 테이퍼의 깊이(Td)는 적어도 20 미크론, 예를 들어 적어도 30 미크론, 또는 적어도 50 미크론, 또는 적어도 80 미크론, 또는 적어도 100 미크론일 수 있다. 다른 양태에서, 테이퍼 깊이(Td)는 400 미크론 이하, 예를 들어 350 미크론 이하, 300 미크론 이하, 250 미크론 이하, 200 미크론 이하, 또는 150 미크론 이하일 수 있다. 테이퍼의 깊이(Td)는 위에서 언급한 임의의 최소값과 최대값 사이의 값일 수 있다. 특정 예에서, Td는 중심 영역에서 상판 블랭크의 두께와 동일할 수 있다. 예를 들어, 상판 블랭크의 두께가 중심 영역에서 100 미크론인 경우, Td도 100 미크론일 수 있다.

상판 블랭크는 다양한 재료로 제조될 수 있다. 재료의 비제한적인 예는 유리 기반 재료, 실리콘, 스피넬, 융합 실리카, 석영, 유기 폴리머, 실록산 폴리머, 플루오로카본 폴리머, 금속, 금속 합금, 경화된 사파이어, 퇴적된 산화물, 양극 산화된 알루미나, 유기 실란, 유기 실리케이트 재료, 무기 폴리머, 또는 이들의 임의의 조합을 포함할 수 있다. 유리 기반 재료는 소다 석회 유리, 붕규산염 유리, 알칼리-바륨 실리케이트 유리, 석영 유리, 알루미노실리케이트 유리, 또는 합성 융합 실리카를 포함할 수 있다.

본 개시내용의 방법의 일 실시예에서, 상판 블랭크(12) 상에 코팅을 도포하는 것은 스핀 코팅에 의해 수행될 수 있다. 전술한 구조의 테이퍼진 상판 블랭크를 사용함으로써, 상판 블랭크 상에 보호 코팅이 형성될 수 있으며, 코팅의 에지 비드는 테이퍼의 경사를 따라 아래로 이동될 수 있다.

본 개시내용의 특정 양태에서, 에지 비드의 형성은 심지어는 완전히 방지될 수 있다. 이는 본 발명의 테이퍼진 에지 영역을 포함하지 않는 상판 블랭크 상에서 스핀 코팅을 수행하면 달성될 수 없다.

도 3a는 상판의 실시예를 예시하고 코팅(24)은 스핀 코팅을 통해 상판 블랭크(20) 상에 도포된다. 도 3a는 테이퍼진 에지 영역(22) 전체 및 중심 영역(21)의 일부를 갖는 상판의 섹션 만을 도시한다. 코팅(24)이 상판 블랭크의 중심 영역(21) 위에 균일하게 놓일 수 있고 테이퍼진 에지 영역(22) 내에 에지 비드(25)를 형성할 수 있음을 알 수 있다. 일 양태에서, 에지 비드(25)의 정점(26)은 중심 영역(21) 내의 코팅(24)의 외부 표면의 평면(27) 아래에 있을 수 있다.

일 실시예에서, 코팅(24)은 폴리머 코팅일 수 있다. 폴리머 코팅 재료의 비제한적인 예는 폴리(메틸 메타크릴레이트)(poly(methyl methacrylate))(PMMA), 플루오로폴리머, 또는 폴리에틸렌 테레프탈레이트 또는 평탄화 프로세스 동안 형성 가능한 재료를 경화하는 데 사용되는 선택된 화학 방사선, 예를 들어, 특정 UV 광파 범위에 투명한 임의의 폴리머일 수 있다.

다른 실시예에서, 코팅(24)은 중심 영역 내에서 적어도 0.1 미크론, 예를 들어 적어도 0.5 미크론, 적어도 1.0 미크론, 적어도 2.0 미크론, 적어도 3 미크론, 또는 적어도 5 미크론의 평균 두께를 가질 수 있다. 또 다른 양태에서, 중심 영역 내의 코팅은 10 미크론 이하, 예를 들어 8 미크론 이하, 또는 6 미크론 이하일 수 있다. 중심 영역 내의 코팅 두께는 위에서 언급한 임의의 최소값과 최대값 사이의 값일 수 있다.

특정 실시예에서, 코팅(24)은 단일층 코팅일 수 있다. 다른 특정 실시예에서, 코팅은 다층 코팅일 수 있다.

코팅(24)은 중심 영역 전체에 걸쳐 높은 평탄도와 평활도를 가질 수 있다. 일 양태에서, 중심 영역 내의 코팅의 표면 거칠기는 5 nm 이하, 예를 들어 3 nm 이하, 2 nm 이하, 1.5 nm 이하, 또는 1 nm 이하일 수 있다.

본 개시내용의 상판의 추가 이점은 테이퍼진 에지 영역이 상판의 분리 구역의 일부일 수 있다는 점일 수 있다. 분리 구역은 기판으로부터 상판을 분리하는 것을 돕기 위해 평탄화 단계 후에 상판과 기판 사이의 진공을 파괴하는 기능을 갖는 리세스 또는 간극을 포함할 수 있는 상판의 외부 에지에 있는 영역이다. 분리 구역은 통상적으로 약 2-3 mm의 반경방향 길이를 가지며 기판의 평탄화를 위한 접촉 표면적으로서 참여하지 않는다. 도 4a에 예시된 바와 같이, 테이퍼진 에지 영역(73) 및 분리 구역(78)이 동일한 웨이퍼 영역을 덮도록 분리 구역을 테이퍼진 에지 영역으로 수정함으로써, 형성된 에지 비드를 분리 구역의 영역으로 전달하고 기판 평탄화에 적절한 큰 표면적(71)을 획득하는 것이 가능하다. 비교하면, 스핀 코팅된 보호 코팅이 있는 통상적인 상판은 도 4b에 예시된 바와 같이 분리 구역(88) 및 분리 구역(88) 옆에 에지 비드 구역(83)을 포함한다. 더욱이, 본 명세서에서 "에지-이웃 구역"(82)이라고 명명되는 에지 비드 구역(83) 옆의 영역을 고려해야 하며, 훨씬 더 높은 결함 가능성이 에지 비드를 제거하는 노력에 의해 야기되는 것으로 예상될 수 있고 또한 기판을 평탄화하기 위한 적절한 표면적(81)으로부터 차감될 수 있다. 따라서, 본 발명의 상판은, 큰 표면적(71)이 기판을 평탄화하는 데 사용될 수 있고, 에지 비드의 제거가 필요없을 수 있다는 이점이 있다. 더욱이, 이를 통해 추가 프로세스 단계를 피할 수 있고 에지 비드를 제거하는 동안 상판에 손상을 일으킬 위험을 감소시킬 수 있다.

도 5를 참조하면, 본 명세서에 설명된 실시예에 따른 장치(50)는 본 개시내용의 상판(58)을 사용하여 기판(52)을 평탄화하는 데 사용될 수 있다. 상판(58)은 기판(52)으로부터 이격되어 위치 설정될 수 있다.

기판(52)은 실리콘 웨이퍼와 같은 반도체 모재일 수 있지만, 유리, 사파이어, 스피넬 등과 같은 절연성 모재를 포함할 수 있다. 기판(52)은 기판 홀더(54), 예를 들어 척에 결합될 수 있다. 척은 진공, 핀형, 홈형, 정전기, 전자기 등을 포함하는 임의의 척일 수 있다. 기판(52) 및 기판 홀더(54)는 스테이지(56)에 의해 추가로 지지될 수 있다. 스테이지(56)는 X, Y, 또는 Z 방향을 따라 병진 또는 회전 운동을 제공할 수 있다.

상판(58)은 기판(52) 상에 퇴적된 형성 가능한 재료를 평탄화하는 데 사용될 수 있다. 상판(58)은 상판 홀더(59)에 결합될 수 있다. 상판(58)은 상판 홀더(59)에 의해 유지되고 그 형상이 조절될 수 있다. 상판 홀더(59)는 척킹 영역 내에 상판(58)을 유지하도록 구성될 수 있다. 상판 홀더(59)는 진공, 핀형, 홈형, 정전기, 전자기, 또는 다른 유사한 홀더 유형으로 구성될 수 있다. 일 실시예에서, 상판 홀더(59)는 상판 홀더(59)의 본체 내에 투명 윈도우를 포함할 수 있다.

장치(50)는 기판(52)의 표면 상에 형성 가능한 재료(53)를 퇴적하기 위한 유체 분배 시스템(51)을 더 포함할 수 있다. 형성 가능한 재료(53)는, 액적 분배, 스핀 코팅, 딥 코팅, 화학 기상 증착(chemical vapor deposition)(CVD), 물리 기상 증착(physical vapor deposition)(PVD), 박막 퇴적, 후막 퇴적, 또는 이들의 조합과 같은 기술을 사용하여 하나 이상의 층으로 기판(52) 상에 위치 설정될 수 있다. 형성 가능한 재료(53)는 원하는 체적이 상판(58)과 기판(52) 사이에 형성되기 전 또는 후에 기판(52) 상에 분배될 수 있다. 형성 가능한 재료(53)는 화학 방사선 및/또는 열을 사용하여 경화될 수 있는 하나 이상의 중합 가능한 모노머 및/또는 올리고머 및/또는 폴리머를 포함할 수 있다.

본 개시내용은 또한 물품을 제조하는 방법에 관한 것이다. 이 방법은, 기판 상에 형성 가능한 재료의 층을 도포하는 단계; 형성 가능한 재료의 층을 본 개시내용의 상판과 접촉시키는 단계; 및 형성 가능한 재료를 광 또는 열로 경화시켜 경화된 층을 형성하는 단계를 포함할 수 있다. 기판 및 경화된 층은, 예를 들어, 고체화된 층 및/또는 고체화된 층 아래에 있는 패턴화된 층 중 하나 또는 둘 모두의 패턴에 대응하는 이미지를 기판으로 전사하는 에칭 프로세스를 포함함으로써, 원하는 물품을 형성하도록 추가 처리를 받을 수 있다. 기판은, 예를 들어 경화, 산화, 층 형성, 퇴적, 도핑, 평탄화, 에칭, 형성 가능한 재료 제거, 다이싱, 접합, 및 패키징 등을 비롯하여 디바이스(물품) 제조를 위한 공지된 단계 및 프로세스를 추가로 받을 수 있다. 특정 양태에서, 기판은 복수의 물품을 생성하도록 처리될 수 있다.

경화된 층은 LSI, 시스템 LSI, DRAM, SDRAM, RDRAM 또는 D-RDRAM과 같은 반도체 디바이스의 개재층 절연막으로서, 또는 반도체 제조 프로세스에서 사용되는 레지스트 막으로서 추가로 사용될 수 있다.

예에서 추가로 입증된 바와 같이, 에지 비드의 정점이 중심 영역의 코팅 레벨보다 아래에 있을 수 있음을 야기할 수 있는 특정 테이퍼진 에지 설계를 상판 블랭크가 포함하는 경우, 상판 블랭크 상의 보호 코팅의 스핀 코팅 동안 형성된 원치않는 에지 비드가 용인될 수 있다는 것을 발견하였다.

예

다음의 비제한적인 예는 본 명세서에 설명된 개념을 예시한다.

예 1

300 mm의 직경 및 700 미크론의 두께를 갖는 원형 융합 실리카 웨이퍼를 웨이퍼의 에지 영역에서 제어된 절단을 받게 하여 테이퍼를 형성함으로써 상판 블랭크를 제조하였다. 절단은 연마에 의해 수행되었다.

획득된 상판 블랭크는 다음의 에지 프로파일을 갖는다: 1,8667 mm의 테이퍼진 에칭 영역의 길이(Tl); 226 미크론의 웨이퍼의 외부 에지에서의 테이퍼 깊이(Td); 및 6.8°의 테이퍼 각도.

MicroChem사의 액체 코팅 조성물 495 PMMA 8 ml을 스핀 코팅을 통해 도포하고 약 180℃의 온도에서 경화시킴으로써 상판 블랭크의 상부 외부 표면 상에 폴리(메틸 메타크릴레이트)(PMMA) 코팅을 형성하였다. 액체 코팅 조성물은 23℃에서 204 cP의 점도를 가지며 Tel Act12 스핀 코팅기를 사용하여 20 초 동안 1000 rpm의 회전 속도로 도포하였고, 1750 rpm에서 55 초 동안 건조시켰다. 상판 블랭크의 중심 영역에서 PMMA 코팅의 두께는 약 2 미크론이었다.

코팅의 형성된 에지 비드의 위치 및 크기는 Bruker Insight 원자간력 프로파일링(Atomic Force Profiling)(AFP)을 사용하여 분석되었다. 도 6에 예시된 바와 같이, 에지 비드는 상판 블랭크의 외부 에지에 매우 가깝게 테이퍼진 에지 영역 내에 형성된다. 에지 비드는 상판의 중심 지점으로부터 약 148.15 mm 반경방향 거리에 그 정점(66)을 가지며, 이는 상판의 외부 에지로부터 1.785 mm에 대응한다.

에지 비드의 정점(66)이 상판 블랭크의 중심 영역에 있는 코팅의 평면보다 낮다는 것을 도 6에서 또한 명확하게 알 수 있다. 도 6에서, 중심 영역(67)에서 상판 블랭크의 외부 표면 아래에 정점의 거리는 -0.35 미크론이었다. 중심 영역에서 약 2 미크론의 코팅 두께의 두께를 추가하면, 에지 비드의 정점은 -2.35 미크론의 음의 높이(He)를 가졌다. 데이터 요약은 아래의 표 1에 또한 나타낸다.

비교예 2

습식 에칭된 측면 영역을 갖는 상판 블랭크의 스핀 코팅.

에지 영역에서 상판 블랭크의 습식 에칭은 통상적으로 분리 구역을 갖는 스핀 코팅된 상판을 제조하기 위해 수행된다.

출발 재료(에칭 전)로서 예 1과 동일한 웨이퍼(테이퍼진 에지를 도입하기 전)를 사용하였다. 습식 에칭은 웨이퍼의 중심을 향해 반경방향으로 웨이퍼의 외부 에지로부터 약 3 mm의 영역에 걸쳐 수행되었다. 웨이퍼를 에칭하여, 웨이퍼의 전체 3 mm 외부 원 영역에 걸쳐 웨이퍼의 두께 방향(y)(깊이(Td)로도 표시됨)으로 50 미크론의 웨이퍼 재료를 제거하였다.

예 1에도 사용된 바와 같은 MicroChem사의 액체 코팅 조성물 495 PMMA를 도포함으로써 상판 블랭크의 상부 외부 표면 상에 a) 약 2 미크론 및 b) 약 1 미크론의 두께를 갖는 폴리(메틸 메타크릴레이트)(PMMA) 코팅을 형성하도록 스핀 코팅 실험을 수행하였다.

형성된 층의 에지 비드는 Zygo NewView 3D 광학 표면 프로파일 분석기를 사용하여 분석되었다.

스핀 코팅 동안 형성된 에지 비드의 분석은, 습식 에칭에 의해 웨이퍼 높이의 감소가 야기되기 전에 에지 비드의 위치가 짧다는 것을 보여주었다.

표 1은, 웨이퍼 중심 영역의 코팅의 외부 표면의 평면으로부터 에지 비드의 정점까지의 수직 방향 거리로 표현된, 형성된 에지 비드의 높이(He); 및 코팅의 외부 표면의 레벨에서 에지 비드의 폭을 나타내는, 에지 비드의 폭(We)과 같은 측정 데이터의 요약을 포함한다.

비교예 2의 상판의 선도는 도 3b에 예시되어 있다. 에칭은 상판 블랭크(31)의 높이를 갑작스럽게 감소시켰으며, 감소의 평균 테이퍼 각도(33)는 45도 이상임을 알 수 있다. 스핀 코팅에 의해 도포된 코팅(32)은 웨이퍼의 에칭된 부분의 갑작스런 표면 강하 전에 정점(36)의 위치가 가까운 에지 비드(35)를 형성하였다. 에지 비드(35)의 정점(36)은 중심 영역 내에서 코팅(32)의 외부 표면 레벨(37)의 위에 있다.

비교예 3

본 발명에 따른 테이퍼진 에지 영역을 갖지 않는 상판 블랭크 상에서 에지 비드 형성을 시뮬레이션하기 위해, 에지 영역의 추가 수정 없이 예 1의 상업용 융합 실리카 웨이퍼를 사용하였다. 웨이퍼는 웨이퍼의 매우 짧은 반경방향 거리에 걸쳐 표준 원형 에지를 포함하였다.

웨이퍼는 다음과 같은 에지 프로파일을 갖는다: 50-85 미크론의 에지 영역의 길이(Tl); 25-48 미크론의 웨이퍼의 외부 에지에서의 깊이(Td), 및 약 45도 이상의 웨이퍼의 반경방향 x에 관한 원형 에지를 따른 각도.

웨이퍼는 비교예 2에서 수행된 바와 동일한 PMMA 코팅 및 중심 영역에서의 코팅 두께(약 1 미크론 및 약 2 미크론)로 스핀 코팅되었다.

웨이퍼 분석은, 스핀 코팅이 웨이퍼의 외부 영역에서 외부 에지에 약 2 mm 가까운 에지 비드를 형성했음을 보여주었다.

웨이퍼(41) 및 도포된 코팅(42)의 선도가 도 3c에 예시되어 있다. 원형 에지 영역 이전에 에지 비드(45)가 형성된 것을 볼 수 있으며, 에지 비드(45)의 정점(46)은 중심 영역 내의 코팅의 외부 표면의 평면(47)보다 훨씬 더 높았다.

데이터의 비교:

표 1은 형성된 에지 비드의 높이(He), 및 에지 비드의 폭(We)과 같은 예 1, 비교예 2 및 3의 측정 데이터의 요약을 포함한다. 높이(He)와 폭(We) 모두는 중심 영역의 코팅의 외부 표면 레벨을 시작 위치로 사용하여 측정되었다.

표 1에 요약된 테스트 데이터는, 웨이퍼의 에지 영역에서 약 2 mm의 영역에 걸쳐 평활하게 감소하는 테이퍼를 갖는 예 1의 상판만이 중심 영역 내의 코팅 레벨 아래의 정점을 갖는 에지 비드를 포함한다는 것을 보여준다.

웨이퍼의 3 mm 외부 링 영역에서 에칭을 받고 스핀 코팅된 웨이퍼는, 중심 영역의 코팅 평면 위의 정점 높이를 갖는 에지 비드를 포함하였다. 그러나, 스핀 코팅된 표준 웨이퍼의 에지 비드와 비교하여, 습식 에칭된 웨이퍼는 정점의 높이가 훨씬 낮았다. 비교예 C2 및 C3의 웨이퍼를 상판으로 사용하기 위해서는, 예를 들어 용해 또는 연마를 통해 에지 비드를 제거할 필요가 있는 반면, 예 1의 상판에 포함된 에지 비드는 용인될 수 있다. 그러나, 특정 예에서, 본 개시내용의 상판의 에지 비드도, 예를 들어 용매로 세정함으로써 제거될 수 있다.

Claims (14)

- 상판 블랭크 및 상기 상판 블랭크의 외부 표면 위에 놓인 코팅을 포함하는 상판으로서,

상기 상판 블랭크는 중심 영역 및 테이퍼진 에지 영역을 포함하고;

상기 테이퍼진 에지 영역은 상기 상판 블랭크의 반경방향에 대해 20도 이하의 평균 테이퍼 각도를 가지며;

상기 코팅은 상기 상판 블랭크의 상기 중심 영역 및 상기 테이퍼진 에지 영역의 적어도 일부 위에 놓이는, 상판. - 제1항에 있어서, 상기 코팅은 상기 테이퍼진 에지 영역 내에 에지 비드를 포함하고, 상기 에지 비드의 정점은 상기 상판의 상기 중심 영역에서 상기 코팅의 외부 표면의 평면 아래에 있을 수 있는, 상판.

- 제1항에 있어서, 표면적 비율 Sc:St는 적어도 15이고, Sc는 상기 중심 영역의 표면적이며 St는 상기 테이퍼진 에지 영역의 표면적인, 상판.

- 제1항에 있어서, 상기 상판 블랭크의 높이 방향에 대한 상기 상판 블랭크의 상기 중심 영역의 상기 외부 표면의 레벨로부터 상기 상판 블랭크의 외부 에지에서의 테이퍼의 깊이(Td)는 적어도 20 미크론이고, 400 미크론 이하인, 상판.

- 제1항에 있어서, 반경방향으로 상기 테이퍼진 에지 영역의 길이(Tl)는 적어도 1.0 mm인, 상판.

- 제1항에 있어서, 상기 상판 블랭크는 상기 중심 영역 내에서 적어도 100 미크론이고, 5000 미크론 이하의 평균 두께를 갖는, 상판.

- 제1항에 있어서, 상기 코팅은 상기 중심 영역 내에서 적어도 0.1 미크론이고, 10 미크론 이하의 평균 두께를 갖는, 상판.

- 제1항에 있어서, 상기 테이퍼진 에지 영역은 10도 이하의 테이퍼 각도를 갖는, 상판.

- 상판의 형성 방법으로서,

중심 영역 및 테이퍼진 에지 영역을 포함하는 상판 블랭크를 준비하는 단계로서, 상기 상판 블랭크의 반경방향에 대한 상기 테이퍼진 에지 영역의 테이퍼 각도는 20도 이하인, 단계; 및

상기 상판 블랭크의 외부 표면 상에 코팅을 도포하는 단계로서, 상기 코팅은 상기 중심 영역 전체 및 상기 테이퍼진 에지 영역의 적어도 일부 위에 놓이는, 단계를

포함하는, 방법. - 제9항에 있어서, 상기 코팅을 도포하는 단계는 스핀 코팅을 포함하는, 방법.

- 제10항에 있어서, 상기 스핀 코팅은 상기 테이퍼진 에지 영역 내에 에지 비드를 형성하는 것을 포함하는, 방법.

- 제11항에 있어서, 상기 에지 비드의 정점은 상기 상판의 상기 중심 영역에서 상기 코팅의 외부 표면의 평면 아래에 있는, 방법.

- 제11항에 있어서, 상기 에지 비드를 제거하는 단계를 더 포함하는, 방법.

- 물품의 제조 방법으로서,

기판 상에 경화 가능한 조성물의 층을 도포하는 단계;

상기 경화 가능한 조성물을 상판과 접촉시키는 단계로서, 상기 상판은 상판 블랭크 및 상기 상판 블랭크의 외부 표면 위에 놓인 코팅을 포함하고,

상기 상판 블랭크는 중심 영역 및 테이퍼진 에지 영역을 포함하고;

상기 테이퍼진 에지 영역은 상기 상판 블랭크의 길이방향에 대해 20도 이하의 테이퍼 각도를 가지며;

상기 코팅은 상기 상판 블랭크의 상기 중심 영역 전체 및 상기 테이퍼진 에지 영역의 적어도 일부 위에 놓이는, 단계;

상기 경화 가능한 조성물을 광 또는 열로 경화시켜 경화된 층을 형성하는 단계;

상기 경화된 층으로부터 상기 상판을 제거하는 단계; 및

상기 경화된 층으로 상기 기판을 처리하여 상기 물품을 제조하는 단계를 포함하는, 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US16/834,465 | 2020-03-30 | ||

| US16/834,465 US20210305082A1 (en) | 2020-03-30 | 2020-03-30 | Superstrate and method of making it |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20210122100A true KR20210122100A (ko) | 2021-10-08 |

Family

ID=77854686

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020210034972A KR20210122100A (ko) | 2020-03-30 | 2021-03-18 | 상판 및 그 제조 방법 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20210305082A1 (ko) |

| JP (1) | JP2021160352A (ko) |

| KR (1) | KR20210122100A (ko) |

| CN (1) | CN113471101A (ko) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11562924B2 (en) * | 2020-01-31 | 2023-01-24 | Canon Kabushiki Kaisha | Planarization apparatus, planarization process, and method of manufacturing an article |

| US11878935B1 (en) * | 2022-12-27 | 2024-01-23 | Canon Kabushiki Kaisha | Method of coating a superstrate |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20080160129A1 (en) * | 2006-05-11 | 2008-07-03 | Molecular Imprints, Inc. | Template Having a Varying Thickness to Facilitate Expelling a Gas Positioned Between a Substrate and the Template |

| JP6385131B2 (ja) * | 2014-05-13 | 2018-09-05 | 株式会社ディスコ | ウェーハの加工方法 |

| JP2017010962A (ja) * | 2015-06-16 | 2017-01-12 | 株式会社東芝 | デバイス基板およびデバイス基板の製造方法並びに半導体装置の製造方法 |

| US11137536B2 (en) * | 2018-07-26 | 2021-10-05 | Facebook Technologies, Llc | Bragg-like gratings on high refractive index material |

| KR20210026955A (ko) * | 2019-09-02 | 2021-03-10 | 삼성전자주식회사 | 반도체 소자 제조 장치, 반도체 소자 검사 장치 및 반도체 소자 제조 방법 |

-

2020

- 2020-03-30 US US16/834,465 patent/US20210305082A1/en active Pending

-

2021

- 2021-01-13 JP JP2021003721A patent/JP2021160352A/ja active Pending

- 2021-03-18 KR KR1020210034972A patent/KR20210122100A/ko active Search and Examination

- 2021-03-30 CN CN202110337576.7A patent/CN113471101A/zh active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| CN113471101A (zh) | 2021-10-01 |

| US20210305082A1 (en) | 2021-09-30 |

| TW202136013A (zh) | 2021-10-01 |

| JP2021160352A (ja) | 2021-10-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR20210122100A (ko) | 상판 및 그 제조 방법 | |

| KR102401043B1 (ko) | 극자외선 리소그래피 마스크 블랭크 제조 시스템 및 그를 위한 작동 방법 | |

| US8048775B2 (en) | Process of forming ultra thin wafers having an edge support ring | |

| JP6688221B2 (ja) | 紫外線リソグラフィ用ガラスセラミックス及びその製造方法 | |

| US10192741B2 (en) | Device substrate, method of manufacturing device substrate, and method of manufacturing semiconductor device | |

| TWI430362B (zh) | 用於挖槽倒角基材之方法 | |

| EP2339399B1 (en) | Photomask-forming glass substrate and making method | |

| WO2007141990A1 (ja) | ウェーハの製造方法 | |

| TWI817064B (zh) | 平坦化設備、平坦化方法及製造物品的方法 | |

| TWI834943B (zh) | 覆板及製造覆板之方法 | |

| WO2018079105A1 (ja) | ウェーハの製造方法およびウェーハ | |

| KR20040014423A (ko) | 엔드포인트 및 반도체 웨이퍼를 결정하는 방법 | |

| US20170040285A1 (en) | Wafer planarization method | |

| KR20220029413A (ko) | 성형 장치, 성형 방법, 및 템플릿 | |

| JP7029272B2 (ja) | エッジ領域のインプリントリソグラフィ | |

| KR20160007372A (ko) | 노광 마스크의 제조 방법 | |

| JP2009010071A (ja) | ウエハの研磨方法 | |

| KR20230082569A (ko) | 상판 및 그 사용 방법 | |

| US20230095286A1 (en) | Method of manufacturing a template | |

| WO2002009165A1 (fr) | Procede de polissage d'une plaquette | |

| JP7192409B2 (ja) | インプリントモールド用基板及びインプリントモールド、並びにそれらの製造方法 | |

| US11541577B2 (en) | Template apparatus and methods of using the same | |

| US11830824B2 (en) | Edge protection on semiconductor substrates | |

| US10663624B2 (en) | Method for creating a nanostructure in a transparent substrate | |

| WO2007145505A1 (en) | Method for manufacturing a device for supporting a substrate during the manufacture of semiconductor components, as well as such a device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination |