KR20180078359A - 발광 반도체 칩 - Google Patents

발광 반도체 칩 Download PDFInfo

- Publication number

- KR20180078359A KR20180078359A KR1020187018915A KR20187018915A KR20180078359A KR 20180078359 A KR20180078359 A KR 20180078359A KR 1020187018915 A KR1020187018915 A KR 1020187018915A KR 20187018915 A KR20187018915 A KR 20187018915A KR 20180078359 A KR20180078359 A KR 20180078359A

- Authority

- KR

- South Korea

- Prior art keywords

- quantum

- semiconductor chip

- layer

- semiconductor

- doping

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 162

- 230000005855 radiation Effects 0.000 claims abstract description 24

- 239000002019 doping agent Substances 0.000 claims description 22

- 238000000034 method Methods 0.000 claims description 18

- 239000000463 material Substances 0.000 claims description 15

- 239000000758 substrate Substances 0.000 claims description 7

- 239000013078 crystal Substances 0.000 claims description 6

- 238000000151 deposition Methods 0.000 description 12

- 230000004888 barrier function Effects 0.000 description 11

- 239000002800 charge carrier Substances 0.000 description 11

- 230000008021 deposition Effects 0.000 description 11

- 229910052738 indium Inorganic materials 0.000 description 10

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 9

- 238000002347 injection Methods 0.000 description 5

- 239000007924 injection Substances 0.000 description 5

- 238000005259 measurement Methods 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 239000000203 mixture Substances 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 238000009826 distribution Methods 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- 230000003595 spectral effect Effects 0.000 description 3

- RNFJDJUURJAICM-UHFFFAOYSA-N 2,2,4,4,6,6-hexaphenoxy-1,3,5-triaza-2$l^{5},4$l^{5},6$l^{5}-triphosphacyclohexa-1,3,5-triene Chemical compound N=1P(OC=2C=CC=CC=2)(OC=2C=CC=CC=2)=NP(OC=2C=CC=CC=2)(OC=2C=CC=CC=2)=NP=1(OC=1C=CC=CC=1)OC1=CC=CC=C1 RNFJDJUURJAICM-UHFFFAOYSA-N 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 230000001427 coherent effect Effects 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 239000000470 constituent Substances 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 239000003063 flame retardant Substances 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 2

- 229910052757 nitrogen Inorganic materials 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 238000013139 quantization Methods 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000012876 carrier material Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- -1 for example Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 229910001092 metal group alloy Inorganic materials 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 239000002096 quantum dot Substances 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 239000010948 rhodium Substances 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000002211 ultraviolet spectrum Methods 0.000 description 1

Images

Classifications

-

- H01L33/06—

-

- H01L33/04—

-

- H01L33/0093—

-

- H01L33/14—

-

- H01L33/24—

-

- H01L33/32—

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H01L33/22—

-

- H01L33/382—

Landscapes

- Led Devices (AREA)

Abstract

본 발명은 반도체 칩(1)과 관련이 있으며, 상기 반도체 칩은 반도체 층 시퀀스를 갖는 반도체 몸체(2)를 포함하고, 이 경우 방사선을 발생할 목적으로 제공되는 활성 영역(20)은 n-도전성 다층 구조물(21)과 p-도전성 반도체 층(22) 사이에 배치되어 있다. 상기 n-도전성 다층 구조물 내에는 적어도 하나의 도핑 팁(doping tip)(4)을 포함하는 도핑 프로파일 엘리먼트(doping profiled element)가 형성되어 있다.

Description

본 발명은 방사선을 발생할 목적으로 제공되는 반도체 칩에 관한 것이다.

본 특허 출원서는 독일 특허 출원서 제 10 2009 060 747.1호를 우선권으로 주장하며, 상기 우선권 서류의 공개 내용은 인용의 방식으로 본 출원서에 수용된다.

LED-반도체 칩들은 대개 방사선을 발생할 목적으로 제공되는, 다수의 양자 웰(quantum well)을 갖는 활성 영역을 포함한다.

활성 영역 내에 있는 InGaN-양자 웰들에서는, 방출되는 방사 전력이 전류 밀도가 증가함에 따라 선형으로 상승되지 않는다는 사실이 드러났다. 이에 대한 이유로는, 전하 캐리어들이 대개 양자 웰들 내부로 효율적으로 주입되지 않기 때문이다.

본 발명의 과제는 전하 캐리어들이 활성 영역 내부로 효율적으로 주입될 수 있는 반도체 칩을 제시하는 것이다.

상기 과제는 독립 청구항 1의 대상에 의해 해결된다. 추가의 실시 예들 및 개선 예들은 종속 청구항들의 대상이다.

본 발명에 따른 반도체 칩의 한 가지 실시 예에서, 반도체 칩은 반도체 층 시퀀스를 갖는 반도체 몸체를 포함하고, 이 경우 상기 반도체 층 시퀀스는 n-도전성 다층 구조물, p-도전성 반도체 층 및 방사선을 발생할 목적으로 제공되는 활성 영역을 포함한다. 상기 활성 영역은 n-도전성 다층 구조물과 p-도전성 반도체 층 사이에 배치되어 있다. 상기 n-도전성 다층 구조물 내에는 적어도 하나의 도핑 팁(doping tip)을 포함하는 도핑 프로파일 엘리먼트(doping profiled element)가 형성되어 있다.

도핑 프로파일 엘리먼트는 특히 수직 방향으로, 더 상세하게 말하자면 반도체 몸체의 반도체 층 시퀀스의 증착 방향을 따라 진행되는 방향으로의 도핑 프로파일을 의미한다. 다른 말로 표현하자면, 상기 도핑 프로파일 엘리먼트는 반도체 몸체의 반도체 층 시퀀스의 반도체 층들의 주 연장 평면에 대하여 수직으로 뻗는다.

본 출원서의 범주에서 도핑 팁이란, 상기 도핑 팁에 인접하는 적어도 하나의 영역에 비해 높은 도펀트 농도를 갖는 반도체 재료의 영역을 의미한다. 바람직하게 2개의 측에서 도핑 팁을 둘러싸는 반도체 재료는 바람직하게는 저 농도로 도핑 되거나, 도핑 되지 않거나 또는 내인성으로 형성된다.

고 도펀트 농도란 특히 적어도 2 * 1018 ㎝-3의 농도를 의미한다.

저 도펀트 농도란 특히 적어도 1 * 1016 ㎝-3 내지 최대 1 * 1018 ㎝-3의 농도를 의미한다.

특히, n-도전성 다층 구조물의 나머지 연장부에 비해, 고 농도로 도핑된 얇은 도핑 팁은 반도체 칩의 활성 영역 내부로의 개선된 전하 캐리어 주입을 야기한다는 사실이 드러났다. 고 농도 도핑으로 인해, n-도전성 다층 구조물이 도핑 팁 영역 내에서 비교적 높은 분로 전도성(shunt conductability), 다시 말하자면 가로 방향으로 높은 전도성을 가짐으로써, 결과적으로 전하 캐리어들은 가로 방향으로 매우 균일하게 활성 영역 내부로 주입될 수 있다. 상기 적어도 하나의 도핑 팁은 활성 영역의 후진 방향에서, 즉 역방향에서도 가로로 비교적 더 균일한 전류 전도를 야기한다. 이로 인해 반도체 칩들은 정전 방전(electrostatic dascharge, ESD)에 대하여 감소된 민감성을 보인다.

본 발명에 따른 반도체 칩의 한 가지 바람직한 실시 예에서, n-도전성 다층 구조물은 도핑 팁에 의해서 고 농도로 도핑된 적어도 하나의 영역 및 저 농도로 n- 도전성 도핑된 영역을 갖는다. 바람직하게 상기 적어도 하나의 도핑 팁 내의 도펀트 농도는 상기 n-도전성 다층 구조물의 저 농도로 n-도전성 도핑된 영역 내의 도펀트 농도보다 적어도 5배, 특히 바람직하게는 적어도 8배, 예를 들면 10배 높다.

이 경우, 저 농도로 n-도전성 도핑된 영역은 특히 도핑 팁에 인접할 수 있다.

바람직하게 도핑 팁 내의 도펀트 농도는 적어도 4 * 1018 ㎝- 3이다. 도펀트 농도가 높음으로써, 고 전도성이 달성될 수 있다.

더 나아가, 바람직하게는 도핑 팁 내의 도펀트 농도가 최대 1 * 1020 ㎝-3, 특히 바람직하게는 최대 3 * 1019 ㎝-3에 달한다.

그 이외에도, 바람직하게는 특히 인접하는, 저 농도로 n-도전성 도핑된 영역 내의 도펀트 농도가 최대 5 * 1017 ㎝-3, 특히 바람직하게는 최대 2 * 1017 ㎝-3에 달한다.

본 발명에 따른 반도체 칩의 한 가지 바람직한 실시 예에서, 상기 적어도 하나의 도핑 팁 내의 도펀트 농도는 적어도 4 * 1018 ㎝-3이고, 상기 저 농도로 n-도전성 도핑된 영역 내의 도펀트 농도는 최대 8 * 1017 ㎝-3이다.

도핑 팁의 수직 연장부는 바람직하게 1 ㎚(1 ㎚ 포함) 내지 30 ㎚(30 ㎚ 포함), 특히 바람직하게는 2 ㎚(2 ㎚ 포함) 내지 20 ㎚(20 ㎚ 포함)이다. 특히, 상기 도핑 팁의 상기 수직 연장부는 7 ㎚(7 ㎚ 포함) 내지 10 ㎚(10 ㎚ 포함)에 달할 수 있다.

n-도전성 다층 구조물은 반도체 칩 작동 중에 특히 활성 영역 내부로 전자들을 주입할 목적으로 사용된다. 이를 위해 상기 n-도전성 다층 구조물은 반드시 연속적으로 n-도전성으로 도핑될 필요는 없다. 오히려, 상기 n-도전성 다층 구조물은 하나 또는 다수의 층을 포함할 수도 있으며, 상기 하나 또는 다수의 층 내에서는 n-도전성 다층 구조물이 도핑 되지 않았거나 내연성으로 구현되어 있다.

그에 상응하게 p-도전성 반도체 층은 특히 활성 영역 안에 홀을 주입하기 위해 제공되었다. 상기 p-도전성 반도체 층은 다층으로 형성될 수도 있으며, 이 경우 개별 층들은 도핑 및/또는 결정 조성물에서 구별될 수 있다.

반도체 몸체는 바람직하게 화합물 반도체, 특히 질화물-화합물 반도체를 기본으로 한다.

본 발명과 관련해서 "질화물-화합물을 기본으로 한다"라는 표현은, 활성 에피택시-층 시퀀스 또는 상기 층 시퀀스 중 적어도 하나의 층이 질화물-Ⅲ/Ⅴ-화합물 반도체 재료, 바람직하게는 AlyGa1 -x- yInxN을 포함하는 것을 의미하며, 이 경우 0x1, 0y1 및 x+y1이다. 이때, 상기 반도체 재료는 반드시 전술한 일반식에 따라 수학적으로 정확한 조성을 가질 필요는 없다. 오히려, 상기 반도체 재료는 하나 또는 다수의 도펀트 그리고 AlyGa1 -x- yInxN-재료의 특징적이고 물리적인 세부 특성을 실제로 변경시키지 않는 추가의 구성 성분들을 포함할 수도 있다. 그러나 비록 결정 격자의 주요 성분들(Al, Ga, In, N)이 부분적으로 적은 량의 추가 물질들로 대체될 수 있을지라도, 간단함을 목적으로 상기 일반식은 상기 결정 격자의 주요 구성 성분만을 포함한다.

활성 영역은 바람직하게 다수의 양자 층을 포함하다. 상기 양자 층들은 바람직하게 배리어 층들 사이에 배치되어 있다. 이러한 경우에는 양자 층들 및 배리어 층들이 양자 구조물을 형성할 수 있다.

본 발명의 범주에서 양자 구조물이라는 표현은, 특히 전하 캐리어들이 구속("confinement")에 의해 자신들의 에너지 상태의 양자화를 경험할 수 있는 모든 구조물을 포함한다. 특히, 양자 구조물이라는 표현은 양자화 차원에 대한 진술을 포함하지는 않는다. 따라서, 상기 양자 구조물은 다른 무엇보다도 양자 웰들, 양자 선들 및 양자 점들 그리고 상기 구조물들의 각각의 조합을 포함한다.

본 발명에 따른 반도체 칩의 한 가지 바람직한 실시 예에서, n-도전성 다층 구조물은 양자 구조물을 포함한다. 상기 양자 구조물은 다수의 양자 층을 포함할 수 있다.

더 나아가, 양자 구조물이라는 용어는 특히 다중 양자 웰 구조물(multi quantum well, MQW)로서의 형성뿐만 아니라 초격자(superlattice)로서의 형성으로도 이해할 수 있다. 다중 양자 웰 구조물과 달리, 초격자의 경우에 이웃한 양자 층들의 간격들이 작음으로써, 이웃한 양자 층들의 전자 상태들은 양자 역학적으로 상호 커플링되어 공통의 전자 상태들을 형성한다.

예를 들어 초격자의 양자 층들 사이에는 5 ㎚ 또는 5 ㎚ 미만의, 예를 들어 2 ㎚의 두께를 갖는 배리어 층들이 형성될 수 있다.

본 발명에 따른 반도체 칩의 한 가지 바람직한 실시 예에서, n-도전성 다층 구조물의 양자 층의 밴드 갭 크기는 적어도 활성 영역의 양자 층의 밴드 갭 크기와 동일하다. 특히 바람직하게는 양자 층의 밴드 갭이 활성 영역의 양자 층의 밴드 갭보다 크다. 예를 들어 질화물-화합물 반도체 재료를 기본으로 하는 반도체 칩의 경우에 n-도전성 다층 구조물의 양자 층들은 활성 영역의 양자 층들보다 더 작은 인듐 함량 x를 가질 수 있다.

n-도전성 다층 구조물의 양자 층들은 활성 영역의 양자 층들과 달리 방사선을 발생할 목적으로 제공되지 않고, 전자들을 활성 영역 내부로 효과적으로 주입할 목적으로 사용되며, 상기 활성 영역 내에서는 상기 n-도전성 다층 구조물이 방사선을 방출하면서 홀들과 재결합될 수 있다.

활성 영역의 양자 층들은 바람직하게 내연성으로 구현되거나 또는 도핑 되지 않은 상태로 구현되어 있다.

본 발명에 따른 반도체 칩의 한 가지 추가 실시 예에서, 도핑 팁은 활성 영역에 가장 가까운 n-도전성 양자 구조물의 양자 층과 상기 n-도전성 양자 구조물에 가장 가까운 활성 영역의 양자 층 사이에 배치되어 있다. 따라서, 활성 영역 부근에서는 가로 방향으로의 우수한 전류 분포가 보장된다.

그 이외에도 바람직하게 활성 영역으로부터, 특히 n-도전성 다층 구조물에 가장 가까운 활성 영역의 양자 층으로부터 도핑 팁의 간격은 1 ㎚(1 ㎚ 포함) 내지 30 ㎚, 특히 바람직하게는 2 ㎚(2 ㎚ 포함) 내지 20 ㎚(20 ㎚ 포함), 특히 7 ㎚(7 ㎚ 포함) 내지 10 ㎚(10 ㎚ 포함)에 달한다.

활성 영역 부근에 있는 고 농도로 도핑된 이러한 도핑 팁에 의해서, 활성 영역 내부로의 전하 캐리어들의 주입이 특히 효율적으로 그리고 특히 가로 방향으로 매우 균일하게 이루어질 수 있다. 높은 분로 전도성으로 인해, 상기 적어도 하나의 도핑 팁은 역방향에서도 가능한 많은 전하 캐리어 경로들의 개선된 이용을 야기하며, 상기와 같은 개선된 다수의 경로 이용은 반도체 몸체의 n-도전성 영역 내에서 도핑 팁을 포함하지 않는 반도체 칩에 비해 ESD-손상 위험을 감소시킨다.

상기 적어도 하나의 도핑 팁은 바람직하게, 도핑 프로파일 엘리먼트가 도펀트 농도가 낮은 곳에서 도펀트 농도가 높은 곳으로 그리고 그 반대로도 변환되는 예리한 천이부들을 포함하도록 형성되어 있다. 반도체 칩 제조시, 상기와 같은 도핑 팁 형성은 낮은 성장 속도에 의해, 예를 들면 20 ㎚/h 내지 500 ㎚/h의 성장 속도에 의해 달성될 수 있다. 바람직하게 증착은 에피택셜 방식으로, 예를 들면 MOCVD에 의해 이루어진다.

본 발명에 따른 반도체 칩의 한 가지 바람직한 개선 예에서, n-도전성 다층 구조물의 결정 구조는 V자형 피트들을 갖는다. 상기와 같은 형태의 피트들 ― 이러한 피트들은 반도체 층들의 증착 시 특히 전위 라인들을 따라서 형성될 수 있음 ― 은 "V-피트"로도 언급된다. 상기와 같은 V자형 피트들은 특히 반도체 재료의 비교적 낮은 증착 온도, 예를 들어 950℃보다 낮은 증착 온도에서 형성될 수 있다. 상기 V자형 피트들은 반도체 칩의 향상된 역방향 특성을 야기할 수 있다.

본 발명에 따른 반도체 칩의 한 가지 추가의 바람직한 실시 예에서, 도핑 프로파일 엘리먼트는 적어도 하나의 추가 도핑 팁을 포함한다. 특히, 상기 도핑 팁과 추가의 도핑 팁 사이에는 n-도전성 다층 구조물의 적어도 하나의 양자 층이 배치될 수 있다. 다른 말로 표현하자면, 도핑 프로파일 엘리먼트는 상기 n-도전성 양자 구조물의 양자 층들의 일부분이 높은 농도로 n-도핑 되고, 반면에 전술한 양자 층들의 일부분에 비해 상기 양자 층들의 나머지 부분이 낮은 농도로 n-도핑 되도록 형성될 수 있다.

도핑 프로파일 엘리먼트는 또한 2개 이상의 도핑 팁, 특히 1개(1개 포함) 내지 5개(5개 포함)의 도핑 팁, 바람직하게는 1개(1개 포함) 내지 3개(3개 포함)의 도핑 팁을 포함할 수도 있다.

본 발명에 따른 반도체 칩의 한 가지 바람직한 실시 예에서, 반도체 몸체의 반도체 층 시퀀스를 위한 성장 기판은 완전히 또는 적어도 부분적으로 분리되어 있다. 상기와 같은 형태의 반도체 칩은 박막-반도체 칩으로도 언급된다.

더 나아가, 본 발명의 범주에서 박막-반도체 칩, 예를 들어 박막-발광 다이오드-칩은 하기의 특징들 중 적어도 한 개의 특징을 특징으로 할 수 있다:

활성 영역을 갖는 반도체 층 시퀀스를 포함하는 반도체 몸체의, 캐리어 소자 쪽을 향하는 제 1 주 표면에, 특히 에피택시-층 시퀀스에 미러 층이 제공되거나 또는, 예를 들어 반도체 층 시퀀스 내에 브래그 미러로서 집적되는 방식으로 형성됨, 이 경우 반도체 층 시퀀스 내에서 발생하는 방사선의 적어도 일부분은 상기 반도체 층 시퀀스 내부로 역반사(reflecting back) 됨;

상기 반도체 층 시퀀스가 20 ㎛ 또는 그 미만의 범위, 특히 10 ㎛ 범위의 두께를 가짐; 그리고/또는

상기 반도체 층 시퀀스가 혼합 구조물을 포함하는 적어도 하나의 표면을 갖는 적어도 하나의 반도체 층을 포함하고, 상기 혼합 구조물은 이상적인 경우 반도체 층 시퀀스 내에서 거의 에르고딕 광 분포를 야기하며, 다시 말하자면 상기 혼합 구조물은 가능한 에르고딕 확률론적인 분산 특성을 가짐.

박막-발광 다이오드 칩의 기본 원리는 예를 들어 I. Schnitzer 외, Appl. Phys. Lett. 63(16), 1993년 10월 18일, p. 2174-2176에 기술되어 있으며, 본 발명과 관련해서 상기 문서의 공개 내용은 인용의 방식으로 본 출원서에 수용된다.

추가의 특징들, 실시 예들 및 합목적성은 도면들과 관련하여 기술된 실시 예들의 하기 설명으로부터 드러난다.

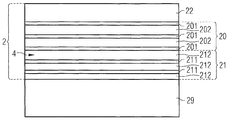

도 1a는 반도체 층 시퀀스를 갖는 반도체 몸체의 실시 예를 도시한 개략적인 단면도이고,

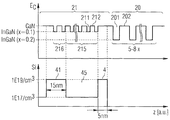

도 1b는 각각 제 2 실시 예에 따른 반도체 몸체의 커트 아우트에 대한 증착 방향(z)을 따라서 전도대 에지 콘투어(EC) 및 도핑 프로파일 엘리먼트를 도시한 개략도이며,

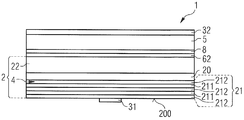

도 2는 반도체 칩의 제 1 실시 예를 도시한 개략적인 단면도이며,

도 3은 반도체 칩의 제 2 실시 예를 도시한 개략적인 단면도이고,

도 4는 역방향으로 인가되는 전압(U)의 함수로서 전류(I)의 측정 결과를 도시한 그래프이다.

도 1b는 각각 제 2 실시 예에 따른 반도체 몸체의 커트 아우트에 대한 증착 방향(z)을 따라서 전도대 에지 콘투어(EC) 및 도핑 프로파일 엘리먼트를 도시한 개략도이며,

도 2는 반도체 칩의 제 1 실시 예를 도시한 개략적인 단면도이며,

도 3은 반도체 칩의 제 2 실시 예를 도시한 개략적인 단면도이고,

도 4는 역방향으로 인가되는 전압(U)의 함수로서 전류(I)의 측정 결과를 도시한 그래프이다.

도면들에서 동일한, 동일한 형태의 또는 동일한 작용을 하는 소자들에는 동일한 도면 부호가 제공되었다.

도면들은 각각 개략도로 도시되어 있기 때문에 절대적으로 정확한 척도로 도시된 것으로 간주될 수 없다. 오히려, 명확한 도시를 목적으로 비교적 작은 소자들 및 특히 층 두께는 과도하게 크게 도시되어 있을 수 있다.

반도체 칩의 반도체 몸체에 대한 제 1 실시 예는 도 1a에서 단면도로 개략적으로 도시되어 있다. 상기 반도체 몸체(2)는 반도체 층 시퀀스를 포함하고, 상기 반도체 층 시퀀스는 반도체 몸체를 형성한다. 반도체 층 시퀀스는 방사선을 발생할 목적으로 제공되는 활성 영역(20)을 포함하고, 상기 활성 영역은 n-도전성 다층 구조물(21)과 p-도전성 반도체 층(22) 사이에 배치되어 있다. 반도체 몸체의 반도체 층 시퀀스는 바람직하게 에피택셜 방식으로, 특히 MBE 또는 MOCVD에 의해서 성장 기판(29) 상에 증착되어 있다. 질화물-화합물 반도체를 기본으로 하는 반도체 몸체의 경우, 성장 기판으로는 예를 들어 사파이어, 탄화 규소(silicon carbide), 규소 또는 질화 갈륨(gallium nitride)이 적합하다. n-도전성 다층 구조물과 성장 기판 사이에는 버퍼 층이 형성될 수 있는데, 상기 버퍼 층은 특히 결정 품질을 상승시킬 목적으로 제공될 수 있다(도면에는 명시적으로 도시되지 않음).

활성 영역(20)은 양자 구조물을 포함하며, 상기 양자 구조물은 다수의 양자 층(201) 및 상기 양자 층들 사이에 배치된 다수의 배리어 층(202)에 의해서 형성되었다. 활성 영역은 본 발명에서는 단지 예시적으로 3개의 양자 층을 갖는 양자 구조물을 포함한다. 그러나 전술한 양자 층의 개수와는 달리, 다른 개수의 양자 층도 제공될 수 있는데, 예를 들어 단 1개 또는 2개의 양자 층 또는 3개 이상, 예를 들면 20개까지의 양자 층, 예를 들어 5개 내지 8개의 양자 층이 제공될 수도 있다. p-도전성 반도체 층(22) 또한 다층으로 형성될 수 있으며, 이 경우 개별 층들은 특히 재료 조성물에 의해 그리고/또는 상기 층들의 도핑에 의해서 서로 구별될 수 있다.

n-도전성 다층 구조물(21)은 배리어 층들(212) 사이에 배치된 다수의 양자 층(211)을 갖는 양자 구조물을 포함한다.

수직 방향으로 있는, 더 정확히 말하자면 반도체 몸체(2)의 주 연장 평면에 대해 수직 방향으로 있는 도핑 팁(4) 위치는 화살표를 이용하여 개략적으로 도시되어 있다. 상기 도핑 팁은 n-도전성 다층 구조물(21) 내에, 특히 활성 영역에 가장 가까운 n-도전성 다층 구조물의 양자 층(211)과 상기 n-도전성 다층 구조물에 가장 가까운 활성 영역(20)의 양자 층(201) 사이에 배치되어 있다. 도핑 팁(4)에 인접하는 n-도전성 다층 구조물의 한 영역 내에서는, 양자 층들(211) 및 상기 양자 층들에 인접하는 배리어 층들이 저 농도로 도핑 되었다.

도핑 팁(4)에 의해서는 활성 영역(20) 내부로의 효율적인 전자 주입이 이루어질 수 있다. 도핑 팁은 후진 방향에서 마찬가지로 향상된 전류 확산을 야기하고, 상기와 같은 향상된 전류 확산은 반도체 층 시퀀스에 의해 형성된 반도체 칩의 ESD-손상 위험을 감소시킨다. 다시 말해, 감소된 ESD-민감성이 이미 반도체 층 시퀀스의 증착에 의해 달성됨으로써, 후속하는 반도체 칩 제조 단계에서 손상 위험이 감소된다.

도 1b에는 반도체 칩용 반도체 몸체의 제 2 실시 예에 대한 z축-방향 함수로서 전도대 에지 콘투어(EC) 및 규소-도핑 프로파일 엘리먼트의 개략적인 파형도가 도시되어 있다. 상기 z축-방향은 반도체 몸체(2)의 반도체 층들의 증착 방향에 상응하고, 반도체 몸체(2)의 반도체 층들의 주 연장 평면에 수직으로 진행된다.

상기 제 2 실시 예는 대체로 도 1a와 관련해서 기술된 반도체 몸체의 제 1 실시 예와 일치한다. 제 1 실시 예와는 달리, 본 실시 예에는 추가의 도핑 팁(41)이 형성되어 있다.

상기 추가의 도핑 팁(41)은 n-도전성 다층 구조물(21)의 고 농도로 도핑된 양자 구조물의 부분 영역을 형성한다. 상기 추가의 도핑 팁(41)과 도핑 팁(4) 사이에는 양자 구조물의 저 농도로 n-도전성 도핑된 영역(45)이 형성되어 있다.

반도체 몸체(2), 특히 활성 영역(20)은 본 실시 예에서 질화물-화합물 반도체 재료를 기본으로 한다.

활성 영역(20)은 다수의 양자 층(201)을 포함한다. 본 실시 예에서 활성 영역은 청색 스펙트럼 범위의 방사선을 발생하기 위해 제공되었다. 이를 위해 양자 층들은 각각 x = 0.2의 인듐 함량을 갖는다. 그러나 활성 영역은 다른 스펙트럼 범위의 방사선을 방출하기 위해서도 형성될 수 있다. 인듐 함량이 높으면 높을수록, 활성 영역 내에서 발생할 수 있는 광자들의 에너지 및 그와 더불어 밴드 갭은 더욱더 작아진다. 더 상세하게 말하자면, 인듐 함량은 넓은 범위 안에서 변동될 수 있다. 예를 들어, x = 0.10의 인듐 함량을 갖는 양자 층들은 작동 중에 자외선 스펙트럼 범위의 방사선을 방출하고, 그리고 x = 0.40의 인듐 함량을 갖는 양자 층들은 녹색 스펙트럼 범위의 방사선을 방출한다. 양자 층들 사이에는 GaN-배리어 층들(202)이 배치되어 있다.

본 실시 예에서 n-도전성 다층 구조물(21)의 도핑 프로파일 엘리먼트는 규소-도핑에 의해 구현되었다. 그러나 다른 도펀트도 사용될 수 있다. 도핑 프로파일 엘리먼트는 도핑 팁(4)을 포함한다. 상기 도핑 팁의 폭은 본 실시 예에서 약 5㎚에 달한다. 도핑 팁(4)의 영역에서는 도핑 농도가 1 * 1019 ㎝-3인 반면에, 상기 도핑 팁(4)에 인접하는 저 농도로 n-도전성 도핑된 영역(45)에서는 도핑 농도가 1 * 1017 ㎝-3이다. 더 나아가, 도핑 프로파일 엘리먼트는 15 ㎚의 폭을 갖는 추가의 도핑 팁(41)을 포함하는데, 상기 도핑 프로파일 엘리먼트에서 n-도전성 다층 구조물은 1 * 1019 ㎝-3의 도핑 농도로 n-도전성으로 도핑 되었다.

상기 도핑 팁들에 의해서는 가로 방향으로 특히 균일한 전하 캐리어 주입이 달성될 수 있다. 다시 말하자면, 특히 활성 영역의 양자 층(201) 바로 아래에서 효율적인 전류 확산이 이루어진다.

n-도전성 다층 구조물은 도 1a와 관련하여 기술된 바와 같이 다수의 양자 층(211)을 갖는 양자 구조물을 포함하고, 상기 다수의 양자 층들은 각각 배리어 층들(212) 사이에 배치되어 있다. 도핑 프로파일 엘리먼트에 의해서는, 저 농도로 도핑된 양자 구조물의 부분 영역(215) 및 고 농도로 도핑된 양자 구조물의 부분 영역(216)이 생성된다. 상기 부분 영역들에서는 각각 양자 층들 및/또는 배리어 층들이 도핑될 수 있다. 바람직하게 상기 적어도 하나의 도핑 팁의 영역에서는 적어도 양자 층들 및 배리어 층들이 고 농도로 도핑되는 방식으로 구현되었다.

다시 말하자면, n-도전성 다층 구조물(21)은 저 농도로 도핑된 양자 구조물의 부분 영역뿐만 아니라 고 농도로 도핑된 양자 구조물의 부분 영역도 포함한다. 저 농도로 도핑된 양자 층들의 부분 영역(215)은 이 경우 도핑 팁들(4, 41) 사이에서 연장되어 반도체 칩의 작동 중에 전자 저장기(reservoir)를 형성한다. 저 농도로 도핑된 양자 구조물의 부분 영역에서는 양자 층들(211) 및 배리어 층들(212)이 저 농도로 도핑되어 있다. 도핑 팁(4)에 의해서는, n-도전성 다층 구조물(21)로부터 활성 영역(20)의 양자 층들 안으로의 매우 효율적이고 그리고 가로 방향으로 균일한 전하 캐리어 주입이 야기된다.

n-도전성 다층 구조물(21)의 양자 층들은 본 실시 예에서 예시적으로 x = 0.1의 인듐 함량을 갖는다. 그러나 인듐 함량은 전술한 수치와는 다르게도 선택될 수 있다. 바람직하게 인듐 함량 크기가 최대한 활성 영역 내에 있는 양자 층들의 인듐 함량과 동일하게 선택됨으로써, 결과적으로 n-도전성 다층 구조물(21)의 양자 층들의 밴드 갭은 활성 영역(20) 내에 있는 양자 층들의 밴드 갭보다 크거나 또는 상기 활성 영역 내에 있는 양자 층들의 밴드 갭에 상응한다.

n-도전성 다층 구조물의 양자 구조물은 특히 양자 웰 구조물로서 또는 예를 들어 5 ㎚ 미만의, 예를 들어 약 2 ㎚의 두께를 갖는 배리어 층들을 갖는 초격자로서 구현될 수 있다.

그럼으로써, 전하 캐리어들을 활성 영역 내부로 효율적으로 주입하는 공정이 간소화된다.

물론, 활성 영역(20) 및 n-도전성 다층 구조물(21)의 재료 조성물들 그리고 도핑 프로파일 엘리먼트는 도시된 실시 예와는 상이할 수도 있다.

바람직하게 적어도 하나의 도핑 팁(4) 내의 도핑 농도는 적어도 4 *1018 ㎝-3에 달한다. 더 나아가, 바람직하게 상기 도핑 팁 내의 도핑 농도는 최대 1 * 1020 ㎝-3, 특히 바람직하게는 최대 3 * 1019 ㎝-3이다.

저 농도로 n-도전성 도핑된 영역(45) 내의 도핑 농도는 바람직하게 최대 5 * 1017 ㎝-3, 특히 바람직하게는 최대 2 * 1017 ㎝-3이다.

상기 적어도 하나의 도핑 팁 내의 도핑 농도는 바람직하게 n-도전성 다층 구조물의 저 농도로 n-도전성 도핑된 영역 내의 도핑 농도보다 적어도 5배, 특히 바람직하게는 적어도 8배 높다.

도핑 팁(4) 및/또는 추가의 도핑 팁(41)의 두께, 즉 수직 연장부는 바람직하게 1 ㎚(1 ㎚ 포함) 내지 30 ㎚(30 ㎚ 포함), 특히 바람직하게는 2 ㎚(2 ㎚포함) 내지 20 ㎚(20 ㎚ 포함), 가장 바람직하게는 7 ㎚(7 ㎚ 포함) 내지 10 ㎚(10 ㎚)이다.

도핑 팁(4)은 활성 영역(20)으로부터 바람직하게 작은 간격, 특히 바람직하게는 최대 30 ㎚의 간격을 갖는데, 특히 1 ㎚(1 ㎚ 포함) 내지 30 ㎚(30 ㎚ 포함), 바람직하게는 2 ㎚(2 ㎚포함) 내지 20 ㎚(20 ㎚ 포함), 가장 바람직하게는 7 ㎚(7 ㎚ 포함) 내지 10 ㎚(10 ㎚)의 간격을 갖는다.

더 나아가, 도시된 실시 예들과는 달리 2개 이상의 도핑 팁도 제공될 수 있는데, 예를 들어 1개(1개 포함) 내지 5개(5개 포함)의 도핑 팁이 제공될 수 있다.

또한, n-도전성으로 도핑된 다층 구조물(21)은 도시된 실시 예들과는 달리 도핑 되지 않았거나 또는 내연성으로 구현된 층들 또는 부분 층들을 포함할 수도 있다. 이러한 경우, 도핑 되지 않았거나 내연성으로 구현된 층들이 바람직하게는 매우 얇음으로써, n-도전성 다층 구조물(21)은 증착 방향으로 충분히 높은 전자 전도성을 갖는다.

도핑 팁들(4, 41)의 영역 내에서 가능한 직사각형의 도핑 프로파일 엘리먼트 콘투어를 제조하기 위해, 증착은 바람직하게 낮은 성장 속도로, 예를 들어 20 ㎚/h(20 ㎚/h 포함) 내지 500 ㎚/h(500 ㎚/h 포함)의 성장 속도로 이루어진다.

그 이외에도, 바람직하게 n-도전성 다층 구조물의 결정 구조는 V자형 피트들을 가지며, 상기 V자형 피트들은 특히 낮은 증착 온도에서, 예를 들면 950℃보다 낮은 증착 온도에서 전위들을 따라서 증대되는 방식으로 형성된다. 상기 V자형 피트들은 전압이 역방향으로 인가될 때 반도체 칩의 향상된 특성을 야기할 수 있다.

반도체 칩(1)의 제 1 실시 예는 도 2에 도시되어 있으며, 이 경우 반도체 몸체(2)는 도 1a와 관련하여 기술된 바와 같이 표본적으로 구현되었다.

이 경우 반도체 칩(1)은 박막-LED-반도체 칩으로서 구현되었으며, 상기 박막-LED-반도체 칩에서는 반도체 몸체(2)의 반도체 층 시퀀스를 위한 성장 기판(29)(도 1a)이 분리되어 있다. 활성 영역(20)은 작동 중에 인코히어런트(incoherent) 방사선을 발생할 목적으로 제공되었다.

반도체 몸체(2)는 캐리어(5) 상에 배치되어 있다. 상기 캐리어(5)가 특히 반도체 몸체를 기계적으로 안정화할 목적으로 사용됨으로써, 결과적으로 방사선 발생을 위해서는 성장 기판이 필요하지 않다.

캐리어 재료로는 예를 들어 반도체 재료(예컨대, 규소, 갈륨 비소 또는 게르마늄) 또는 세라믹(예컨대, 질화 알루미늄)이 적합하다.

캐리어(5)와 반도체 몸체는 연결층(8)에 의해 기계적으로 견고하게 그리고 더 나아가 도전성으로 접속되어 있다.

예를 들어 연결 층으로는 납땜 또는 도전성 접착제가 적합하다.

캐리어(5)와 반도체 몸체(2) 사이에는 미러 층(62)이 형성되어 있다. 미러 층에 의해서는, 반도체 바디(2)의 작동 중에 활성 영역(20)에서 발생되어 캐리어(5) 방향으로 방사되는 방사선이 방사선 출력 면(200) 방향으로 반사되어 반도체 칩으로부터 배출될 수 있다.

캐리어(5)로부터 떨어져서 마주하는 반도체 몸체(2)의 측에서 상기 반도체 몸체는 제 1 콘택(31)을 갖는다. 반도체 몸체의 마주 놓인 측에는, 즉 반도체 몸체(2)로부터 떨어져서 마주하는 캐리어(5)의 측에는 제 2 콘택(32)이 형성되어 있다.

상기 제 1 콘택 및/또는 제 2 콘택은 바람직하게 금속(예컨대, 금, 은, 백금, 알루미늄, 니켈, 크롬 또는 구리) 또는 상기 언급한 재료들 중 적어도 하나의 재료와의 합금을 포함한다.

상기 제 1 콘택(31) 및 제 2 콘택(32)에 의해서는, 반도체 칩(1)의 작동 중에 전하 캐리어들이 상이한 측들로부터 활성 영역(20) 내부로 주입될 수 있고 그리고 상기 활성 영역에서 방사선을 방출하면서 재결합할 수 있다.

제 1 콘택(31)을 통해서 주입된 전자들은 n-도전성 다층 구조물(21) 내 적어도 하나의 도핑 팁(4)의 영역에서 가로 방향으로 효율적으로 분포되어 활성 영역(20)의 양자 층들(201) 내로 주입된다.

미러 층(62)은 바람직하게 금속성으로 구현되어 있으며, 더 나아가 바람직하게는 활성 영역에서 발생되는 방사선에 대하여 높은 반사성을 갖는다. 예를 들어 미러 층에는 금속(예컨대, 알루미늄, 은, 금, 팔라듐 또는 로듐) 또는 상기 언급한 금속들 중 적어도 하나의 금속과의 금속 합금이 적합하다.

반도체 칩(1)의 제 2 실시 예는 도 3에서 단면도로 개략적으로 도시되어 있다. 반도체 몸체(2)는 이 경우 재차 도 1a와 관련하여 기술된 바와 같이 구현되었다. 도 2와 관련하여 기술된 제 1 실시 예에 따른 반도체 칩과 달리, 반도체 몸체(2)가 리세스(24)를 가지며, 상기 리세스는 캐리어(5) 쪽을 향하는 측으로부터 p-도전성 반도체 층(22) 및 활성 영역(20)을 통과하여 n-도전성 다층 구조물(21) 내부로 연장된다. 이 경우, 상기 리세스는 n-도전성 다층 구조물의 양자 층들(211)을 관통한다. 리세스의 측면들은, 활성 영역(20)의 전기적 단락으로부터 반도체 몸체(2)를 보호하는 절연층(27)에 의해 덮여 있다.

리세스(24) 내부에는 콘택 층(65)이 형성되어 있으며, 상기 콘택 층은 p-도전성 반도체 층(22)으로부터 떨어져서 마주보는 측으로부터 활성 영역을 전기적으로 콘택팅할 목적으로 사용된다.

캐리어(5)는 제 1 접속 면(51) 및 제 2 접속 면(52)을 포함하고, 이 경우 상기 제 1 접속 면(51)은 콘택 층(65)을 통해서 n-도전성 다층 구조물(21)에 도전 접속되어 있고, 제 2 접속 면(52)은 미러 층(62)을 통해서 p-도전성 반도체 층(22)에 도전 접속되어 있다. 제 1 접속 면(51) 및 제 2 접속 면(52)은 캐리어(5)의 동일한 측에 배치되어 있다.

더 자세히 말하자면, 리세스(24)에 의해서는 캐리어(5)로부터 떨어져서 마주보는 활성 영역(20)의 측에 배치된 n-도전성 다층 구조물(21)이 전기적으로 콘택팅될 수 있음으로써, 결과적으로 방사선 출력 면(200)은 외부 전기 콘택 없이 형성될 수 있다. 그럼으로써, 방사선을 투과시키지 않는 콘택에 의한 방사선 출력 면의 셰이딩(shading)이 피해진다.

캐리어(5)는 관통구들(55)을 포함하고, 상기 관통구들은 반도체 몸체(2) 쪽을 향하는 상기 캐리어의 제 1 주 표면(501)으로부터 상기 제 1 주 표면에 마주 놓인 제 2 주 표면(502) 끝까지 연장된다. 상기 관통구들을 통해서, 제 1 접속 면(51)이 제 1 콘택(31)에 도전 접속되고, 제 2 접속 면(52)이 제 2 콘택(32)에 도전 접속됨으로써, 결과적으로 반도체 칩(1)은 방사선 출력 면(200)으로부터 떨어져서 마주하는 반도체 칩의 하부면으로부터 외부에서 전기적으로 콘택팅될 수 있다.

더 나아가 반도체 바디(2)는 방사선 출력 면(200)의 측에 패터닝(7)을 갖는다. 상기 패터닝은 반도체 칩 내부에서, 활성 영역에서 발생되는 방사선의 전반사를 감소시킴으로써, 아웃 커플링 효율(outcoupling efficiency)을 상승시킬 목적으로 사용된다. 물론, 상기와 같은 패터닝은 도 2와 관련하여 기술된 반도체 칩의 제 1 실시 예의 경우에도 제공될 수 있다.

도 4에는 활성 영역(20)의 후진 방향, 즉 역방향으로의 전압 함수로서 역방향 전류(I)의 특성이 도시되어 있다. 이 경우, 곡선(99)은 반도체 층 시퀀스에 대한 측정 결과들을 보여주며, 상기 반도체 층 시퀀스로부터는 후속하는 처리 공정에서 반도체 칩의 반도체 몸체들이 유래한다. 반도체 층 시퀀스는 이 경우 도 1b와 관련하여 기술된 실시 예와 같이 구현되었다.

도 1b와 비교해서, 곡선(98)은 도핑 팁들을 갖지 않는 종래의 n-도전성 영역이 사용되는 반도체 층 시퀀스에 대한 측정 결과들을 보여준다.

화살표 97은, n-도전성 다층 구조물(21)의 기술된 구조에 의해 얻어질 수 있으며, 그리고 제일 먼저 전류 프로파일이 작은 전압에 있어서는 비교적 서서히 상승되고, 매우 높은 전압 값에서 비로소 가파른 전류 상승을 보인다는 내용을 지시한다. 다시 말하자면, 측정 곡선은 훨씬 더 심하게 뚜렷하게 꺽인 모양의 프로파일을 보여준다.

실시 예들에 대한 설명은 LED-반도체 칩의 설명을 참고로 하여 단지 예시적으로만 이루어진다. 그러나 n-도전성 다층 구조물(21) 및 적어도 하나의 도핑 팁(4)을 갖는 도핑 프로파일 엘리먼트의 기술된 형상은 코히어런트(coherent) 또는 적어도 부분 코히어런트 방사선을 방출하는 소자에도 사용될 수 있으며, 예를 들어 표면 방출 또는 단면 방출 반도체 레이저 칩 또는 RCLED(resonant cavity light emitting diode)에도 사용될 수 있다.

본 발명은 실시 예들을 참조하는 상세한 설명으로 인해 상기 실시 예들에만 한정되지 않는다. 오히려 본 발명은 각각의 새로운 특징 그리고 상기 특징들의 각각의 조합을 포함하며, 상기 특징 또는 특징 조합 자체가 특허청구범위 또는 실시 예들에 명시적으로 기재되어 있지 않더라도, 특히 상기 각각의 특징 조합은 특허청구범위에 포함된 것으로 간주한다.

Claims (18)

- 반도체 칩(1)으로서,

상기 반도체 칩은 반도체 층 시퀀스를 갖는 반도체 몸체(2)를 포함하고,

상기 반도체 층 시퀀스는 n-도전성 다층 구조물(21), p-도전성 반도체 층(22) 및 방사선을 발생할 목적으로 제공되는 활성 영역(20)을 포함하고, 상기 활성 영역은 상기 n-도전성 다층 구조물과 p-도전성 반도체 층 사이에 배치되어 있으며,

상기 반도체 몸체는 리세스(24)를 가지며, 상기 리세스는 상기 p-도전성 반도체 층 및 활성 영역을 통과하여 상기 n-도전성 다층 구조물 내부로 연장되고,

상기 n-도전성 다층 구조물 내에는 적어도 하나의 도핑 팁(doping tip)(4)을 포함하는 도핑 프로파일 엘리먼트(doping profiled element)가 형성되어 있으며, 그리고

상기 리세스는 상기 도핑 팁을 관통하는,

반도체 칩. - 제 1 항에 있어서,

상기 리세스 내부에는 콘택 층(65)이 형성되어 있으며, 상기 콘택 층은 상기 n-도전성 다층 구조물에 도전 접속된,

반도체 칩. - 제 1 항 또는 제 2 항에 있어서,

상기 반도체 층 시퀀스는 캐리어(5) 상에 배치되어 있고,

상기 n-도전성 다층 구조물은 상기 캐리어를 등지는 활성 영역의 측에 배치된,

반도체 칩. - 제 1 항 내지 제 3 항 중 어느 한 항에 있어서,

상기 적어도 하나의 도핑 팁 내의 도펀트 농도가 상기 n-도전성 다층 구조물의 저 농도로 n-도전성 도핑된 영역(45) 내의 도펀트 농도보다 적어도 5배 높은,

반도체 칩. - 제 4 항에 있어서,

상기 적어도 하나의 도핑 팁 내의 도펀트 농도가 적어도 4 * 1018 ㎝-3이고, 상기 저 농도로 n-도전성 도핑된 영역 내의 도펀트 농도가 최대 8 * 1017 ㎝-3인,

반도체 칩. - 제 1 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 도핑 팁이 1 ㎚(1 ㎚ 포함) 내지 30 ㎚(30 ㎚ 포함)의 수직 연장부를 갖는,

반도체 칩. - 제 1 항 내지 제 6 항 중 어느 한 항에 있어서,

상기 도핑 팁이 5 ㎚(5 ㎚ 포함) 내지 20 ㎚(20 ㎚ 포함)의 수직 연장부를 갖는,

반도체 칩. - 제 1 항 내지 제 7 항 중 어느 한 항에 있어서,

상기 도핑 팁이 상기 활성 영역으로부터 2 ㎚(2 ㎚ 포함) 내지 20 ㎚(20 ㎚ 포함)의 간격을 갖는,

반도체 칩. - 제 1 항 내지 제 8 항 중 어느 한 항에 있어서,

상기 n-도전성 다층 구조물이 다수의 양자 층(211)을 갖는 양자 구조물을 포함하는,

반도체 칩. - 제 9 항에 있어서,

상기 리세스는 상기 n-도전성 다층 구조물의 양자 층들을 관통하는,

반도체 칩. - 제 9 항에 있어서,

상기 활성 영역이 다수의 양자 층(201)을 포함하고, 상기 도핑 팁은 상기 활성 영역에 가장 가까운 n-도전성 다층 구조물의 양자 층과 상기 n-도전성 다층 구조물에 가장 가까운 활성 영역의 양자 층 사이에 배치된,

반도체 칩. - 제 11 항에 있어서,

상기 n-도전성 다층 구조물의 양자 층의 밴드 갭의 크기가 적어도 상기 활성 영역의 양자 층(201)의 밴드 갭과 동일한,

반도체 칩. - 제 9 항 내지 제 12 항 중 어느 한 항에 있어서,

상기 도핑 프로파일 엘리먼트가 추가의 도핑 팁(41)을 포함하고, 상기 도핑 팁과 추가의 도핑 팁 사이에는 상기 n-도전성 다층 구조물의 적어도 하나의 양자 층이 배치된,

반도체 칩. - 제 13 항에 있어서,

상기 추가의 도핑 팁(45)에 의해서 상기 n-도전성 다층 구조물의 양자 구조물의 부분 영역(216)이 높은 도펀트 농도를 갖는,

반도체 칩. - 제 1 항 내지 제 14 항 중 어느 한 항에 있어서,

상기 활성 영역이 질화물-화합물 반도체 재료를 기본으로 하는,

반도체 칩. - 제 1 항 내지 제 15 항 중 어느 한 항에 있어서,

상기 n-도전성 다층 구조물의 결정 구조가 V자형 피트(V-pit)들을 갖는,

반도체 칩. - 제 1 항 내지 제 16 항 중 어느 한 항에 있어서,

상기 반도체 몸체의 반도체 층 시퀀스를 위한 성장 기판이 분리된,

반도체 칩. - 제 1 항에 있어서,

상기 적어도 하나의 도핑 팁 내의 도펀트 농도가 상기 도핑 팁에 인접하는 n-도전성 다층 구조물의 영역 내의 도펀트 농도보다 적어도 5배 높고,

상기 활성 영역이 적어도 하나의 양자 층(201)을 갖는 양자 구조물을 포함하며, 그리고

상기 다층 구조물이 다수의 양자 층(211)을 갖는 양자 구조물을 포함하고, 상기 n-도전성 다층 구조물의 양자 층의 밴드 갭은 상기 활성 영역의 양자 층의 밴드 갭보다 큰,

반도체 칩.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102009060747A DE102009060747A1 (de) | 2009-12-30 | 2009-12-30 | Halbleiterchip |

| DE102009060747.1 | 2009-12-30 | ||

| PCT/EP2010/070761 WO2011080249A1 (de) | 2009-12-30 | 2010-12-27 | Lichtemittierender halbleiterchip |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020177017884A Division KR20170080718A (ko) | 2009-12-30 | 2010-12-27 | 발광 반도체 칩 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20180078359A true KR20180078359A (ko) | 2018-07-09 |

Family

ID=43827573

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020177017884A KR20170080718A (ko) | 2009-12-30 | 2010-12-27 | 발광 반도체 칩 |

| KR1020127020140A KR101755586B1 (ko) | 2009-12-30 | 2010-12-27 | 발광 반도체 칩 |

| KR1020187018915A KR20180078359A (ko) | 2009-12-30 | 2010-12-27 | 발광 반도체 칩 |

Family Applications Before (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020177017884A KR20170080718A (ko) | 2009-12-30 | 2010-12-27 | 발광 반도체 칩 |

| KR1020127020140A KR101755586B1 (ko) | 2009-12-30 | 2010-12-27 | 발광 반도체 칩 |

Country Status (8)

| Country | Link |

|---|---|

| US (4) | US9012885B2 (ko) |

| EP (1) | EP2519980B1 (ko) |

| JP (1) | JP5735984B2 (ko) |

| KR (3) | KR20170080718A (ko) |

| CN (2) | CN106229395B (ko) |

| DE (1) | DE102009060747A1 (ko) |

| TW (1) | TWI449212B (ko) |

| WO (1) | WO2011080249A1 (ko) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102009060747A1 (de) | 2009-12-30 | 2011-07-07 | OSRAM Opto Semiconductors GmbH, 93055 | Halbleiterchip |

| US8357924B2 (en) | 2010-01-05 | 2013-01-22 | Seoul Opto Device Co., Ltd. | Light emitting diode and method of fabricating the same |

| DE102011100037A1 (de) | 2011-04-29 | 2012-10-31 | Osram Opto Semiconductors Gmbh | Strahlung emittierender Halbleiterchip mit integriertem ESD-Schutz |

| JP5123414B2 (ja) * | 2011-05-16 | 2013-01-23 | 株式会社東芝 | 半導体発光素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法 |

| US9070613B2 (en) * | 2011-09-07 | 2015-06-30 | Lg Innotek Co., Ltd. | Light emitting device |

| DE102013103602A1 (de) * | 2013-04-10 | 2014-10-16 | Osram Opto Semiconductors Gmbh | Optoelektronischer Halbleiterchip und Verfahren zu seiner Herstellung |

| DE102013104272A1 (de) | 2013-04-26 | 2014-10-30 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement und Verfahren zu seiner Herstellung |

| DE102014111058A1 (de) * | 2014-08-04 | 2016-02-04 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement und Verfahren zur Herstellung |

| CN104701431B (zh) * | 2014-11-27 | 2017-03-29 | 厦门市三安光电科技有限公司 | 一种发光二极管的外延结构及其制作方法 |

| KR102391513B1 (ko) | 2015-10-05 | 2022-04-27 | 삼성전자주식회사 | 물질막 적층체, 발광 소자, 발광 패키지, 및 발광 소자의 제조 방법 |

| US20180033912A1 (en) * | 2016-07-28 | 2018-02-01 | Lumileds Llc | Iii-p light emitting device with a superlattice |

| JP6921179B2 (ja) * | 2016-07-28 | 2021-08-18 | ルミレッズ リミテッド ライアビリティ カンパニー | 超格子を用いたiii−p発光デバイス |

| DE102016120419A1 (de) * | 2016-10-26 | 2018-04-26 | Osram Opto Semiconductors Gmbh | Halbleiterkörper |

| DE102016123262A1 (de) * | 2016-12-01 | 2018-06-07 | Osram Opto Semiconductors Gmbh | Strahlungsemittierender Halbleiterkörper und Verfahren zur Herstellung einer Halbleiterschichtenfolge |

| DE102017104370A1 (de) * | 2017-03-02 | 2018-09-06 | Osram Opto Semiconductors Gmbh | Halbleiterkörper |

Family Cites Families (40)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07263748A (ja) * | 1994-03-22 | 1995-10-13 | Toyoda Gosei Co Ltd | 3族窒化物半導体発光素子及びその製造方法 |

| US6677619B1 (en) * | 1997-01-09 | 2004-01-13 | Nichia Chemical Industries, Ltd. | Nitride semiconductor device |

| JP3374737B2 (ja) | 1997-01-09 | 2003-02-10 | 日亜化学工業株式会社 | 窒化物半導体素子 |

| JP3429446B2 (ja) | 1998-03-19 | 2003-07-22 | シャープ株式会社 | 半導体発光素子 |

| EP0908988A3 (en) | 1997-10-06 | 2001-10-17 | Sharp Kabushiki Kaisha | Light-emitting device and fabricating method thereof |

| US7193246B1 (en) | 1998-03-12 | 2007-03-20 | Nichia Corporation | Nitride semiconductor device |

| JP3622562B2 (ja) | 1998-03-12 | 2005-02-23 | 日亜化学工業株式会社 | 窒化物半導体発光ダイオード |

| JP4629178B2 (ja) | 1998-10-06 | 2011-02-09 | 日亜化学工業株式会社 | 窒化物半導体素子 |

| US6649942B2 (en) * | 2001-05-23 | 2003-11-18 | Sanyo Electric Co., Ltd. | Nitride-based semiconductor light-emitting device |

| US6717969B2 (en) * | 2001-07-16 | 2004-04-06 | Fuji Photo Film Co., Ltd. | Semiconductor laser device which includes current confinement structure and trenches formed through current stopping layer down to active layer |

| KR100909739B1 (ko) | 2002-01-28 | 2009-07-29 | 니치아 카가쿠 고교 가부시키가이샤 | 대향전극구조의 질화물 반도체소자 |

| SG115549A1 (en) * | 2002-07-08 | 2005-10-28 | Sumitomo Chemical Co | Epitaxial substrate for compound semiconductor light emitting device, method for producing the same and light emitting device |

| JP2005093682A (ja) * | 2003-09-17 | 2005-04-07 | Toyoda Gosei Co Ltd | GaN系半導体発光素子及びその製造方法 |

| KR100456063B1 (ko) | 2004-02-13 | 2004-11-10 | 에피밸리 주식회사 | Ⅲ-질화물 반도체 발광소자 |

| JP2005277374A (ja) * | 2004-02-26 | 2005-10-06 | Toyoda Gosei Co Ltd | Iii族窒化物系化合物半導体発光素子及びその製造方法 |

| CN1324719C (zh) | 2004-04-01 | 2007-07-04 | 光磊科技股份有限公司 | 一种发光二极管 |

| TWI250666B (en) | 2004-05-03 | 2006-03-01 | Osram Opto Semiconductors Gmbh | Method to produce a radiation-emitting semiconductor-chip and said produced semiconductor-chip |

| US7943949B2 (en) * | 2004-09-09 | 2011-05-17 | Bridgelux, Inc. | III-nitride based on semiconductor device with low-resistance ohmic contacts |

| US7042018B2 (en) * | 2004-09-22 | 2006-05-09 | Formosa Epitaxy Incorporation | Structure of GaN light-emitting diode |

| US7042019B1 (en) * | 2004-10-12 | 2006-05-09 | Formosa Epitaxy Incorporation | Gallium-nitride based multi-quantum well light-emitting diode n-type contact layer structure |

| KR100631971B1 (ko) * | 2005-02-28 | 2006-10-11 | 삼성전기주식회사 | 질화물 반도체 발광 소자 |

| US7446345B2 (en) | 2005-04-29 | 2008-11-04 | Cree, Inc. | Light emitting devices with active layers that extend into opened pits |

| WO2007102627A1 (en) * | 2005-07-06 | 2007-09-13 | Lg Innotek Co., Ltd | Nitride semiconductor led and fabrication metho thereof |

| JP2007042751A (ja) * | 2005-08-01 | 2007-02-15 | Hitachi Cable Ltd | 半導体発光素子 |

| KR100674862B1 (ko) * | 2005-08-25 | 2007-01-29 | 삼성전기주식회사 | 질화물 반도체 발광 소자 |

| US20070051962A1 (en) * | 2005-09-08 | 2007-03-08 | Mu-Jen Lai | Gallium nitride semiconductor light emitting device |

| JP2007201195A (ja) * | 2006-01-26 | 2007-08-09 | Sumitomo Electric Ind Ltd | 窒化物半導体発光素子 |

| TWI325641B (en) * | 2006-09-04 | 2010-06-01 | Huga Optotech Inc | Light emitting device and methods for forming the same |

| DE102007019776A1 (de) | 2007-04-26 | 2008-10-30 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement und Verfahren zur Herstellung einer Mehrzahl optoelektronischer Bauelemente |

| DE102007046027A1 (de) | 2007-09-26 | 2009-04-02 | Osram Opto Semiconductors Gmbh | Optoelektronischer Halbleiterchip mit einer Mehrfachquantentopfstruktur |

| WO2009045005A2 (en) * | 2007-10-02 | 2009-04-09 | Epivalley Co., Ltd. | Iii-nitride semiconductor light emitting device |

| KR20090034163A (ko) | 2007-10-02 | 2009-04-07 | 주식회사 에피밸리 | 3족 질화물 반도체 발광소자 |

| DE102007057674A1 (de) * | 2007-11-30 | 2009-06-04 | Osram Opto Semiconductors Gmbh | LED mit Stromaufweitungsschicht |

| KR100903103B1 (ko) | 2007-12-05 | 2009-06-16 | 우리엘에스티 주식회사 | 화합물 반도체를 이용한 발광소자 |

| JP2009200084A (ja) | 2008-02-19 | 2009-09-03 | Seiko Instruments Inc | 発光デバイス |

| JP5992662B2 (ja) | 2008-02-29 | 2016-09-14 | オスラム オプト セミコンダクターズ ゲゼルシャフト ミット ベシュレンクテル ハフツングOsram Opto Semiconductors GmbH | モノリシックなオプトエレクトロニクス半導体ボディおよびその製造方法 |

| US8536615B1 (en) * | 2009-12-16 | 2013-09-17 | Cree, Inc. | Semiconductor device structures with modulated and delta doping and related methods |

| DE102009060747A1 (de) | 2009-12-30 | 2011-07-07 | OSRAM Opto Semiconductors GmbH, 93055 | Halbleiterchip |

| US8357924B2 (en) * | 2010-01-05 | 2013-01-22 | Seoul Opto Device Co., Ltd. | Light emitting diode and method of fabricating the same |

| CN101789473B (zh) * | 2010-02-23 | 2013-03-20 | 厦门大学 | 一种GaN基垂直结构发光二极管及其制备方法 |

-

2009

- 2009-12-30 DE DE102009060747A patent/DE102009060747A1/de active Granted

-

2010

- 2010-12-27 CN CN201610643061.9A patent/CN106229395B/zh active Active

- 2010-12-27 EP EP10798567.3A patent/EP2519980B1/de active Active

- 2010-12-27 US US13/518,809 patent/US9012885B2/en active Active

- 2010-12-27 TW TW099146097A patent/TWI449212B/zh active

- 2010-12-27 KR KR1020177017884A patent/KR20170080718A/ko active Application Filing

- 2010-12-27 KR KR1020127020140A patent/KR101755586B1/ko active IP Right Grant

- 2010-12-27 WO PCT/EP2010/070761 patent/WO2011080249A1/de active Application Filing

- 2010-12-27 CN CN201080060204.4A patent/CN102687290B/zh active Active

- 2010-12-27 JP JP2012546427A patent/JP5735984B2/ja active Active

- 2010-12-27 KR KR1020187018915A patent/KR20180078359A/ko not_active Application Discontinuation

-

2015

- 2015-03-18 US US14/662,037 patent/US9530931B2/en active Active

-

2016

- 2016-10-06 US US15/287,140 patent/US9799797B2/en active Active

-

2017

- 2017-07-21 US US15/656,169 patent/US10388828B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP5735984B2 (ja) | 2015-06-17 |

| US9799797B2 (en) | 2017-10-24 |

| CN106229395A (zh) | 2016-12-14 |

| KR20120102146A (ko) | 2012-09-17 |

| KR101755586B1 (ko) | 2017-07-07 |

| US9012885B2 (en) | 2015-04-21 |

| US20170025570A1 (en) | 2017-01-26 |

| TWI449212B (zh) | 2014-08-11 |

| EP2519980B1 (de) | 2019-04-03 |

| CN106229395B (zh) | 2020-08-14 |

| DE102009060747A1 (de) | 2011-07-07 |

| US9530931B2 (en) | 2016-12-27 |

| US10388828B2 (en) | 2019-08-20 |

| EP2519980A1 (de) | 2012-11-07 |

| WO2011080249A1 (de) | 2011-07-07 |

| US20170324001A1 (en) | 2017-11-09 |

| TW201135968A (en) | 2011-10-16 |

| KR20170080718A (ko) | 2017-07-10 |

| US20120298964A1 (en) | 2012-11-29 |

| CN102687290B (zh) | 2016-08-17 |

| CN102687290A (zh) | 2012-09-19 |

| US20150194570A1 (en) | 2015-07-09 |

| JP2013516751A (ja) | 2013-05-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101755586B1 (ko) | 발광 반도체 칩 | |

| US7939833B2 (en) | Nitride semiconductor light emitting device | |

| KR101536791B1 (ko) | 전류 확산층을 포함한 led | |

| CN114243448B (zh) | 半导体激光二极管 | |

| US7791081B2 (en) | Radiation-emitting semiconductor chip | |

| US9293657B2 (en) | Semiconductor light emitting device | |

| KR101221067B1 (ko) | 리지 도파형 반도체 레이저 다이오드 | |

| KR20110072424A (ko) | 발광 소자, 발광 소자 패키지 및 발광 소자 제조방법 | |

| KR20110027296A (ko) | 발광소자 및 그 제조방법 | |

| JP7129630B2 (ja) | 発光素子および発光素子の製造方法 | |

| JP7064269B2 (ja) | 半導体発光素子 | |

| US20130181187A1 (en) | Semiconductor light emitting device | |

| RU2277736C1 (ru) | Полупроводниковый элемент, излучающий свет в синей области видимого спектра | |

| US8354687B1 (en) | Efficient thermal management and packaging for group III nitride based UV devices | |

| US20140353578A1 (en) | Light-emitting device | |

| KR101172136B1 (ko) | 발광소자, 발광소자의 제조방법 및 발광소자 패키지 | |

| CN116435428A (zh) | Iii族氮化物半导体光电器件结构及其制备方法 | |

| KR20110101116A (ko) | 발광소자 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A107 | Divisional application of patent | ||

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application |