KR20180037326A - Soi 웨이퍼를 인시츄로 패시베이션하기 위한 방법 - Google Patents

Soi 웨이퍼를 인시츄로 패시베이션하기 위한 방법 Download PDFInfo

- Publication number

- KR20180037326A KR20180037326A KR1020187009456A KR20187009456A KR20180037326A KR 20180037326 A KR20180037326 A KR 20180037326A KR 1020187009456 A KR1020187009456 A KR 1020187009456A KR 20187009456 A KR20187009456 A KR 20187009456A KR 20180037326 A KR20180037326 A KR 20180037326A

- Authority

- KR

- South Korea

- Prior art keywords

- wafer

- chamber

- cleaned surface

- soi

- soi wafer

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/7806—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices involving the separation of the active layers from a substrate

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Element Separation (AREA)

- Formation Of Insulating Films (AREA)

- Pressure Welding/Diffusion-Bonding (AREA)

Abstract

웨이퍼가 클리브되는 챔버에서 SOI 웨이퍼에 대해 패시베이션 프로세스를 수행하기 위한 방법 및 시스템이 개시된다. 결합된 웨이퍼 쌍은 SOI(silicon-on-insulator; SOI) 웨이퍼를 형성하기 위해 챔버 내에서 클리브된다. SOI 웨이퍼의 클리브된 표면은 그 다음 현장에서(in-situ) 클리브된 표면을 패시베이션 물질(passivating substance)에 노출하여 패시베이션된다. 패시베이션 물질로의 이러한 노출은 결과적으로 클리브된 표면에 얇은 산화물층을 형성하게 된다. SOI 웨이퍼는 그 다음 챔버로부터 제거된다. 다른 실시예들에서, SOI 웨이퍼는 먼저 인접한 챔버로 이송되고, 그 다음 웨이퍼가 패시베이션된다. 웨이퍼를 챔버 외측 분위기에 노출하지 않고 웨이퍼가 인접한 챔버로 이송된다.

Description

반도체 웨이퍼는 일반적으로 단결정 잉곳(single crystal ingot)(예컨대, 실리콘 잉곳)으로부터 개개의 웨이퍼로 슬라이스되어 마련된다. 웨이퍼의 한 유형으로는 SOI(silicon-on-insulator) 웨이퍼가 있다. SOI 웨이퍼는 절연층(즉, 산화물층)의 상부에 얇은 실리콘층을 포함하고, 실리콘 기판상에 배치된다. SOI 웨이퍼는 한 쌍의 웨이퍼를 함께 결합(bond)하고, 나중에 클리빙 동작(cleaving operation)에서 웨이퍼들 중 하나의 일부를 제거함으로써 형성된다.

SOI 웨이퍼의 외부(즉, 클리브된(cleaved)) 표면은, SOI 웨이퍼가 형성되는 챔버로부터 분리된 후 다양한 재료와의 접촉 또는 노출에 의해 종종 오염된다. 오염되면, SOI 웨이퍼의 클리브된 표면의 클리닝이 어려워지고, 시간이 많이 걸리며, 비용이 많이 들고, 완전히 성공적이지 못할 때가 많다. 따라서, SOI 웨이퍼의 클리브된 표면을 오염으로부터 보호하는 프로세스에 대한 충족되지 않은 욕구가 남아 있다.

하나의 측면은 챔버에서 SOI 웨이퍼에 대해 패시베이션 프로세스(passivation process))를 수행하기 위한 방법이다. 이 방법은 SOI(SOI) 웨이퍼를 형성하기 위해 챔버 내에서 결합된 웨이퍼 쌍(bonded wafer pair)을 클리브하는 단계를 포함하며, SOI 웨이퍼는 클리브된 표면을 갖는다. 그 다음 상기 클리브된 표면을 가스 형태의 오존에 노출하여, SOI 웨이퍼의 클리브된 표면이 인시츄(in-situ)로 패시베이션되고(passivated), 여기에서 클리브된 표면을 가스 형태의 오존에 노출하여 결과적으로 클리브된 표면에 얇은 산화물층이 형성된다. 그 다음 SOI 웨이퍼는 챔버로부터 분리된다.

또 다른 측면은, 결합된 웨이퍼 쌍이 SOI 웨이퍼를 형성하기 위해 클리브되는(cleaved) 챔버에서 SOI 웨이퍼에 대해 패시베이션 프로세스를 수행하기 위한 방법이다. 이 방법은 SOI 웨이퍼를 형성하기 위해 챔버 내에서 결합된 웨이퍼 쌍을 클리브하는 단계를 포함하고, 여기에서 결합된 웨이퍼 쌍을 클리브하여 SOI 웨이퍼 상에 클리브된 표면을 형성한다. 그 다음 클리브된 표면에 얇은 산화물층을 형성하기 위해, SOI 웨이퍼의 클리브된 표면에 대한 패시베이션 프로세스가 인시츄로 수행된다. 그 다음 SOI 웨이퍼는 챔버로부터 분리된다.

또 다른 측면은 계층화된(layered) 실리콘 구조가 형성되는 제1 챔버에 인접한 제2 챔버에서 계층화된 실리콘 구조에 대해 패시베이션 프로세스를 수행하는 방법이다. 이 방법은 제1 챔버에서 계층화된 실리콘 구조를 형성하는 단계를 포함하고, 계층화된 구조는 표면을 갖는다. 그 다음, 챔버 외측의 분위기(atmosphere)에 계층화된 실리콘 구조를 노출하지 않고, 계층화된 실리콘 구조는 제1 챔버에서 제2 챔버로 이송된다. 그 다음 패시베이션 프로세스는 계층화된 실리콘 구조의 표면에 대해 수행된다. 그 다음 계층화된 실리콘 구조는 제2 챔버로부터 분리된다.

위에서 언급한 측면들과 관련하여 주목된 특징들에 대한 다양한 개선(refinements)이 존재한다. 뿐만 아니라, 위에서 언급한 측면들에는 추가 특징들이 또한 포함될 수 있다. 이러한 개선들 및 추가 특징들은 개별적으로 또는 임의의 조합으로 존재할 수 있다. 예를 들어, 도시된 실시예들 중 임의의 것과 관련하여 아래 논의된 다양한 특징들은, 단독으로 또는 임의의 조합으로, 위에서 설명한 측면들 중 임의의 것에 통합될 수 있다.

도 1은 도너(donor) 실리콘 웨이퍼의 상면도이다.

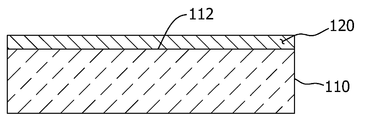

도 2는 도 1b의 도너 실리콘 웨이퍼의 단면도이다.

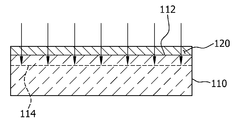

도 3은 이온 주입 중인 도너 실리콘 웨이퍼의 단면도이다.

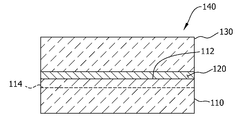

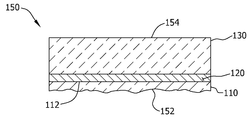

도 4는 핸들 실리콘 웨이퍼에 결합된 도너 실리콘 웨이퍼를 포함하는 결합된 웨이퍼의 단면도이다.

도 5는, SOI 웨이퍼를 형성하기 위해 도너 웨이퍼의 일부가 제거된 후의, 도 4의 결합된 웨이퍼의 단면도이다.

도 6은, 웨이퍼의 클리브된 표면이 평탄화된 후의, 도 5의 SOI 웨이퍼의 단면도이다.

도 7은 도 4의 결합된 웨이퍼를 클리브하기 위해 그 안에 고정물이 배치된 챔버의 개략도이다.

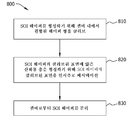

도 8은 SOI 웨이퍼가 형성되는 챔버에서 SOI 웨이퍼에 대해 패시베이션 프로세스를 수행하는 방법을 도시하는 순서도이다.

도 9는 SOI 웨이퍼가 형성되는 챔버에서 SOI 웨이퍼에 대해 패시베이션 프로세스를 수행하는 다른 방법을 도시하는 순서도이다.

도 10은 SOI 웨이퍼가 형성되는 챔버에서 SOI 웨이퍼에 대해 패시베이션 프로세스를 수행하는 또 다른 방법을 도시하는 순서도이다.

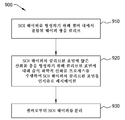

도 11은 계층화된 실리콘 구조가 형성되는 챔버에 인접한 챔버에서 계층화된 실리콘 구조에 대해 패시베이션 프로세스를 수행하는 방법을 도시하는 순서도이다.

도 2는 도 1b의 도너 실리콘 웨이퍼의 단면도이다.

도 3은 이온 주입 중인 도너 실리콘 웨이퍼의 단면도이다.

도 4는 핸들 실리콘 웨이퍼에 결합된 도너 실리콘 웨이퍼를 포함하는 결합된 웨이퍼의 단면도이다.

도 5는, SOI 웨이퍼를 형성하기 위해 도너 웨이퍼의 일부가 제거된 후의, 도 4의 결합된 웨이퍼의 단면도이다.

도 6은, 웨이퍼의 클리브된 표면이 평탄화된 후의, 도 5의 SOI 웨이퍼의 단면도이다.

도 7은 도 4의 결합된 웨이퍼를 클리브하기 위해 그 안에 고정물이 배치된 챔버의 개략도이다.

도 8은 SOI 웨이퍼가 형성되는 챔버에서 SOI 웨이퍼에 대해 패시베이션 프로세스를 수행하는 방법을 도시하는 순서도이다.

도 9는 SOI 웨이퍼가 형성되는 챔버에서 SOI 웨이퍼에 대해 패시베이션 프로세스를 수행하는 다른 방법을 도시하는 순서도이다.

도 10은 SOI 웨이퍼가 형성되는 챔버에서 SOI 웨이퍼에 대해 패시베이션 프로세스를 수행하는 또 다른 방법을 도시하는 순서도이다.

도 11은 계층화된 실리콘 구조가 형성되는 챔버에 인접한 챔버에서 계층화된 실리콘 구조에 대해 패시베이션 프로세스를 수행하는 방법을 도시하는 순서도이다.

처음에 도 1 및 2를 참조하면, 본 개시물의 하나의 실시예의 도너 웨이퍼(donor wafer; 110) 및 산화물층(oxide layer; 120)이 도시된다. 도 1은 도너 웨이퍼(110)의 상면도인 한편, 도 2는 도너 웨이퍼의 단면도이다. 산화물층(120)은 도너 웨이퍼(110)의 전방 표면(front surface; 112)에 결합된다. 산화물층(120)은 도너 웨이퍼(110)를 산화물층 성장에 적합한 분위기에서 처리함으로써 전방 표면(112)의 상부에서 성장될 수 있다. 대안적으로, 산화물층(120)은 임의의 알려진 화학적 피착 프로세스를 통해 전방 표면(112)에 피착될 수 있고, 절연체(즉, 유전체)의 역할을 한다.

도 3은 입자들(예컨대, 수소 원자 또는 수소 원자와 헬륨 원자 둘 다의 조합)이 주입되는 도너 웨이퍼(110)의 단면도이다. 도너 웨이퍼(110)에는, 도너 웨이퍼(110)의 전방 표면(112) 아래 지정된 깊이로 입자들이 주입된다. 일부 실시예들에서, 입자들은 이온 주입 프로세스를 통해 주입되는 수소 또는 헬륨 이온이다. 그 다음, 클리브 면(cleave plane; 114)은, 도너 웨이퍼(120)의 전방 표면(112) 아래, 입자들이 주입된 지정된 깊이와 동일한 전방 표면으로부터의 거리에 형성된다. 클리브 면(114)은 도너 웨이퍼(110)를 관통하는 면을 정의하며, 여기서, 도너 웨이퍼는 이온의 주입에 의해 그리고 후속하는 도너 웨이퍼의 가열시에 실질적으로 약화된다.

도 4는 결합된 웨이퍼(140)를 형성하기 위해 함께 결합된 도너 웨이퍼(110)와 핸들 웨이퍼(130)의 단면도이다. 도너 웨이퍼(110) 및 핸들 웨이퍼(130)는, 친수성 결합(hydrophilic bond)과 같은, 임의의 적절한 방법에 따라 함께 결합된다. 도너 웨이퍼(110) 및 핸들 웨이퍼(130)는, 예를 들어, 산소 또는 질소를 함유하는 플라즈마에 웨이퍼의 표면을 노출하여 함께 결합된다. 웨이퍼들(110, 130)의 표면은 종종 표면 활성화(surface activation)로 지칭되는 프로세스에서 플라즈마에 노출하여 수정된다. 그 다음 웨이퍼들(110, 130)은 함께 가압되어 그들 사이에 결합이 형성된다. 이러한 결합은 약하지만, 결합된 웨이퍼(140)가 더 처리되기 전에 결합이 강화된다.

일부 프로세스에서, 도너 웨이퍼(110)와 핸들 웨이퍼(130) 사이의 친수성 결합(즉, 결합된 웨이퍼(140))은 결합된 웨이퍼 쌍을 대략 300℃와 500℃ 사이의 온도에서 가열 또는 어닐링하여 강화된다. 높은 온도(elevated temperatures)는 도너 웨이퍼(110)와 핸들 웨이퍼(130)의 인접한 표면들 사이에 공유 결합(covalent bonds)의 형성을 야기하므로, 도너 웨이퍼와 핸들 웨이퍼 사이의 결합을 확고히 한다(solidifying). 결합된 웨이퍼(140)의 가열 또는 어닐링과 동시에, 도너 웨이퍼(110)에 더 일찍 주입된 입자들은 이동하기 시작하고 클리브 면(114)을 약화시킨다.

도 5는, 결합된 웨이퍼의 일부가 클리브 프로세스동안 분리된 후에, 결과적으로, 일반적으로 150으로 지칭되는, SOI(SOI) 웨이퍼를 생성하게 되는, 도 4에 도시된 결합된 웨이퍼(140)의 단면도이다. 다른 방법들에 따르면, 결합된 웨이퍼(140)는 그 대신 결합된 웨이퍼로부터 도너 웨이퍼의 일부를 분리하기 위해 일정 시간 기간에 걸쳐 높은 온도의 적용을 받게 할 수 있다. 높은 온도에 노출함으로써, 균열(crack)이 시작된 다음 클리브 면을 따라 전파되고, 따라서, 도너 웨이퍼의 나머지 부분(remainder)으로부터 도너 웨이퍼(110)의 일부가 분리된다.

클리브 면(114)은 이온의 주입에 의해 실질적으로 약화되었기 때문에, 클리브 면은 경계를 정의하는데, 힘이 인가될 때 그 경계를 따라 웨이퍼가 쉽게 분리되어 진다. 일부 실시예들에 따르면, 도 7에 도시된 바와 같이, 결합된 웨이퍼(140)는 먼저 챔버(170) 내에 배치된 고정물(fixture)(일반적으로 160에서 점선으로 표시됨)에 위치한다. 챔버(170)는 결합된 웨이퍼(140)의 클리브 동안 외측 환경으로부터 실질적으로 밀폐되고, 예시적인 실시예에서, SOI 웨이퍼(150)가 패시베이션되기 전에 불활성 가스(inert gas)(예컨대, 아르곤 또는 질소)로 채워진다. 또 다른 실시예에서, 챔버(170)는 불활성 가스로 채워지지 않고, 그 대신 클리브된 후에 웨이퍼의 표면을 패시베이션하는 가스 또는 물질(substance)(아래에 더 자세히 설명됨)로 채워진다. 게다가, 일부 실시예들에서, 결합된 웨이퍼(140)는 야외 환경(open-air environment)에서 클리브된다. 이 야외 환경에서, SOI 웨이퍼(150)의 클리브된 표면(152)은 분위기(atmosphere)에서 흔히 발견된 요소들에 노출될 수 있다. SOI 웨이퍼(150)의 클리브된 표면(152)의 패시베이션을 돕기 위해 이러한 야외 환경에서 습도(humidity)가 증가될 수 있다. 이러한 실시예들에서, SOI 웨이퍼(150)는 카세트에 배치될 수 있다. 카세트는 다수의 웨이퍼를 가지고 있을 수 있다. 이 카세트는 SOI 웨이퍼의 클리브된 표면(152)을 패시베이션하기 위해 질소 또는 다른 패시베이션 물질(예컨대, 오존)로 퍼지(purge)될 수 있다.

고정물(160)은, 결합된 웨이퍼로부터 도너 웨이퍼(110)의 일부를 떼어내기 위해, 결합된 웨이퍼(140)의 맞은 편(opposing sides)에 수직인 기계적 힘을 인가한다. 하나의 실시예에서, 흡입 컵들(suction cups)이 기계적 힘을 인가하기 위해 사용된다. 도너 웨이퍼(110)의 일부의 분리는, 클리브 면을 따른 균열의 전파를 개시하기 위해, 클리브 면에서 결합된 웨이퍼의 에지에 기계적 웨지(mechanical wedge)를 인가하여 개시된다. 클리브 면의 약화된 구조로 인해, 결합된 웨이퍼(140)가 클리브 면을 따라 두 조각으로 분리될 때까지, 균열이 클리브 면(114)을 따라 전파한다. 흡입 컵들에 의해 인가된 기계적 힘은 그 다음 결합된 웨이퍼(140)를 두 조각으로 떼어 놓는다. 한 조각은 도너 웨이퍼(110)의 일부로만 이루어진다. 다른 한 조각은 핸들 웨이퍼(130) 및 거기에 결합된 도너 웨이퍼(110)의 일부로 이루어지고 SOI 웨이퍼(150)를 형성한다.

SOI 웨이퍼(150)의 클리브된 표면(152)은 클리브 면(114)을 따른 결합된 웨이퍼(140)의 분리 후의 결과적인 표면을 정의한다. 클리브된 표면(152)은 클리브 면(114)을 따라 분리된 결과로 손상된 표면을 갖게 되고, 이 표면은 추가적인 처리 없이는 최종 사용 애플리케이션에 부적절하게 된다. 따라서, 손상을 복구하고 클리브된 표면을 평탄화하기 위해, 클리브된 표면(152)은 추가적인 처리 단계들의 적용을 받아, 결과적으로 도 6에 도시된 평탄한 클리브된 표면(152S)을 얻게 된다.

이전 시스템에서 SOI 웨이퍼(150)의 클리브된 표면(152)은 종종 도너 웨이퍼(110)의 일부의 클리브 또는 분리한 다음 오염되었다. 오염은, 클리브된 후에 SOI 웨이퍼(150)가 저장되는 카세트와 같은, 다양한 소스에서 발생할 수 있다. 오염의 소스는 또한 챔버(170)로부터 분리된 후 및 후속 처리 동작들 이전에 SOI 웨이퍼(150)가 노출되는 분위기 내의 오염 물질들(예컨대, 유기 화합물 등)을 포함할 수 있다.

임의의 특정한 이론에 한정되는 것은 아니지만, 클리브된 표면(152)의 오염에 대한 친화성(affinity)은 클리브 동작 동안 SOI 웨이퍼(150)의 클리브된 표면에 형성된 댕글링 결합(dangling bond)의 결과인 것으로 믿어진다. 도너 웨이퍼(110)의 일부가 접합된 웨이퍼(140)부터 클리브될 때, 클리브된 표면(152)에서 분자들로부터 원자들이 제거됨에 따라, 이러한 댕글링 결합은 화학적으로 반응성이 높은 것으로 믿어진다. 댕글링 결합은 SOI 웨이퍼(150)의 클리브된 표면(152)에 접촉하는 물질에, 특히 유기 물질(즉, 탄소를 포함하는 물질)에 빠르게 반응한다.

클리브된 표면(152)에 대해 수행된 클리닝 프로세스는 클리브된 표면 상의 오염을 제거하려고 시도하기 위해 이전 시스템들에서 수정되었다. 그러나, 이러한 클리닝 프로세스는 완전히 성공적이지는 않았다. SOI 웨이퍼(150)의 클리브된 표면(152)으로부터 오염을 제거하려는 다른 시도는 챔버(170) 내에서 환경의 청결을 개선하거나 SOI 웨이퍼(150)가 저장되는 카세트를 교체하는 것에 의해 오염의 소스들을 제거하는 것에 초점이 맞추어 진다. 많은 잠재적인 오염 소스가 존재하고, 클리브된 표면(152)은 오염 물질과의 반응에 대한 강한 친화성을 갖는 것으로 믿어짐에 따라, 이러한 시도들이 마찬가지로 만족스럽지 못한 결과를 산출했다.

따라서, SOI 웨이퍼(150)의 클리브된 표면(152)이 오염물과 반응하지 않도록, 클리브된 표면을 패시베이션 물질에 노출시켜 패시베이션하는 방법이 여기에 개시되어 있다. 일반적으로, 여기에 설명된 방법에 사용된 패시베이션 물질(passivating substances)은 이에 노출될 때 SOI 웨이퍼(150)의 클리브된 표면(152)에 얇은 산화물층을 성장 및/또는 형성하는 산화 물질을 포함한다. 클리브된 표면(152)에 대해 패시베이션이 수행되면 결과적으로 클리브된 표면에 나중에 피착되는 임의의 오염 물질이 상대적으로 쉽게 제거되게 된다. SOI 웨이퍼(150)의 클리브된 표면(152)은 또한 웨이퍼가 클리브된 후에 인시츄로 패시베이션된다. 즉, SOI 웨이퍼(150)는, 그것이 챔버(170)에 있는 동안 및 챔버로부터 분리되기 전에 패시베이션된다. 클리빙(cleaving) 및 패시베이션(passivation) 사이에 어떠한 중간 또는 다른 단계들도 수행되지 않는다.

SOI 웨이퍼(150)는 따라서 패시베이션되기 전에 챔버(170)을 둘러싼 외측 분위기에 노출되지 않는다. 따라서, SOI 웨이퍼의 반응성이 높은 클리브된 표면은 패시베이션되기 전에 오염 물질에 노출되지 않고, 챔버(170) 내에서 제어된 불활성 분위기에만 노출된다. 위에서 설명한 바와 같이, 일부 실시예들에서, 불활성 분위기는 챔버(170) 내에서 사용되지 않고, 그 대신 웨이퍼가 클리브되는 동안 또는 그 직후에 웨이퍼의 표면을 패시베이션하는 가스 또는 다른 물질(넓게는, "패시베이션 물질(passivating substance)")이 챔버에 존재한다. 웨이퍼는 따라서 불활성 환경 보다는 오히려 패시베이션 환경(passivating environment)에서 클리브될 수 있다.

다른 실시예들에서, SOI 웨이퍼(150)는 챔버(170)에서 인접한 챔버(180)(넓게는, "제2 챔버")로 전송될 수 있고, 여기에서 그것은 패시베이션된다. 이러한 인접한 챔버(180)는 챔버(170)에 인접하게 배치되고, 챔버들을 둘러싼, 외측 분위기 및 그 안에 포함된 오염 물질들에 SOI 웨이퍼를 노출하지 않고, SOI 웨이퍼(150)가 챔버에서 인접한 챔버로 이송될 수 있도록 챔버들 양측이 구성된다.

게다가, 다른 계층화된 실리콘 구조(예컨대, 비-산화된 도너 웨이퍼를 사용하는 직접 실리콘-결합 구조)의 표면은 또한 SOI 웨이퍼(150)의 클리브된 표면(152)과 동일한 유형의 오염에 민감하다. 따라서, SOI 웨이퍼(150)의 클리브된 표면(152)에 대해 패시베이션 프로세스를 수행하기 위한 여기에 설명된 방법은 계층화된 실리콘 구조의 표면에 대해서도 사용될 수 있다.

도 8은, 도 1-7과 관련하여 위에서 설명한 SOI 웨이퍼(150)와 같은, SOI 웨이퍼에 대해 패시베이션 프로세스를 수행하기 위한 방법(800)을 도시한다. 방법(800)은 SOI 웨이퍼를 형성하기 위해 챔버(즉, 챔버(170)) 내에서 결합된 웨이퍼 쌍을 클리브하는 블록 810에서 시작된다. SOI 웨이퍼의 클리브된 표면은 그 다음 블록 820에서 인시츄로(즉, 여전히 챔버에 있는 동안) 패시베이션된다. SOI 웨이퍼의 클리브된 표면은 가스 형태의 오존에 그것을 노출하여 패시베이션될 수 있다. 오존은, 결합된 웨이퍼 쌍이 클리브된 후에 챔버에 유입될 수 있고, 또한 오존은 결합된 웨이퍼 쌍이 클리브되는 동안 챔버에 존재할 수 있다. 기체 오존에 클리브된 표면을 노출하는 것으로 인해, 클리브된 표면에 얇은 산화물층이 형성된다. 이러한 얇은 산화물층은 클리브된 표면이 오염 물질과 반응하는 것을 방지할 수 있다. 클리브된 표면에 나중에 증착되는 오염 물질은, 얇은 산화물층에 의해, 그들이 클리브된 표면에 반응 또는 결합하는 것이 방지되기 때문에, 더 쉽게 제거된다.

다른 실시예들에서, SOI 웨이퍼의 클리브된 표면은 가스 오존을 생성하는 자외선에 노출되어 패시베이션된다. 자외선에 클리브된 표면을 노출하는 동안 클리브된 표면에 얇은 산화물층이 형성된다. 게다가, 다른 실시예들에서, SOI 웨이퍼의 클리브된 표면은 산화 글로우 방전 플라즈마 프로세스(oxidizing glow discharge plasma process)에 노출하여 패시베이션된다.

도 9는 SOI 웨이퍼에 대해 패시베이션 프로세스를 수행하기 위한 방법(900)을 도시한다. 도 9의 방법(900)은, 그 방법(900)이 SOI 웨이퍼의 클리브된 표면을 패시베이션하기 위해 상이한 프로세스를 사용한다는 것을 제외하고, 위에서 설명한 방법(800)과 유사하다. 방법(900)은 SOI 웨이퍼를 형성하기 위해 챔버 내에서 결합된 웨이퍼 쌍을 클리브하는 블록 910에서 시작된다. 그 다음 블록 920에서 SOI 웨이퍼의 클리브된 표면은 인시츄로(즉, 여전히 챔버에 있는 동안) 패시베이션된다. SOI 웨이퍼의 클리브된 표면은 코로나 방전에 그것을 노출하여 패시베이션된다. 코로나 방전은 전도체를 둘러싼 유체의 이온화에 의해 개시되는 전기적 방전이다. 전위 그래디언트(potential gradient)(즉, 전기장의 강도)가 그 유체에 대한 특정 값을 초과할 때, 전기적 방전이 발생한다. 전기적 방전은 전도체와 SOI 웨이퍼 주변에 플라즈마를 형성한다. 플라즈마의 생성은 SOI 웨이퍼의 클리브된 표면에 얇은 산화물층을 형성하기 위해 클리브된 표면과 반응하는 오존 및 산소 유리기(free radical)를 생성한다. 이러한 얇은 산화물층은 클리브된 표면이 오염 물질과 반응하는 것을 방지한다. 클리브된 표면에 나중에 증착되는 오염 물질은, 얇은 산화물층에 의해, 그들이 클리브된 표면에 반응 또는 결합하는 것이 방지되기 때문에, 쉽게 제거된다.

도 10은 SOI 웨이퍼에 대해 패시베이션 프로세스를 수행하기 위한 방법(1000)을 도시하는데, 그 방법(1000)은 웨이퍼의 클리브된 표면을 패시베이션하기 위해 상이한 프로세스를 사용하는 것을 제외하고, 위에서 설명한 방법들(800, 900)과 유사하다. 방법(1000)은, 결합된 웨이퍼 쌍이 SOI 웨이퍼를 형성하기 위해 클리브되는 블록 1010에서 시작된다. 그 다음 블록 1020에서 SOI 웨이퍼의 클리브된 표면이 인시츄로 패시베이션된다. SOI 웨이퍼의 클리브된 표면은 클리브된 표면에 대해 습식 화학적 산화물 프로세스(wet chemical oxide process)를 수행하여 패시베이션된다. 습식 화학적 산화물 프로세스는 결과적으로 클리브된 표면에 얇은 산화물층이 형성되게 하여 클리브된 표면이 그것이 접촉하는 오염 물질과 반응하는 것을 방지한다. 게다가, 클리브된 표면에 나중에 증착되는 오염 물질은, 얇은 산화물층에 의해, 그들이 클리브된 표면에 반응 또는 결합하는 것을 방지하기 때문에, 쉽게 제거된다.

다른 실시예들에서, SOI 웨이퍼의 클리브된 표면은 오존화된 물(ozonated water)과 과산화수소(hydrogen peroxide) 중 하나를 포함하는 습식 화학적 에칭에 노출하여 패시베이션된다. 습식 화학적 에칭 컴포지션들의 다른 예들은 표준 클린(Standard Clean) 1(즉, 암모니아 수산화물, 과산화물, 및 물) 및 표준 클린 2(즉, HCl 및 과산화수소)로 지칭된 컴포지션들을 포함한다.

도 11은 계층화된 실리콘 구조(예컨대, SOI 웨이퍼, 또는 직접 실리콘-결합 구조)에 대해 패시베이션 프로세스를 수행하기 위한 방법(1100)을 도시하는 것으로, 계층화된 실리콘 구조가 형성되는 챔버에 인접한 제2 챔버에서 패시베이션 프로세스가 수행된다는 것을 제외하면, 위에서 설명한 방법들(800, 900, 1000)과 유사하다. 방법(1100)은 계층화된 실리콘 구조가 제1 챔버(예컨대, 챔버(170))에 형성되는 블록 1110에서 시작된다. 블록 1120에서, 계층화된 실리콘 구조는 제1 챔버에서 인접한 제2 챔버(예컨대, 제2 챔버(180))로 전송된다. 계층화된 실리콘 구조가 챔버의 외측 분위기 및 그 안에 포함된 오염 물질에 노출되지 않고 그들 사이에서 전송될 수 있도록 제1 챔버와 제2 챔버가 각각 구성된다. 따라서, 두 개의 챔버 사이에 무결성을 유지하기 위해, 제1 챔버와 인접한 챔버 사이에 일련의 밀폐 또는 다른 메커니즘이 배치될 수 있다. 제1 챔버에서 제2 챔버로 계층화된 실리콘 구조를 운송하기 위해 챔버들 내에 메커니즘(예컨대, 트롤리(trolley)) 또는 다른 적절한 디바이스가 또한 배치될 수 있다.

블록 1130에서, 계층화된 실리콘 구조의 표면은 제2 챔버에서 패시베이션된다. 표면에 대해 사용된 패시베이션 프로세스는 도 8-10과 관련하여 위에서 설명한 것들 중 임의의 것일 수 있고, 결과적으로 표면에 얇은 산화물층이 형성된다. 구조의 표면에 형성된 얇은 산화물층은, 표면이 오염 물질과 반응 또는 그에 결합하는 것을 방지한다는 점에서, 도 8-10과 관련하여 위에서 설명한 것과 동일한 기능을 제공한다. 패시베이션 프로세스가 완료되고 얇은 산화물층이 표면에 형성된 후에, 블록 1140에서 계층화된 실리콘 구조는 제2 챔버로부터 제거된다.

별도로 명시하지 않는 한, 여기에 도시 및 설명된 본 발명의 실시예들에서 동작들의 실행 또는 수행 순서는 필수적인 것이 아니다. 즉, 별도로 명시하지 않는 한, 동작들은 임의의 순서로 수행될 수 있으며, 본 발명의 실시예들은 여기에 개시된 것 외에 추가의 또는 더 적은 동작을 포함할 수 있다. 예를 들어, 또 다른 동작 이전에, 그와 동시에, 또는 그 이후에 특정한 동작을 실행 또는 수행하는 것은 본 발명의 측면들의 범위 내에 있는 것으로 생각된다.

본 발명 또는 그의 실시예(들)의 요소들을 소개할 때, "하나(a, an)", "그(the)", 및 "상기(said)"라는 항목은 하나 이상의 요소들이 존재한다는 것을 의미하기 위한 것이다. "포함하는(comprising, including)" 및 "갖는(having)"이라는 용어는 포괄적인 것으로 의도되고 나열된 요소들 외에 추가적인 요소들이 존재할 수 있다는 것을 의미하기 위한 것이다.

본 발명의 범위를 벗어나지 않고 위의 구성들에서 다양한 변경이 실시될 수 있어, 위의 설명에 포함되고 첨부 도면에 도시된 모든 문제는 제한적인 의미가 아니라 예시적인 것으로 해석되도록 의도된다.

Claims (1)

- 제1항에 기재된 장치.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US35999810P | 2010-06-30 | 2010-06-30 | |

| US61/359,998 | 2010-06-30 | ||

| PCT/IB2011/052903 WO2012001659A2 (en) | 2010-06-30 | 2011-06-30 | Methods for in-situ passivation of silicon-on-insulator wafers |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020137002599A Division KR102083688B1 (ko) | 2010-06-30 | 2011-06-30 | Soi 웨이퍼를 인시츄로 패시베이션하기 위한 방법 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020197020821A Division KR20190087668A (ko) | 2010-06-30 | 2011-06-30 | Soi 웨이퍼를 인시츄로 패시베이션하기 위한 방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20180037326A true KR20180037326A (ko) | 2018-04-11 |

Family

ID=44653366

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020197020821A KR20190087668A (ko) | 2010-06-30 | 2011-06-30 | Soi 웨이퍼를 인시츄로 패시베이션하기 위한 방법 |

| KR1020187009456A KR20180037326A (ko) | 2010-06-30 | 2011-06-30 | Soi 웨이퍼를 인시츄로 패시베이션하기 위한 방법 |

| KR1020137002599A KR102083688B1 (ko) | 2010-06-30 | 2011-06-30 | Soi 웨이퍼를 인시츄로 패시베이션하기 위한 방법 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020197020821A KR20190087668A (ko) | 2010-06-30 | 2011-06-30 | Soi 웨이퍼를 인시츄로 패시베이션하기 위한 방법 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020137002599A KR102083688B1 (ko) | 2010-06-30 | 2011-06-30 | Soi 웨이퍼를 인시츄로 패시베이션하기 위한 방법 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US8859393B2 (ko) |

| EP (1) | EP2589075A2 (ko) |

| JP (1) | JP5989642B2 (ko) |

| KR (3) | KR20190087668A (ko) |

| CN (1) | CN102959697A (ko) |

| SG (1) | SG186853A1 (ko) |

| TW (1) | TW201216414A (ko) |

| WO (1) | WO2012001659A2 (ko) |

Families Citing this family (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102427097B (zh) * | 2011-11-23 | 2014-05-07 | 中国科学院物理研究所 | 一种硅的氧化钝化方法及钝化装置 |

| US8747598B2 (en) | 2012-04-25 | 2014-06-10 | Gtat Corporation | Method of forming a permanently supported lamina |

| US10079170B2 (en) | 2014-01-23 | 2018-09-18 | Globalwafers Co., Ltd. | High resistivity SOI wafers and a method of manufacturing thereof |

| US9853133B2 (en) * | 2014-09-04 | 2017-12-26 | Sunedison Semiconductor Limited (Uen201334164H) | Method of manufacturing high resistivity silicon-on-insulator substrate |

| US9899499B2 (en) | 2014-09-04 | 2018-02-20 | Sunedison Semiconductor Limited (Uen201334164H) | High resistivity silicon-on-insulator wafer manufacturing method for reducing substrate loss |

| US10381260B2 (en) | 2014-11-18 | 2019-08-13 | GlobalWafers Co., Inc. | Method of manufacturing high resistivity semiconductor-on-insulator wafers with charge trapping layers |

| WO2016081367A1 (en) | 2014-11-18 | 2016-05-26 | Sunedison Semiconductor Limited | HIGH RESISTIVITY SILICON-ON-INSULATOR SUBSTRATE COMPRISING A CHARGE TRAPPING LAYER FORMED BY He-N2 CO-IMPLANTATION |

| EP3573094B1 (en) | 2014-11-18 | 2023-01-04 | GlobalWafers Co., Ltd. | High resistivity semiconductor-on-insulator wafer and a method of manufacturing |

| CN107533953B (zh) | 2015-03-03 | 2021-05-11 | 环球晶圆股份有限公司 | 具有可控膜应力的在硅衬底上沉积电荷捕获多晶硅膜的方法 |

| US9881832B2 (en) | 2015-03-17 | 2018-01-30 | Sunedison Semiconductor Limited (Uen201334164H) | Handle substrate for use in manufacture of semiconductor-on-insulator structure and method of manufacturing thereof |

| WO2016149113A1 (en) | 2015-03-17 | 2016-09-22 | Sunedison Semiconductor Limited | Thermally stable charge trapping layer for use in manufacture of semiconductor-on-insulator structures |

| WO2016196060A1 (en) | 2015-06-01 | 2016-12-08 | Sunedison Semiconductor Limited | A method of manufacturing semiconductor-on-insulator |

| CN114496732B (zh) | 2015-06-01 | 2023-03-03 | 环球晶圆股份有限公司 | 制造绝缘体上硅锗的方法 |

| EP3378094B1 (en) | 2015-11-20 | 2021-09-15 | Globalwafers Co., Ltd. | Manufacturing method of smoothing a semiconductor surface |

| US9831115B2 (en) | 2016-02-19 | 2017-11-28 | Sunedison Semiconductor Limited (Uen201334164H) | Process flow for manufacturing semiconductor on insulator structures in parallel |

| US10468294B2 (en) | 2016-02-19 | 2019-11-05 | Globalwafers Co., Ltd. | High resistivity silicon-on-insulator substrate comprising a charge trapping layer formed on a substrate with a rough surface |

| US10622247B2 (en) | 2016-02-19 | 2020-04-14 | Globalwafers Co., Ltd. | Semiconductor on insulator structure comprising a buried high resistivity layer |

| EP3758050A1 (en) | 2016-03-07 | 2020-12-30 | GlobalWafers Co., Ltd. | Semiconductor on insulator structure comprising a low temperature flowable oxide layer and method of manufacture thereof |

| US11114332B2 (en) | 2016-03-07 | 2021-09-07 | Globalwafers Co., Ltd. | Semiconductor on insulator structure comprising a plasma nitride layer and method of manufacture thereof |

| WO2017155804A1 (en) | 2016-03-07 | 2017-09-14 | Sunedison Semiconductor Limited | Method of manufacturing a semiconductor on insulator structure by a pressurized bond treatment |

| WO2017155806A1 (en) | 2016-03-07 | 2017-09-14 | Sunedison Semiconductor Limited | Semiconductor on insulator structure comprising a plasma oxide layer and method of manufacture thereof |

| SG11201810486VA (en) | 2016-06-08 | 2018-12-28 | Globalwafers Co Ltd | High resistivity single crystal silicon ingot and wafer having improved mechanical strength |

| US10269617B2 (en) | 2016-06-22 | 2019-04-23 | Globalwafers Co., Ltd. | High resistivity silicon-on-insulator substrate comprising an isolation region |

| EP3533081B1 (en) | 2016-10-26 | 2021-04-14 | GlobalWafers Co., Ltd. | High resistivity silicon-on-insulator substrate having enhanced charge trapping efficiency |

| EP3549162B1 (en) | 2016-12-05 | 2022-02-02 | GlobalWafers Co., Ltd. | High resistivity silicon-on-insulator structure and method of manufacture thereof |

| EP3653761B1 (en) | 2016-12-28 | 2024-02-28 | Sunedison Semiconductor Limited | Silicon wafers with intrinsic gettering and gate oxide integrity yield |

| FR3061988B1 (fr) * | 2017-01-13 | 2019-11-01 | Soitec | Procede de lissage de surface d'un substrat semiconducteur sur isolant |

| EP3989272A1 (en) | 2017-07-14 | 2022-04-27 | Sunedison Semiconductor Limited | Method of manufacture of a semiconductor on insulator structure |

| US10916416B2 (en) * | 2017-11-14 | 2021-02-09 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor wafer with modified surface and fabrication method thereof |

| JP7160943B2 (ja) | 2018-04-27 | 2022-10-25 | グローバルウェーハズ カンパニー リミテッド | 半導体ドナー基板からの層移転を容易にする光アシスト板状体形成 |

| CN112262467B (zh) | 2018-06-08 | 2024-08-09 | 环球晶圆股份有限公司 | 将硅薄层移转的方法 |

| US11296277B2 (en) | 2018-10-16 | 2022-04-05 | Samsung Electronics Co., Ltd. | Variable resistance memory device having an anti-oxidation layer and a method of manufacturing the same |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3836786A (en) * | 1967-01-04 | 1974-09-17 | Purification Sciences Inc | Dielectric liquid-immersed corona generator |

| CA1030102A (en) * | 1972-08-17 | 1978-04-25 | Purification Sciences Inc. | Dielectric liquid-immersed corona generator |

| US5000113A (en) * | 1986-12-19 | 1991-03-19 | Applied Materials, Inc. | Thermal CVD/PECVD reactor and use for thermal chemical vapor deposition of silicon dioxide and in-situ multi-step planarized process |

| JPH07118522B2 (ja) * | 1990-10-24 | 1995-12-18 | インターナショナル・ビジネス・マシーンズ・コーポレイション | 基板表面を酸化処理するための方法及び半導体の構造 |

| JPH05259153A (ja) * | 1992-03-12 | 1993-10-08 | Fujitsu Ltd | シリコン酸化膜の製造方法と製造装置 |

| JPH0766195A (ja) * | 1993-06-29 | 1995-03-10 | Sumitomo Sitix Corp | シリコンウェーハの表面酸化膜形成方法 |

| CN1104264A (zh) * | 1994-09-02 | 1995-06-28 | 复旦大学 | 热壁密装低温低压淀积二氧化硅薄膜技术 |

| US5880029A (en) * | 1996-12-27 | 1999-03-09 | Motorola, Inc. | Method of passivating semiconductor devices and the passivated devices |

| US5972802A (en) * | 1997-10-07 | 1999-10-26 | Seh America, Inc. | Prevention of edge stain in silicon wafers by ozone dipping |

| JP3153162B2 (ja) * | 1997-10-08 | 2001-04-03 | 松下電子工業株式会社 | シリコン酸化膜の形成方法 |

| JP4379943B2 (ja) | 1999-04-07 | 2009-12-09 | 株式会社デンソー | 半導体基板の製造方法および半導体基板製造装置 |

| US20020175143A1 (en) * | 2001-05-22 | 2002-11-28 | Seh America, Inc. | Processes for polishing wafers |

| US6833322B2 (en) * | 2002-10-17 | 2004-12-21 | Applied Materials, Inc. | Apparatuses and methods for depositing an oxide film |

| JP4614416B2 (ja) | 2003-05-29 | 2011-01-19 | 日東電工株式会社 | 半導体チップの製造方法およびダイシング用シート貼付け装置 |

| JP2007149723A (ja) | 2005-11-24 | 2007-06-14 | Sumco Corp | 貼り合わせウェーハの製造方法 |

| US7939424B2 (en) * | 2007-09-21 | 2011-05-10 | Varian Semiconductor Equipment Associates, Inc. | Wafer bonding activated by ion implantation |

| SG161151A1 (en) | 2008-10-22 | 2010-05-27 | Semiconductor Energy Lab | Soi substrate and method for manufacturing the same |

| KR20110115570A (ko) | 2008-11-26 | 2011-10-21 | 엠이엠씨 일렉트로닉 머티리얼즈, 인크. | 절연체-상-실리콘 구조의 가공 방법 |

-

2011

- 2011-06-16 US US13/162,122 patent/US8859393B2/en active Active

- 2011-06-30 KR KR1020197020821A patent/KR20190087668A/ko not_active Application Discontinuation

- 2011-06-30 WO PCT/IB2011/052903 patent/WO2012001659A2/en active Application Filing

- 2011-06-30 SG SG2012096020A patent/SG186853A1/en unknown

- 2011-06-30 EP EP11757935.9A patent/EP2589075A2/en not_active Withdrawn

- 2011-06-30 TW TW100123193A patent/TW201216414A/zh unknown

- 2011-06-30 CN CN2011800328260A patent/CN102959697A/zh active Pending

- 2011-06-30 KR KR1020187009456A patent/KR20180037326A/ko active Application Filing

- 2011-06-30 JP JP2013517642A patent/JP5989642B2/ja active Active

- 2011-06-30 KR KR1020137002599A patent/KR102083688B1/ko active IP Right Grant

Also Published As

| Publication number | Publication date |

|---|---|

| WO2012001659A2 (en) | 2012-01-05 |

| EP2589075A2 (en) | 2013-05-08 |

| SG186853A1 (en) | 2013-02-28 |

| CN102959697A (zh) | 2013-03-06 |

| KR20130129897A (ko) | 2013-11-29 |

| KR20190087668A (ko) | 2019-07-24 |

| TW201216414A (en) | 2012-04-16 |

| US8859393B2 (en) | 2014-10-14 |

| JP5989642B2 (ja) | 2016-09-07 |

| JP2013534731A (ja) | 2013-09-05 |

| KR102083688B1 (ko) | 2020-03-02 |

| US20120003814A1 (en) | 2012-01-05 |

| WO2012001659A3 (en) | 2012-03-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102083688B1 (ko) | Soi 웨이퍼를 인시츄로 패시베이션하기 위한 방법 | |

| KR101905788B1 (ko) | 절연체-위-반도체 형 기판의 마무리 방법 | |

| JP6373354B2 (ja) | ライトポイント欠陥と表面粗さを低減するための半導体オンインシュレータウエハの製造方法 | |

| US8012855B2 (en) | Method and structure for fabricating multiple tiled regions onto a plate using a controlled cleaving process | |

| KR102658526B1 (ko) | 산화물 단결정 박막을 구비한 복합 웨이퍼의 제조 방법 | |

| US8486772B2 (en) | Method of manufacturing SOI substrate | |

| EP1194949B1 (en) | Surface finishing of soi substrates using an epi process | |

| US8088670B2 (en) | Method for manufacturing bonded substrate with sandblast treatment | |

| KR20080036209A (ko) | 스트레인드 실리콘-온-인슐레이터 구조의 제조 방법 | |

| KR101672547B1 (ko) | 샌드 블라스트 처리된 이면을 갖는 soi 기판의 제조 방법 | |

| KR20090006265A (ko) | 플라즈마 세정 방법 | |

| CA2778197A1 (en) | Method and apparatus for manufacturing silicon carbide semiconductor device | |

| KR102138949B1 (ko) | Sos 기판의 제조 방법 및 sos 기판 | |

| WO2015056386A1 (ja) | 貼り合わせウェーハの製造方法 | |

| TW202349491A (zh) | 剝除及清洗半導體結構之方法 | |

| KR20090107919A (ko) | 접합 기판의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A107 | Divisional application of patent | ||

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E601 | Decision to refuse application | ||

| A107 | Divisional application of patent |