KR20170066319A - 스트레인 수정된 표면 활성 영역을 가진 iii-질화물 나노와이어 led 및 이의 제조 방법 - Google Patents

스트레인 수정된 표면 활성 영역을 가진 iii-질화물 나노와이어 led 및 이의 제조 방법 Download PDFInfo

- Publication number

- KR20170066319A KR20170066319A KR1020177005165A KR20177005165A KR20170066319A KR 20170066319 A KR20170066319 A KR 20170066319A KR 1020177005165 A KR1020177005165 A KR 1020177005165A KR 20177005165 A KR20177005165 A KR 20177005165A KR 20170066319 A KR20170066319 A KR 20170066319A

- Authority

- KR

- South Korea

- Prior art keywords

- shell

- nanowire

- indium

- region

- lower portion

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/20—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular shape, e.g. curved or truncated substrate

- H01L33/24—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular shape, e.g. curved or truncated substrate of the light emitting region, e.g. non-planar junction

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/0004—Devices characterised by their operation

- H01L33/0008—Devices characterised by their operation having p-n or hi-lo junctions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0062—Processes for devices with an active region comprising only III-V compounds

- H01L33/0066—Processes for devices with an active region comprising only III-V compounds with a substrate not being a III-V compound

- H01L33/007—Processes for devices with an active region comprising only III-V compounds with a substrate not being a III-V compound comprising nitride compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/005—Processes

- H01L33/0062—Processes for devices with an active region comprising only III-V compounds

- H01L33/0075—Processes for devices with an active region comprising only III-V compounds comprising nitride compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/025—Physical imperfections, e.g. particular concentration or distribution of impurities

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/04—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a quantum effect structure or superlattice, e.g. tunnel junction

- H01L33/06—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a quantum effect structure or superlattice, e.g. tunnel junction within the light emitting region, e.g. quantum confinement structure or tunnel barrier

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/08—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a plurality of light emitting regions, e.g. laterally discontinuous light emitting layer or photoluminescent region integrated within the semiconductor body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/12—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a stress relaxation structure, e.g. buffer layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/16—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular crystal structure or orientation, e.g. polycrystalline, amorphous or porous

- H01L33/18—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies with a particular crystal structure or orientation, e.g. polycrystalline, amorphous or porous within the light emitting region

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/26—Materials of the light emitting region

- H01L33/30—Materials of the light emitting region containing only elements of group III and group V of the periodic system

- H01L33/32—Materials of the light emitting region containing only elements of group III and group V of the periodic system containing nitrogen

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices with at least one potential-jump barrier or surface barrier specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/40—Materials therefor

- H01L33/42—Transparent materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2933/00—Details relating to devices covered by the group H01L33/00 but not provided for in its subgroups

- H01L2933/0008—Processes

- H01L2933/0033—Processes relating to semiconductor body packages

- H01L2933/0058—Processes relating to semiconductor body packages relating to optical field-shaping elements

Abstract

코어-쉘 나노와이어 디바이스는 쉘의 상측 선단 부분에 p-평면으로부터 쉘의 하측 부분에 m-평면까지 구조적 불연속을 갖는 이브(eave) 영역을 포함한다. 이브 영역은 쉘의 p-평면 및 m-평면보다 적어도 5 원자 퍼센트 더 높은 인듐 함량을 갖는다.

Description

관련 출원

이 출원은 2014년 8월 12일자로 출원된 미국 가 출원 제62/036,363호의 우선권을 주장하며, 이 전체 내용은 본원에 참고로 포함된다.

발명의 실시예는 일반적으로 나노와이어 발광 다이오드(LED)와 같은 반도체 디바이스에 관한 것이며, 특히 불균일한 활성 영역을 갖는 나노와이어 LED에 관한 것이다.

나노와이어 발광 다이오드(LED)는 평면형 LED의 대안으로서 관심이 높아지고 있다. 종래의 평면형 기술로 생산된 LED와 비교하여, 나노와이어 LED는 나노와이어의 일차원적 특성에 기인한 고유한 특성, 격자 매칭 제약이 적음에 기인한 물질 조합의 개선된 융통성, 및 대형 기판 상에 처리할 기회를 제공한다.

전체가 본원에 참고로 인용된 2012년 3월 20일에 허여된 미국 특허 제8,138,493호는 GaN 시스템에서 종래의 평면형 기술을 사용하여 적외선 내지 녹색 파장 영역에서 발광 다이오드를 제조하는 것이 어렵고 이들은 청색 방출 LED보다 훨씬 낮은 효율을 준다는 것을 언급한다. 이것은 a) 대략 0.4<x<0.8을 갖는 InxGa1-xN이 이론적으로 안정한 물질일 것으로 기대되지 않기 때문에 적색 및 녹색 파장 영역에서 InGaN 물질에 대한 혼화성 갭; 및 b) LED 구조의 평면형 층의 내재적 고 결함 밀도는 청색 LED에 사용되는 저 In 함유 InGaN보다 훨씬 높은 정도의 고 In 함유 InGaN에 의해 광자 재결합 효율을 감소시킨다는 것에 기인할 수 있다. 제8,138,493호 특허는 개선된 방출을 갖는 적외선 내지 녹색 파장 영역에서 광 방출을 제공하는 나노와이어 코어와 나노와이어 쉘 사이에 InGaN 양자 도트를 포함하는 나노구조의 LED 디바이스를 제공함으로써 이 문제를 해결한다. 예로서, 이러한 나노구조 LED 디바이스는 GaN 기반 쉘 내에 매립된 GaN 및 InGaN 양자 도트로 만들어진 나노와이어 코어를 포함한다.

발명의 실시예는 쉘의 상측 선단 부분의 p-평면으로부터 쉘의 하측 부분의 m-평면까지 구조적 불연속을 갖는 이브 영역을 포함하는 코어-쉘 나노와이어 디바이스를 제공한다. 이브 영역은 쉘의 p-평면 및 m-평면보다 적어도 5 원자 퍼센트 더 높은 인듐 함량을 갖는다.

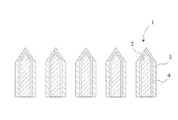

도 1은 나노와이어 LED의 기초의 측단면도를 개략적으로 도시한다.

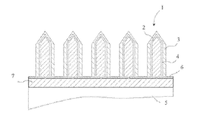

도 2는 버퍼층 상에 나노와이어 LED 구조의 측단면도를 개략적으로 도시한다.

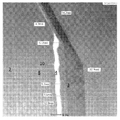

도 3a 및 도 3b는 활성 영역 쉘이 매끄럽고 균일한 방사상 표면 상에 형성되는 나노와이어 LED 디바이스의 전자 현미경 사진이다.

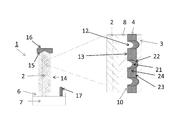

도 4는 활성 영역 쉘이 불균일한 방사상 표면 상에 형성되고 인듐 농후 영역을 내포하는 나노와이어 LED 디바이스의 측단면도를 개략적으로 도시한다.

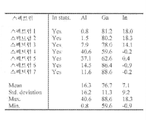

도 5a, 도 5b, 도 6b, 도 7b 및 도 8은 도 4에 도시된 나노와이어 LED 디바이스의 전자 현미경 사진이다. 도 6a 및 도 7a는 각각의 도 6b 및 도 7b에서 선택된 영역의 조성을 보여주는 표이다.

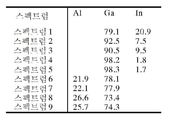

도 9a, 도 9b, 도 9c 및 도 9e는 발명의 다른 실시예에 따른 나노와이어 LED의 전자 현미경 사진이다. 도 9d는 도 9c에서 선택된 영역의 조성을 보여주는 표이다.

도 2는 버퍼층 상에 나노와이어 LED 구조의 측단면도를 개략적으로 도시한다.

도 3a 및 도 3b는 활성 영역 쉘이 매끄럽고 균일한 방사상 표면 상에 형성되는 나노와이어 LED 디바이스의 전자 현미경 사진이다.

도 4는 활성 영역 쉘이 불균일한 방사상 표면 상에 형성되고 인듐 농후 영역을 내포하는 나노와이어 LED 디바이스의 측단면도를 개략적으로 도시한다.

도 5a, 도 5b, 도 6b, 도 7b 및 도 8은 도 4에 도시된 나노와이어 LED 디바이스의 전자 현미경 사진이다. 도 6a 및 도 7a는 각각의 도 6b 및 도 7b에서 선택된 영역의 조성을 보여주는 표이다.

도 9a, 도 9b, 도 9c 및 도 9e는 발명의 다른 실시예에 따른 나노와이어 LED의 전자 현미경 사진이다. 도 9d는 도 9c에서 선택된 영역의 조성을 보여주는 표이다.

일 실시예에서, 활성 영역 쉘은 활성 영역 쉘이 불균일한 프로파일(예를 들어, 비직선 방사상 측벽 및/또는 수직 방향으로 높이의 함수로서 수평 방향으로 불균일한 두께)을 갖도록 불균일한 표면 상에 형성된다. 이 "범프성" 표면은 바깥 쉘 내 결함(예를 들면, 스택킹 결함)을 감소 또는 제거한다.

불균일한 표면 상에 하나 이상의 In(Al)GaN/(Al)GaN 양자 우물을 포함하는 활성 영역 쉘의 형성은 인듐 농후 In(Al)GaN 영역(예를 들면, 15 내지 35 원자 퍼센트 인듐과 같이 10 이상의 원자 퍼센트 인듐을 갖는 InGaN 또는 InAlGaN 영역)이 활성 영역의 형성 중에 자기 조립에 의해 형성되게 한다. 이들 인듐 농후 영역은 영역의 인듐 함량에 따라 더 긴 파장의 스펙트럼 영역(예를 들면, 녹색 내지 황색 495-590 nm 피크 방출 파장 영역 및/또는 주황색 내지 적색 591-650 nm 피크 방출 파장 영역)에서 고 밝기, 고효율 방출을 담당할 것으로 여겨진다.

그러나, 활성 영역 쉘의 부분들 사이에 개별적으로 형성되는 개별적 형성된 양자 도트와는 달리, 인듐 농후 영역은 활성 영역 쉘의 형성 동안 인시츄(in-situ)로 일체로 형성된다. 따라서, 인듐 농후 영역은 활성 영역 양자 우물 쉘 내 매립된 개별적 나노입자 또는 양자 도트가 아니라 활성 영역 양자 우물 쉘의 일체된 부분을 포함한다. 예를 들어, 개별적 나노입자는 종종, 전자 현미경 사진에서 볼 수 있는 것으로, 주위의 반도체 층과는 상이한 그레인 구조 및/또는 방위, 및 나노입자와 주변 층 그레인 사이에 급격한 천이 또는 그레인 경계를 갖는다. 대조적으로, 일체적 인듐 농후 영역은 주변 활성 영역 쉘의 주변의 인듐 빈약 영역과는 상이한 결정 방위를 반드시 갖는 것은 아니며, 급격한 천이 또는 그레인 경계를 반드시 갖는 것은 아니다.

예를 들어, 약 10 원자 퍼센트 인듐을 내포하는 InGaN 활성 영역은 청색 스펙트럼 범위에서 약 450 nm의 피크 파장을 갖는 광을 방출하고, 약 20 원자 퍼센트 인듐을 내포하는 InGaN 활성 영역은 녹색 스펙트럼 범위에서 약 520 nm의 피크 파장을 갖는 광을 방출하고, 약 30 원자 퍼센트 인듐을 내포하는 InGaN 활성 영역은 적색 스펙트럼 범위에서 약 610 nm의 피크 파장을 갖는 광을 방출한다. 물론, In(Al)GaN 활성 영역의 인듐 농도는 약 430 내지 약 650 nm, 예를 들어 450 내지 620 nm 사이의 원하는 색 방출(예를 들어, 청색, 녹색, 황색, 주황색 또는 적색)을 달성하기 위해, 5 내지 35 원자 퍼센트, 예컨대 15 내지 30 원자 퍼센트로 다양할 수 있다.

양자 우물 자체가 불균일한 두께를 갖는 한(즉, 범프성 방사상 양자 우물 쉘이다), 인듐 농후 In(Al)GaN 영역은 양자 우물 밑에 불균일한 표면을 사용함이 없이 활성 영역 양자 우물 내에 형성될 수 있음에 유의한다.

InN(a=.354 nm)과 GaN(a=.319 nm) 사이의 큰(약 10%) 격자 불일치는 결과적인 InGaN 층에 구조적 결함을 일으키지 않고 GaN 격자에 높은 농도의 인듐을 포함시키기를 어렵게 한다. 그러나, 인듐 빈약(예를 들면, 10 원자 퍼센트 이하, 예를 들어 5 내지 10 원자 퍼센트 인듐을 갖는) 활성 영역 In(Al)GaN 양자 우물, 예컨대 GaN/InGaN 코어/방사상 쉘 나노와이어의 m-평면(즉, 수직 평면)에 평행한 방사상 양자 우물에 인듐 농후 In(Al)GaN 영역을 형성함으로써, 결과적인 InGaN 활성 영역 쉘 내에 구조적 결함이 감소될 수 있다.

본 발명의 일 실시예는 In(Al)GaN 활성 영역 쉘에 나노와이어의 길이를 따라 인듐의 피착을 향상시키기 위해 m-평면을 따라 일련의 나노미터-스케일 불연속을 포함한다. 이것은 m-평면에 평행한 직선 양자 우물 표면을 유지하는 대신에 m-평면을 따라 나노미터 스케일의 피크(인듐 농후 영역을 포함하는) 및 밸리(인듐 빈약 영역을 포함하는)로 구성된 "범프성" 표면을 생성한다. 예를 들어, 이 "범프성" 표면에서 나노스케일 피처는 m-평면에 평행한 활성 영역 양자 우물의 수직 부분으로부터 적어도 부분적으로 대각 p-평면(10-11)을 따라 투사한다.

나노 기술 분야에서, 나노와이어는 일반적으로 나노-스케일 또는 나노미터 치수의 가로 크기(예를 들어, 원통형 나노와이어에 대해선 직경 또는 피라미드 또는 육각형 나노와이어에 대해선 폭)를 가지며 세로 크기는 제약되지 않는 나노구조로서 해석된다. 이러한 나노구조는 일반적으로 나노위스커, 일차원 나노-요소, 나노로드, 나노튜브, 등으로도 지칭된다. 나노와이어는 약 2 미크론까지의 직경 또는 폭을 가질 수 있다. 나노와이어의 작은 크기는 고유한 물리적, 광학적 및 전자적 특성을 제공한다. 이들 특성은 예를 들면 양자역학적 효과를 이용하는(예를 들어, 양자 와이어를 사용하는) 디바이스를 형성하거나 큰 격자 불일치로 인해 일반적으로 결합될 수 없는 조성적으로 서로 상이한 물질들의 헤테로 구조를 형성하기 위해 사용될 수 있다. 용어 "나노와이어"가 의미하는 바와 같이, 일차원 특성은 확장된 형상과 관련될 수 있다. 나노와이어는 다양한 단면 형상을 가질 수 있기 때문에, 직경은 유효 직경을 지칭하는 것으로 의도된다. 유효 직경은 구조의 단면의 장축과 단축의 평균을 의미한다.

기판이 하부에 있고 나노와이어가 기판으로부터 위쪽으로 확장하는 것을 고찰할 때 상측, 상부, 하측, 아래쪽으로, 등의 모든 언급이 행해진다. 수직은 기판에 의해 형성된 평면에 수직인 방향을 지칭하며, 수평은 기판에 의해 형성된 평면에 평행한 방향을 지칭한다. 이 명명법은 단지 이해를 쉽게 하기 위해 도입된 것으로, 특정 어셈블리 방위, 등으로 제한하는 것으로 간주되지 않아야 한다.

당업계에 공지된 임의의 적합한 나노와이어 LED 구조가 발명의 방법에 사용될 수 있다. 나노와이어 LED는 일반적으로 하나 이상의 pn- 또는 p-i-n-접합을 기반으로한다. pn 접합과 p-i-n-접합 간에 차이는 후자가 넓은 활성 영역을 갖는다는 것이다. 더 넓은 활성 영역은 i-영역에서 더 높은 재결합 확률이 되게 한다. 각각의 나노와이어는 동작시 광 발생을 위한 활성 영역을 제공하는 pn 또는 pin 접합을 형성하기 위해 제1 도전성 유형(예를 들어, n-형) 나노와이어 코어 및 둘러싸는 제2 도전성 유형(예를 들어, p-유형) 쉘을 포함한다. 코어의 제1 도전성 유형은 본원에서 n-형 반도체 코어로서 기술되고 제2 도전성 유형 쉘은 본원에서 p-형 반도체 쉘로서 기술되지만, 이들의 도전성 유형들은 역전될 수 있음을 이해해야 한다.

도 1은 발명의 실시예에 따라 수정된 나노와이어 LED 구조에 대한 기초를 개략적으로 도시한 것이다. 원칙적으로, 나노와이어 LED를 형성하기 위해서는 하나의 단일 나노와이어로 충분하지만, 작은 크기에 기인하여, 나노와이어들은 LED 구조를 형성하기 위해 나란히 수백, 수천, 수만 또는 그 이상의 나노와이어를 포함하는 어레이들로 배열되는 것이 바람직하다. 예시적 목적을 위해, 개개의 나노와이어 LED 디바이스는 n-형 나노와이어 코어(2)와 나노와이어 코어(2)를 적어도 부분적으로 둘러싸는 p-형 쉘(3), 및 단일 진성 혹은 저농도 도핑된(예를 들면, 1016cm-3 미만의 도핑 레벨) 반도체층 또는 상이한 밴드 갭의 복수의 반도체층을 포함하는 3 내지 10 양자 우물과 같은 하나 이상의 양자 우물을 포함할 수 있는 중간 활성 영역(4)을 갖는 나노와이어 LED(1)로부터 구성되는 것으로서 본원에서 기술될 것이다. 그러나, 발명의 실시예에서, 나노와이어 LED는 이것으로 제한되지 않는다. 예를 들어, 나노와이어 코어(2), 활성 영역(4), 및 p-형 쉘(3)은 다수의 층 또는 세그먼트로부터 구성될 수 있다. 대안적 실시예에서, 코어(2)만이 2 마이크론 미만의 폭 또는 직경을 갖는 나노구조 또는 나노와이어를 포함할 수 있고, 반면에 쉘(3)은 1 마이크론 이상의 폭 또는 직경을 가질 수 있다.

III-V 반도체는 고속 및 저전력 전자장치, 및 레이저 및 LED와 같은 광전자 디바이스를 용이하게 하는 특성으로 인해 특히 중요하다. 나노와이어는 임의의 반도체 물질을 포함할 수 있고, 나노와이어에 적합한 물질은 GaAs(p), InAs, Ge, ZnO, InN, GaInN, GaNAlGaInN, BN, InP, InAsP, GaInP, InGaP:Si, InGaP:Zn, GaInAs, AlInP, GaAlInP, GaAlInAsP, GaInSb, InSb, Si를 포함하는데, 그러나 이들로 제한되지 않는다. 예를 들어 GaP을 위한 가능한 도너 도펀트는 Si, Sn, Te, Se, S, 등이며, 동일 물질을 위한 어셉터 도펀트는 Zn, Fe, Mg, Be, Cd, 등이다. 나노와이어 기술은 종래 기술로 쉽게 접근할 수 없는 파장 영역의 광을 방출하는 LED의 제조를 용이하게 하는 GaN, InN 및 AlN과 같은 질화물을 사용하는 것을 가능하게 함에 유의한다. 상업적으로 특히 중요한 그외 다른 조합은 GaAs, GaInP, GaAIInP, GaP 시스템을 포함하지만 이에 한정되지 않는다. 일반적인 도핑 레벨은 1018 내지 1020cm-3의 범위이다. 그렇지만 당업자는 이들 및 다른 물질에 익숙하며 다른 물질 및 물질 조합이 가능하다는 것을 인식한다.

나노와이어 LED에 바람직한 물질은 III-질화물 반도체(예를 들어, GaN, AlInGaN, AlGaN 및 InGaN, 등) 또는 다른 반도체(예를 들어, InP, GaAs)와 같은 III-V 반도체이다. LED로서 기능하기 위해, 각각의 나노와이어 LED(1)의 n-측 및 p-측은 접촉되어야 하고, 본 발명은 LED 구조에 나노와이어의 n-측 및 p-측을 접촉시키는 것에 관계된 방법 및 조성을 제공한다.

본원에 기술된 예시적 제조 방법은 바람직하게는 나노와이어 제조 방법의 교시를 위해 본원에 참조로 포함되는 Seifert 등의 미국 특허 제7,829,443호에 개시된 바와 같이 코어-쉘 나노와이어를 형성하기 위해 코어 위에 반도체 쉘 층을 성장시키기 위해 나노와이어 코어를 사용하는데, 본 발명은 이로 제한되지 않는다는 것에 유의한다.

예를 들어, 대안적인 실시예에서, 코어만이 나노구조(예를 들어, 나노와이어)를 구성할 수 있는 반면, 쉘은 선택적으로 전형적인 나노와이어 쉘보다 큰 치수를 가질 수 있다. 또한, 디바이스는 다수의 패싯을 포함하도록 형상화될 수 있으며, 상이한 유형의 패싯들의 면적비는 제어될 수 있다. 이것은 "피라미드" 패싯 및 수직 측벽 패싯에 의해 예증된다. LED는 지배적 피라미드 패싯 또는 측벽 패싯을 갖는 템플릿 상에 방출층이 형성되도록 제조될 수 있다. 이는 방출층의 형상에 관계없이 접촉층에 대해서도 마찬가지이다.

도 2는 나노와이어에 대한 지지체를 제공하는 예시적인 구조를 도시한다. 위치를 정의하고, 나노와이어의 하부 계면 영역을 결정하기 위해 선택적으로 성장 마스크 또는 유전체 마스크 층(6)(실리콘 질화물 유전체 마스크 층과 같은, 질화물 층)을 사용하여, 성장 기판(5) 상에 나노와이어를 성장시킴으로써, 기판(5)은 적어도 처리 동안 기판(5)으로부터 돌출하는 나노와이어를 위한 캐리어로서 기능한다. 나노와이어의 하부 인터페이스 영역은 유전체 마스크 층(6) 내 각 개구 내부에 코어(2)의 루트 영역을 포함한다. 기판(5)은 스웨덴 특허 출원 SE 1050700-2(GLO AB에 양도 됨)에서 논의된 바와 같이 III-V 또는 II-VI 반도체, Si, Ge, Al2O3, SiC, 석영, 유리, 등과 같은 상이한 물질들을 포함할 수 있다. 기판을 위한 그외 다른 적합한 물질은 GaAs, GaP, GaP:Zn, GaAs, InAs, InP, GaN, GaSb, ZnO, InSb, SOI(silicon-on-insulator), CdS, ZnSe, CdTe을 포함하지만, 이에 한정되지 않는다. 일 실시예에서, 나노와이어 코어(2)는 성장 기판(5) 상에 직접 성장된다.

바람직하게는, 기판(5)은 또한 각 나노와이어 LED(1)의 n-측에 연결하는 전류 수송층으로서 기능하도록 적응된다. 이는, 도 2에 도시된 바와 같이, 나노와이어 LED(1)에 면하여 기판 표면 상에 배열된 반도체 버퍼층(7), 예로서 Si 기판(5) 상에 GaN 및/또는 AlGaN 버퍼층(7)과 같은 III-질화물층을 포함하는 기판(5)을 갖게 함으로써 달성될 수 있다. 버퍼층(7)은 일반적으로 원하는 나노 와이어 물질에 매칭되고, 따라서 제조 프로세스에서 성장 템플릿으로서 기능한다. n-형 코어(2)에 있어서, 버퍼층(7)은 바람직하게 n-형으로 도핑된다. 버퍼층(7)은 단일 층(예컨대, GaN), 몇개의 서브-층(예컨대, GaN 및 AlGaN), 또는 고 Al 함유 AlGaN부터 저 Al 함유 AlGaN 또는 GaN까지 그레이드되는 그레이드된 층을 포함할 수 있다.

제7,829,443호 특허에 기술된 방법은 지지체(예를 들어, 버퍼층(7)) 상에 성장 마스크(6)를 제공하는 것을 포함한다. 이어서 버퍼층을 노출시키기 위해 성장 마스크(6) 내에 개구가 형성된다. 개구는 바람직하게는 이들의 직경 및 이들의 상대적 위치설정 둘 다에 대해 잘 제어된다. 전자 빔 리소그래피(EBL), 나노임프린트 리소그래피, 광학 리소그래피 및 반응성 이온 에칭(RIE) 또는 습식 화학 에칭 방법을 포함하지만 이에 제한되지 않는 절차에 대해 당업계에 공지된 여러 기술이 사용될 수 있다. 바람직하게는, 개구는 직경이 약 75-125nm, 이를테면 약 100nm이고 0.5-5㎛ 이격하여 피치된다. 개구는 생성될 나노와이어 코어(2)의 위치 및 직경을 정의한다.

이어, 나노와이어 코어(2)는 프리커서 소스 흐름이 연속적인 CVD 기반 프로세스에 의해 성장된다. 프리커서 소스 유속은 성장 구역에서 낮은 과포화를 달성하도록 조정된다. V/III 비는 100 이하, 예를 들면 1 내지 100, 바람직하게는 1 내지 50, 더욱 바람직하게는 5 내지 50이어야 한다. 이 V/III 비는 벌크 막 성장에 사용된 비보다 상당히 낮음을 유의해야 한다. 즉, 나노와이어 코어(2)는 비교적 낮은 온도(예를 들어, 800℃ 미만)에서 낮은 V/III 비로 성장된다.

이어, 도 1 및 도 2에 도시된 하나 이상의 쉘(3, 4)은 900℃ 내지 1200℃와 같은 800℃ 이상의 온도를 증가시키고 V/III 비를 코어(2) 성장을 위해 사용된 것보다 더 큰 량으로(예를 들어, 100보다 높은, 예를 들어 200-1000의 V/III 비) 증가시킴으로써 코어(2) 상에 성장된다. 예를 들어, n-GaN 나노와이어 코어(2)는 암모니아 및 TMG(트리메틸갈륨) 가스 소스 및 선택적인 도핑 소스 가스(예를 들어, Mg 함유 소스 가스)를 사용하여 MOCVD에 의해 성장될 수 있다. NH3 유속은 코어(2) 성장 동안 0.2 내지 3.0 sccm이고, 쉘(3, 4) 성장 동안 50 내지 100 sccm일 수 있다. TMG(트리메틸갈륨) 유속은 0.12 내지 1.2 μmol/min 일 수 있다.

요망된다면, 활성 영역 쉘(4)을 형성하기 전에 중간 n-GaN 쉘(8)이 n-GaN 코어(2) 상에 형성될 수 있다. n-GaN 쉘(8)은 고온(800℃ 이상, 이를테면 900-1200℃) 및 200-1000와 같은 100보다 큰 높은 V/III 비에서 형성될 수 있다. 이 쉘(8)은 도 3a 및 도 3b에 도시되어 있으며 매끄러운(즉, 직선) 바깥 측벽(즉, m-평면 방사상 측벽)을 갖는다.

일 실시예에서, 양자 우물 활성 영역 쉘(4)이 중간 n-GaN 쉘(8)의 매끄러운 방사상 표면 상에 형성될 때, 도 3a 및 도 3b에 도시된 바와 같이, 활성 영역 쉘(4)을 둘러싸는 바깥 쉘(3)(예를 들어, p-형 GaN 및/또는 AlGaN 쉘) 내에 수평 스택킹 결함(9)으로 생각되는 다수의 결함이 형성된다.

따라서, 도 4에 도시된 일 실시예에서, 활성 영역 쉘은 활성 영역 쉘(4)이 불균일한 프로파일 및 국소화된 인듐 농후 In(Al)GaN 영역(21)을 갖도록 불균일한(예를 들어, "범프성") 표면 상에 형성된다. "범프성" 표면은, 이를테면 중간 쉘 내, 또는 활성 영역 양자 우물 쉘(4) 밑에 장벽 층 내와 같은, 활성 영역 양자 우물 쉘(4) 밑에(예를 들어, 이로부터 안쪽으로 방사상으로) 하지층(8) 내에서 개시될 수 있다. 이것은 스트레인 수정된 표면 활성 영역 쉘(4)을 형성한다. 바람직하게, 하지층(8)은 양자 우물 방출을 흡수하는 것을 피하기 위해서 활성 영역 양자 우물(4)보다 낮은 인듐 함량을 갖는다(즉, 하지층(8)은 활성 영역 양자 우물(4)보다 넓은 밴드 갭을 갖는다). 예를 들어, 하지층(8)은 인듐을 갖지 않을 수도 있고(예를 들어, GaN 또는 AlGaN으로 구성된다), 또는 10 미만의 원자 퍼센트 인듐, 예컨대 1 내지 5 원자 퍼센트 인듐을 갖는 InGaN 또는 InAlGaN 하지층을 포함할 수 있다.

하지층(8)의 범프성을 제어함으로써, 결함을 도입하지 않고 더 균질한 고 인듐 함유 활성 양자 우물 층(4)이 후속하여 성장될 수 있다. 하지층(8)의 범프성 정도는 온도, MOCVD 압력, MOCVD 반응물 유속 및/또는 하지층의 In/Ga 비과 같은 성장 조건에 의해 제어될 수 있다. 예를 들어, 범프성 정도는 인듐 함량을 증가시키고 성장 온도가 낮을수록 증가한다.

하지층(8)의 범프성 및 성장 조건은 균질 내지 저 인듐 함량의 In(Al)GaN 양자 우물에 매립된 개별적 인듐 농후 영역의 생성까지 양자 우물 활성 영역(4)의 조성을 제어할 수 있다. 양자 우물의 두께는 아래에서 설명하는 피크-밸리 높이와 유사하거나 미만이 될 것이다.

단일 양자 웰 활성 영역(4)이 도 4에 도시되어 있지만, 다수의 양자 우물 활성 영역(4)이 또한 형성될 수 있다. 범프성 양자 우물(4)을 범프성 GaN 또는 저 In 함유 InGaN 또는 InAlGaN 장벽층으로 분리하는 것은, 결함량이 감소되고 각 양자 웰이 국소화된 인듐 농후 영역들(21)을 갖는 나노와이어의 바깥 쉘(8) 상의 다수의 양자 우물 활성 영역(4) 구조의 성장을 제공한다.

예를 들어, 하지층(8) 및/또는 활성 영역 쉘(4) 내의 불균일한 표면 또는 프로파일은 피크(12)와 인접 밸리(13) 간에 10 내지 30 nm의 분리와 피크(12)와 인접 밸리(13) 간에 3 내지 5 nm의 깊이(즉, 두께 변동)을 가질 수 있다. 바람직하게, 활성층 영역 쉘(4)은 스택킹 결함을 야기하는 것을 피하기 위해 5nm보다 큰 두께를 갖는다. 하지층(8)이 15%보다 많은 인듐을 갖는다면, 이것은 또한 바람직하게 스택킹 결함을 야기하는 것을 피하기 위해 5nm보다 큰 두께를 갖는다.

본원에서 사용된 바와 같이, 불균일한 표면은 수평 방향을 따른 방사상(즉, m-평면) 표면 내에 적어도 하나의 밸리(예를 들어, 리세스)(13)로부터 적어도 2 nm, 예컨대 3 내지 5nm를 확장하는 적어도 3개의 피크(예를 들어, 돌출(bulge))(12)를 갖는, 비직선 또는 매끄럽지 않은(즉, 범프성 또는 거친) 표면을 의미한다. 불균일한 프로파일은 활성 영역 쉘 내의 양자 우물이 비-직선 방사상 표면(즉, 측벽) 및/또는 수직 방향으로 높이의 함수로서 방사상(즉, 수평) 방향을 따라 불균일한 두께를 갖는다는 것을 의미한다. 불균일한 두께는 활성 영역 쉘(예를 들어, 양자 우물)(4)의 방사상(즉, 수평 방향) 두께가 쉘(4) 내의 상이한 수직 위치들에서 20-40%와 같이 적어도 15%만큼 다르며 대략 평행하지 않은 방사상 측벽을 갖는 것을 의미한다.

5nm 이상으로 In 함유 범프성 층(예를 들어, 활성 영역 쉘)의 막 두께를 증가시키는 것은 밸리(13)과 비해 피크(12)에 인듐을 불균형하게 피착하고 하지층(8) 내 피크(12) 위에 활성 영역 쉘(4) 내에 국소화된 인듐 농후 In(Al)GaN 영역(21)을 형성할 것이다. 도 4에 도시된 바와 같이, 활성 영역 쉘(4) 내 인듐 농후 영역(21)은 활성 영역 쉘(4) 내 피크(22)에 대응하고, 인듐 농후 영역(21)은 활성 영역 쉘(4) 내 밸리(23)에 대응하는 인듐 빈약 영역(24)에 의해 분리된다. 바람직하게, 쉘(4) 내에 인듐 농후 영역과 인듐 빈약 영역 사이의 인듐 함량의 차이는 적어도 5 원자 퍼센트, 예를 들어 10 내지 25 원자 퍼센트이다.

이것은 전기적 접촉이 나노와이어의 m-평면(14) 상에 직접 놓여지면 다수의 방출 피크를 야기할 수 있는 비균질 활성층(4)을 갖게 한다. 도 4에 도시된 바와 같이, 바람직하게, p-형 GaN 쉘(3)에의 p-측 GaN 전기적 접촉(16)은 쉘(3)의 선단에서 경사진 p-평면(15) 상에 만들어지고, n-형 GaN 또는 AlGaN 기판(7)을 통해 n-형 GaN 나노와이어 코어(2)의 c-평면에 n-측 전기적 접촉(17)이 만들어진다. 따라서, m-평면(14)으로부터 오는 낮은 방출 피크는 EL 스펙트럼에서 보이지 않는다. 따라서, 더 긴 파장의 녹색, 황색, 주황색 또는 적색 광을 방출하는 고 In 함유 물질(즉, 영역(21))의 볼륨은 유해한 스택킹 결함을 도입하지 않고 증가할 수 있다.

예를 들어, 도 5a 및 도 5b에 도시된 바와 같이, 불균일 표면은 높은 V/III 비를 유지하면서 저온(예를 들어, 800℃ 이하)에서 중간 쉘(8)을 형성함으로써 달성될 수 있다. 이것은 중간 쉘(8)의 바깥 방사상 표면(10)을 불균일해지게 한다. 이어, 활성 영역 쉘(4) 및 바깥 p-형 쉘(들)(3)은 중간 쉘(8) 위에 형성된다. 도 5a 및 도 5b에서 알 수 있는 바와 같이, 불균일 표면 상에 이러한 성장은 불균일한 프로파일을 가진 활성 영역 쉘(4)을 생성하고 바깥 쉘(들)(3) 내 결함(예를 들어, 스택킹 결함)(9)을 감소 또는 제거한다.

도 5a 및 도 5b에 도시된 바와 같이, 활성 영역 쉘(4)은 불균일한 두께를 갖는다. 예를 들어, 양자 우물 함유 셀(4)은 위치 #5에서 7.6 nm 내지 위치 #3에서 12.2 nm까지의 범위의 두께를 갖는다. 따라서, 쉘(4) 방사상 두께는 수직 방향을 따라 30% 이상(즉, 30-38 %) 및 4nm 이상만큼 변화한다.

불균일한 표면(10) 상에 하나 이상의 InGaN/GaN 양자 우물을 포함하는 불균일한 프로파일을 갖는 활성 영역 쉘(4)의 형성은 활성 영역 쉘의 형성 중에 자기 조립에 의해 국소적인 인듐 농후 InGaN 영역(21)이 형성되게 한다. 구체적으로, 영역(21)은 활성 영역 쉘(4)의 더 두꺼운(즉, 돌출한) 영역에 형성되는 것으로 생각된다. 도 6a 및 도 7a는 각각의 도 6b 및 도 7b에 도시된 나노와이어 LED의 다양한 위치에 있는 원자 퍼센트로 Al, Ga 및 In 함량을 보여주는 표를 도시한다. 도 6a 및 도 6b에 도시된 바와 같이, InGaN/GaN 양자 우물 활성 영역들(4)에 영역 #1, 2, 3 및 7은 17.5 내지 23.9 원자 퍼센트 인듐과 같은(즉, 각각 20.5, 17.5, 19.9 및 23.9) 15 이상의 원자 퍼센트 인듐을 함유한다. 따라서, 인듐 농도는 영역 # 2와 영역 7 사이에서 5 원자 퍼센트 이상(예를 들어, 5 내지 6.4 원자 퍼센트) 만큼 변화한다. 영역 #4-6은 AlGaN 바깥 쉘(들) 내에 위치되고 인듐 및 가변 농도 알루미늄이 없다.

도 7a 및 도 7b에 도시된 바와 같이, InGaN/GaN 양자 우물 활성 영역(4)의 영역 #1, 2 및 3은 14 이상의 원자 퍼센트 인듐, 예를 들어 14.1 내지 18.3 원자 퍼센트 인듐(즉, 각각 18.0, 18.3 및 14.1)를 함유한다. 따라서, 인듐 농도는 영역 #2와 3 사이에서 4 원자 퍼센트 이상만큼 변한다. 영역 # 4-7은 AlGaN 바깥 쉘(들)에 위치되고 인듐 및 가변 농도의 알루미늄을 갖지 않는다.

이들 인듐 농후 영역(21)은 녹색 내지 황색 파장 스펙트럼 영역에서 고 밝기, 고효율 방출을 담당하는 것으로 여겨진다.

또한, 불균일 표면(10) 상에 활성 영역 쉘(4)을 형성하는 것은 중간 쉘(8)의 피라미드형의 기울어진 상측 표면(즉, 반-극성 {1-101} p-평면)보다 방사상 표면(즉, 비-극성 {10-10} m-평면) 상에 활성 영역(4)의 두께가 훨씬 더 두꺼워지게 한다. 중간 쉘(8)의 m-평면에 걸친 활성 영역 쉘(4)의 방사상 두께는 디바이스의 상부에서 중간 쉘(8)의 p-평면, 10-11, 에 걸친 두께보다 적어도 3배, 예를 들어 3-10배 더 두껍다. 이것은 InGaN 양자 우물의 m-평면 부분으로부터의 방출이 동일 양자 우물의 p-평면, 10-11, 부분들로부터의 방출과 비교하여 개선되기 때문에 LED 디바이스 성능을 향상시킨다. 따라서, 양자 우물의 m-평면 두께가 이들의 p-평면, 10-11, 두께와 비교하여 증가는 양자 우물의 보다 두꺼운 p-평면, 10-11, 부분들을 갖는 종래 기술의 디바이스에서보다 양자 우물의 p-평면, 10-11, 부분보다 m-평면 부분으로부터 더 높은 비의 방사선이 방출됨을 의미한다.

도 8은 발명의 대안적 실시예를 도시한다. 이 실시예에서, 디바이스는 3개의 중간 쉘(8A, 8B, 8C)을 포함한다. 내부 중간 쉘(8A)은 n-GaN 쉘을 포함한다. 중간 쉘(8B)은 불균일한 표면을 갖는 n-InGaN 쉘을 포함하고, 바깥 쉘(8C)은 불균일한 표면을 갖는 n-GaN 쉘을 포함한다. 쉘(8B, 8C) 모두는 바깥 중간 쉘(8) 상의 활성 영역 쉘(4)의 성장을 위한 불균일한 표면을 형성하기 위해 고 V/III 흐름 비 및 낮은 온도(예를 들어, 800℃ 미만)로 형성될 수 있다.

도 8에 도시된 바와 같이, 활성 영역 쉘(4)은 불균일한 두께를 갖는다. 예를 들어, 양자 우물 함유 쉘(4)은 위치 #4에서 6.8nm 내지 위치 #3에서 12.5nm의 범위 인 두께를 갖는다. 따라서, 쉘(4) 방사상 두께는 40% 이상(즉, 40-45.6 %) 및 5nm 이상(예를 들어, 5 내지 5.7㎚) 만큼 변화한다.

도 9a, 도 9b, 도 9c 및 도 9e에 도시된 다른 실시예에서, LED 디바이스와 같은 코어-쉘 나노와이어 디바이스는 이브(eave) 영역(31)을 포함한다. 즉, m-평면 부분(34)과 p-평면 부분(32)이 결합하는 나노와이어 쉘(4)의 코너는 "이브" 또는 이브 영역(31)이라 지칭된다. 영역(31)은 쉘(4)의 상측 선단 부분의 p-평면 부분(32)으로부터 쉘(4)의 하측 부분에 m-평면 부분(34)에 구조적인 불연속을 포함한다. 이브 영역은 쉘(4)의 p- 평면(32) 및 m-평면(34) 부분보다 적어도 5 원자 % 더 높은 인듐 함량을 갖는다. 바람직하게, 이브 영역(31)은 In(Al)GaN 활성 영역 양자 우물 쉘(4) 내에 인듐 농후 In(Al)GaN 영역이다.

따라서, 도 9a-도 9c 및 도 9e에 도시된 바와 같이, LED 디바이스와 같은 나노와이어 디바이스는 경사진 p-평면 측벽을 갖는 상측 선단 부분과 실질적으로 수직인 m-평면 측벽을 갖는 III-질화물 반도체 나노와이어 코어(2), 및 반도체 나노와이어 코어(2) 주위에 방사상으로 위치된 인듐 함유 III-질화물 반도체 쉘(예를 들어, 활성 영역 양자 우물 쉘(4))을 포함한다. 쉘(4)은 나노와이어 코어의 상측 선단 부분 상에 위치한 경사진 p-평면 측벽(32)을 갖는 상측 선단 부분, 및 나노와이어 코어(2)의 하측 부분 상에 위치되는 실질적으로 수직인 m-평면 측벽(34)을 갖는 하측 부분을 포함한다. 쉘(4)은 또한 쉘(4)의 상측 선단 부분(32)에 p-평면으로부터 쉘(4)의 하측 부분(34)에 m-평면까지 구조적 불연속을 포함하는 이브 영역(31)을 내포한다. 디바이스는 또한 쉘(3, 8, 8A, 8B, 8C 및/또는 9)와 같은 위에 설명된 추가 쉘을 포함할 수 있다.

쉘(4)의 상측 선단 부분(32)은 나노와이어 코어(2)의 상측 선단 부분의 전체 주변을 둘러싸는 링 형상 영역을 포함한다. 쉘(4)의 하측 부분(34)은 나노와이어 코어(2)의 하측 부분의 전체 주변을 둘러싸는 링 형상 영역을 포함한다. 이브 영역(31)은 나노 와이어 코어(2)의 상측 선단 부분과 하측 부분 사이에 나노 와이어 코어의 중간 부분의 전체 주변을 둘러싸는 링 형상 영역을 포함한다. 따라서, 바람직하게, 이브 영역(31)은 쉘(4)의 p-평면(32) 및 m-평면(34) 부분과 비교하여 실질적으로 일정하고 상승된 인듐 조성의 링을 형성하기 위해 나노와이어의 원주(예를 들어, 활성 영역 쉘(4)의 원주) 둘레로 확장한다. Ⅲ-질화물 나노와이어는 일반적으로 수평 방향으로 6각형의 단면 형상을 가지기 때문에, 링은 위에서 보았을 때 실질적으로 6각형의 단면 형상을 가질 것이다. 녹색(520nm) 및 적색(600nm) LED에 대해 보다 긴 파장의 디바이스를 가능하게 하기 위해 보다 높은 인듐 조성 합금(예를 들면, In(Al)GaN)이 이브 영역(31)에 우선적으로 피착될 수 있다.

이브 영역(31)은 경사진 p-평면 측벽(32)을 갖는 쉘(4)의 상측 선단 부분 및 실질적으로 수직인 m-평면 측벽(34)을 갖는 쉘의 하측 부분보다 적어도 5 원자 퍼센트, 예컨대 10 원자 퍼센트, 예를 들면 10 내지 30 원자 퍼센트 더 높은 인듐 함량을 갖는다. 예를 들어, 이브 영역(31)은 15-30 원자 퍼센트 인듐을 함유할 수 있고, 쉘(4)의 상측 선단 부분(32) 및 쉘의 하측 부분(34)은 15 원자 퍼센트 인듐 이하, 예를 들어 1 내지 9 원자 퍼센트 인듐을 함유할 수 있다.

In 농후 이브 영역(31)을 내포하는 LED 디바이스는 495 내지 590nm 피크 방출 파장 또는 591 내지 650nm 피크 방출 파장과 같은 적색, 주황색, 황색, 또는 녹색 피크 방출 파장을 가질 수 있다. 피크 방출 파장 영역이 길어질수록, 이브 영역(31)의 인듐 함량은 더 높다. 예를 들어, 인듐 함량은 495 내지 590nm의 피크 방출 파장 범위를 갖는 LED에서 15 내지 22 원자 퍼센트이고, 591 내지 650 nm 피크 방출 파장 범위를 갖는 LED에서 23 내지 30 원자 퍼센트일 수 있다. 예를 들어, LED가 약 520nm의 피크 방출 파장을 가질 때, 이브 영역(31)은 약 20 원자 퍼센트 인듐을 함유할 수 있고, LED가 약 610nm의 피크 방출 파장을 가질 때, 이브 영역(31)은 약 30 원자 퍼센트 인듐을 함유할 수 있다.

특정 이론에 구속되기를 바라지 않고, 본 발명자는 인듐 농후 In(Al) GaN 이브 영역(31)이 쉘(4)의 p-평면과 m-평면 부분 사이의 구조적인 불연속에서 형성된다고 생각한다. 불연속은 In-N 본드가 완화되어 m-평면 부분(34)보다 높은 확률로 인듐을 포함시키는 저 에너지 표면을 생성한다. In-N 본드는 이용가능한 자유 표면이 있을 때 GaN에 보다 용이하게 포함시키는 것으로 나타났다. 따라서, 활성 영역 쉘(4)의 형성 동안 자체 조립에 의해 인듐 농후 이브 영역(31)이 형성된다.

앞에 실시예에서 기술된 바와 같이, 활성 영역 쉘(4)이 불균일한 표면(10) 상에 형성된다면, 쉘(4)은 m-평면 부분(34)에 국소적인 인듐 농후 In(Al)GaN 영역들(21)에 추가하여 인듐 농후 이브 영역(31)을 포함할 수 있다. 대안적으로, 쉘(4)이 균일한 표면 상에 형성된다면, 쉘(4)은 인듐 농후 이브(31) 영역만을 포함하지만 인듐 농후 영역(21)은 포함하지 않을 수 있다.

이브 영역(31)과 쉘(4)의 m-평면 부분(34) 사이의 인듐 조성의 차이는 MOCVD에 의한 쉘(4)의 피착 동안의 성장 온도, TMIn/TMGa 흐름 비, 및/또는 MOCVD에 의한 쉘(4)의 피착 동안 암모니아 흐름에 의해 제어될 수 있다. 온도를 감소시키는 것은 m-평면 부분(34)에 비해 이브 영역(31)의 인듐 함량을 증가시키는 가장 직접적인 방법이다. 온도 효과는 낮은 성장 속도에서 강화되는데, 성장 속도는 쉘(4)의 MOCVD 동안 TMIn + TMGa/NH3에 의해 제어된다. 성장 속도는 이브의 높은 표면 에너지로 인해 m-평면 부분(34) 두께(t2)에 비해 이브 영역(31) 두께(t1)를 증가시킬 수 있다. 예를 들어, t1은 t2보다 1.1 내지 1.5배 더 클 수 있다. InGaN 쉘(4) 두께를 증가시키는 것은 이브 영역(31)에 인듐 함량을 1.5 내지 5배만큼 증가시킨다.

예를 들어, 이브 영역(31)은 쉘(4)의 m-평면 부분(34)보다 20 내지 35 퍼센트 두꺼운 것을 포함하여, 적어도 20 퍼센트 더 두꺼운 것과 같이 적어도 10 퍼센트 더 두꺼울 수 있다. p-평면 부분(32)은 이브 영역(31) 및 m-평면 부분(34) 둘 다보다 일반적으로 더 얇다. 높은 인듐 함량 이브 영역(31)으로부터의 방출은 LED에 인가된 전류의 함수로서 지배적이라고 여겨진다. 예를 들어, 이브 영역(31)은 12 내지 20nm 두께일 수 있는 반면 쉘(4)의 m-평면 부분(34)은 7 내지 11 nm 두께일 수 있다. 쉘(4)의 p-평면 부분(32)은 0.4 내지 2nm 두께일 수 있다.

도 9a 및 도 9b는 활성 영역 쉘(4)에 인듐 농후 이브 영역(31)을 내포하는 예시적 LED 디바이스를 도시한다. 도 9a의 디바이스는 하나의 중간 n-GaN 쉘(8)을 내포함는 반면 도 9b의 디바이스는 3개의 중간 쉘(8A, 8B, 8C) 를 내포한다.

도 9a에 도시된 바와 같이, 이브 영역(31)의 두께(t1)는 약 13nm이고 쉘(4) m-평면 부분(34) 두께는 약 10nm이다. 이브 영역(31)은 약 10 원자 퍼센트 인듐을 함유하고, m-평면 부분(34)은 약 3 원자 퍼센트 인듐을 함유한다.

유사하게, 도 9b에 도시된 바와 같이, 이브 영역(31) 두께(t1)는 약 15nm이고, 쉘(4)의 m-평면 부분(34) 두께는 7 내지 11nm 범위이다. 이브 영역(31)은 약 25 원자 퍼센트 인듐을 함유하고, m-평면 부분(34)은 약 15 원자 퍼센트 인듐을 함유한다. 따라서, 이브 영역(31)의 두께는 도 9a 및 도 9b의 디바이스에서 m-평면 부분(34)의 두께보다 약 30% 더 크다.

도 9c는 활성 영역 쉘(4)에 인듐 농후 이브 영역(31)을 내포하는 또 다른 예시적 LED 디바이스를 도시한다. 도 9c의 InGaN 이브 영역(31)(도 9d의 표에서 스펙트럼 1로 표기됨)은 20.9 원자 퍼센트 인듐을 함유하고, InGaN m-평면 부분(34)(도 9d의 표에서 스펙트럼 2 및 3으로 표기됨)은 7.5 내지 9.5 원자 퍼센트 인듐을 함유한다. 중간 InGaN 쉘(8)은 1.7 내지 1.8 원자 퍼센트 인듐을 함유한다(도 9d의 표에서 스펙트럼 4 및 5). 스펙트럼 6 - 스펙트럼 9는 바깥 AlGaN 쉘(9)에서 취해진다. p-평면 부분(32)에서의 양자 우물 쉘(4)의 두께는 0.5nm 미만이고 m-평면 부분(34)에서 약 8nm이다.

보다 긴 파장(예를 들어, 녹색 및 보다 긴 피크 파장)에서 고효율 디바이스는 이브 영역의 활성 영역 볼륨을 증가시킴으로써 달성될 수 있다. 이것은 나노와이어 피치를 감소시킴으로써 기판 상의 나노와이어 직경 및/또는 나노와이어 밀도를 증가시킴으로써 행해질 수 있다.

이브 영역(31)의 수를 증가시키는 것은 나노와이어 내에 다수의 양자 우물 활성 영역(4)을 성장시킴으로써 달성될 수 있다. 예를 들어, 도 9e에 도시된 바와 같이, LED 디바이스는 2개의 양자 우물 활성 영역 쉘(4A, 4B)을 포함하며, 각각은 각각의 이브 영역(31A, 31B)을 포함한다. 쉘(4A, 4B)은 쉘(4A, 4B)보다 낮은 인듐 함량을 갖는 p-형 AlGaN 또는 GaN 쉘 또는 In(Al)GaN 쉘에 의한 중간 쉘(33)에 의해 분리된다.

본 발명이 나노와이어 LED에 관하여 기술되었지만, 전계 효과 트랜지스터, 다이오드 및 특히 광 흡수 또는 광 발생을 수반하는 디바이스, 예컨대 광 검출기, 태양 전지, 레이저, 등과 같은 다른 나노와이어 기반의 반도체 디바이스가 임의의 나노와이어 구조 상에 구현될 수 있음을 알아야 할 것이다.

이 명세서에 인용된 모든 공보 및 특허는 각각의 개별 공보 또는 특허가 구체적으로 및 개별적으로 참조로 포함되도록 표시된 것처럼 본원에 참고로 포함되며, 인용된 공보와 관련하여 방법 및/또는 물질을 개시하고 기술하기 위해 본원에 참고로 포함된다. 임의의 공보의 인용은 이의 개시된 바가 출원일 이전이며 본 발명이 이전 발명에 의해 이러한 공보를 선행할 자격이 없다는 것을 인정하는 것으로 해석되어서는 안 된다. 또한, 제공되는 공보의 일자는 독립적으로 확인해야 할 필요가 있을 수 있는 실제 공보 일자와 다를 수 있다.

Claims (20)

- 나노와이어 디바이스에 있어서,

경사진 p-평면 측벽들을 갖는 상측 선단 부분 및 실질적으로 수직인 m-평면 측벽들을 갖는 하측 부분을 갖는 III-질화물 반도체 나노와이어 코어; 및

상기 반도체 나노와이어 코어 주위에 방사상으로 위치된 인듐 함유 III-질화물 반도체 제1 쉘을 포함하며;

상기 제1 쉘은 상기 나노와이어 코어의 상기 상측 선단 부분 위에 위치된 경사진 p-평면 측벽들을 가진 상측 선단 부분, 및 상기 나노와이어 코어의 하측 부분 상에 위치된 실질적으로 수직인 m-평면 측벽들을 갖는 하측 부분을 포함하고;

상기 제1 쉘은 상기 제1 쉘의 상기 상측 선단 부분에 상기 p-평면으로부터 상기 제1 쉘의 상기 하측 부분의 상기 m-평면까지 구조적 불연속을 포함하는 이브(eave) 영역을 더 포함하고;

상기 이브 영역은 상기 경사진 p-평면 측벽들을 갖는 제1 쉘의 상측 선단 부분 및 상기 실질적으로 수직인 m-평면 측벽들을 갖는 상기 제1 쉘의 상기 하측 부분보다 적어도 5 원자 퍼센트 더 높은 인듐 함량을 갖는, 나노와이어 디바이스. - 제1항에 있어서, 상기 디바이스는 발광 다이오드(LED) 디바이스를 포함하고, 상기 제1 쉘은 활성 영역 양자 우물 쉘을 포함하는, 나노와이어 디바이스.

- 제2항에 있어서, 제1 쉘의 상기 상측 선단 부분은 상기 나노와이어 코어의 상기 상측 선단 부분의 전체 주변을 둘러싸는 링 형상 영역을 포함하며;

상기 제1 쉘의 상기 하측 부분은 상기 나노와이어 코어의 하측 부분의 전체 주변을 둘러싸는 링 형상의 영역을 포함하고;

상기 이브 영역은 상기 나노와이어 코어의 상기 상측 선단 부분과 상기 하측 부분 사이에 상기 나노와이어 코어의 중간 부분의 전체 주변을 둘러싸는 링 형상의 영역을 포함하는, 나노와이어 디바이스. - 제3항에 있어서, 상기 활성 양자 우물 쉘은 In(Al)GaN 반도체 양자 우물 쉘을 포함하는, 나노와이어 디바이스.

- 제4항에 있어서, 상기 이브 영역은 10 이상의 원자 퍼센트 인듐을 함유하고, 상기 제1 쉘의 상측 선단 부분 및 상기 제1 쉘의 하측 부분은 10 미만의 원자 퍼센트 인듐을 함유하는, 나노와이어 디바이스.

- 제5항에 있어서, 상기 이브 영역은 15-30 원자 퍼센트 인듐을 함유하고, 상기 제1 쉘의 상측 선단 부분 및 상기 제1 쉘의 하측 부분은 15 이하의 원자 퍼센트 인듐을 함유하는, 나노와이어 디바이스.

- 제5항에 있어서, 상기 LED는 495 내지 590 ㎚ 피크 방출 파장 또는 591 내지 650 ㎚ 피크 방출 파장을 갖는, 나노와이어 디바이스.

- 제7항에 있어서, 상기 LED는 약 520 nm의 피크 방출 파장을 가지며, 상기 이브 영역은 약 20 원자 퍼센트 인듐을 함유하는, 나노와이어 디바이스.

- 제7항에 있어서, 상기 LED는 약 610 nm의 피크 방출 파장을 가지며, 상기 이브 영역은 약 30 원자 퍼센트 인듐을 함유하는, 나노와이어 디바이스.

- 제2항에 있어서, 상기 제1 쉘의 하측 부분은 적어도 3개의 피크들을 갖는 불균일한 표면 프로파일을 가지며;

상기 적어도 3개의 피크들 각각은 밸리에 의해 상기 적어도 3개의 피크들 중 인접한 피크로부터 분리되고;

상기 적어도 3개의 피크들 각각은 인접한 밸리로부터 방사상 방향으로 적어도 2 nm 확장하는, 나노와이어 디바이스. - 제10항에 있어서, 상기 반도체 나노와이어 코어와 상기 제1 쉘 사이에 방사상으로 위치된 반도체 제2 쉘을 더 포함하며, 상기 제2 쉘은 상기 활성 영역 양자 우물의 하지층 장벽 쉘 또는 상기 활성 영역으로부터 방사상으로 안쪽으로 위치된 하지층 쉘을 포함하는, 나노와이어 디바이스.

- 제11항에 있어서, 상기 제2 쉘은 적어도 3개의 피크들을 갖는 불균일한 표면 프로파일을 가지며;

상기 적어도 3개의 피크들 각각은 밸리에 의해 상기 적어도 3개의 피크들 중 인접한 피크로부터 분리되고;

상기 적어도 3개의 피크들 각각은 인접한 밸리로부터 방사상 방향으로 적어도 2 nm 확장하는, 나노와이어 디바이스. - 제2항에 있어서, 지지체의 반도체 표면 상에 위치된 절연 마스크 층으로서, 상기 나노와이어 코어는 상기 절연 마스크 내 개구를 통해 상기 지지체의 상기 반도체 표면으로부터 실질적으로 수직으로 확장하는 제1 도전성 유형 반도체 나노와이어 코어를 포함하는 것인, 상기 절연 마스크 층;

상기 활성 영역 양자 우물 쉘 위 및 주위로 확장하는 적어도 하나의 제2 도전성 유형 반도체 쉘;

상기 제2 도전성 유형 반도체 쉘과 접촉하는 제1 전극층; 및

상기 반도체 나노와이어 코어에 전기적으로 연결되는 제2 전극층을 더 포함하는, 나노와이어 디바이스. - 제13항에 있어서, 상기 제1 도전성 유형은 n-형을 포함하고;

상기 제2 도전성 유형은 p-형을 포함하고;

상기 지지체는 기판 상에 n-GaN 또는 n-AlGaN n-형 반도체 버퍼층을 포함하고;

상기 반도체 나노와이어 코어는 n-GaN 나노와이어 코어를 포함하고;

상기 활성 영역 양자 우물 쉘은 GaN 장벽 쉘들 사이에 InGaN 쉘을 포함하고;

상기 제1 전극은 투명 도전성 산화물(TCO)을 포함하는, 나노와이어 디바이스. - 다이오드(LED) 발광 디바이스 제조 방법에 있어서,

반도체 나노와이어 코어를 형성하는 단계;

In(Al)GaN 활성 영역 양자 우물을 포함하는 제1 쉘을 상기 반도체 나노와이어 코어 주위에 방사상으로 형성하는 단계를 포함하고;

상기 제1 쉘은 상기 나노와이어 코어의 상측 선단 부분 상에 위치된 경사진 p-평면 측벽들을 갖는 상측 선단 부분, 및 상기 나노와이어 코어의 하측 부분 상에 위치된 실질적으로 수직인 m-평면 측벽들을 갖는 하측 부분을 포함하며;

상기 제1 쉘은 상기 제1 쉘의 상기 상측 선단 부분에 상기 p-평면으로부터 상기 제1 쉘의 상기 하측 부분의 상기 m-평면까지 구조적 불연속을 포함하는 이브 영역을 더 포함하고;

상기 이브 영역은 상기 경사진 p-평면 측벽들을 갖는 제1 쉘의 상측 선단 부분 및 상기 실질적으로 수직인 m-평면 측벽들을 갖는 상기 제1 쉘의 상기 하측 부분보다 적어도 5 원자 퍼센트 더 높은 인듐 함량을 갖는, 방법. - 제15항에 있어서, 상기 제1 반도체 쉘을 형성하기 전에 상기 반도체 나노와이어 코어 주위에 방사상으로 제2 반도체 쉘을 형성하는 단계를 더 포함하는, 방법.

- 제15항에 있어서, 상기 구조적 불연속은 In-N 본드들을 완화하여 실질적으로 수직인 m-평면 측벽들을 갖는 상기 제1 쉘의 상기 하측 부분보다 높은 확률로 인듐을 포함시키는 저 에너지 표면을 생성하는, 방법.

- 발광 다이오드(LED) 디바이스 제조 방법에 있어서,

반도체 나노와이어 코어를 형성하는 단계;

상기 반도체 나노와이어 코어 주위에 방사상으로 제1 쉘을 형성하는 단계로서, 상기 제1 쉘은 상기 제1 쉘의 형성 동안 일체로 인-시튜로 형성된 인듐 농후 이브 영역을 갖는 In(Al)GaN 활성 영역 양자 우물 쉘을 포함하는, 단계를 포함하고;

인듐 농후 이브 영역은 제1 쉘의 인듐 빈약 부분들보다 적어도 5 원자 퍼센트 더 높은 인듐 함량을 갖는, 방법. - 제18항에있어서, 상기 제1 쉘의 상기 인듐 빈약 부분들은 상기 나노와이어 코어의 상측 선단 부분 위에 위치된 경사진 p-평면 측벽들을 갖는 상측 선단 부분, 및 상기 나노와이어 코어의 하측 부분 상에 위치된 실질적으로 수직인 m-평면 측벽들을 갖는 하측 부분을 포함하는, 방법.

- 제19항에 있어서, 상기 이브 영역은 상기 제1 쉘의 상기 상측 선단 부분의 p-평면으로부터 상기 제1 쉘의 상기 하측 부분의 상기 m-평면까지 구조적 불연속을 포함하며;

상기 구조적 불연속은 In-N 본드들을 완화하여 실질적으로 수직인 m-평면 측벽들을 갖는 상기 제1 쉘의 상기 하측 부분보다 높은 확률로 인듐을 포함시키는 저 에너지 표면을 생성하는, 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201462036363P | 2014-08-12 | 2014-08-12 | |

| US62/036,363 | 2014-08-12 | ||

| PCT/US2015/044245 WO2016025325A1 (en) | 2014-08-12 | 2015-08-07 | Iii-nitride nanowire led with strain modified surface active region and method of making thereof |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20170066319A true KR20170066319A (ko) | 2017-06-14 |

Family

ID=55304513

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020177005165A KR20170066319A (ko) | 2014-08-12 | 2015-08-07 | 스트레인 수정된 표면 활성 영역을 가진 iii-질화물 나노와이어 led 및 이의 제조 방법 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US9882086B2 (ko) |

| EP (1) | EP3180806A4 (ko) |

| JP (1) | JP6505208B2 (ko) |

| KR (1) | KR20170066319A (ko) |

| CN (1) | CN107251239B (ko) |

| WO (1) | WO2016025325A1 (ko) |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8669574B2 (en) | 2008-07-07 | 2014-03-11 | Glo Ab | Nanostructured LED |

| WO2014138904A1 (en) * | 2013-03-14 | 2014-09-18 | The Royal Institution For The Advancement Of Learning/Mcgill University | Methods and devices for solid state nanowire devices |

| WO2016022824A1 (en) | 2014-08-08 | 2016-02-11 | Glo Ab | Pixilated display device based upon nanowire leds and method for making the same |

| WO2016025325A1 (en) | 2014-08-12 | 2016-02-18 | Glo Ab | Iii-nitride nanowire led with strain modified surface active region and method of making thereof |

| WO2016049507A1 (en) | 2014-09-26 | 2016-03-31 | Glo Ab | Monolithic image chip for near-to-eye display |

| DE102014117892A1 (de) * | 2014-12-04 | 2016-06-09 | Osram Opto Semiconductors Gmbh | Optoelektronisches Bauelement sowie optoelektronisches Bauteil |

| KR101787435B1 (ko) * | 2016-02-29 | 2017-10-19 | 피에스아이 주식회사 | 나노 로드 제조방법 |

| KR20180133436A (ko) | 2016-05-04 | 2018-12-14 | 글로 에이비 | 상이한 색상의 led를 포함하는 일체형 다색 직시형 디스플레이와 이의 제조 방법 |

| US10361341B2 (en) | 2016-10-24 | 2019-07-23 | Glo Ab | Indium gallium nitride red light emitting diode and method of making thereof |

| CN107749437A (zh) * | 2017-11-17 | 2018-03-02 | 广州市香港科大霍英东研究院 | 可挠性发光二极管制程及其结构 |

| US11605668B2 (en) * | 2018-05-21 | 2023-03-14 | Intel Corporation | Pixel architectures for low power micro light-emitting diode displays |

| CN109037401A (zh) * | 2018-06-21 | 2018-12-18 | 中国工程物理研究院电子工程研究所 | 一种氮化镓基水平纳米柱壳核结构阵列led的制备方法 |

| CN109616553B (zh) * | 2018-11-22 | 2020-06-30 | 中南大学 | 一种新型纤锌矿GaAs核壳纳米线光电探测器的制备方法 |

| US11156759B2 (en) | 2019-01-29 | 2021-10-26 | Osram Opto Semiconductors Gmbh | μ-LED, μ-LED device, display and method for the same |

| US11302248B2 (en) | 2019-01-29 | 2022-04-12 | Osram Opto Semiconductors Gmbh | U-led, u-led device, display and method for the same |

| US11271143B2 (en) | 2019-01-29 | 2022-03-08 | Osram Opto Semiconductors Gmbh | μ-LED, μ-LED device, display and method for the same |

| US11610868B2 (en) | 2019-01-29 | 2023-03-21 | Osram Opto Semiconductors Gmbh | μ-LED, μ-LED device, display and method for the same |

| CN109860355A (zh) * | 2019-02-02 | 2019-06-07 | 苏州汉骅半导体有限公司 | 深紫外led制备方法 |

| US11538852B2 (en) | 2019-04-23 | 2022-12-27 | Osram Opto Semiconductors Gmbh | μ-LED, μ-LED device, display and method for the same |

| US10930747B2 (en) * | 2019-06-04 | 2021-02-23 | Nxp B.V. | Semiconductor device with an encircled electrode |

| JP7336767B2 (ja) | 2019-10-03 | 2023-09-01 | 株式会社小糸製作所 | 半導体発光素子および半導体発光素子の製造方法 |

| KR20210099681A (ko) | 2020-02-04 | 2021-08-13 | 삼성전자주식회사 | 3차원 구조 반도체 발광소자 및 디스플레이 장치 |

| CN116014043B (zh) * | 2023-03-24 | 2023-06-02 | 江西兆驰半导体有限公司 | 深紫外发光二极管外延片及其制备方法、led |

Family Cites Families (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3660446B2 (ja) * | 1996-11-07 | 2005-06-15 | 日亜化学工業株式会社 | 窒化物半導体素子及びその製造方法 |

| JP3282174B2 (ja) | 1997-01-29 | 2002-05-13 | 日亜化学工業株式会社 | 窒化物半導体発光素子 |

| JP4158519B2 (ja) * | 2002-12-26 | 2008-10-01 | 住友電気工業株式会社 | 白色発光素子およびその製造方法 |

| US7968359B2 (en) | 2006-03-10 | 2011-06-28 | Stc.Unm | Thin-walled structures |

| US20140012224A1 (en) | 2006-04-07 | 2014-01-09 | The Regents Of The University Of California | Targeted hollow gold nanostructures and methods of use |

| CN102255018B (zh) | 2006-12-22 | 2013-06-19 | 昆南诺股份有限公司 | 带有直立式纳米线结构的led及其制作方法 |

| EP2102899B1 (en) | 2007-01-12 | 2020-11-11 | QuNano AB | Nitride nanowires and method of producing such |

| US8188513B2 (en) | 2007-10-04 | 2012-05-29 | Stc.Unm | Nanowire and larger GaN based HEMTS |

| JP2009105088A (ja) | 2007-10-19 | 2009-05-14 | Panasonic Electric Works Co Ltd | 半導体発光素子およびそれを用いる照明装置ならびに半導体発光素子の製造方法 |

| JP4856666B2 (ja) * | 2008-03-26 | 2012-01-18 | 独立行政法人科学技術振興機構 | 発光ダイオード素子及びその製造方法 |

| US8138493B2 (en) | 2008-07-09 | 2012-03-20 | Qunano Ab | Optoelectronic semiconductor device |

| KR101549620B1 (ko) | 2009-01-30 | 2015-09-02 | 삼성전자주식회사 | pn 구조를 지닌 Zn 산화물 나노 와이어 및 그 제조 방법 |

| KR20110064702A (ko) | 2009-12-08 | 2011-06-15 | 삼성전자주식회사 | 요철 구조를 지닌 코어-쉘 나노 와이어 및 이를 이용한 열전 소자 |

| US9112240B2 (en) | 2010-01-04 | 2015-08-18 | Nanotek Instruments, Inc. | Lithium metal-sulfur and lithium ion-sulfur secondary batteries containing a nano-structured cathode and processes for producing same |

| US8138439B2 (en) | 2010-02-11 | 2012-03-20 | Eaton Corporation | Limiter including a number of gas channels and electrical switching apparatus employing the same |

| EP2553696A4 (en) | 2010-04-02 | 2016-07-06 | Intel Corp | LOAD MEMORY DEVICE, METHOD OF MANUFACTURING THEREFOR, METHOD FOR PRODUCING AN ELECTRICALLY CONDUCTIVE STRUCTURE THEREFOR, MOBILE ELECTRONIC DEVICE THEREWITH AND MICROELECTRONIC DEVICE THEREWITH |

| SG186312A1 (en) | 2010-06-24 | 2013-02-28 | Glo Ab | Substrate with buffer layer for oriented nanowire growth |

| KR101691906B1 (ko) * | 2010-09-14 | 2017-01-02 | 삼성전자주식회사 | Ⅲ족 질화물 나노로드 발광 소자 제조방법 |

| FR2975532B1 (fr) * | 2011-05-18 | 2013-05-10 | Commissariat Energie Atomique | Connexion electrique en serie de nanofils emetteurs de lumiere |

| KR20120052651A (ko) | 2010-11-16 | 2012-05-24 | 삼성엘이디 주식회사 | 나노로드 발광소자 |

| KR20120059064A (ko) | 2010-11-30 | 2012-06-08 | 삼성엘이디 주식회사 | 발광소자 및 그 제조방법 |

| US8350251B1 (en) * | 2011-09-26 | 2013-01-08 | Glo Ab | Nanowire sized opto-electronic structure and method for manufacturing the same |

| TWI476953B (zh) * | 2012-08-10 | 2015-03-11 | Univ Nat Taiwan | 半導體發光元件及其製作方法 |

| WO2014066379A1 (en) | 2012-10-26 | 2014-05-01 | Glo Ab | Nanowire sized opto-electronic structure and method for modifying selected portions of same |

| JP6070257B2 (ja) * | 2013-02-21 | 2017-02-01 | 株式会社リコー | 13族窒化物結晶の製造方法、及び13族窒化物結晶の製造装置 |

| JP6227128B2 (ja) | 2013-06-07 | 2017-11-08 | グロ アーベーGlo Ab | マルチカラーled及びその製造方法 |

| WO2015095049A1 (en) * | 2013-12-17 | 2015-06-25 | Glo Ab | Iii-nitride nanowire led with strain modified surface active region and method of making thereof |

| WO2016022824A1 (en) * | 2014-08-08 | 2016-02-11 | Glo Ab | Pixilated display device based upon nanowire leds and method for making the same |

| WO2016025325A1 (en) | 2014-08-12 | 2016-02-18 | Glo Ab | Iii-nitride nanowire led with strain modified surface active region and method of making thereof |

-

2015

- 2015-08-07 WO PCT/US2015/044245 patent/WO2016025325A1/en active Application Filing

- 2015-08-07 EP EP15832263.6A patent/EP3180806A4/en not_active Withdrawn

- 2015-08-07 JP JP2017507866A patent/JP6505208B2/ja active Active

- 2015-08-07 US US15/502,758 patent/US9882086B2/en active Active

- 2015-08-07 KR KR1020177005165A patent/KR20170066319A/ko unknown

- 2015-08-07 CN CN201580050665.6A patent/CN107251239B/zh not_active Expired - Fee Related

-

2018

- 2018-01-03 US US15/861,013 patent/US10205054B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN107251239A (zh) | 2017-10-13 |

| EP3180806A4 (en) | 2018-03-07 |

| US20180145218A1 (en) | 2018-05-24 |

| JP2017525159A (ja) | 2017-08-31 |

| WO2016025325A1 (en) | 2016-02-18 |

| WO2016025325A9 (en) | 2017-03-23 |

| US20170236975A1 (en) | 2017-08-17 |

| CN107251239B (zh) | 2019-06-28 |

| EP3180806A1 (en) | 2017-06-21 |

| US9882086B2 (en) | 2018-01-30 |

| JP6505208B2 (ja) | 2019-04-24 |

| US10205054B2 (en) | 2019-02-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10205054B2 (en) | III-nitride nanowire LED with strain modified surface active region and method of making thereof | |

| US10026866B2 (en) | III-nitride nanowire LED with strain modified surface active region and method of making thereof | |

| JP6486519B2 (ja) | ナノワイヤサイズの光電構造及びその選択された部分を改質する方法 | |

| KR20110039335A (ko) | 광전자 반도체 디바이스 | |

| US20160035941A1 (en) | High index dielectric film to increase extraction efficiency of nanowire leds | |

| WO2014082192A1 (zh) | 一种半导体外延结构及其发光器件 | |

| US9196787B2 (en) | Nanowire LED structure with decreased leakage and method of making same | |

| US9196792B2 (en) | Nanowire LED structure with decreased leakage and method of making same | |

| TW201511334A (zh) | 具有經減低漏電之奈米線發光二極體結構及其製造方法 | |

| US20220352398A1 (en) | Composition of matter |