KR20160044004A - 텅스텐 육플루오르화물(wf6) 에치백을 이용하는 텅스텐 증착 - Google Patents

텅스텐 육플루오르화물(wf6) 에치백을 이용하는 텅스텐 증착 Download PDFInfo

- Publication number

- KR20160044004A KR20160044004A KR1020167006832A KR20167006832A KR20160044004A KR 20160044004 A KR20160044004 A KR 20160044004A KR 1020167006832 A KR1020167006832 A KR 1020167006832A KR 20167006832 A KR20167006832 A KR 20167006832A KR 20160044004 A KR20160044004 A KR 20160044004A

- Authority

- KR

- South Korea

- Prior art keywords

- tungsten

- tungsten film

- depositing

- layer

- film

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic System

- H01L21/28556—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic System by chemical means, e.g. CVD, LPCVD, PECVD, laser CVD

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/04—Coating on selected surface areas, e.g. using masks

- C23C16/045—Coating cavities or hollow spaces, e.g. interior of tubes; Infiltration of porous substrates

-

- C—CHEMISTRY; METALLURGY

- C23—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; CHEMICAL SURFACE TREATMENT; DIFFUSION TREATMENT OF METALLIC MATERIAL; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL; INHIBITING CORROSION OF METALLIC MATERIAL OR INCRUSTATION IN GENERAL

- C23C—COATING METALLIC MATERIAL; COATING MATERIAL WITH METALLIC MATERIAL; SURFACE TREATMENT OF METALLIC MATERIAL BY DIFFUSION INTO THE SURFACE, BY CHEMICAL CONVERSION OR SUBSTITUTION; COATING BY VACUUM EVAPORATION, BY SPUTTERING, BY ION IMPLANTATION OR BY CHEMICAL VAPOUR DEPOSITION, IN GENERAL

- C23C16/00—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes

- C23C16/06—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of metallic material

- C23C16/08—Chemical coating by decomposition of gaseous compounds, without leaving reaction products of surface material in the coating, i.e. chemical vapour deposition [CVD] processes characterised by the deposition of metallic material from metal halides

- C23C16/14—Deposition of only one other metal element

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/20—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy

- H01L21/205—Deposition of semiconductor materials on a substrate, e.g. epitaxial growth solid phase epitaxy using reduction or decomposition of a gaseous compound yielding a solid condensate, i.e. chemical deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3205—Deposition of non-insulating-, e.g. conductive- or resistive-, layers on insulating layers; After-treatment of these layers

- H01L21/321—After treatment

- H01L21/3213—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer

- H01L21/32133—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only

- H01L21/32135—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only

- H01L21/32136—Physical or chemical etching of the layers, e.g. to produce a patterned layer from a pre-deposited extensive layer by chemical means only by vapour etching only using plasmas

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/7687—Thin films associated with contacts of capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

Landscapes

- Chemical & Material Sciences (AREA)

- Engineering & Computer Science (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- General Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Materials Engineering (AREA)

- Mechanical Engineering (AREA)

- Metallurgy (AREA)

- Organic Chemistry (AREA)

- Chemical Vapour Deposition (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Plasma & Fusion (AREA)

Abstract

본원에서 설명되는 구현들은 일반적으로, 기상 증착 프로세스들을 사용하여, 기판들 상에 텅스텐 재료들을 형성하기 위한 방법들에 관한 것이다. 방법은, 기판 프로세싱 챔버에, 피처가 내부에 형성된 기판을 위치시키는 단계, 피처 위에 제 1 텅스텐 막을 증착하기 위해, 프로세싱 챔버에 텅스텐 할로겐화물 화합물 및 수소 함유 가스의 연속적인 유동을 도입함으로써, 벌크 텅스텐 층의 제 1 막을 증착하는 단계, 활성화된 처리 가스 및 텅스텐 할로겐화물 화합물의 연속적인 유동에 제 1 막을 노출시킴으로써, 제 1 막의 일부를 제거하기 위해, 플라즈마 처리를 사용하여, 벌크 텅스텐 층의 제 1 막을 에칭하는 단계, 및 제 1 텅스텐 막 위에 제 2 텅스텐 막을 증착하기 위해, 프로세싱 챔버에 텅스텐 할로겐화물 화합물 및 수소 함유 가스의 연속적인 유동을 도입함으로써, 벌크 텅스텐 층의 제 2 막을 증착하는 단계를 포함한다.

Description

[0001] 본원에서 설명되는 구현들은 일반적으로, 기판들의 프로세싱에 관한 것이고, 더 상세하게는, 기상 증착 프로세스들을 사용하여, 기판들 상에 텅스텐 재료들을 형성하기 위한 방법들에 관한 것이다.

[0002] 나노미터-크기의 피처(feature)들을 신뢰가능하게 생성하는 것은, 차세대 반도체 디바이스들에 대한 핵심 기술들 중 하나이다. 디바이스들 및 회로들의 축소되는 치수들은 프로세싱 능력들에 대해 부가적인 요구들을 제기하였다. 집적 회로 기술의 중심(heart)에 놓인 멀티레벨 인터커넥트(multilevel interconnect)들은, 비아(via)들 및 다른 인터커넥트들과 같은 고 종횡비 피처들의 정밀한 프로세싱을 요구한다. 이러한 인터커넥트들의 신뢰가능한 형성은, 개별적인 기판들의 품질 및 회로 밀도를 증가시키기 위한 계속되는 노력 및 미래의 성공에 대해 매우 중요하다.

[0003] 기판들 상에 형성된 피처들의 금속화(metallization)는, 텅스텐과 같은 금속들의 CVD 증착을 포함한다. 텅스텐은, 소스 콘택(contact)들, 드레인 콘택들, 금속 게이트 충전(fill), 및 게이트 콘택들의 금속 충전, 뿐만 아니라, DRAM 및 플래시 메모리에서의 애플리케이션들에 대해 사용될 수 있다. 기술 노드 축소로 인해, 낮은 저항률 및 낮은 거칠기를 갖는 텅스텐 막들이, 후속 프로세스들과의 통합(integration) 및 디바이스 특성들에 대해 바람직하다.

[0004] 화학 기상 증착(CVD)은 텅스텐의 금속 충전에 대해 사용되는 하나의 프로세스 기술이다. 아래 놓인 층간 유전체(ILD) 재료(10)에 패턴이 에칭된다. 그 후에, 에칭된 기판들을 충전하기 위해, 텅스텐이 프로세싱된다.

[0005] 그러나, 피처 크기들에서의 계속되는 감소는 이러한 프로세스에서 어려움이 증가되는 것을 의미하였다. 텅스텐 층이 피처의 바닥 표면, 뿐만 아니라, 측벽들 상에 형성되는 경우에, CVD 프로세스는 피처 내의 표면들 양자 모두 상에 금속을 증착한다. 고 종횡비 피처들의 경우에, CVD 동안의 텅스텐 증착 성장의 결과를 도시하는 도 1에서 볼 수 있는 바와 같이, 피처의 (공칭(nominal) 피처 갭(gap) 개구 치수들이 32 nm 이하의 범위에 있는(유전체 재료 층에서의 피처(또는 디프레션(depression))에 의해 생성된, 유전체 재료 층의 표면에서의 갭이 32 nm 또는 그 미만일 수 있는) 새로운 세대의 디바이스들에서의) 개구는, 보톰 업(bottom up) 충전 프로세스가, 실질적인 무-공극(void-free) 텅스텐 충전 재료로 피처를 완전히 충전하도록 유전체 층의 두께의 전체 높이에 도달하기 전에, "차단된 상태(closed off)"(27)가 될 수 있다. 측벽들 상에서의 텅스텐 성장은, 피처의 하부 부분이 피처 바닥 표면으로부터 완전히 성장되기 전에, 피처 개구에서 피처를 차단시키는 경향이 있고, 그에 따라, 피처 내에 공극(30)이 형성된다. 공극(30)의 존재는 인터커넥트 피처의 재료 및 동작 특성들을 변화시키고, 결국, 디바이스의 부적절한 동작 및 조기 고장(breakdown)을 야기할 수 있다. 효율적이기 위해, 전도성 엘리먼트, 즉, 라인(line)은, 거의, 현재의 최신 디바이스들에서의 당업자에 의해 확립되고 알려져 있는 바와 같은, 그러한 라인의 실질적인 최대 전류 밀도를 운반(carry)한다. 목적은, 미래의 디바이스들에서의 더 작은 피처들에서 동일한 또는 더 높은 전류 유동 밀도를 달성하는 것이다.

[0006] 따라서, 위에서 논의된 종래의 기법들의 문제들 및 제한들 없이, 텅스텐에 의한 고 종횡비 초-소형 피처들의 무-공극 충전을 위해, CVD를 사용하는 것이 바람직하다.

[0007] 본원에서 설명되는 구현들은 일반적으로, 기판들의 프로세싱에 관한 것이고, 더 상세하게는, 기상 증착 프로세스들을 사용하여, 기판들 상에 텅스텐 재료들을 형성하기 위한 방법들에 관한 것이다. 일 구현에서, 기판 상에 텅스텐 막을 증착하기 위한 방법이 제공된다. 방법은, 기판 프로세싱 챔버에, 피처가 내부에 형성된 기판을 위치시키는 단계 ― 피처는 적어도 하나의 측벽 및 바닥 표면에 의해 정의됨 ―, 피처 위에 제 1 텅스텐 막을 증착하기 위해, 프로세싱 챔버에 텅스텐 할로겐화물 화합물 및 수소 함유 가스의 연속적인 유동을 도입함으로써, 벌크(bulk) 텅스텐 층의 제 1 막을 증착하는 단계, 활성화된 처리 가스 및 텅스텐 할로겐화물 화합물의 연속적인 유동에 제 1 막을 노출시킴으로써, 제 1 막의 일부를 제거하기 위해, 플라즈마 처리를 사용하여, 벌크 텅스텐 층의 제 1 막을 에칭하는 단계, 및 제 1 텅스텐 막 위에 제 2 텅스텐 막을 증착하기 위해, 프로세싱 챔버에 텅스텐 할로겐화물 화합물 및 수소 함유 가스의 연속적인 유동을 도입함으로써, 벌크 텅스텐 층의 제 2 막을 증착하는 단계를 포함한다.

[0008] 본 개시의 상기 열거된 특징들이 상세히 이해될 수 있는 방식으로, 앞서 간략히 요약된, 본 개시의 보다 구체적인 설명이 구현들을 참조로 하여 이루어질 수 있는데, 이러한 구현들의 일부는 첨부된 도면들에 예시되어 있다. 그러나, 첨부된 도면들은 본 개시의 단지 전형적인 구현들을 도시하는 것이므로 본 개시의 범위를 제한하는 것으로 간주되지 않아야 한다는 것이 주목되어야 하는데, 이는 본 개시가 다른 균등하게 유효한 구현들을 허용할 수 있기 때문이다.

[0009] 도 1(종래 기술)은, 종래 기술의 프로세스들을 사용하여, 텅스텐이 내부에 증착된 피처를 갖는 기판의 개략적인 단면도들이다.

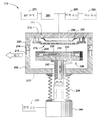

[0010] 도 2는, 본원에서 설명되는 구현들에 따라 텅스텐 층을 증착하기 위해 사용될 수 있는 플라즈마 강화 CVD(PECVD) 프로세싱 챔버의 개략적인 단면도이다.

[0011] 도 3은, 본원에서 설명되는 구현들에 따른, 텅스텐 충전 층을 증착하기 위한 방법을 도시하는 흐름도이다.

[0012] 도 4a 내지 도 4f는, 본원에서 설명되는 구현들에 따라 텅스텐이 내부에 증착된 피처를 갖는 기판의 개략적인 단면도들이다.

[0013] 도 5는, 본원에서 설명되는 구현들을 수행하기 위해 사용될 수 있는 클러스터 툴의 개략적인 평면도이다.

[0014] 이해를 용이하게 하기 위하여, 도면들에 대해 공통인 동일한 엘리먼트들을 지시하기 위해 가능한 경우에 동일한 참조 번호들이 사용되었다. 일 구현에서 개시된 엘리먼트들이, 구체적인 설명 없이 다른 구현들에 대해 유익하게 활용될 수 있다는 것이 고려된다.

[0009] 도 1(종래 기술)은, 종래 기술의 프로세스들을 사용하여, 텅스텐이 내부에 증착된 피처를 갖는 기판의 개략적인 단면도들이다.

[0010] 도 2는, 본원에서 설명되는 구현들에 따라 텅스텐 층을 증착하기 위해 사용될 수 있는 플라즈마 강화 CVD(PECVD) 프로세싱 챔버의 개략적인 단면도이다.

[0011] 도 3은, 본원에서 설명되는 구현들에 따른, 텅스텐 충전 층을 증착하기 위한 방법을 도시하는 흐름도이다.

[0012] 도 4a 내지 도 4f는, 본원에서 설명되는 구현들에 따라 텅스텐이 내부에 증착된 피처를 갖는 기판의 개략적인 단면도들이다.

[0013] 도 5는, 본원에서 설명되는 구현들을 수행하기 위해 사용될 수 있는 클러스터 툴의 개략적인 평면도이다.

[0014] 이해를 용이하게 하기 위하여, 도면들에 대해 공통인 동일한 엘리먼트들을 지시하기 위해 가능한 경우에 동일한 참조 번호들이 사용되었다. 일 구현에서 개시된 엘리먼트들이, 구체적인 설명 없이 다른 구현들에 대해 유익하게 활용될 수 있다는 것이 고려된다.

[0015] 본원에서 설명되는 구현들은 일반적으로, 기판들의 프로세싱에 관한 것이고, 더 상세하게는, 기상 증착 프로세스들을 사용하여, 기판들 상에 텅스텐 재료들을 형성하기 위한 방법들에 관한 것이다.

[0016] 텅스텐(W)은, 약 이십년 동안, 로직 애플리케이션에서의 콘택 레벨에서 사용되었다. 최근의 진보된 CMOS 디바이스들에서, FinFET 및 금속 게이트와 같은 새로운 기술이 출현하였고, 이는, PMOS 및 NMOS 디바이스들 양자 모두를 위한 금속 게이트 충전으로서의 텅스텐에 대한 새로운 애플리케이션을 발생시킨다. 3D NAND 디바이스들에서, 금속 게이트 충전을 위해 텅스텐이 또한 사용된다. 텅스텐 충전에 대한 요건들은 점점 더 어려운 문제가 되고 있다(challenging). 콘택의 경우에, 콘택들의 치수들이 더 작아지게 됨에 따라, 둘출부(overhang)가 더 어려운 문제가 되고, 전형적으로, 텅스텐 등각(conformal) 충전 후에 큰 심(seam)을 남긴다. 게다가, 심은 WCMP 동안에 슬러리에 노출될 것이고, 이는, 통합 문제들을 야기한다. 진보된 CMOS 및 3D NAND 양자 모두에서의 금속 게이트 트렌치(trench)의 경우에, 통상적인 텅스텐 등각 성장은 필연적으로, 중간에 심을 남기고, 그러한 심은 텅스텐 에치백(etch back) 프로세스 동안에 더 넓게 확장될 수 있고, 그에 따라, 디바이스 고장이 야기될 수 있다. 따라서, 진보된 로직 및 메모리 디바이스들에서의 콘택 및 금속 게이트 충전 양자 모두에 대해, 심리스(seamless) 텅스텐 충전이 요구된다. 이러한 심리스 텅스텐 충전은, 본원에서 설명되는 텅스텐 증착-에치백-증착 충전 프로세스들에 의해 달성될 수 있다. 일반적으로, 텅스텐 에치백 프로세스들은, 더 우수한 프로세스 제어를 위해, 전용 에칭 챔버에서 에천트(etchant)로서 NF3를 활용한다. 부가적인 에칭 챔버는 툴 구성을 더 복잡하게 만든다. NF3 에칭의 다른 주요한 결점은, 에치백 후에, NF3가 텅스텐 표면을 포이즈닝(poison)할 것이라는 것이고, 그에 따라, 제 2 텅스텐 증착 프로세스가 다른 텅스텐 핵형성(nucleation) 층을 요구하고, 이는, 더 낮은 처리량 및 더 높은 콘택/라인 저항을 야기한다.

[0017] 본원에서 설명되는 특정한 구현들에서, 텅스텐 에치백은, 텅스텐 할로겐화물 플라즈마(예컨대, WF6 플라즈마)를 사용함으로써 달성된다. 플라즈마 소스는 RF 또는 원격 플라즈마 소스(RPS)일 수 있다. 원자 불소가 WF6 플라즈마로부터 해리되고(dissociated), 금속 텅스텐을 에칭하기 위해 사용된다. 에칭 레이트는 WF6 유동 및 플라즈마 조건에 따라 좌우된다. 프로세스 조건들을 조정함으로써, 에치백 양을 제어하기 위해, ~0.5 Å/초 내지 3 Å/초의 범위에서의 매우 약한(mild) 에칭 레이트가 달성될 수 있다. 그로 인해, 상이한 임계 치수(CD)들 및 돌출부를 갖는 구조들 상에 심리스 충전이 생성될 수 있고, 원자 불소에 의한 TiN 라이너(liner) 공격이 방지될 수 있다. 에천트에 질소가 존재하지 않기 때문에, WF6 에치백 후에, 포이즈닝 영향이 존재하지 않는다. 제 2 증착 프로세스는, 핵형성 층을 요구하지 않으면서, 직접적으로, WF6 + H2 케미스트리(chemistry)를 활용할 수 있다. 다른 큰 이점은, WF6가 하나의 챔버에서 증착 전구체 및 에천트 양자 모두로서 사용될 수 있기 때문에 달성될 수 있는 단일 챔버 증착-에칭-증착 프로세스이다. RF 또는 RPS 플라즈마 능력을 갖는 표준 WCVD 챔버가 증착 및 에치백 양자 모두를 수행할 수 있고, 이는, 개선된 처리량 및 챔버 리던던시(redundancy)를 제공한다.

[0018] 도 2는, 본원에서 설명되는 구현들에 따라 텅스텐 층을 증착하기 위해 사용될 수 있는 PECVD 프로세싱 챔버(200)의 개략적인 단면도이다. 그러한 프로세싱 챔버(200)는, 캘리포니아, 산타클라라에 위치된 어플라이드 머티어리얼스, 인코포레이티드(Applied Materials, Inc.)로부터 입수가능하고, 이에 대한 간략한 설명이 뒤따른다. 본원에서 설명되는 핵형성 및 벌크 층 증착 방법들을 수행할 수 있는 통합된 프로세싱 시스템은, 캘리포니아, 산타클라라에 위치된 어플라이드 머티어리얼스, 인코포레이티드로부터 입수가능한 텅스텐 화학 기상 증착 챔버이다. 아래에서 설명되는 챔버는 예시적인 구현이고, 다른 제조자들로부터의 챔버들을 포함하는 다른 챔버들이, 본원에서 설명되는 본 발명의 특성들로부터 벗어나지 않으면서, 본 개시의 구현들과 함께 사용될 수 있거나, 또는 본 개시의 구현들과 매칭(match)하도록 변형될 수 있다는 것이 이해되어야 한다.

[0019] 프로세싱 챔버(200)는, 중앙 이송 챔버에 연결되고 로봇에 의해 서비싱되는 다수의 프로세싱 챔버들을 포함하는 프로세싱 시스템의 일부일 수 있다(도 5 참조). 프로세싱 챔버(200)는, 프로세싱 볼륨(212)을 정의하는, 벽들(206), 바닥(208), 및 덮개(210)를 포함한다. 벽들(206) 및 바닥(208)은 전형적으로, 알루미늄의 단일 블록(unitary block)으로 제조된다. 벽들(206)은, 벽들(206)의 온도를 제어하기 위해 유체가 통과될 수 있는 도관들(미도시)을 내부에 가질 수 있다. 프로세싱 챔버(200)는 또한, 프로세싱 볼륨(212)을 배기 포트(216)에 커플링시키는 펌핑 링(214), 뿐만 아니라, 다른 펌핑 컴포넌트들(미도시)을 포함할 수 있다.

[0020] 가열될 수 있는 기판 지지 어셈블리(238)가 프로세싱 챔버(200) 내에서 중앙에 배치될 수 있다. 기판 지지 어셈블리(238)는 증착 프로세스 동안에 기판(203)을 지지한다. 기판 지지 어셈블리(238)는 일반적으로, 알루미늄, 세라믹, 또는 알루미늄과 세라믹의 조합으로 제조되고, 전형적으로, 진공 포트(미도시) 및 적어도 하나 또는 그 초과의 가열 엘리먼트들(232)을 포함한다.

[0021] 진공 포트는, 증착 프로세스 동안에 기판 지지 어셈블리(238)에 기판(203)을 고정시키도록, 기판 지지 어셈블리(238)와 기판(203) 사이에 진공을 적용하기 위해 사용될 수 있다. 하나 또는 그 초과의 가열 엘리먼트들(232)은, 예컨대, 기판 지지 어셈블리(238), 및 그러한 기판 지지 어셈블리(238) 상에 위치된 기판(203)을 미리 결정된 온도로 가열하기 위해, 전력 소스(230)에 커플링되고 기판 지지 어셈블리(238)에 배치된 전극들일 수 있다.

[0022] 일반적으로, 기판 지지 어셈블리(238)는 스템(stem)(242)에 커플링된다. 스템(242)은, 기판 지지 어셈블리(238)와 프로세싱 챔버(200)의 다른 컴포넌트들 사이의, 전기 리드들, 진공 및 가스 공급 라인들을 위한 도관을 제공한다. 부가적으로, 스템(242)은, 기판 지지 어셈블리(238)를 (도 2에서 도시된 바와 같은) 상승된 위치와 하강된 위치(미도시) 사이에서 이동시키는 리프트 시스템(244)에 기판 지지 어셈블리(238)를 커플링시킨다. 벨로즈(bellows)(246)는, 기판 지지 어셈블리(238)의 이동을 용이하게 하면서, 챔버(200) 외부의 분위기(atmosphere)와 프로세싱 볼륨(212) 사이에 진공 밀봉을 제공한다.

[0023] 기판 지지 어셈블리(238)는 부가적으로, 주위를 둘러싸는(circumscribing) 쉐도우 링(248)을 지지한다. 쉐도우 링(248)은 형태가 환상이고, 전형적으로, 예컨대 알루미늄 질화물과 같은 세라믹 재료를 포함한다. 일반적으로, 쉐도우 링(248)은 기판 지지 어셈블리(238) 및 기판(203)의 에지에서의 증착을 방지한다.

[0024] 덮개(210)는 벽들(206)에 의해 지지되고, 프로세싱 챔버(200)의 서비싱을 허용하기 위해 제거가능할 수 있다. 덮개(210)는 일반적으로, 알루미늄으로 구성될 수 있고, 부가적으로, 내부에 형성된 열 전달 유체 채널들(224)을 가질 수 있다. 열 전달 유체 채널들(224)은, 덮개(210)를 통해 열 전달 유체를 유동시키는 유체 소스(미도시)에 커플링된다. 열 전달 유체 채널들(224)을 통해 유동하는 유체는 덮개(210)의 온도를 조절한다.

[0025] 샤워헤드(218)가 일반적으로, 덮개(210)의 내부 측(220)에 커플링될 수 있다. 천공된 블로커 플레이트(236)가 선택적으로, 덮개(210)와 샤워헤드(218) 사이의 공간(222)에 배치될 수 있다. 혼합 블록(234)을 통해 프로세싱 챔버(200)에 진입하는 가스들(즉, 프로세스 및 다른 가스들)은 먼저, 블로커 플레이트(236)에 의해 확산되고, 그에 따라, 가스들이 샤워헤드(218) 뒤의 공간(222)을 충전한다. 그 후에, 가스들은 샤워헤드(218)를 통해 그리고 프로세싱 챔버(200) 내로 통과한다. 블로커 플레이트(236) 및 샤워헤드(218)는 프로세싱 챔버(200)에 가스들의 균일한 유동을 제공하도록 구성된다. 균일한 가스 유동은 기판(203) 상의 균일한 층 형성을 촉진하는데 있어서 바람직하다.

[0026] 샤워헤드(218)에서의 가스 통로들을 통해, 기판(203)과 샤워헤드(218) 사이의 프로세싱 영역에 가스를 제공하기 위해, 가스 소스(260)가 덮개(210)에 커플링된다. 프로세싱 볼륨을 원하는 압력으로 제어하기 위해, 진공 펌프(미도시)가 프로세싱 챔버(200)에 커플링될 수 있다. 샤워헤드(218)에 RF 전류를 제공하기 위해, 매칭 네트워크(290)를 통해 덮개(210) 및/또는 샤워헤드(218)에 RF 소스(270)가 커플링된다. RF 전류는 기판 지지 어셈블리(238)와 샤워헤드(218) 사이에 전기장을 생성하고, 그에 따라, 기판 지지 어셈블리(238)와 샤워헤드(218) 사이에서 가스들로부터 플라즈마가 생성될 수 있다.

[0027] 유도성으로 커플링된 원격 플라즈마 소스와 같은 원격 플라즈마 소스(280)가 또한, 덮개(210)와 가스 소스(260) 사이에 커플링될 수 있다. 기판들의 프로세싱 사이에, 원격 플라즈마가 생성되도록, 원격 플라즈마 소스(280)에 세정 가스가 제공될 수 있다. 원격 플라즈마로부터의 라디칼들은, 플라즈마 에칭 프로세스를 위해, 프로세싱 챔버에 제공될 수 있다. 에칭 가스는 추가로, 샤워헤드(218)에 제공되는 RF 소스(270)에 의해 여기될 수 있다.

[0028] 도 3은, 본원에서 설명되는 구현들에 따른, 텅스텐 충전 층을 증착하기 위한 방법(300)을 도시하는 흐름도이다. 블록(310)에서, 내부에 피처가 형성된 기판이 프로세싱 챔버에 위치된다. 블록(320)에서, 텅스텐 핵형성 층이 피처에 증착된다. 블록(330)에서, 텅스텐 함유 가스를 사용하여, 텅스텐 핵형성 층 위에 제 1 텅스텐 막이 증착된다. 블록(340)에서, 제 1 텅스텐 막의 일부를 제거하기 위해, 텅스텐 함유 가스를 사용하여, 제 1 텅스텐 막이 에칭된다. 블록(350)에서, 텅스텐 함유 가스를 사용하여, 제 1 텅스텐 막 위에 제 2 텅스텐 막이 증착된다. 블록(360)에서, 전체 원하는 두께의 텅스텐 층이 증착되었는지가 결정된다. 전체 원하는 두께가 달성된 경우에, 프로세스가 종료된다. 전체 원하는 두께가 달성되지 않은 경우에, 에칭-증착 프로세스가 반복될 수 있다.

[0029] 도 4a 내지 도 4f는, 본원에서 설명되는 구현들에 따른, 프로세스(300)의 블록들(310 내지 360)과 같은 경과되는 프로세스 기간들에서의 기판의 개략적인 단면도들이다. 프로세스(300)는 기판 표면 상에 텅스텐 금속화 재료들을 형성하기 위해 활용된다. 일 예에서, 도 4a 내지 도 4f에서 도시된 워크피스(workpiece)(400)는 프로세스(300)에 의해 제조될 수 있거나, 또는 그렇지 않으면 형성될 수 있다.

[0030] 도 4a는, 기판(402) 상에 배치된 유전체 층(410), 및 유전체 층(410) 내에 형성된 또는 그렇지 않으면 포함된 피처(408)를 포함하는 워크피스(400)를 도시한다. 피처(408)는 적어도 하나의 측벽(422) 및 바닥 표면(424)을 갖는다. 예시적인 피처들은, 비아들, 트렌치들, 라인들, 콘택 홀들, 또는 반도체, 솔라(solar) 또는 다른 전자 디바이스들에서 활용되는 다른 피처들, 예컨대 고 종횡비 콘택 플러그들과 같은 피처들을 포함한다. 피처가 비아인 몇몇 구현들에서, 비아는 고 종횡비(예컨대, AR ~ 20 내지 50)를 가질 수 있다. 일반적으로, 기판(402)은 실리콘 기판이거나, 또는 적어도, 실리콘 또는 실리콘-계 재료를 함유한다. 다수의 예들에서, 워크피스(400)는 기판(402)으로서 실리콘 기판 또는 웨이퍼를 갖는 반도체 워크피스이고; 유전체 층(410)은, 적어도 하나의 유전체 재료, 예컨대, 실리콘, 단결정질(monocrystalline) 실리콘, 미정질(microcrystalline) 실리콘, 다결정질(polycrystalline) 실리콘(폴리실리콘), 비정질(amorphous) 실리콘, 수소화(hydrogenated) 비정질 실리콘, 실리콘 산화물 재료들, 이들의 도펀트(dopant) 유도체들, 또는 이들의 조합들을 함유한다.

[0031] 워크피스(400)의 상부 표면(404)은, 그러한 상부 표면(404) 상에 배치된 적어도 하나 또는 그 초과의 오염물들을 가질 수 있다. 워크피스(400)의 상부 표면(404) 상에 배치된 오염물들은, 네이티브(native) 산화물들, 잔여물들, 입자들, 및/또는 다른 오염물들을 포함할 수 있다. 프로세스(300)의 다양한 구현들에서, 워크피스(400)의 상부 표면(404)을 세정하기 위해, 선택적인 프로세스가 활용될 수 있다. 예컨대, 오염물들은, 사전세정(preclean) 프로세스 또는 배면 폴리싱 프로세스와 같은 선택적인 프로세스 동안에, 워크피스(400)의 상부 표면(404)으로부터 제거된다. 도 4a는, 네이티브 산화물들이 없는 것을 포함하여, 오염물들이 없는, 또는 실질적으로 오염물들이 없는, 워크피스(400)의 상부 표면(404)을 도시한다.

[0032] 몇몇 구현들에서, 워크피스(400)의 상부 표면(404)은 사전-세정 프로세스에 노출될 수 있다. 상부 표면(404)은 일반적으로, 그러한 상부 표면(404) 상에 배치된, 실리콘, 폴리실리콘, 또는 실리콘 함유 표면(예컨대, 실리사이드(silicide))을 함유하고, 사전-세정 프로세스 동안에, 사전-세정 용액, 증기, 또는 플라즈마에 노출될 수 있다. 일 구현에서, 상부 표면(404)은, 실란, 디실란, 디보란, 수소, 포스핀(phosphine), 또는 이들의 유도체들과 같은, 가스 형태의 환원제에 노출된다. 캐리어 가스가 환원제와 함께 공동-유동될(co-flowed) 수 있다. 캐리어 가스들은, 수소, 질소, 아르곤, 또는 이들의 조합들을 포함한다. 다른 구현에서, 상부 표면(404)은 플라즈마 사전-세정 프로세스에 노출된다. 플라즈마는 내부에서 생성될 수 있거나(예컨대, 인 시튜(in situ) 플라즈마), 또는 외부에서 생성될 수 있다(예컨대, 원격 플라즈마 시스템). 상부 표면(404)은, 아르곤, 헬륨, 네온, 수소, 질소, 암모니아, 실란, 디실란, 디보란, 또는 이들의 혼합물들을 함유하는, 가스 또는 가스 혼합물로부터 형성된 플라즈마에 노출될 수 있다. 수개의 예들에서, 플라즈마는, 수소와 암모니아 혼합물, 수소와 질소 혼합물, 또는 질소와 암모니아 혼합물로부터 형성될 수 있다.

[0033] 선택적인 사전-세정 프로세스 후에, 도 4b에서 도시된 바와 같이, 기판 상에 배치된 유전체 층 상에 접착(adhesion) 층이 형성될 수 있다. 접착 층(420)은, 유전체 층(410)의 평탄한 상부 표면(404), 피처(408)의 측벽들(422), 및 피처(408)의 바닥 표면(424) 상에 재료의 비교적 균일한 층을 형성한다. 몇몇 구현들에서, 접착 층(420)은, 금속 또는 금속 질화물 재료, 예컨대, 티타늄, 티타늄 질화물, 이들의 합금들, 또는 이들의 조합들을 함유한다. 접착 층(420)을 위한 예시적인 재료들은, 탄탈(Ta), 텅스텐 질화물(WN), 티타늄 질화물(TiN), TiNxSiy, 탄탈 질화물(TaNx), 실리콘 질화물(SiN), 텅스텐(W), CoWP, NiMoP, NiMoB, 루테늄(Ru), RuO2, 몰리브덴(Mo), MoxNy, 및 이들의 조합들을 포함하고, 여기에서, x 및 y는 비-제로(non-zero) 수들이다. 접착 층(420)은, 약 2 Å 내지 약 100 Å의 범위 내의, 더 제한적으로는(narrowly), 약 3 Å 내지 약 80 Å의 범위 내의, 더 제한적으로는, 약 4 Å 내지 약 50 Å의 범위 내의, 더 제한적으로는, 약 5 Å 내지 약 25 Å의 범위 내의, 더 제한적으로는, 약 5 Å 내지 약 20 Å의 범위 내의, 더 제한적으로는, 약 5 Å 내지 약 15 Å의 범위 내의, 그리고 더 제한적으로는, 약 5 Å 내지 약 10 Å의 범위 내의 두께를 가질 수 있다. 접착 층(420)은 일반적으로, 화학 기상 증착(CVD), 원자 층 증착(ALD), 또는 물리 기상 증착(PVD) 프로세스들에 의해 증착된다.

[0034] 프로세스(300)의 블록(320)에서, 도 4c에서 도시된 바와 같이, 접착 층(420) 상에 원하는 두께의 핵형성 층(430)이 증착된다. 핵형성 층(430)은, 후속 막을 위한 성장 사이트(site)로서 작용하는, 텅스텐의 얇은 층일 수 있다. 핵형성 층(430)은, 원자 층 증착(ALD), 종래의 화학 기상 증착(CVD), 또는 펄스(pulsed) 화학 기상 증착(CVD)과 같은 기법들에 의해 증착될 수 있다. 이러한 프로세스는, 도 2에 관하여 위에서 설명된 것과 유사한 CVD 프로세싱 챔버에서 수행될 수 있다. 핵형성 층은, 배리어 층 소킹(soak) 프로세스에 대해 사용된 것과 동일한 프로세싱 챔버에서 증착될 수 있다. 핵형성 층(430)은, 텅스텐, 텅스텐 합금들, 텅스텐-함유 재료들(예컨대, 텅스텐 붕소화물 또는 텅스텐 실리사이드), 및 이들의 조합들을 포함할 수 있다. 핵형성 층(430)은, 약 10 옹스트롬 내지 약 200 옹스트롬, 또는 약 50 옹스트롬 내지 약 150 옹스트롬의 범위에서의 두께로 증착될 수 있다. 핵형성 층은, 도 2에서 도시된 프로세싱 챔버(200)와 같은 프로세싱 챔버 내로, 텅스텐 함유 가스(예컨대, WF6와 같은 텅스텐 할로겐화물 화합물) 및 수소 함유 가스(예컨대, H2, B2H6, 또는 SiH4)를 유동시킴으로써, 증착될 수 있다. 텅스텐 핵형성 층을 증착하기 위한 프로세스들은 추가로, 본원과 양수인이 동일한 미국 특허 번호 제 7,405,158 호에서 설명된다.

[0035] 프로세스(300)의 블록(330)에서, 도 4d에서 도시된 바와 같이, 핵형성 층(430) 위에 벌크 텅스텐 층(460)의 제 1 텅스텐 막(440)이 증착된다. 도 4d에서 도시된 바와 같이, 피처(408)의 측벽들(422)을 따르는 제 1 텅스텐 막(440)의 성장은, 피처(408)의 하부 부분이 피처(408)의 바닥 표면(424)으로부터 완전히 성장되기 전에, 피처의 개구(442)를 차단시키는 경향이 있고, 그에 따라, 피처(408) 내에 공극(444)이 형성된다.

[0036] 일 구현에서, 제 1 텅스텐 막(440)은 핵형성 층(430) 상에 또는 위에 증착될 수 있다. 제 1 텅스텐 막(440)은 일반적으로, 열 CVD, 펄스-CVD, PE-CVD, 또는 펄스 PE-CVD에 의해 형성된다. 제 1 텅스텐 막(440)을 증착하기 위해 사용되는 프로세싱 챔버는 프로세싱 챔버(200)일 수 있다. 제 1 텅스텐 막(440)은, 금속성 텅스텐, 텅스텐 합금들, 텅스텐-함유 재료들(예컨대, 텅스텐 붕소화물, 텅스텐 실리사이드, 또는 텅스텐 인화물), 또는 이들의 조합들을 함유할 수 있다.

[0037] 일 예에서, 제 1 텅스텐 막(440)은, CVD 프로세스 동안에 수소 함유 가스(예컨대, 수소(H2)) 및 텅스텐 함유 가스(예컨대, 텅스텐 육플루오르화물(WF6))에 동시에 노출되는, 워크피스(400) 상의 핵형성 층(430) 상에 또는 위에 증착될 있다. 핵형성 층(430)을 소킹하고, 그러한 핵형성 층(430) 상에 제 1 텅스텐 막(440)을 증착하기 위한 예시적인 프로세스들은 추가로, 본원과 양수인이 동일한 미국 특허 번호 제 6,156,382 호에서 설명된다.

[0038] 제 1 텅스텐 막(440)은, 핵형성 층(430)을 증착하기 위해 사용된 것과 동일한 프로세싱 가스들, 즉, 텅스텐 함유 가스 및 수소 함유 가스들을 사용하여, 증착될 수 있다. 제 1 텅스텐 막(440)은, 핵형성 층(430)과 동일한 프로세싱 챔버, 예컨대 프로세싱 챔버(200)에서 형성될 수 있다.

[0039] 일 구현에서, 핵형성 층(430)의 증착, 및 임의의 후속 퍼징(purging) 또는 포스트 소킹 프로세스(post soak process)들 후에, 기판은, 약 13,560 cm3의 볼륨을 갖는 300 mm 프로세싱 챔버에, 그리고 약 100 ℃ 내지 약 600 ℃의 범위에서의(예컨대, 약 300 ℃ 내지 430 ℃의 범위에서의) 온도를 갖는 페데스탈(pedestal) 상에 위치될 수 있다. 일 예에서, 온도는 약 400 ℃일 수 있다. 제 1 텅스텐 막(440)의 증착은, 약 10 Torr 내지 약 300 Torr의 범위에서의(예컨대, 약 30 Torr 내지 약 100 Torr의 범위에서의) 압력에서의 프로세싱 챔버에서 수행될 수 있다. 일 예에서, 압력은 약 90 Torr일 수 있다. 환원 가스, 예컨대 수소 가스(H2)와 같은 수소 함유 가스가, 1,000 sccm 내지 약 8,000 sccm, 예컨대 5,000 sccm의 연속적인 유량으로 도입될 수 있다. 환원 가스는, 약 0 sccm 내지 약 20,000 sccm의 범위에서의 유량으로, 아르곤(Ar)과 같은 캐리어 가스와 함께 도입될 수 있다. 일 예에서, 아르곤은 11,000 sccm의 총 유량으로 도입될 수 있다. 증착 가스들이 기판의 배면 및 에지와 접촉하는 것을 방지하기 위해, 아르곤의 제 2 유동이, 약 0 sccm 내지 2,000 sccm의 레이트로, 퍼지 가이드(purge guide)(도 2에서는 도시되지 않음)를 통해 유동될 수 있다. 일 예에서, 아르곤 에지 퍼지 유동은 500 sccm일 수 있다. 유사하게, 수소 가스(H2)의 제 2 유동이, 약 0 sccm 내지 6,000 sccm의 레이트로, 퍼지 가이드(도 2에서는 도시되지 않음)를 통해 유동될 수 있다. 일 예에서, 수소 가스 에지 퍼지 유동은 2,500 sccm일 수 있다. 다른 구현에서, 아르곤과 같은 캐리어 가스의 부가적인 유동이, 챔버 가열 엘리먼트들의 배면 상에서의 증착을 방지하기 위해, 바닥 퍼지로서 도입될 수 있다. 일 예에서, 아르곤 바닥 퍼지 유동은 5,000 sccm일 수 있다. 텅스텐-함유 화합물은 텅스텐 육플루오르화물(WF6)일 수 있고, 약 50 sccm 내지 500 sccm의 범위에서의, 예컨대 약 300 sccm 내지 400 sccm의 범위에서의 연속적인 유량으로 도입될 수 있다.

[0040] 제 1 텅스텐 막(440)은, 약 100 Å/분 내지 약 1,200 Å/분, 예컨대 약 500 Å/분 내지 약 800 Å/분의 증착 레이트로 증착될 수 있다. 제 1 텅스텐 막(440)은, 약 10 Å 내지 약 200 Å의 범위 내의, 그리고 더 제한적으로는, 약 20 Å 내지 약 100 Å의 범위 내의 두께를 가질 수 있다.

[0041] 프로세스(300)의 블록(340)에서, 도 4d 및 도 4e에서 도시된 바와 같이, 제 1 텅스텐 막(440)의 일부를 제거하기 위해, 텅스텐 함유 가스를 사용하여, 벌크 텅스텐 층(460)의 제 1 텅스텐 막(440)이 에칭된다. 에칭 프로세스(또한, 에치백 프로세스라고 지칭됨)는, 텅스텐 재료의 추가적인 증착을 위하여, 피처 개구(442)의 일부를 클리어링(clear)하기 위해, 피처(408)의 측벽들(422)로부터 제 1 텅스텐 막(440)의 일부를 제거한다. 에칭 프로세스는 또한, 블록(330)의 텅스텐 증착 프로세스와 동일한 프로세싱 챔버, 예컨대 프로세싱 챔버(200)에서 수행될 수 있다. 에칭 프로세스는 일반적으로, 블록(330)에서 사용된 것과 동일한 텅스텐 함유 가스들을 사용하여 수행된다.

[0042] 일 구현에서, 제 1 텅스텐 막(440)의 증착, 및 임의의 후속 퍼징 또는 포스트 소킹 프로세스들 후에, 플라즈마 에칭 프로세스를 사용하여, 제 1 텅스텐 막(440)이 에칭된다. 플라즈마는, He, Ar, O2, N2, 또는 이들의 조합들과 같은 처리 가스에 RF 전력을 커플링시킴으로써 형성될 수 있다. 플라즈마는 원격 플라즈마 소스(RPS)에 의해 형성될 수 있고, 프로세싱 챔버에 전달될 수 있다.

[0043] 에칭 프로세스 동안에, 페데스탈은, 약 100 ℃ 내지 약 600 ℃의 범위에서의(예컨대, 약 300 ℃ 내지 430 ℃의 범위에서의) 온도를 가질 수 있다. 일 예에서, 온도는 약 400 ℃일 수 있다. 제 1 텅스텐 막(440)의 에칭은, 약 0.1 Torr 내지 약 5 Torr의 범위에서의(예컨대, 약 0.5 Torr 내지 약 2 Torr의 범위에서의) 압력에서의 프로세싱 챔버에서 수행될 수 있다. 일 예에서, 압력은 약 1 Torr일 수 있다. 처리 가스(예컨대, 아르곤(Ar))는, 약 100 sccm 내지 약 3,000 sccm의 범위에서의 유량으로 도입될 수 있다. 일 예에서, 아르곤은 2,000 sccm의 총 유량으로 도입될 수 있다. 증착 가스들이 기판의 배면 및 에지와 접촉하는 것을 방지하기 위해, 아르곤의 제 2 유동이, 약 0 sccm 내지 2,000 sccm의 레이트로, 퍼지 가이드(도 2에서는 도시되지 않음)를 통해 유동될 수 있다. 일 예에서, 아르곤 에지 퍼지 유동은 500 sccm일 수 있다. 유사하게, 수소 가스(H2)의 제 2 유동이, 약 0 sccm 내지 6,000 sccm의 레이트로, 퍼지 가이드(도 2에서는 도시되지 않음)를 통해 유동될 수 있다. 일 예에서, 수소 가스 에지 퍼지 유동은 2,500 sccm일 수 있다. 다른 구현에서, 아르곤과 같은 처리 가스의 부가적인 유동이, 챔버 가열 엘리먼트들의 배면 상에서의 증착을 방지하기 위해, 바닥 퍼지로서 도입될 수 있다. 일 예에서, 아르곤 바닥 퍼지 유동은 5,000 sccm일 수 있다. 텅스텐-함유 화합물은 텅스텐 육플루오르화물(WF6)일 수 있고, 약 1 sccm 내지 150 sccm의 범위에서의, 예컨대 약 3 sccm 내지 100 sccm의 범위에서의 연속적인 유량으로 도입될 수 있다.

[0044] 화살표들(464')은, 원자 불소가 제 1 텅스텐 막(440)의 상단(평탄한) 표면과 충돌하게 하는, 에칭 프로세스 동안의 원자 불소의 방향을 표현한다.

[0045] 처리 가스에 RF 전력을 커플링시킴으로써 플라즈마가 형성되는 구현들에서, 약 10 MHz 내지 약 30 MHz, 예컨대 약 13.56 MHz의 RF 전력 주파수에서의, 50 W 내지 100 W, 예컨대 75 W의 RF 전력이 사용될 수 있다.

[0046] 원격 플라즈마 소스(RPS)에서 플라즈마가 형성되는 구현들에서, 처리 가스 유량(예컨대, 아르곤)이 약 500 sccm 내지 약 6,000 sccm이면서, 전력 인가는, 약 1,000 와트 내지 약 6,000 와트, 예컨대 약 1,000 와트 내지 약 2,000 와트일 수 있다.

[0047] 제 1 텅스텐 막(440)의 부분들은, 약 0.1 Å/초 내지 약 10 Å/초, 예컨대 약 0.5 Å/초 내지 약 3 Å/초의 에칭 레이트로 제거될 수 있다. 에치백 프로세스를 위한 프로세싱 조건들은 전형적으로, 제 1 텅스텐 막(440)으로부터 제 1 텅스텐 막(440)의 돌출 부분(443)이 제거되도록 선택된다.

[0048] 프로세스(300)의 블록(350)에서, 도 4f에서 도시된 바와 같이, 제 1 텅스텐 막(440)의 에칭 후에, 남은 제 1 텅스텐 막(446) 위에 벌크 텅스텐 층(460)의 제 2 텅스텐 막(448)이 증착된다. 벌크 텅스텐 층(460)의 제 2 텅스텐 막(448)은, 블록(330)의 증착 프로세스 및 블록(340)의 에칭 프로세스와 동일한 프로세싱 챔버, 예컨대 프로세싱 챔버(200)에서 증착될 수 있다. 벌크 텅스텐 층(460)의 제 2 텅스텐 막(448)은, 블록(330) 및 블록(340)에서 사용된 것과 동일한 텅스텐 함유 가스들을 사용하여 증착될 수 있다.

[0049] 일 구현에서, 제 1 텅스텐 막(440)의 에칭 후에, 벌크 텅스텐 층(460)의 제 2 텅스텐 막(448)의 증착이 수행된다. 벌크 텅스텐 층(460)의 제 2 텅스텐 막(448)은, 약 100 ℃ 내지 약 600 ℃의 범위에서의(예컨대, 약 300 ℃ 내지 약 430 ℃의 범위에서의) 온도를 갖는 페데스탈 상에서 수행될 수 있다. 일 예에서, 온도는 약 400 ℃일 수 있다. 벌크 텅스텐 층(460)의 제 2 텅스텐 막(448)의 증착은, 약 10 Torr 내지 약 300 Torr의 범위에서의(예컨대, 약 30 Torr 내지 약 100 Torr의 범위에서의) 압력에서의 프로세싱 챔버에서 수행될 수 있다. 일 예에서, 압력은 약 90 Torr일 수 있다. 환원 가스, 예컨대 수소 가스(H2)가, 1,000 sccm 내지 약 8,000 sccm, 예컨대 5,000 sccm의 연속적인 유량으로 도입될 수 있다. 환원 가스는, 약 0 sccm 내지 약 20,000 sccm의 범위에서의 유량으로, 아르곤(Ar)과 같은 캐리어 가스와 함께 도입될 수 있다. 일 예에서, 아르곤은 11,000 sccm의 총 유량으로 도입될 수 있다. 증착 가스들이 기판의 배면 및 에지와 접촉하는 것을 방지하기 위해, 아르곤의 제 2 유동이, 약 0 sccm 내지 2,000 sccm의 레이트로, 퍼지 가이드(도 2에서는 도시되지 않음)를 통해 유동될 수 있다. 일 예에서, 아르곤 에지 퍼지 유동은 500 sccm일 수 있다. 유사하게, 수소 가스(H2)의 제 2 유동이, 약 0 sccm 내지 6,000 sccm의 레이트로, 퍼지 가이드(도 2에서는 도시되지 않음)를 통해 유동될 수 있다. 일 예에서, 수소 가스 에지 퍼지 유동은 2,500 sccm일 수 있다. 다른 구현에서, 아르곤과 같은 캐리어 가스의 부가적인 유동이, 챔버 가열 엘리먼트들의 배면 상에서의 증착을 방지하기 위해, 바닥 퍼지로서 도입될 수 있다. 일 예에서, 아르곤 바닥 퍼지 유동은 5,000 sccm일 수 있다. 텅스텐-함유 화합물은 텅스텐 육플루오르화물(WF6)일 수 있고, 약 50 sccm 내지 500 sccm의 범위에서의, 예컨대 약 300 sccm 내지 400 sccm의 범위에서의 연속적인 유량으로 도입될 수 있다.

[0050] 벌크 텅스텐 층(460)의 제 2 텅스텐 막(448)은, 약 1,200 Å/분 내지 약 3,000 Å/분의 증착 레이트로 증착될 수 있다. 벌크 텅스텐 층(460)의 제 2 텅스텐 막(448)은, 약 1,800 Å/분 내지 약 2,300 Å/분의 증착 레이트로 증착될 수 있다.

[0051] 프로세스(300)의 블록(360)에서, 전체 원하는 두께의 벌크 텅스텐 층(460)이 달성되었는지가 결정된다. 원하는 두께의 벌크 텅스텐 층(460)이 달성된 경우에, 프로세스(300)는 종료된다. 원하는 두께의 벌크 텅스텐 층(460)이 달성되지 않은 경우에, 전술된 증착 및 에칭 프로세스들 중 임의의 것이 다시 수행될 수 있다. 텅스텐 벌크 층의 두께의 결정은, 예컨대 분광 측정(spectroscopic measurement)들과 같은 종래의 프로세스들을 사용하여 수행될 수 있다.

[0052] 프로세스 통합(integration)

[0053] 위에서 설명된 바와 같은, 텅스텐-함유 층 및 배리어 층은, 우수한 막 특성들을 갖는 피처들을 형성하기 위해, 통상적인 핵형성 충전 기법들과 통합되는 경우에, 특정한 유용성을 나타내었다. 통합 스킴(scheme)은, 텅스텐-함유 층들 및 배리어 층들을 증착하기 위해, ALD, CVD, 펄스-CVD 프로세스들, 플라즈마-강화 CVD, 또는 펄스 PE-CVD를 포함할 수 있는 한편, 핵형성 층은 ALD 프로세스에 의해 증착될 수 있다. 그러한 통합 스킴을 수행할 수 있는 통합된 프로세싱 시스템들은, ENDURA®, ENDURA SL®, CENTURA®, 또는 PRODUCER® 프로세싱 시스템들을 포함하고, 이들 각각은, 캘리포니아, 산타클라라에 위치된 어플라이드 머티어리얼스, 인코포레이티드로부터 입수가능하다. 이러한 시스템들 중 임의의 것은, 텅스텐-함유 층 및 배리어 층을 증착하기 위한 적어도 하나의 ALD 챔버, 핵형성 층을 증착하기 위한 적어도 하나의 ALD 또는 펄스-CVD 챔버, 벌크 충전을 증착하기 위한 적어도 하나의 CVD 챔버, 및/또는 부가적인 재료들을 위한 적어도 하나의 PVD 챔버를 포함하도록 구성될 수 있다. 일 구현에서, 하나의 ALD 또는 CVD 챔버가, 텅스텐-함유 층들에 관련된 모든 기상 증착 프로세스들을 수행하도록 구성될 수 있다.

[0054] 도 5는, 본원에서 설명되는 구현들을 수행하기 위해 사용될 수 있는 클러스터 툴(500)의 개략적인 평면도이다. 유사한 멀티-챔버 프로세싱 시스템이, 본원과 양수인이 동일한 미국 특허 번호 제 5,186,718 호에서 개시된다. 프로세싱 시스템(500)은 일반적으로, 프로세싱 시스템(500) 내로 그리고 밖으로의 기판들의 이송을 위한 로드 락 챔버들(502 및 504)을 포함한다. 전형적으로, 프로세싱 시스템(500)이 진공 하에 있기 때문에, 로드 락 챔버들(502 및 504)은, 프로세싱 시스템(500) 내로 도입되는 기판들을 "펌핑 다운(pump down)"할 수 있다. 제 1 로봇(510)은, 하나 또는 그 초과의 기판 프로세싱 챔버들(512, 514, 516, 및 518)(4개가 도시됨)의 제 1 세트와 로드 락 챔버들(502 및 504) 사이에서 기판들을 이송할 수 있다. 각각의 프로세싱 챔버(512, 514, 516, 및 518)는, ALD, CVD, PVD, 에칭, 사전-세정, 탈기(de-gas), 배향(orientation), 또는 다른 기판 프로세스들과 같은 다수의 기판 프로세싱 동작들을 수행하도록 장비될(outfitted) 수 있다. 제 1 로봇(510)은 또한, 하나 또는 그 초과의 이송 챔버들(522 및 524)로/로부터 기판들을 이송한다.

[0055] 이송 챔버들(522 및 524)은, 기판들이 프로세싱 시스템(500) 내에서 이송되게 허용하면서, 초-고 진공 조건들을 유지하기 위해 사용된다. 제 2 로봇(530)은, 하나 또는 그 초과의 프로세싱 챔버들(532, 534, 536, 및 538)의 제 2 세트와 이송 챔버들(522 및 524) 사이에서 기판들을 이송할 수 있다. 프로세싱 챔버들(512, 514, 516, 및 518)과 유사하게, 프로세싱 챔버들(532, 534, 536, 및 538)은, ALD, CVD, PVD, 에칭, 사전-세정, 탈기, 또는 배향과 같은 다양한 기판 프로세싱 동작들을 수행하도록 장비될 수 있다. 프로세싱 챔버들(512, 514, 516, 518, 532, 534, 536, 및 538) 중 임의의 것이, 프로세싱 시스템(500)에 의해 수행될 특정한 프로세스를 위해 필요하지 않은 경우에, 프로세싱 시스템(500)으로부터 제거될 수 있다. 마이크로프로세서 제어기(520)가, 프로세싱 시스템(500)의 모든 양상들을 동작시키기 위해 사용될 수 있다.

[0056] 일 배열에서, 각각의 프로세싱 챔버(532 및 538)는, ALD 챔버, 또는 상이한 화학 화합물을 함유하는 순차적인 층들을 증착하도록 적응된 다른 기상 증착 챔버일 수 있다. 예컨대, 순차적인 층들은, 층, 배리어 층, 및 핵형성 층을 포함할 수 있다. 프로세싱 챔버들(534 및 536)은, 벌크 층을 형성하도록 적응된, ALD 챔버, CVD 챔버, 또는 PVD일 수 있다. 프로세싱 챔버들(512 및 514)은, 유전체 층을 증착하도록 적응된, PVD 챔버, CVD 챔버, 또는 ALD 챔버일 수 있다. 또한, 프로세싱 챔버들(516 및 518)은, 인터커넥트 피처들을 위한 개구들 또는 피처들을 에칭하도록 장비된 에칭 챔버일 수 있다. 프로세싱 시스템(500)의 이러한 하나의 특정한 배열은 본 개시의 몇몇 구현들을 예시하기 위해 제공되고, 본 개시의 다른 구현들의 범위를 제한하기 위해 사용되지 않아야 한다.

[0057] 다른 통합 스킴에서, 하나 또는 그 초과의 ALD 챔버들이 제 1 프로세싱 시스템 상에 통합되는 한편, 하나 또는 그 초과의 벌크 층 증착 챔버들이 제 2 프로세싱 시스템 상에 통합된다. 이러한 구성에서, 기판들은 먼저, 제 1 시스템에서 프로세싱되고, 여기에서, 기판 상에 층, 배리어 층, 및 핵형성 층이 순차적으로 증착된다. 그 후에, 기판들은 제 2 프로세싱 시스템으로 이동되고, 여기에서, 벌크 증착이 발생한다.

[0058] 또 다른 통합된 시스템에서, 시스템은, 단일 챔버에서, 핵형성 증착, 뿐만 아니라, 벌크 충전 증착을 포함할 수 있다. ALD 모드, 뿐만 아니라, 종래의 CVD 모드 양자 모두에서 동작하도록 구성된 챔버가, 본원에서 설명되는 프로세스들에서 사용될 수 있다. 그러한 챔버의 일 예는, 본원과 양수인이 동일한 미국 특허 번호 제 6,878,206 호에서 설명된다.

[0059] 본원에서 설명되는, WF6에 의한 증착-에칭-증착 프로세스를 사용하는 특정한 구현들에서, 단일 챔버 솔루션(solution)에 의해, 심리스 갭-충전이 달성되었다.

[0060] 전술한 바가 본 개시의 구현들에 관한 것이지만, 본 개시의 다른 그리고 추가적인 구현들이, 본 개시의 기본적인 범위로부터 벗어나지 않고 고안될 수 있고, 본 개시의 범위는 다음의 청구항들에 의해 결정된다.

Claims (15)

- 기판 상에 텅스텐 막을 증착하기 위한 방법으로서,

기판 프로세싱 챔버에, 피처(feature)가 내부에 형성된 기판을 위치시키는 단계 ― 상기 피처는 적어도 하나의 측벽 및 바닥 표면에 의해 정의됨 ―;

상기 피처 위에 제 1 텅스텐 막을 증착하기 위해, 상기 프로세싱 챔버에 텅스텐 할로겐화물 화합물 및 수소 함유 가스의 연속적인 유동을 도입함으로써, 벌크 텅스텐 층의 상기 제 1 텅스텐 막을 증착하는 단계;

활성화된 처리 가스 및 상기 텅스텐 할로겐화물 화합물의 연속적인 유동에 상기 제 1 텅스텐 막을 노출시킴으로써, 상기 제 1 텅스텐 막의 일부를 제거하기 위해, 플라즈마 처리를 사용하여, 상기 벌크 텅스텐 층의 상기 제 1 텅스텐 막을 에칭하는 단계; 및

상기 제 1 텅스텐 막 위에 제 2 텅스텐 막을 증착하기 위해, 상기 프로세싱 챔버에 상기 텅스텐 할로겐화물 화합물 및 상기 수소 함유 가스의 연속적인 유동을 도입함으로써, 상기 벌크 텅스텐 층의 상기 제 2 텅스텐 막을 증착하는 단계

를 포함하는,

텅스텐 막을 증착하기 위한 방법. - 제 1 항에 있어서,

상기 텅스텐 할로겐화물 화합물은, 텅스텐 육플루오르화물(WF6) 및 텅스텐 육염화물(WCl6)로 구성된 그룹으로부터 선택되는,

텅스텐 막을 증착하기 위한 방법. - 제 2 항에 있어서,

상기 수소 함유 가스는 수소(H2)인,

텅스텐 막을 증착하기 위한 방법. - 제 3 항에 있어서,

상기 활성화된 처리 가스는 아르곤 가스를 포함하는,

텅스텐 막을 증착하기 위한 방법. - 제 4 항에 있어서,

상기 활성화된 처리 가스는 상기 기판 프로세싱 챔버에서 인-시튜(in-situ)로 형성되는,

텅스텐 막을 증착하기 위한 방법. - 제 4 항에 있어서,

상기 활성화된 처리 가스는, 원격 플라즈마 소스를 사용하여 형성되는,

텅스텐 막을 증착하기 위한 방법. - 제 6 항에 있어서,

상기 피처는, 상기 기판 상에 형성된 유전체 층의 표면에 그리고 상기 유전체 층의 표면 아래에 형성되는,

텅스텐 막을 증착하기 위한 방법. - 제 1 항에 있어서,

상기 피처의 상기 바닥 표면 및 상기 적어도 하나의 측벽 위에 접착(adhesion) 층이 형성되는,

텅스텐 막을 증착하기 위한 방법. - 제 8 항에 있어서,

상기 접착 층 위에 핵형성(nucleation) 층이 형성되는,

텅스텐 막을 증착하기 위한 방법. - 제 1 항에 있어서,

상기 제 1 텅스텐 막 및 상기 제 2 텅스텐 막은, 열 화학 기상 증착(CVD) 프로세스를 사용하여 증착되는,

텅스텐 막을 증착하기 위한 방법. - 제 1 항에 있어서,

상기 제 1 텅스텐 막의 일부를 제거하기 위해, 플라즈마 처리를 사용하여, 벌크 텅스텐 층의 상기 제 1 텅스텐 막을 에칭하는 단계는, 상기 프로세싱 챔버에서 수행되는,

텅스텐 막을 증착하기 위한 방법. - 제 1 항에 있어서,

상기 피처에 의해 생성된, 상기 기판의 표면에서의 갭(gap)에 걸친 공칭(nominal) 최소 치수는, 32 nm 또는 그 미만인,

텅스텐 막을 증착하기 위한 방법. - 제 1 항에 있어서,

상기 피처는, 콘택(contact), 비아(via), 트렌치(trench), 및 라인(line)으로부터 선택된 고 종횡비 피처인,

텅스텐 막을 증착하기 위한 방법. - 기판 상에 텅스텐 막을 증착하기 위한 방법으로서,

기판 프로세싱 챔버에, 피처가 내부에 형성된 기판을 위치시키는 단계 ― 상기 피처는 적어도 하나의 측벽 및 바닥 표면에 의해 정의됨 ―;

상기 피처 위에 제 1 텅스텐 막을 증착하기 위해, 상기 프로세싱 챔버에 텅스텐 할로겐화물 화합물 및 수소 함유 가스의 연속적인 유동을 도입함으로써, 벌크 텅스텐 층의 상기 제 1 텅스텐 막을 증착하는 단계;

활성화된 처리 가스 및 상기 텅스텐 할로겐화물 화합물의 연속적인 유동에 상기 제 1 텅스텐 막을 노출시킴으로써, 상기 제 1 텅스텐 막의 일부를 제거하기 위해, 플라즈마 처리를 사용하여, 상기 벌크 텅스텐 층의 상기 제 1 텅스텐 막을 에칭하는 단계; 및

상기 제 1 텅스텐 막 위에 제 2 텅스텐 막을 증착하기 위해, 상기 프로세싱 챔버에 상기 텅스텐 할로겐화물 화합물 및 수소 함유 가스의 연속적인 유동을 도입함으로써, 상기 벌크 텅스텐 층의 상기 제 2 텅스텐 막을 증착하는 단계

를 포함하며,

상기 제 1 텅스텐 막의 일부는, 약 0.5 Å/초 내지 약 3 Å/초의 범위에서의 에칭 레이트로 제거되는,

텅스텐 막을 증착하기 위한 방법. - 제 14 항에 있어서,

상기 텅스텐 할로겐화물 화합물은, 텅스텐 육플루오르화물(WF6) 및 텅스텐 육염화물(WCl6)로 구성된 그룹으로부터 선택되는,

텅스텐 막을 증착하기 위한 방법.

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201361866665P | 2013-08-16 | 2013-08-16 | |

| US61/866,665 | 2013-08-16 | ||

| PCT/US2014/047618 WO2015023404A1 (en) | 2013-08-16 | 2014-07-22 | Tungsten deposition with tungsten hexafluoride (wf6) etchback |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20160044004A true KR20160044004A (ko) | 2016-04-22 |

| KR102291990B1 KR102291990B1 (ko) | 2021-08-19 |

Family

ID=52467136

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020167006832A KR102291990B1 (ko) | 2013-08-16 | 2014-07-22 | 텅스텐 육플루오르화물(wf6) 에치백을 이용하여 텅스텐 막을 증착하기 위한 방법 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9748105B2 (ko) |

| KR (1) | KR102291990B1 (ko) |

| CN (1) | CN105453230B (ko) |

| TW (1) | TWI629373B (ko) |

| WO (1) | WO2015023404A1 (ko) |

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20200000477A (ko) * | 2017-05-25 | 2020-01-02 | 어플라이드 머티어리얼스, 인코포레이티드 | 고압 처리에 의한 텅스텐 탈플루오린화 |

| WO2021194768A1 (en) * | 2020-03-27 | 2021-09-30 | Lam Research Corporation | Feature fill with nucleation inhibition |

| US11177128B2 (en) | 2017-09-12 | 2021-11-16 | Applied Materials, Inc. | Apparatus and methods for manufacturing semiconductor structures using protective barrier layer |

| US11361978B2 (en) | 2018-07-25 | 2022-06-14 | Applied Materials, Inc. | Gas delivery module |

| US11462417B2 (en) | 2017-08-18 | 2022-10-04 | Applied Materials, Inc. | High pressure and high temperature anneal chamber |

| US11527421B2 (en) | 2017-11-11 | 2022-12-13 | Micromaterials, LLC | Gas delivery system for high pressure processing chamber |

| US11581183B2 (en) | 2018-05-08 | 2023-02-14 | Applied Materials, Inc. | Methods of forming amorphous carbon hard mask layers and hard mask layers formed therefrom |

| US11610773B2 (en) | 2017-11-17 | 2023-03-21 | Applied Materials, Inc. | Condenser system for high pressure processing system |

| US11694912B2 (en) | 2017-08-18 | 2023-07-04 | Applied Materials, Inc. | High pressure and high temperature anneal chamber |

| US11749555B2 (en) | 2018-12-07 | 2023-09-05 | Applied Materials, Inc. | Semiconductor processing system |

| US11881411B2 (en) | 2018-03-09 | 2024-01-23 | Applied Materials, Inc. | High pressure annealing process for metal containing materials |

| US11901222B2 (en) | 2020-02-17 | 2024-02-13 | Applied Materials, Inc. | Multi-step process for flowable gap-fill film |

| US11901227B2 (en) | 2014-09-30 | 2024-02-13 | Lam Research Corporation | Feature fill with nucleation inhibition |

| US11978666B2 (en) | 2018-12-05 | 2024-05-07 | Lam Research Corporation | Void free low stress fill |

Families Citing this family (58)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11437269B2 (en) | 2012-03-27 | 2022-09-06 | Novellus Systems, Inc. | Tungsten feature fill with nucleation inhibition |

| US9169556B2 (en) * | 2012-10-11 | 2015-10-27 | Applied Materials, Inc. | Tungsten growth modulation by controlling surface composition |

| JP6297884B2 (ja) * | 2014-03-28 | 2018-03-20 | 東京エレクトロン株式会社 | タングステン膜の成膜方法 |

| US20150348840A1 (en) * | 2014-05-31 | 2015-12-03 | Lam Research Corporation | Methods of filling high aspect ratio features with fluorine free tungsten |

| US9953984B2 (en) | 2015-02-11 | 2018-04-24 | Lam Research Corporation | Tungsten for wordline applications |

| US20160300731A1 (en) * | 2015-04-10 | 2016-10-13 | Applied Materials, Inc. | Methods of etchback profile tuning |

| US9978605B2 (en) | 2015-05-27 | 2018-05-22 | Lam Research Corporation | Method of forming low resistivity fluorine free tungsten film without nucleation |

| KR102365114B1 (ko) | 2015-08-28 | 2022-02-21 | 삼성전자주식회사 | 반도체 장치 및 그 제조 방법 |

| KR102447489B1 (ko) | 2015-09-02 | 2022-09-27 | 삼성전자주식회사 | 반도체 메모리 소자 |

| WO2016172740A2 (en) * | 2015-11-10 | 2016-10-27 | L'air Liquide, Societe Anonyme Pour L'etude Et L'exploitation Des Procedes Georges Claude | Etching reactants and plasma-free oxide etching processes using the same |

| US9449921B1 (en) | 2015-12-15 | 2016-09-20 | International Business Machines Corporation | Voidless contact metal structures |

| US9673058B1 (en) * | 2016-03-14 | 2017-06-06 | Lam Research Corporation | Method for etching features in dielectric layers |

| KR102441431B1 (ko) * | 2016-06-06 | 2022-09-06 | 어플라이드 머티어리얼스, 인코포레이티드 | 표면을 갖는 기판을 프로세싱 챔버에 포지셔닝하는 단계를 포함하는 프로세싱 방법 |

| US10224224B2 (en) | 2017-03-10 | 2019-03-05 | Micromaterials, LLC | High pressure wafer processing systems and related methods |

| US11404313B2 (en) | 2017-04-26 | 2022-08-02 | Applied Materials, Inc. | Selective tungsten deposition at low temperatures |

| CN110678973B (zh) | 2017-06-02 | 2023-09-19 | 应用材料公司 | 碳化硼硬掩模的干式剥除 |

| WO2018234567A1 (en) * | 2017-06-23 | 2018-12-27 | Merck Patent Gmbh | ATOMIC LAYER DEPOSITION METHODS FOR SELECTIVE FILM GROWTH |

| US10269571B2 (en) | 2017-07-12 | 2019-04-23 | Applied Materials, Inc. | Methods for fabricating nanowire for semiconductor applications |

| US10179941B1 (en) | 2017-07-14 | 2019-01-15 | Applied Materials, Inc. | Gas delivery system for high pressure processing chamber |

| US10618805B2 (en) | 2017-09-22 | 2020-04-14 | Applied Materials, Inc. | Method to reduce pore diameter using atomic layer deposition and etching |

| DE102017216937A1 (de) * | 2017-09-25 | 2019-03-28 | Robert Bosch Gmbh | Verfahren zum Herstellen zumindest einer Durchkontaktierung in einem Wafer |

| US10847374B2 (en) | 2017-10-31 | 2020-11-24 | Lam Research Corporation | Method for etching features in a stack |

| US10643867B2 (en) | 2017-11-03 | 2020-05-05 | Applied Materials, Inc. | Annealing system and method |

| US10332888B2 (en) * | 2017-11-13 | 2019-06-25 | United Microelectronics Corp. | Memory devices and method of manufacturing the same |

| SG11202003438QA (en) | 2017-11-16 | 2020-05-28 | Applied Materials Inc | High pressure steam anneal processing apparatus |

| WO2019103995A1 (en) * | 2017-11-22 | 2019-05-31 | Applied Materials, Inc. | Methods of reducing or eliminating defects in tungsten film |

| JP7018748B2 (ja) * | 2017-11-28 | 2022-02-14 | 東京エレクトロン株式会社 | 成膜方法及び成膜条件の算出方法 |

| JP7299898B2 (ja) | 2018-01-24 | 2023-06-28 | アプライド マテリアルズ インコーポレイテッド | 高圧アニールを用いたシーム修復 |

| US10361092B1 (en) | 2018-02-23 | 2019-07-23 | Lam Research Corporation | Etching features using metal passivation |

| JP7023150B2 (ja) * | 2018-03-26 | 2022-02-21 | 東京エレクトロン株式会社 | タングステン膜の成膜方法及び制御装置 |

| US10714331B2 (en) | 2018-04-04 | 2020-07-14 | Applied Materials, Inc. | Method to fabricate thermally stable low K-FinFET spacer |

| US11549175B2 (en) | 2018-05-03 | 2023-01-10 | Lam Research Corporation | Method of depositing tungsten and other metals in 3D NAND structures |

| US10566188B2 (en) | 2018-05-17 | 2020-02-18 | Applied Materials, Inc. | Method to improve film stability |

| US10704141B2 (en) | 2018-06-01 | 2020-07-07 | Applied Materials, Inc. | In-situ CVD and ALD coating of chamber to control metal contamination |

| US10515821B1 (en) | 2018-06-26 | 2019-12-24 | Lam Research Corporation | Method of achieving high selectivity for high aspect ratio dielectric etch |

| US10675581B2 (en) | 2018-08-06 | 2020-06-09 | Applied Materials, Inc. | Gas abatement apparatus |

| CN110875245B (zh) * | 2018-09-04 | 2023-06-16 | 北京北方华创微电子装备有限公司 | 用于填充孔洞或沟槽的薄膜沉积方法 |

| US10741407B2 (en) | 2018-10-19 | 2020-08-11 | Lam Research Corporation | Reduction of sidewall notching for high aspect ratio 3D NAND etch |

| KR102528076B1 (ko) | 2018-10-30 | 2023-05-03 | 어플라이드 머티어리얼스, 인코포레이티드 | 반도체 응용들을 위한 구조를 식각하기 위한 방법들 |

| CN111162039A (zh) * | 2018-11-08 | 2020-05-15 | 长鑫存储技术有限公司 | 金属导电结构及半导体器件的制备方法 |

| JP2022507390A (ja) | 2018-11-16 | 2022-01-18 | アプライド マテリアルズ インコーポレイテッド | 強化拡散プロセスを使用する膜の堆積 |

| CN113366144B (zh) | 2019-01-28 | 2023-07-07 | 朗姆研究公司 | 金属膜的沉积 |

| US11821071B2 (en) | 2019-03-11 | 2023-11-21 | Lam Research Corporation | Precursors for deposition of molybdenum-containing films |

| US11189633B2 (en) | 2019-03-21 | 2021-11-30 | Samsung Electronics Co., Ltd. | Semiconductor device and apparatus of manufacturing the same |

| KR20220082023A (ko) * | 2019-10-15 | 2022-06-16 | 램 리써치 코포레이션 | 몰리브덴 충진 |

| WO2021117368A1 (ja) * | 2019-12-09 | 2021-06-17 | 東京エレクトロン株式会社 | エッチング方法およびエッチング装置 |

| CN114787972A (zh) * | 2019-12-13 | 2022-07-22 | 朗姆研究公司 | 用于在弓形控制和掩模选择之间取得平衡的多态脉冲化 |

| CN115244663A (zh) * | 2020-02-28 | 2022-10-25 | 朗姆研究公司 | 高深宽比3d nand蚀刻的侧壁凹陷的减少 |

| TW202206634A (zh) * | 2020-06-30 | 2022-02-16 | 美商應用材料股份有限公司 | 在低溫下的選擇性鎢沉積 |

| US11377733B2 (en) * | 2020-08-07 | 2022-07-05 | Sandisk Technologies Llc | Fluorine-free tungsten deposition process employing in-situ oxidation and apparatuses for effecting the same |

| US11749564B2 (en) | 2020-09-22 | 2023-09-05 | Applied Materials, Inc. | Techniques for void-free material depositions |

| KR20230104542A (ko) * | 2020-11-20 | 2023-07-10 | 램 리써치 코포레이션 | 텅스텐 저 저항 펄싱된 cvd |

| US11515200B2 (en) * | 2020-12-03 | 2022-11-29 | Applied Materials, Inc. | Selective tungsten deposition within trench structures |

| CN116601742A (zh) * | 2020-12-17 | 2023-08-15 | 株式会社国际电气 | 半导体装置的制造方法、程序以及基板处理装置 |

| WO2022232997A1 (en) * | 2021-05-06 | 2022-11-10 | Applied Materials, Inc. | Processing system and methods to improve productivity of void-free and seam-free tungsten gapfill process |

| US20230008315A1 (en) * | 2021-07-09 | 2023-01-12 | Taiwan Semiconductor Manufacturing Co., Ltd. | Conductive Features of Semiconductor Devices and Methods of Forming the Same |

| CN114250444A (zh) * | 2021-12-01 | 2022-03-29 | 安徽光智科技有限公司 | 一种等离子体辅助化学气相沉积高纯钨溅射靶材的方法 |

| CN115831867B (zh) * | 2023-02-24 | 2023-06-27 | 粤芯半导体技术股份有限公司 | 半导体器件中的钨填充方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20060072521A (ko) * | 2004-12-23 | 2006-06-28 | 주식회사 하이닉스반도체 | 반도체 소자의 제조방법 |

| KR20110014069A (ko) * | 2009-08-04 | 2011-02-10 | 노벨러스 시스템즈, 인코포레이티드 | 고애스펙트비의 특징부에 대한 텅스텐 증착 방법 및 장치 |

| KR20130006314A (ko) * | 2011-07-06 | 2013-01-16 | 도쿄엘렉트론가부시키가이샤 | 텅스텐 막의 성막 방법 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5186718A (en) | 1989-05-19 | 1993-02-16 | Applied Materials, Inc. | Staged-vacuum wafer processing system and method |

| US6093645A (en) * | 1997-02-10 | 2000-07-25 | Tokyo Electron Limited | Elimination of titanium nitride film deposition in tungsten plug technology using PE-CVD-TI and in-situ plasma nitridation |

| US6156382A (en) | 1997-05-16 | 2000-12-05 | Applied Materials, Inc. | Chemical vapor deposition process for depositing tungsten |

| US6878206B2 (en) | 2001-07-16 | 2005-04-12 | Applied Materials, Inc. | Lid assembly for a processing system to facilitate sequential deposition techniques |

| KR100440260B1 (ko) * | 2001-12-19 | 2004-07-15 | 주식회사 하이닉스반도체 | 반도체 소자의 비트라인 형성 방법 |

| US20030203616A1 (en) * | 2002-04-24 | 2003-10-30 | Applied Materials, Inc. | Atomic layer deposition of tungsten barrier layers using tungsten carbonyls and boranes for copper metallization |

| KR100528073B1 (ko) * | 2003-04-07 | 2005-11-15 | 동부아남반도체 주식회사 | 반도체소자 제조방법 |

| US20080311711A1 (en) | 2007-06-13 | 2008-12-18 | Roland Hampp | Gapfill for metal contacts |

| KR101275025B1 (ko) | 2007-07-12 | 2013-06-14 | 삼성전자주식회사 | 반도체 소자용 배선 구조물 및 이의 형성방법 |

| US8058170B2 (en) * | 2008-06-12 | 2011-11-15 | Novellus Systems, Inc. | Method for depositing thin tungsten film with low resistivity and robust micro-adhesion characteristics |

| US20100072623A1 (en) * | 2008-09-19 | 2010-03-25 | Advanced Micro Devices, Inc. | Semiconductor device with improved contact plugs, and related fabrication methods |

| US20100144140A1 (en) * | 2008-12-10 | 2010-06-10 | Novellus Systems, Inc. | Methods for depositing tungsten films having low resistivity for gapfill applications |

| KR101263856B1 (ko) | 2008-12-31 | 2013-05-13 | 어플라이드 머티어리얼스, 인코포레이티드 | 비저항이 감소되고 표면 형태가 개선된 텅스텐 필름을 증착하는 방법 |

| JP5550843B2 (ja) * | 2009-03-19 | 2014-07-16 | ラピスセミコンダクタ株式会社 | 半導体装置の製造方法 |

| US8865594B2 (en) | 2011-03-10 | 2014-10-21 | Applied Materials, Inc. | Formation of liner and barrier for tungsten as gate electrode and as contact plug to reduce resistance and enhance device performance |

| TWI602283B (zh) * | 2012-03-27 | 2017-10-11 | 諾發系統有限公司 | 鎢特徵部塡充 |

-

2014

- 2014-07-22 KR KR1020167006832A patent/KR102291990B1/ko active IP Right Grant

- 2014-07-22 US US14/337,908 patent/US9748105B2/en active Active

- 2014-07-22 WO PCT/US2014/047618 patent/WO2015023404A1/en active Application Filing

- 2014-07-22 CN CN201480043646.6A patent/CN105453230B/zh active Active

- 2014-08-14 TW TW103127945A patent/TWI629373B/zh active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20060072521A (ko) * | 2004-12-23 | 2006-06-28 | 주식회사 하이닉스반도체 | 반도체 소자의 제조방법 |

| KR20110014069A (ko) * | 2009-08-04 | 2011-02-10 | 노벨러스 시스템즈, 인코포레이티드 | 고애스펙트비의 특징부에 대한 텅스텐 증착 방법 및 장치 |

| KR20130006314A (ko) * | 2011-07-06 | 2013-01-16 | 도쿄엘렉트론가부시키가이샤 | 텅스텐 막의 성막 방법 |

Cited By (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11901227B2 (en) | 2014-09-30 | 2024-02-13 | Lam Research Corporation | Feature fill with nucleation inhibition |

| KR20200000477A (ko) * | 2017-05-25 | 2020-01-02 | 어플라이드 머티어리얼스, 인코포레이티드 | 고압 처리에 의한 텅스텐 탈플루오린화 |

| US11705337B2 (en) | 2017-05-25 | 2023-07-18 | Applied Materials, Inc. | Tungsten defluorination by high pressure treatment |

| KR20220025181A (ko) * | 2017-05-25 | 2022-03-03 | 어플라이드 머티어리얼스, 인코포레이티드 | 고압 처리에 의한 텅스텐 탈플루오린화를 위한 장치 |

| US11469113B2 (en) | 2017-08-18 | 2022-10-11 | Applied Materials, Inc. | High pressure and high temperature anneal chamber |

| US11462417B2 (en) | 2017-08-18 | 2022-10-04 | Applied Materials, Inc. | High pressure and high temperature anneal chamber |

| US11694912B2 (en) | 2017-08-18 | 2023-07-04 | Applied Materials, Inc. | High pressure and high temperature anneal chamber |

| US11177128B2 (en) | 2017-09-12 | 2021-11-16 | Applied Materials, Inc. | Apparatus and methods for manufacturing semiconductor structures using protective barrier layer |

| US11756803B2 (en) | 2017-11-11 | 2023-09-12 | Applied Materials, Inc. | Gas delivery system for high pressure processing chamber |

| US11527421B2 (en) | 2017-11-11 | 2022-12-13 | Micromaterials, LLC | Gas delivery system for high pressure processing chamber |

| US11610773B2 (en) | 2017-11-17 | 2023-03-21 | Applied Materials, Inc. | Condenser system for high pressure processing system |

| US11881411B2 (en) | 2018-03-09 | 2024-01-23 | Applied Materials, Inc. | High pressure annealing process for metal containing materials |

| US11581183B2 (en) | 2018-05-08 | 2023-02-14 | Applied Materials, Inc. | Methods of forming amorphous carbon hard mask layers and hard mask layers formed therefrom |

| US11361978B2 (en) | 2018-07-25 | 2022-06-14 | Applied Materials, Inc. | Gas delivery module |

| US11978666B2 (en) | 2018-12-05 | 2024-05-07 | Lam Research Corporation | Void free low stress fill |

| US11749555B2 (en) | 2018-12-07 | 2023-09-05 | Applied Materials, Inc. | Semiconductor processing system |

| US11901222B2 (en) | 2020-02-17 | 2024-02-13 | Applied Materials, Inc. | Multi-step process for flowable gap-fill film |

| WO2021194768A1 (en) * | 2020-03-27 | 2021-09-30 | Lam Research Corporation | Feature fill with nucleation inhibition |

Also Published As

| Publication number | Publication date |

|---|---|

| US9748105B2 (en) | 2017-08-29 |

| US20150050807A1 (en) | 2015-02-19 |

| WO2015023404A1 (en) | 2015-02-19 |

| CN105453230B (zh) | 2019-06-14 |

| TW201510267A (zh) | 2015-03-16 |

| CN105453230A (zh) | 2016-03-30 |

| KR102291990B1 (ko) | 2021-08-19 |

| TWI629373B (zh) | 2018-07-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR102291990B1 (ko) | 텅스텐 육플루오르화물(wf6) 에치백을 이용하여 텅스텐 막을 증착하기 위한 방법 | |

| JP6727359B2 (ja) | シームレスのコバルト間隙充填を可能にする方法 | |

| US10269633B2 (en) | Method of enabling seamless cobalt gap-fill | |

| US11024537B2 (en) | Methods and apparatus for hybrid feature metallization | |

| US20200251340A1 (en) | Methods and apparatus for filling a feature disposed in a substrate | |

| US10950500B2 (en) | Methods and apparatus for filling a feature disposed in a substrate | |

| TWI737601B (zh) | 回蝕輪廓調整的方法 | |

| US20230317458A1 (en) | Gap fill enhancement with thermal etch |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |