KR20120037520A - 수직 채널 트랜지스터를 구비하는 반도체 장치 및 그 제조 방법 - Google Patents

수직 채널 트랜지스터를 구비하는 반도체 장치 및 그 제조 방법 Download PDFInfo

- Publication number

- KR20120037520A KR20120037520A KR1020100098119A KR20100098119A KR20120037520A KR 20120037520 A KR20120037520 A KR 20120037520A KR 1020100098119 A KR1020100098119 A KR 1020100098119A KR 20100098119 A KR20100098119 A KR 20100098119A KR 20120037520 A KR20120037520 A KR 20120037520A

- Authority

- KR

- South Korea

- Prior art keywords

- region

- patterns

- pattern

- gate

- active

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/05—Making the transistor

- H10B12/053—Making the transistor the transistor being at least partially in a trench in the substrate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/315—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor with the capacitor higher than a bit line

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/34—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells the transistor being at least partially in a trench in the substrate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/025—Manufacture or treatment of FETs having insulated gates [IGFET] of vertical IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/63—Vertical IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

- H10D84/83—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET]

- H10D84/85—Complementary IGFETs, e.g. CMOS

Landscapes

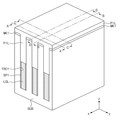

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

Description

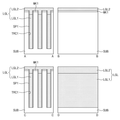

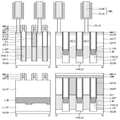

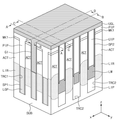

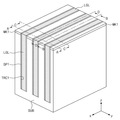

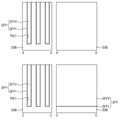

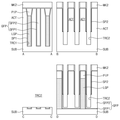

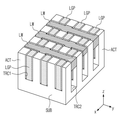

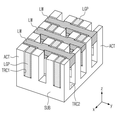

도 2a 내지 도 2c는 본 발명의 실시예들에 따른 반도체 장치들을 보다 구체적으로 설명하기 위한 도면들이다.

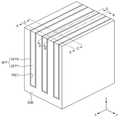

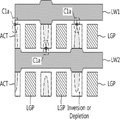

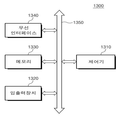

도 3은 본 발명의 실시예들에 따른 반도체 장치의 일 측면을 도시하는 도식도(schematic diagram)이다.

도 4는 본 발명의 제 1 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다.

도 5a 내지 도 19a는 본 발명의 제 1 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다.

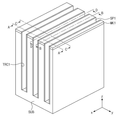

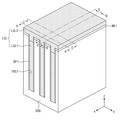

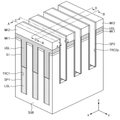

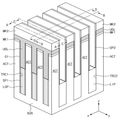

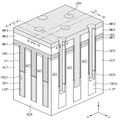

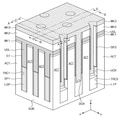

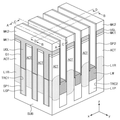

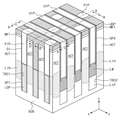

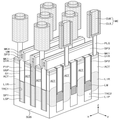

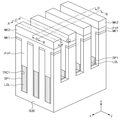

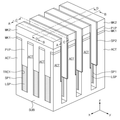

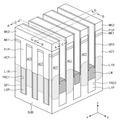

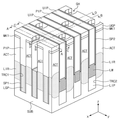

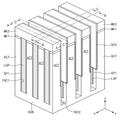

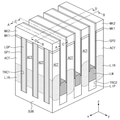

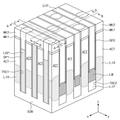

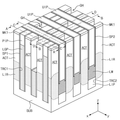

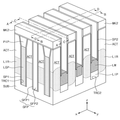

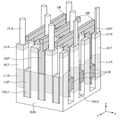

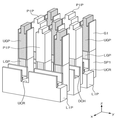

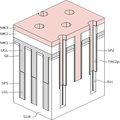

도 5b 내지 도 19b는 본 발명의 제 1 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

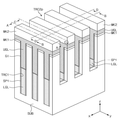

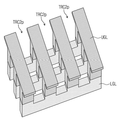

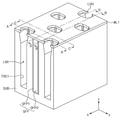

도 20 내지 도 22는 본 발명의 제 1 실시예에 따른 반도체 장치의 제조 방법에서의 일부 특징들을 예시적으로 그리고 보다 명확하게 보여주기 위해 제공되는 사시도들이다.

도 23는 본 발명의 제 2 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다.

도 24a 내지 도 31a는 본 발명의 제 2 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다.

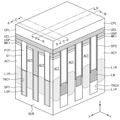

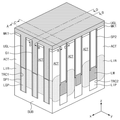

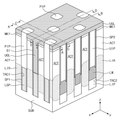

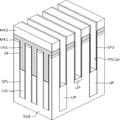

도 24b 내지 도 31b는 본 발명의 제 2 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

도 32는 본 발명의 제 3 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다.

도 33a 내지 도 40a는 본 발명의 제 3 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다.

도 33b 내지 도 40b는 본 발명의 제 3 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

도 41는 본 발명의 제 4 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다.

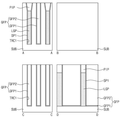

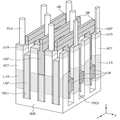

도 42a 내지 도 46a는 본 발명의 제 4 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다.

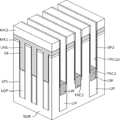

도 42b 내지 도 46b는 본 발명의 제 4 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

도 47는 본 발명의 제 5 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 순서도이다.

도 48a 내지 도 56a는 본 발명의 제 5 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 단면도들이다.

도 48b 내지 도 56b는 본 발명의 제 5 실시예에 따른 반도체 장치의 제조 방법을 설명하기 위한 사시도들이다.

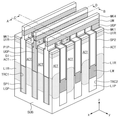

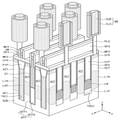

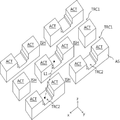

도 57 내지 도 67은 본 발명의 기술적 사상에 따른 반도체 장치들의 일 측면을 예시적으로 보여주는 사시도들이다.

도 68 내지 도 72는 본 발명의 실시예들에 따른 반도체 장치의 다른 측면을 예시적으로 도시하는 사시도들이다.

도 73 및 도 74는 본 발명의 일 측면을 설명하기 위한 평면도들이다.

도 75 내지 도 79는 본 발명의 변형된 실시예에 따른 반도체 장치의 제조 방법을 보여주는 사시도들이다.

도 80 및 도 81은 도 75 내지 도 79를 참조하여 설명된 실시예에 따른 반도체 장치의 평면도 및 사시도이다.

도 82 및 도 83는 본 발명의 실시예들에 따른 수직 채널 트랜지스터들을 포함하는 전자 장치들을 도식적으로 설명하기 위한 도면들이다.

TRC1: 제 1 트렌치 TRC2: 제 2 트렌치

LGL: 하부 게이트막 UGL: 상부 게이트막

LGP: 하부 게이트 패턴 UGP: 상부 게이트 패턴

GI: 게이트 절연막 PIP: 플러그 절연 패턴

LIP: 하부 절연 패턴 UIP: 상부 절연 패턴

JDR: 접합 정의 영역 UCR: 언더컷 영역

LIR: 하부 불순물 영역 UIR: 상부 불순물 영역

LW: 하부 배선 UW: 상부 배선

UCL: 상부 도전막 CPL: 캐핑

PLG: 플러그 CLE: 커패시터 하부 전극

CUE: 커패시터 상부 전극 ME: 메모리 요소

MK1/MK2/MK3/MK4: 제 1 내지 제 4 마스크 패턴

SP1/SP2/SP3: 제 1 내지 제 3 스페이서

Claims (30)

- 제 1 전계효과 트랜지스터 및 제 2 전계효과 트랜지스터를 포함하되,

상기 제 1 전계효과 트랜지스터의 채널 영역은 상기 제 2 전계효과 트랜지스터의 소오스 전극을 구성하고,

상기 제 2 전계효과 트랜지스터의 채널 영역은 상기 제 1 전계효과 트랜지스터의 드레인 전극을 구성하되,

상기 제 1 및 제 2 전계효과 트랜지스터들의 채널 영역들은 직접 접촉하는 것을 반도체 장치. - 청구항 1에 있어서,

상기 반도체 장치는 차례로 배열된 제 1, 제 2, 제 3 및 제 4 영역들을 포함하는 활성 패턴을 포함하고, 상기 제 1 및 제 3 영역들은 같은 도전형이고, 상기 제 2 및 제 4 영역들은 같은 도전형이고, 상기 제 1 영역과 상기 제 2 영역은 서로 다른 도전형이되,

상기 제 1, 제 2 및 제 3 영역들은 차례로 상기 제 1 전계효과 트랜지스터의 소오스 전극, 채널 영역 및 드레인 전극으로 사용되고,

상기 제 2, 제 3 및 제 4 영역들은 차례로 상기 제 2 전계효과 트랜지스터의 소오스 전극, 채널 영역 및 드레인 전극으로 사용되는 반도체 장치. - 청구항 2에 있어서,

상기 제 1 영역에 전기적으로 연결된 메모리 요소를 더 포함하는 반도체 장치. - 청구항 2에 있어서,

상기 제 2 영역은 상기 제 1 및 제 3 영역들을 통해서만 그것의 외부에 배치된 도전성 패턴에 전기적으로 연결되고,

상기 제 3 영역은 상기 활성 패턴의 일 측에 배치되는 하부 배선에 전기적으로 연결되는 반도체 장치. - 청구항 2에 있어서,

상기 제 1 전계효과트랜지스터는 상기 제 2 영역의 측면에 배치되는 상부 게이트 패턴을 포함하고, 상기 제 2 전계효과트랜지스터는 상기 제 3 영역의 측면에 배치되는 적어도 하나의 하부 게이트 패턴을 포함하되,

상기 하부 게이트 패턴은 상기 제 4 영역과 전기적으로 오믹하게(Ohmicly) 연결되는 반도체 장치. - 청구항 5에 있어서,

상기 제 1 전계효과트랜지스터는 상기 상부 및 하부 게이트 패턴들의 측벽들과 상기 활성 패턴의 측벽 사이에 배치되는 게이트 절연막 구조체를 포함하되,

상기 게이트 절연막 구조체는 수평적으로 연장되어 상기 상부 게이트 패턴의 바닥면을 덮는 반도체 장치. - 청구항 2에 있어서,

상기 제 2 전계효과트랜지스터는 상기 활성 패턴의 측면에 배치되는 제 1 및 제 2 하부 게이트 패턴들을 포함하고,

상기 제 1 전계효과트랜지스터는 상기 제 1 하부 게이트 패턴의 상부에 배치되는 상부 게이트 패턴을 포함하는 반도체 장치. - 청구항 7에 있어서,

상기 제 2 하부 게이트 패턴의 상부면은 상기 상부 게이트 패턴의 바닥면보다 상기 제 4 영역에 가까운 반도체 장치. - 청구항 7에 있어서,

상기 제 2 하부 게이트 패턴의 상부면은 상기 제 1 하부 게이트 패턴의 상부면보다 상기 제 1 영역에 가깝게 형성되어, 상기 제 2 하부 게이트 패턴과 상기 제 2 영역의 측벽들은 서로 마주보는 반도체 장치. - 청구항 2에 있어서,

상기 제 1 및 제 2 전계효과트랜지스터들은 각각 상기 활성 패턴의 둘레에 배치되는 하나의 상부 게이트 패턴 및 하나의 하부 게이트 패턴을 포함하되,

상기 하부 게이트 패턴은 상기 활성 패턴의 제 1 측면에 인접하게 배치되고,

상기 상부 게이트 패턴은, 상기 제 1 측면을 마주보는, 상기 활성 패턴의 제 2 측면에 인접하게 배치되고,

상기 하부 게이트 패턴의 상부면은 상기 상부 게이트 패턴의 하부면보다 상기 제 1 영역에 가깝게 형성되어, 상기 하부 게이트 패턴과 상기 제 2 영역의 측벽들은 서로 마주보는 반도체 장치. - 청구항 2에 있어서,

상기 하부 게이트 패턴은 상기 제 4 영역과 같은 도전형의 반도체 물질 또는 상기 제 4 영역에 오믹하게 연결되는 도전성 물질을 포함하는 반도체 장치. - 청구항 1에 있어서,

상기 제 1 및 제 2 전계효과 트랜지스터들 중의 하나는 n-채널 모스 전계효과트랜지스터이고, 상기 제 1 및 제 2 전계효과 트랜지스터들 중의 다른 하나는 p-채널 모스 전계효과트랜지스터인 반도체 장치. - 기판의 상부면에 수직한 장축을 가지면서 상기 기판 상에 2차원적으로 배열되는 활성 패턴들; 및

상기 기판의 상부면에 수직한 장축을 가지면서 상기 활성 패턴들 사이에 배치되는 게이트 패턴들을 포함하되,

상기 활성 패턴들 각각은

상기 기판과 다른 도전형의 제 1 영역;

상기 기판과 같은 도전형이면서 상기 제 1 영역과 상기 기판 사이에 배치되는 제 2 영역; 및

상기 기판과 다른 도전형이면서 상기 제 2 영역과 상기 기판 사이에 배치되는 제 3 영역을 포함하고,

상기 게이트 패턴들은

상기 제 3 영역과 함께 모스 커패시터를 구성하는 하부 게이트 패턴들; 및

상기 제 2 영역과 모스 커패시터를 구성하는 상부 게이트 패턴들을 포함하는 반도체 장치. - 청구항 13에 있어서,

상기 기판의 상부면에 평행한 장축을 가지면서 상기 활성 패턴들 사이에서 상기 활성 패턴들을 가로지르는 하부 배선들; 및

상기 기판의 상부면에 평행한 장축을 가지면서 상기 게이트 패턴들의 상부에서 상기 하부 배선들을 가로지르는 상부 배선들을 더 포함하되,

상기 상부 게이트 패턴들 각각은 상기 상부 배선들 중의 하나에 전기적으로 연결되고,

상기 하부 게이트 패턴들은 상기 기판에 전기적으로 연결되는 반도체 장치. - 청구항 14에 있어서,

상기 활성 패턴들은 복수의 활성 그룹들을 구성하고, 상기 활성 그룹들 각각은, 인접하는 한 쌍의 상기 하부 배선들 사이에 배치되는, 상기 활성 패턴들 중의 일부로 구성되되,

상기 인접하는 한 쌍의 하부 배선들 중의 하나는, 상기 활성 그룹들 중에서 선택된 하나를 구성하는, 상기 활성 패턴들 중의 홀수번째 것들에 접속하고,

상기 인접하는 한 쌍의 하부 배선들 중의 다른 하나는, 상기 선택된 활성 그룹을 구성하는, 상기 활성 패턴들 중의 짝수번째 것들에 접속하는 반도체 장치. - 청구항 13에 있어서,

상기 활성 패턴들 중의 일부는 제 1 및 제 2 그룹들을 구성하고,

상기 제 1 및 제 2 그룹들 각각은, 동일한 y 좌표 및 다른 x 좌표들을 갖는, 복수의 상기 활성 패턴들로 구성되고,

상기 상부 게이트 패턴들은 상기 제 1 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 짝수번째 것들 그리고 상기 제 2 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 홀수번째 것들에 국소적으로 배치되는 반도체 장치. - 청구항 16에 있어서,

상기 하부 게이트 패턴들은 상기 제 1 및 제 2 그룹들 각각을 구성하는 상기 활성 패턴들 사이의 공간들 모두에 배치되는 반도체 장치. - 청구항 16에 있어서,

상기 하부 게이트 패턴들은 상기 제 1 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 홀수번째 것들 그리고 상기 제 2 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 짝수번째 것들에 국소적으로 배치되는 반도체 장치. - 청구항 16에 있어서,

상기 제 1 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 홀수번째 것들 그리고 상기 제 2 그룹을 구성하는 상기 활성 패턴들 사이의 공간들 중의 짝수번째 것들에 배치되는, 상기 하부 게이트 패턴들의 상부면은 상기 상부 게이트 패턴들의 상부면보다 상기 제 1 영역에 인접하는 반도체 장치. - 청구항 16에 있어서,

상기 제 1, 제 2 및 제 3 영역들 그리고 상기 상부 게이트 패턴은 제 1 전계효과트랜지스터를 구성하고,

상기 제 2 및 제 3 영역들, 상기 기판 그리고 상기 하부 게이트 패턴은 제 2 전계효과트랜지스터를 구성하되,

상기 제 2 영역은 상기 제 1 및 제 2 전계효과트랜지스터들의 채널 영역 및 소오스 전극으로 각각 사용되고,

상기 제 3 영역들은 상기 제 1 및 제 2 전계효과트랜지스터들의 드레인 전극 및 채널 영역으로 각각 사용되는 반도체 장치. - 기판을 패터닝하여 제 1 트렌치를 형성하는 단계;

상기 제 1 트렌치 내에 상기 기판에 전기적으로 연결되는 하부 게이트막을 형성하는 단계;

상기 기판 및 상기 하부 게이트막을 패터닝하여 상기 제 1 트렌치를 가로지르는 제 2 트렌치를 형성함으로써, 활성 패턴 및 하부 게이트 패턴을 형성하는 단계; 및

상기 제 2 트렌치 내에 상기 활성 패턴의 하부 영역에 접속하는 하부 배선을 형성하는 단계를 포함하는 수직한 채널 영역을 갖는 반도체 장치의 제조 방법. - 청구항 21에 있어서,

상기 제 1 트렌치 내에 상부 게이트막을 형성하는 단계;

상기 상부 게이트막이 형성된 결과물 상에 상부 도전막을 형성하는 단계; 및

상기 상부 도전막을 패터닝하여 상기 하부 배선을 가로지르는 상부 배선을 형성하는 단계를 더 포함하되,

상기 상부 도전막은 상기 하부 배선을 형성한 이후에 형성되는 반도체 장치의 제조 방법. - 청구항 22에 있어서,

상기 상부 게이트막은, 상기 제 2 트렌치를 형성하기 전에, 상기 제 1 트렌치 내에 형성되는 것을 특징으로 하는 반도체 장치의 제조 방법. - 청구항 22에 있어서,

상기 상부 게이트막은, 상기 하부 배선을 형성한 후에, 상기 제 1 트렌치 내에 형성되는 것을 특징으로 하는 반도체 장치의 제조 방법. - 청구항 22에 있어서,

상기 상부 배선을 형성하기 전에, 상기 제 1 트렌치 내에 플러그 절연막을 형성하는 단계를 더 포함하되,

상기 플러그 절연막은, 상기 배선들 각각과 그것의 아래에 위치하는 상기 하부 게이트 패턴들 중의 일부 사이에 국소적으로 형성되는 반도체 장치의 제조 방법. - 청구항 25에 있어서,

상기 플러그 절연막은 상기 하부 배선을 형성한 후에 형성되는 반도체 장치의 제조 방법. - 청구항 25에 있어서,

상기 플러그 절연막은 상기 상부 게이트막을 형성하기 전에 형성되는 반도체 장치의 제조 방법. - 청구항 25에 있어서,

상기 플러그 절연막을 형성하는 단계는

상기 상부 게이트막을 패터닝하여 상기 제 1 트렌치의 일부 영역을 노출시키는 갭 영역을 형성하는 단계; 및

상기 갭 영역을 채우는 상기 플러그 절연막을 형성하는 단계를 포함하는 반도체 장치의 제조 방법. - 청구항 25에 있어서,

상기 플러그 절연막은 상기 제 2 트렌치를 형성하기 전에 상기 하부 게이트막이 형성된 상기 제 1 트렌치를 채우도록 형성되는 반도체 장치의 제조 방법. - 청구항 21에 있어서,

상기 하부 배선을 형성하기 전에, 상기 활성 패턴의 하부 영역에 하부 불순물 영역을 형성하는 단계를 더 포함하되,

상기 하부 게이트 패턴의 상부면은 적어도 상기 하부 불순물 영역의 가장 낮은 상부면보다 높게 형성되는 반도체 장치의 제조 방법.

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020100098119A KR101736235B1 (ko) | 2010-10-08 | 2010-10-08 | 수직 채널 트랜지스터를 구비하는 반도체 장치 및 그 제조 방법 |

| US13/097,343 US8384141B2 (en) | 2010-10-08 | 2011-04-29 | Semiconductor device with vertical channel transistor |

| CN201110295534.8A CN102446920B (zh) | 2010-10-08 | 2011-10-08 | 具有垂直沟道晶体管的半导体器件及其制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020100098119A KR101736235B1 (ko) | 2010-10-08 | 2010-10-08 | 수직 채널 트랜지스터를 구비하는 반도체 장치 및 그 제조 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20120037520A true KR20120037520A (ko) | 2012-04-20 |

| KR101736235B1 KR101736235B1 (ko) | 2017-05-17 |

Family

ID=45924461

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020100098119A Active KR101736235B1 (ko) | 2010-10-08 | 2010-10-08 | 수직 채널 트랜지스터를 구비하는 반도체 장치 및 그 제조 방법 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8384141B2 (ko) |

| KR (1) | KR101736235B1 (ko) |

| CN (1) | CN102446920B (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20180052993A (ko) * | 2016-11-11 | 2018-05-21 | 서울대학교산학협력단 | 비대칭 듀얼 게이트를 가진 반도체 소자 및 그 어레이 |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20130027155A (ko) * | 2011-09-07 | 2013-03-15 | 삼성전자주식회사 | 반도체 기억 소자 |

| KR20130134813A (ko) * | 2012-05-31 | 2013-12-10 | 에스케이하이닉스 주식회사 | 자기정렬된 게이트전극을 구비한 수직채널트랜지스터 및 그 제조 방법 |

| US8901687B2 (en) | 2012-11-27 | 2014-12-02 | Industrial Technology Research Institute | Magnetic device with a substrate, a sensing block and a repair layer |

| US10014302B1 (en) * | 2016-12-27 | 2018-07-03 | Micron Technology, Inc. | Methods of forming memory arrays |

| US11164890B2 (en) * | 2020-01-09 | 2021-11-02 | Sandisk Technologies Llc | Cross-point array of ferroelectric field effect transistors and method of making the same |

| CN112466358A (zh) * | 2020-11-30 | 2021-03-09 | 光华临港工程应用技术研发(上海)有限公司 | 磁性隧道结存储器 |

| CN113629057B (zh) * | 2021-08-09 | 2023-10-27 | 长鑫存储技术有限公司 | 半导体结构及其制造方法 |

| CN116803232A (zh) * | 2022-01-18 | 2023-09-22 | 华为技术有限公司 | 铁电存储器及垂直结构晶体管 |

| WO2025149057A1 (zh) * | 2024-01-11 | 2025-07-17 | 北京超弦存储器研究院 | Dram单元结构及其操作方法、dram阵列结构及其操作方法和制造方法 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5909618A (en) | 1997-07-08 | 1999-06-01 | Micron Technology, Inc. | Method of making memory cell with vertical transistor and buried word and body lines |

| US5977579A (en) * | 1998-12-03 | 1999-11-02 | Micron Technology, Inc. | Trench dram cell with vertical device and buried word lines |

| EP2323164B1 (en) | 2000-08-14 | 2015-11-25 | SanDisk 3D LLC | Multilevel memory array and method for making same |

| US6531727B2 (en) * | 2001-02-09 | 2003-03-11 | Micron Technology, Inc. | Open bit line DRAM with ultra thin body transistors |

| US6670642B2 (en) * | 2002-01-22 | 2003-12-30 | Renesas Technology Corporation. | Semiconductor memory device using vertical-channel transistors |

| KR100543901B1 (ko) | 2003-09-19 | 2006-01-20 | 삼성전자주식회사 | 반도체 소자 및 그 제조 방법 |

| DE102006016550B4 (de) | 2005-04-09 | 2010-04-29 | Samsung Electronics Co., Ltd., Suwon-si | Feldeffekttransistoren mit vertikal ausgerichteten Gate-Elektroden und Verfahren zum Herstellen derselben |

| KR100688576B1 (ko) | 2005-10-14 | 2007-03-02 | 삼성전자주식회사 | 수직채널 트랜지스터를 갖는 반도체 메모리 장치 및 그제조방법 |

| KR100685659B1 (ko) * | 2006-01-26 | 2007-02-26 | 삼성전자주식회사 | 반도체 장치 및 그 제조 방법 |

| JP4939955B2 (ja) * | 2007-01-26 | 2012-05-30 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| KR20080113858A (ko) * | 2007-06-26 | 2008-12-31 | 주식회사 하이닉스반도체 | 수직 채널 트랜지스터를 구비한 반도체 소자의 제조 방법 |

| KR100934840B1 (ko) | 2007-10-30 | 2009-12-31 | 주식회사 하이닉스반도체 | 반도체 소자 및 그 제조 방법 |

| KR100972908B1 (ko) | 2008-03-17 | 2010-07-28 | 주식회사 하이닉스반도체 | 반도체 소자의 형성 방법 |

| KR20090121475A (ko) | 2008-05-22 | 2009-11-26 | 주식회사 하이닉스반도체 | 수직형 반도체 소자 및 그의 제조방법 |

-

2010

- 2010-10-08 KR KR1020100098119A patent/KR101736235B1/ko active Active

-

2011

- 2011-04-29 US US13/097,343 patent/US8384141B2/en active Active

- 2011-10-08 CN CN201110295534.8A patent/CN102446920B/zh active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20180052993A (ko) * | 2016-11-11 | 2018-05-21 | 서울대학교산학협력단 | 비대칭 듀얼 게이트를 가진 반도체 소자 및 그 어레이 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR101736235B1 (ko) | 2017-05-17 |

| US20120086065A1 (en) | 2012-04-12 |

| CN102446920A (zh) | 2012-05-09 |

| US8384141B2 (en) | 2013-02-26 |

| CN102446920B (zh) | 2015-07-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101736235B1 (ko) | 수직 채널 트랜지스터를 구비하는 반도체 장치 및 그 제조 방법 | |

| KR20120036447A (ko) | 수직 채널 트랜지스터를 구비하는 반도체 장치 및 그 제조 방법 | |

| KR101820022B1 (ko) | 수직 채널 트랜지스터를 갖는 반도체 소자 및 그 제조방법 | |

| US9287395B2 (en) | Semiconductor device and a bit line and the whole of a bit line contact plug having a vertically uniform profile | |

| US9947661B2 (en) | Semiconductor device and method of manufacturing the same | |

| US20140291755A1 (en) | Semiconductor device and semiconductor module | |

| US8735956B2 (en) | Semiconductor device and method for manufacturing the same | |

| KR101732462B1 (ko) | 수직 채널 트랜지스터를 구비하는 반도체 장치 및 그 동작 방법 | |

| US8399917B2 (en) | Semiconductor devices including buried gate electrodes including bitline shoulder attack protection and methods of forming such semiconductor devices | |

| US9165935B2 (en) | Semiconductor devices and methods for manufacturing the same | |

| KR101774511B1 (ko) | 수직 채널 트랜지스터를 구비하는 반도체 장치 | |

| KR102335280B1 (ko) | 커패시터를 갖는 반도체 장치 및 이의 제조 방법 | |

| JP5697952B2 (ja) | 半導体装置、半導体装置の製造方法およびデータ処理システム | |

| KR20160087968A (ko) | 반도체 소자 및 그 제조방법 | |

| TW201322255A (zh) | 動態隨機存取記憶體結構及其製作方法 | |

| US8492812B2 (en) | Semiconductor device having dummy pattern and method of fabricating a semiconductor device comprising dummy pattern | |

| WO2023130877A1 (zh) | 半导体器件的制造方法及半导体器件 | |

| KR20250096343A (ko) | 반도체 소자 | |

| KR20250096342A (ko) | 반도체 소자 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

Patent event code: PA01091R01D Comment text: Patent Application Patent event date: 20101008 |

|

| PG1501 | Laying open of application | ||

| A201 | Request for examination | ||

| PA0201 | Request for examination |

Patent event code: PA02012R01D Patent event date: 20151007 Comment text: Request for Examination of Application Patent event code: PA02011R01I Patent event date: 20101008 Comment text: Patent Application |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

Comment text: Notification of reason for refusal Patent event date: 20161019 Patent event code: PE09021S01D |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

Patent event code: PE07011S01D Comment text: Decision to Grant Registration Patent event date: 20170424 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

Comment text: Registration of Establishment Patent event date: 20170510 Patent event code: PR07011E01D |

|

| PR1002 | Payment of registration fee |

Payment date: 20170511 End annual number: 3 Start annual number: 1 |

|

| PG1601 | Publication of registration | ||

| PR1001 | Payment of annual fee |

Payment date: 20200429 Start annual number: 4 End annual number: 4 |

|

| PR1001 | Payment of annual fee |

Payment date: 20210428 Start annual number: 5 End annual number: 5 |

|

| PR1001 | Payment of annual fee |

Payment date: 20220420 Start annual number: 6 End annual number: 6 |

|

| PR1001 | Payment of annual fee |

Payment date: 20230426 Start annual number: 7 End annual number: 7 |