KR20080098797A - 반도체 패키지 및 제조방법 - Google Patents

반도체 패키지 및 제조방법 Download PDFInfo

- Publication number

- KR20080098797A KR20080098797A KR1020070044110A KR20070044110A KR20080098797A KR 20080098797 A KR20080098797 A KR 20080098797A KR 1020070044110 A KR1020070044110 A KR 1020070044110A KR 20070044110 A KR20070044110 A KR 20070044110A KR 20080098797 A KR20080098797 A KR 20080098797A

- Authority

- KR

- South Korea

- Prior art keywords

- semiconductor chip

- semiconductor

- adhesive layer

- groove

- chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H10W72/30—

-

- H10W72/381—

-

- H10W72/884—

-

- H10W72/931—

-

- H10W74/00—

-

- H10W90/732—

Landscapes

- Die Bonding (AREA)

Abstract

본 발명은 반도체 패키지 및 제조방법에 관한 것으로, 기판과, 상기 기판 상에 탑재되는 하부 반도체 칩과, 상기 하부 반도체 칩이 삽입되는 홈을 포함하며 상기 하부 반도체 칩이 상기 홈에 삽입되는 형태로 상기 하부 반도체 칩 상에 적층되는 상부 반도체 칩을 포함하는 것을 특징으로 한다. 이에 의하면, 상하부 반도체 칩들이 오버행 구조를 이루도록 적층되더라도 반도체 칩들의 파손없이 적층할 수 있는 효과가 있다.

반도체 패키지, 멀티칩 패키지, 오버행

Description

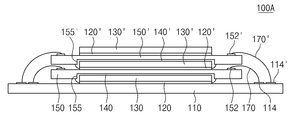

도 1은 본 발명의 실시예 1에 따른 반도체 패키지를 도시한 평면도.

도 2a 및 도 2b는 도 1의 A-A'선을 절개한 단면도.

도 3a 및 도 3b는 본 발명의 실시예에 따른 반도체 패키지의 응용예를 도시한 단면도.

도 4a 내지 도 4d는 본 발명의 실시예에 따른 반도체 패키지를 제조하는 방법을 도시한 단면도.

< 도면의 주요부분에 대한 부호의 설명 >

100; 반도체 패키지 112,114; 기판패드

120; 제1 접착층 130; 제1 반도체 칩

140; 제2 접착층 150; 제2 반도체 칩

152; 칩패드 155; 홈

160,170; 와이어

본 발명은 반도체 패키지 및 제조방법에 관한 것으로, 보다 구체적으로는 오버행 구조를 갖는 반도체 패키지 및 제조방법에 관한 것이다.

전자기기의 소형화에 따라 반도체 패키지의 크기 또한 점점 축소화, 박형화 및 경량화되어 가고 있는 것이 최근의 추세이다. 통상적으로 반도체 패키지는 하나의 반도체 칩을 포함하고 있으나 최근에는 하나의 패키지 내에 서로 다른 기능을 갖는 다수의 반도체 칩이 탑재되는 이른바 멀티칩 패키지(MCP)가 주로 개발되고 있다. 멀티칩 패키지는 다수의 반도체 칩이 탑재될 수 있도록 박막화된 반도체 칩이 요구되며, 각각의 반도체 칩 별로 와이어 본딩이 수행될 수 있도록 크기가 다양한 반도체 칩이 적층될 수 있다.

크기가 작은 반도체 칩 위에 크기가 큰 반도체 칩이 적층된 반도체 패키지의 경우 큰 반도체 칩의 일부가 작은 칩의 바깥으로 돌출된 이른바 오버행(overhang) 구조를 갖게 된다. 오버행 구조를 갖게 되면 와이어 본딩시 와이어가 휘어지거나 심지어 파손되는 현상이 일어날 수 있다. 특히, 반도체 칩이 박형화되어 가는 추세에 있어서는 반도체 칩의 강도가 상대적으로 저하되어 와이어 본딩시 반도체 칩이 파손되는 현상이 일어날 수 있다. 따라서, 이러한 제약을 극복하지 못하게 되면 결국 원하는 칩 스택(chip stack)를 구현할 수 없다는 문제점이 있다.

본 발명은 상술한 종래 기술상의 문제점을 해결하기 위하여 안출된 것으로, 본 발명의 목적은 반도체 칩의 파손없이 안정적인 와이어 본딩이 가능한 반도체 패키지 및 제조방법을 제공함에 있다.

상기 목적을 달성하기 위한 본 발명에 따른 반도체 패키지 및 제조방법은 상부칩의 하면에 홈을 형성하여 이 홈을 통해 상부칩과 하부칩을 서로 맞물리는 형태로 적층하고, 상부칩의 오버행 부분의 강도를 약화시키지 않게 하는 것을 특징으로 한다.

상기 특징을 구현할 수 있는 본 발명의 실시예에 따른 반도체 패키지는, 기판과; 상기 기판 상에 탑재되는 제1 반도체 칩과; 상기 제1 반도체 칩이 삽입되는 제1 홈을 포함하며 상기 제1 반도체 칩이 상기 제1 홈에 삽입되는 형태로 상기 제1 반도체 칩 상에 적층되는 제2 반도체 칩을 포함하는 것을 특징으로 한다.

본 실시예의 반도체 패키지에 있어서, 상기 제1 반도체 칩은 제1 폭을 가지며, 상기 제2 반도체 칩은 상기 제1 폭에 비해 큰 제2 폭을 가지며, 상기 제1 홈은 상기 제1 폭에 비해 크고 상기 제2 폭에 비해 작은 제3 폭을 가진다.

본 실시예의 반도체 패키지에 있어서, 상기 제2 반도체 칩은 상기 제1 반도체 칩의 바깥으로 돌출된 제1 오버행 부분을 가진다.

본 실시예의 반도체 패키지에 있어서, 상기 제1 반도체 칩과 상기 제2 반도체 칩 사이에 개재되어 상기 제1 홈을 채우는 제1 접착층을 더 포함한다. 상기 제1 접착층은 상기 제1 오버행 부분을 지지하는 부분을 더 포함한다.

본 실시예의 반도체 패키지에 있어서, 상기 제2 반도체 칩 상에 적층되며, 상기 제2 반도체 칩에 비해 작은 폭을 가지는 제3 반도체 칩과; 상기 제3 반도체 칩이 삽입되는 제2 홈을 포함하며, 상기 제3 반도체 칩이 상기 제2 홈에 삽입되는 형태로 상기 제3 반도체 칩 상에 적층되며, 상기 제3 반도체 칩의 폭에 비해 큰 폭을 가지며 상기 제3 반도체 칩의 바깥으로 돌출된 제2 오버행 부분을 갖는 제4 반도체 칩을 더 포함한다.

본 실시예의 반도체 패키지에 있어서, 상기 제3 반도체 칩과 상기 제4 반도체 칩 사이에 개재되어 상기 제2 홈을 채우는 제2 접착층을 더 포함한다. 상기 제2 접착층은 상기 제2 오버행 부분을 지지하는 부분을 더 포함한다.

상기 특징을 구현할 수 있는 본 발명의 실시예에 따른 반도체 패키지의 제조방법은, 기판을 제공하는 단계와; 상기 기판에 제1 반도체 칩을 탑재하는 단계와; 상기 제1 반도체 칩의 바깥으로 돌출된 제1 오버행 부분을 가지도록 상기 제1 반도체 칩 상에 상기 제2 반도체 칩을 적층하는 단계를 포함하는 것을 특징으로 한다.

본 실시예의 방법에 있어서, 상기 제2 반도체 칩을 적층하는 단계는: 상기 제1 반도체 칩이 삽입되는 제1 홈을 가지는 제2 반도체 칩을 제공하는 단계와; 상기 제1 반도체 칩과 상기 제2 반도체 칩 사이에 제1 접착층을 형성하는 단계와; 상기 제1 접착층의 개재하에 상기 제1 반도체 칩을 상기 제1 홈에 삽입시키는 단계를 포함한다.

본 실시예의 방법에 있어서, 상기 제1 반도체 칩을 상기 제1 홈에 삽입시키는 단계는 상기 제1 접착층이 상기 홈으로부터 흘러나와 상기 제1 오버행 부분을 지지하는 부분을 형성하는 단계를 포함한다.

본 실시예의 방법에 있어서, 상기 제2 반도체 칩 상에 제3 반도체 칩을 적층하는 단계와; 상기 제3 반도체 칩이 삽입되는 제2 홈을 가지는 제4 반도체 칩을 제 공하는 단계와; 상기 제3 반도체 상에 제2 접착층을 형성하는 단계와; 상기 제2 접착층의 개재하에 상기 제3 반도체 칩을 상기 제2 홈에 삽입시켜 상기 제3 반도체 칩 상에 상기 제4 반도체 칩을 적층하는 단계를 더 포함한다.

본 실시예의 방법에 있어서, 상기 제4 반도체 칩은 상기 제3 반도체 칩의 바깥으로 돌출된 제2 오버행 부분을 포함하고, 상기 제2 접착층은 상기 제2 오버행 부분을 지지한다.

본 발명에 의하면, 오버행을 이루는 상부칩에 하부칩이 삽입되는 홈을 형성하여 상부칩과 하부칩을 맞물려 끼우는 방법으로 반도체 칩들이 적층되며, 상하부 칩들이 맞물리는 부분이 접착층에 의해 고정되며, 접착층이 상하부 칩들 사이의 틈으로 밀려나와 오버행 부분을 지지한다.

이하, 본 발명에 따른 반도체 패키지 및 제조방법을 첨부한 도면을 참조하여 상세히 설명한다.

본 발명과 종래 기술과 비교한 이점은 첨부된 도면을 참조한 상세한 설명과 특허청구범위를 통하여 명백하게 될 것이다. 특히, 본 발명은 특허청구범위에서 잘 지적되고 명백하게 청구된다. 그러나, 본 발명은 첨부된 도면과 관련해서 다음의 상세한 설명을 참조함으로써 가장 잘 이해될 수 있다. 도면에 있어서 동일한 참조부호는 다양한 도면을 통해서 동일한 구성요소를 나타낸다.

(장치 실시예)

도 1은 본 발명의 실시예에 따른 반도체 패키지를 도시한 평면도이고, 도 2a 및 도 2b는 도 1의 A-A'선을 절개한 단면도이다.

도 1 및 도 2a를 참조하면, 본 발명의 실시예에 따른 반도체 패키지(100)는 PCB(Printed Circuit Board)와 같은 기판(110)에 제1 반도체 칩(130)과 제2 반도체 칩(150)이 이른바 오버행(overhang) 구조로 상하 적층된 패키지이다. 기판(110)은 상측면(110A)과 하측면(110C)이 서로 마주보고 좌측면(110C)과 우측면(110D)이 서로 마주보는 형태인 장방형 외관을 가질 수 있다. 기판(110)의 상면(110f)에는 상측면(110A) 및 하측면(110C)을 따라 제1 기판패드(112)가 다수 배열되고 좌측면(110B) 및 우측면(110D)을 따라 제2 기판패드(114)가 다수 배열된다.

제1 반도체 칩(130)은 제1 접착층(120)을 매개로 기판 상면(110f)에 탑재된다. 제1 반도체 칩(130)의 활성면(130f)에는 다수개의 제1 칩패드(132)가 기판(110)의 상측면(110A) 및 하측면(110C)에 근접 배열된다. 다수개의 제1 칩패드(132)는 다수개의 제1 와이어(160)를 매개로 다수개의 제1 기판패드(112)와 전기적으로 연결되므로써 제1 반도체 칩(130)은 기판(110)과 전기적으로 연결된다.

제2 반도체 칩(150)은 제2 접착층(140)을 매개로 제1 반도체 칩(130)의 활성면(130f)에 탑재된다. 제2 반도체 칩(150)의 활성면(150f)에는 다수개의 제2 칩패드(152)가 기판(110)의 좌측면(110C) 및 우측면(110D)에 근접 배열된다. 다수개의 제2 칩패드(152)는 다수개의 제2 와이어(170)를 매개로 다수개의 제2 기판패드(114)와 전기적으로 연결되므로써 제2 반도체 칩(150)은 기판(110)과 전기적으로 연결된다.

제1 및 제2 반도체 칩(130,150)은 오버행(overhang) 구조를 이루도록 적층된 다. 구체적으로, 제1 폭(D1)을 가지는 제1 반도체 칩(130) 상에 제1 폭(D1)에 비해 큰 제2 폭(D2)을 가지는 제2 반도체 칩(150)이 제2 접착층(140)을 매개로 부착된다. 이에 따라, 제2 반도체 칩(150)은 제1 반도체 칩(130)의 바깥으로 돌출되는 오버행 부분(E1,E2)을 좌우 각각에 갖게 된다. 오버행 부분(E1,E2)은 제2 반도체 칩(150)의 좌우 균형을 위해 동일한 길이를 갖는 것이 바람직하다.

제1 및 제2 반도체 칩(130,150)과의 적층은 제1 반도체 칩(130)이 제2 반도체 칩(150)의 비활성면(150b)에 삽입되는 형태로 구현된다. 이를 위해 제2 반도체 칩(150)의 비활성면(150b)에는 제1 반도체 칩(130)이 삽입되기에 충분한 제3 폭(D3)을 가지는 홈(155)이 마련된다. 제2 접착층(140)은 마치 제1 및 제2 반도체 칩(130,150)이 맞물리는 틈새, 즉 홈(155)을 메우는 형태가 된다. 홈(155) 및 제2 접착층(140)에 의해 제2 반도체 칩(150)은 제1 반도체 칩(130)의 활성면(130f) 상에 견고하게 고정된다. 제1 및 제2 접착층(120,140)으로는 통상의 반도체 공정에 사용되는 액상 또는 필름 형태의 접착제로써 이루어질 수 있다.

도 2b를 참조하면, 제2 접착층(140)의 양을 증가시키게 되면 제2 접착층(140)은 오버행 부분(E1,E2) 하부에까지 연장된 부분(140a)을 포함하도록 형성될 수 있다. 연장된 부분(140a)이 특히 오버행 부분(E1,E2)을 견고히 지지하고 있어 케필러리(미도시)와 같은 와이어 본딩 기구가 제2 반도체 칩(150)의 오버행 부분(E1,E2)을 누르게 될 때 제2 반도체 칩(150)이 파손되는 현상을 억제한다. 아울 러, 기판(110)과 오버행 부분(E1,E2)과의 사이가 제2 접착층(140)으로부터 연장된 부분(140a)이 미리 채워져 있어 에폭시 몰딩 컴파운드(EMC)를 이용한 몰딩막 충진 불량이 발생하는 문제가 극복될 수 있다.

도 1 및 도 2a를 다시 참조하면, 제3 폭(D3)은 제2 폭(D2)에 비해 작고 제1 폭(D1)에 비해 커야 할 것이다. 그런데, 제3 폭(D3)이 제1 폭(D1)에 비해 너무 큰 경우 홈(155)과 제1 반도체 칩(130) 사이의 간격(d1,d2)이 비교적 크게 형성된다. 간격(d1,d2)이 비교적 크면 제2 와이어(170)를 본딩하는 경우 케필러리(미도시)와 같은 와이어 본딩 기구가 제2 반도체 칩(150)의 가장자리, 즉 오버행 부분(E1,E2)을 누르게 될 때 제2 반도체 칩(150)이 파손되거나 제2 와이어(170)가 정상적으로 형성되지 않을 수 있다. 따라서, 홈(155)과 제1 반도체 칩(130) 사이의 간격(d1,d2)은 대략적으로 수 마이크로미터(㎛) 내지 수십 마이크로미터(㎛) 범위 내에 있는 것이 바람직하다. 예를 들어, 간격(d1,d2)은 1 마이크로미터(㎛) 내지 100 마이크로미터(㎛) 정도로 설정될 수 있다. 홈(155)으로 제1 반도체 칩(130)이 삽입되는 형태로 제1 및 제2 반도체 칩(130,150)이 견고하게 적층되고 제2 반도체 칩(150)의 오버행 부분(E1,E2)은 두껍게 유지되므로 오버행 부분(E1,E2)의 강도가 약화되지 않는다.

홈(155)의 깊이(h1)는 제2 반도체 칩(150) 중에서 오버행 부분(E1,E2)과 나머지 부분과의 두께 차이에 의해 결정되는데, 오버행 부분(E1,E2)의 길이가 길수록 오 버행 부분(E1,E2)의 두께가 두껍게 유지되도록 적절히 조절할 수 있다. 홈(155)의 깊이(h1)가 클수록 제1 및 제2 반도체 칩(130,150)의 적층 높이(H)가 낮아질 것이다. 즉, 홈(155)의 깊이(h1)는 제1 및 제2 반도체 칩(130,150)과의 적층 높이(H)를 축소시키는 요인으로 작용한다. 따라서, 홈(155)이 형성되어 있음으로 해서 패키지의 높이를 종래와 동일하게 유지하면서도 종래보다는 적층되는 반도체 칩의 수를 더 많게 가져갈 수 있다.

도 3a 및 도 3b는 본 발명의 실시예에 따른 반도체 패키지의 응용예를 도시한 단면도이다.

도 3a를 참조하면, 본 응용예의 반도체 패키지(100A)는 도 2a에서 설명한 바와 같이 기판(110) 상에 제1 접착층(120)을 매개로 제1 반도체 칩(130)이 탑재되고, 제1 반도체 칩(130) 상에는 제2 접착층(140)을 매개로 제2 반도체 칩(150)이 적층된다. 제2 반도체 칩(150)에는 홈(155)이 형성되어 있어 제1 반도체 칩(130)이 홈(155)에 삽입되는 형태로 제1 및 제2 반도체 칩(130,150)이 도 2a에 도시된 바와 같은 오버행 구조를 이루도록 적층된다. 제2 반도체 칩(150)에 형성된 제2 칩패드(152)와 기판(110)에 형성된 제2 기판패드(114)가 제2 와이어(170)에 의해 전기적으로 연결되므로써 제2 반도체 칩(150)은 기판(110)과 전기적으로 연결된다. 제1 반도체 칩(120)과 기판(110)은 도 1에 도시된 바와 마찬가지로 제1 와이어(도 1의 160)에 의해 전기적으로 연결된다.

마찬가지로, 제2 반도체 칩(150) 상에 제3 접착층(120')을 매개로 제3 반도 체 칩(130')이 적층되고, 제3 반도체 칩(130') 상에는 제4 접착층(140')을 매개로 제4 반도체 칩(150')이 적층된다. 제4 반도체 칩(150')에는 홈(155')이 형성되어 있어 제3 반도체 칩(130')이 홈(155')에 삽입되는 형태로 제3 및 제4 반도체 칩(130',150')이 도 2a에 도시된 바와 같은 오버행 구조를 이루도록 적층된다. 기판(110)에는 제3 기판패드(114')가 더 형성되어 있을 수 있다. 제4 반도체 칩(150')에 형성된 칩패드(152')와 기판(110)에 형성된 제3 기판패드(114')가 제3 와이어(170')에 의해 전기적으로 연결되므로써 제4 반도체 칩(150')은 기판(110)과 전기적으로 연결된다. 제4 반도체 칩(150') 상에는 제5 접착층(120˝)을 매개로 제5 반도체 칩(130˝)이 더 적층될 수 있다. 제3 반도체 칩(120')과 기판(110)은 도 1에 도시된 바와 마찬가지로 와이어에 의해 전기적으로 연결되며, 제5 반도체 칩(130˝)과 기판(110)과의 전기적 연결도 이와 마찬가지이다.

도 3b를 참조하면, 특히 제1 반도체 칩(130)과 제2 반도체 칩(150) 사이에 개재된 제2 접착층(140)이 제2 반도체 칩(150)의 오버행 부분을 지지하는 연장된 부분(140a)을 포함하고 있으면 오버행 부분은 더 견고히 지지된다. 제3 반도체 칩(130')과 제4 반도체 칩(150') 사이에 개재된 제4 접착층(140a)도 이와 마찬가지로 연장된 부분(140a')을 포함하고 있으면 제4 반도체 칩(150')의 오버행 부분이 더 견고하게 지지된다.

(방법 실시예)

도 4a 내지 도 4d는 본 발명의 실시예에 따른 반도체 패키지를 제조하는 방 법을 도시한 단면도이다.

도 4a를 참조하면, 기판(110)의 상면(110f)에 제1 접착층(120)을 매개로 제1 반도체 칩(130)을 실장한다. 이때, 제1 반도체 칩(130)의 활성면(130f)이 위를 향하게 한다. 기판(110)에는 다수개의 제1 기판패드(도 1의 112)와 제2 기판패드(114)가 형성되어 있다. 도 1에 도시된 바와 유사하게 제1 반도체 칩(130)과 기판(110)을 제1 와이어(도 1의 160)를 이용하여 전기적으로 연결시킨다. 제1 접착층(120)은 통상의 반도체 공정에 사용되는 액상 또는 필름 형태의 접착제로써 이루어질 수 있다.

도 4b를 참조하면, 제1 반도체 칩(130)의 활성면(130f) 상에 제2 접착층(140)을 형성하고, 제2 반도체 칩(150)을 제1 반도체 칩(130) 상에 적층시켜 제2 반도체 칩(150)의 일부가 제1 반도체 칩(130)의 바깥으로 돌출된 이른바 오버행 구조를 이루도록 한다. 이때, 제2 반도체 칩(150)의 비활성면(150b)이 제1 반도체 칩(130)의 활성면(130f)이 서로 마주보도록 하여 비활성면(150b)에 형성된 홈(155)에 제1 반도체 칩(130)이 삽입되도록 한다. 제1 및 제2 반도체 칩(130,150)의 적층은 P방향으로의 적당한 압력을 가하여 진행할 수 있고, 제2 접착층(140)이 홈(155)에 충분히 충진될 수 있도록 수십 ℃(예; 10 ~ 80 ℃) 정도의 적당한 열을 선택적으로 가할 수 있다. 홈(155)은, 예를 들어, 화학약품 또는 플라즈마 등을 이용한 식각 공정을 이용하여 제2 반도체 칩(150)의 비활성면(150b) 일부를 제거하여 형성할 수 있다. 제2 접착층(140)은 통상의 반도체 공정에 사용되는 액상 또는 필름 형태의 접착제로써 이루어질 수 있다.

도 4c를 참조하면, 제2 기판패드(114)와 제2 칩패드(152)를 전기적으로 연결하는 제2 와이어(170)를 형성하여 제2 반도체 칩(150)과 기판(110)을 전기적으로 연결시켜 반도체 패키지(100)를 구현한다. 선택적으로, 에폭시 몰딩 컴파운드(EMC)와 같은 몰딩재를 이용하여 몰딩 공정을 더 진행할 수 있다. 한편, 제2 접착층(140)의 양을 상대적으로 더 늘리면 가압 또는 가열에 의해 제2 접착층(140)이 흘러 나와 도 2b에 도시된 바와 같이 제2 반도체 칩(150)의 오버행 부분을 지지하는 연장된 부분(140a)이 형성되도록 할 수 있다.

도 4d를 참조하면, 선택적으로 제2 반도체 칩(150) 상에 제3 접착층(120')을 매개로 제3 반도체 칩(130')을 적층하고, 제3 반도체 칩(130') 상에 제4 접착층(140')을 매개로 제4 반도체 칩(150')을 더 적층할 수 있다. 또한, 제4 반도체 칩(150') 상에는 제5 접착층(120˝)을 매개로 제5 반도체 칩(130˝)을 더 적층할 수 있다. 이에 따라, 다수개의 반도체 칩이 오버행 구조로 적층된 반도체 패키지(100A)가 구현된다.

한편, 제4 반도체 칩(150')에 홈(155')을 형성하여 제3 반도체 칩(130')이 홈(155')에 삽입되도록 하여 제3 및 제4 반도체 칩(130',150')이 오버행 구조를 이루도록 적층한다. 제4 반도체 칩(150')에 형성된 칩패드(152')와 기판(110)에 형성된 제3 기판패드(114')를 제3 와이어(170')로써 연결하여 제4 반도체 칩(150')을 기판(110)과 전기적으로 연결한다. 제3 반도체 칩(120')과 기판(110)은 도 1에 도시된 바와 유사하게 와이어에 의해 전기적으로 연결하고, 제5 반도체 칩(130˝)과 기판(110)과의 전기적 연결도 이와 마찬가지이다.

여기에 있어서도 도 4c에서 설명한 바와 같이 제2 접착층(140) 및 제4 접착층(140')의 양을 늘려 도 3b에 도시된 바와 같이 제2 반도체 칩(150)의 오버행 부분을 지지하는 부분(140a)과 제4 반도체 칩(150')의 오버행 부분을 지지하는 부분(140a')을 더 형성할 수 있다.

이상의 발명의 상세한 설명은 개시된 실시 상태로 본 발명을 제한하려는 의도가 아니며, 본 발명의 요지를 벗어나지 않는 범위 내에서 다양한 다른 조합, 변경 및 환경에서 사용할 수 있다. 첨부된 청구범위는 다른 실시 상태도 포함하는 것으로 해석되어야 할 것이다.

이상에서 상세히 설명한 바와 같이, 본 발명에 의하면, 오버행을 이루는 상부칩에 하부칩이 삽입되는 홈을 형성하여 상부칩과 하부칩을 맞물려 끼우는 방법으로 반도체 칩들이 적층된다. 그리고, 상하부 칩들이 맞물리는 부분이 접착층에 의해 고정되도록 하며, 접착층이 상하부 칩들 사이의 틈으로 밀려나와 오버행 부분을 지지하게 한다. 이에 따라, 반도체 칩들이 오버행 구조를 이루도록 적층되더라도 강도가 약화되지 않아 칩들의 파손없이 적층할 수 있는 효과가 있다.

Claims (13)

- 기판과;상기 기판 상에 탑재되는 제1 반도체 칩과;상기 제1 반도체 칩이 삽입되는 제1 홈을 포함하며 상기 제1 반도체 칩이 상기 제1 홈에 삽입되는 형태로 상기 제1 반도체 칩 상에 적층되는 제2 반도체 칩을;포함하는 것을 특징으로 하는 반도체 패키지.

- 제1항에 있어서,상기 제1 반도체 칩은 제1 폭을 가지며, 상기 제2 반도체 칩은 상기 제1 폭에 비해 큰 제2 폭을 가지며, 상기 제1 홈은 상기 제1 폭에 비해 크고 상기 제2 폭에 비해 작은 제3 폭을 가지는 것을 특징으로 하는 반도체 패키지.

- 제2항에 있어서,상기 제2 반도체 칩은 상기 제1 반도체 칩의 바깥으로 돌출된 제1 오버행 부분을 가지는 것을 특징으로 하는 반도체 패키지.

- 제3항에 있어서,상기 제1 반도체 칩과 상기 제2 반도체 칩 사이에 개재되어 상기 제1 홈을 채우는 제1 접착층을 더 포함하는 것을 특징으로 하는 반도체 패키지.

- 제4항에 있어서,상기 제1 접착층은 상기 제1 오버행 부분을 지지하는 부분을 더 포함하는 것을 특징으로 하는 반도체 패키지.

- 제1항에 있어서,상기 제2 반도체 칩 상에 적층되며, 상기 제2 반도체 칩에 비해 작은 폭을 가지는 제3 반도체 칩과;상기 제3 반도체 칩이 삽입되는 제2 홈을 포함하며, 상기 제3 반도체 칩이 상기 제2 홈에 삽입되는 형태로 상기 제3 반도체 칩 상에 적층되며, 상기 제3 반도체 칩의 폭에 비해 큰 폭을 가지며 상기 제3 반도체 칩의 바깥으로 돌출된 제2 오버행 부분을 갖는 제4 반도체 칩을;더 포함하는 것을 특징으로 하는 반도체 패키지.

- 제6항에 있어서,상기 제3 반도체 칩과 상기 제4 반도체 칩 사이에 개재되어 상기 제2 홈을 채우는 제2 접착층을 더 포함하는 것을 특징으로 하는 반도체 패키지.

- 제7항에 있어서,상기 제2 접 착층은 상기 제2 오버행 부분을 지지하는 부분을 더 포함하는 것을 특징으로 하는 반도체 패키지.

- 기판을 제공하는 단계와;상기 기판에 제1 반도체 칩을 탑재하는 단계와;상기 제1 반도체 칩의 바깥으로 돌출된 제1 오버행 부분을 가지도록 상기 제1 반도체 칩 상에 상기 제2 반도체 칩을 적층하는 단계를;포함하는 것을 특징으로 하는 반도체 패키지의 제조방법.

- 제9항에 있어서,상기 제2 반도체 칩을 적층하는 단계는:상기 제1 반도체 칩이 삽입되는 제1 홈을 가지는 제2 반도체 칩을 제공하는 단계와;상기 제1 반도체 칩과 상기 제2 반도체 칩 사이에 제1 접착층을 형성하는 단계와;상기 제1 접착층의 개재하에 상기 제1 반도체 칩을 상기 제1 홈에 삽입시키는 단계를;포함하는 것을 특징으로 하는 반도체 패키지의 제조방법.

- 제10항에 있어서,상기 제1 반도체 칩을 상기 제1 홈에 삽입시키는 단계는 상기 제1 접착층이 상기 홈으로부터 흘러나와 상기 제1 오버행 부분을 지지하는 부분을 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 패키지의 제조방법.

- 제9항에 있어서,상기 제2 반도체 칩 상에 제3 반도체 칩을 적층하는 단계와;상기 제3 반도체 칩이 삽입되는 제2 홈을 가지는 제4 반도체 칩을 제공하는 단계와;상기 제3 반도체 상에 제2 접착층을 형성하는 단계와;상기 제2 접착층의 개재하에 상기 제3 반도체 칩을 상기 제2 홈에 삽입시켜 상기 제3 반도체 칩 상에 상기 제4 반도체 칩을 적층하는 단계를;더 포함하는 것을 특징으로 하는 반도체 패키지의 제조방법.

- 제12항에 있어서,상기 제4 반도체 칩은 상기 제3 반도체 칩의 바깥으로 돌출된 제2 오버행 부분을 포함하고, 상기 제2 접착층은 상기 제2 오버행 부분을 지지하는 것을 특징으로 하는 반도체 패키지의 제조방법.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020070044110A KR20080098797A (ko) | 2007-05-07 | 2007-05-07 | 반도체 패키지 및 제조방법 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020070044110A KR20080098797A (ko) | 2007-05-07 | 2007-05-07 | 반도체 패키지 및 제조방법 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR20080098797A true KR20080098797A (ko) | 2008-11-12 |

Family

ID=40286030

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020070044110A Withdrawn KR20080098797A (ko) | 2007-05-07 | 2007-05-07 | 반도체 패키지 및 제조방법 |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR20080098797A (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20150081646A (ko) * | 2014-01-06 | 2015-07-15 | 에스케이하이닉스 주식회사 | 칩 적층 패키지 및 그 제조방법 |

-

2007

- 2007-05-07 KR KR1020070044110A patent/KR20080098797A/ko not_active Withdrawn

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20150081646A (ko) * | 2014-01-06 | 2015-07-15 | 에스케이하이닉스 주식회사 | 칩 적층 패키지 및 그 제조방법 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5529371B2 (ja) | 半導体装置及びその製造方法 | |

| JP4498403B2 (ja) | 半導体装置と半導体記憶装置 | |

| KR100574223B1 (ko) | 멀티칩 패키지 및 그 제조방법 | |

| US20090166839A1 (en) | Semiconductor stack device and mounting method | |

| JPH11354669A (ja) | ボ―ルグリッドアレイ型半導体パッケ―ジ及びその製造方法 | |

| JP2003078105A (ja) | スタックチップモジュール | |

| TW201312723A (zh) | 晶片封裝結構及其製造方法 | |

| KR20060125574A (ko) | 오버행 다이용 에폭시 범프 | |

| US20090057916A1 (en) | Semiconductor package and apparatus using the same | |

| JP4766050B2 (ja) | 電子回路装置の製造方法 | |

| US7199465B2 (en) | Wire bonding system and method of use | |

| JP2013069988A (ja) | 半導体装置とその製造方法 | |

| JP2006128169A (ja) | 半導体装置及び半導体装置の製造方法 | |

| KR20080098797A (ko) | 반도체 패키지 및 제조방법 | |

| KR101046251B1 (ko) | 적층형 반도체 패키지 | |

| KR100650728B1 (ko) | 스택 패키지 및 그 제조방법 | |

| KR100947146B1 (ko) | 반도체 패키지 | |

| CN101409265B (zh) | 用于一半导体封装结构的基板、半导体封装结构及其制造方法 | |

| KR20110056768A (ko) | 반도체 패키지 | |

| JP4602223B2 (ja) | 半導体装置とそれを用いた半導体パッケージ | |

| JP2016063002A (ja) | 半導体装置およびその製造方法 | |

| KR101019706B1 (ko) | 반도체 패키지 및 이의 제조 방법 | |

| JP2012227320A (ja) | 半導体装置 | |

| CN103426872A (zh) | 半导体封装件及其制造方法 | |

| KR20060000729A (ko) | 반도체 칩 패키지 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| PC1203 | Withdrawal of no request for examination |

St.27 status event code: N-1-6-B10-B12-nap-PC1203 |

|

| WITN | Application deemed withdrawn, e.g. because no request for examination was filed or no examination fee was paid | ||

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-3-3-R10-R18-oth-X000 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-2-2-P10-P22-nap-X000 |