KR20080098335A - 확장된 재배선층 범프 웨이퍼 반도체 장치와 그 제조 방법 - Google Patents

확장된 재배선층 범프 웨이퍼 반도체 장치와 그 제조 방법 Download PDFInfo

- Publication number

- KR20080098335A KR20080098335A KR1020080042039A KR20080042039A KR20080098335A KR 20080098335 A KR20080098335 A KR 20080098335A KR 1020080042039 A KR1020080042039 A KR 1020080042039A KR 20080042039 A KR20080042039 A KR 20080042039A KR 20080098335 A KR20080098335 A KR 20080098335A

- Authority

- KR

- South Korea

- Prior art keywords

- organic material

- wafer

- dies

- die

- ubm

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H10W72/00—

-

- H10P72/74—

-

- H10P72/7402—

-

- H10W72/019—

-

- H10W74/019—

-

- H10P72/7416—

-

- H10P72/743—

-

- H10W70/60—

-

- H10W70/655—

-

- H10W72/01225—

-

- H10W72/0198—

-

- H10W72/241—

-

- H10W72/248—

-

- H10W72/251—

-

- H10W72/252—

-

- H10W72/29—

-

- H10W72/922—

-

- H10W72/9413—

-

- H10W74/129—

-

- H10W74/141—

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Manufacturing & Machinery (AREA)

- Dicing (AREA)

- Mechanical Treatment Of Semiconductor (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Wire Bonding (AREA)

Abstract

Description

Claims (27)

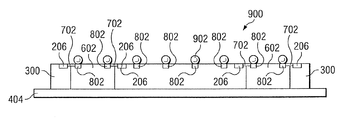

- 반도체 장치에 있어서,상면, 저면 및 둘레 면으로 구성되는 다이와;상기 상면 위에 형성되는 본드 패드와;상기 제 1 다이에 연결되고, 상기 다이의 상기 둘레면 주위에 배치되는 유기물질과;상기 유기물질 부분 상단에 패턴화되는 재배선 층(RDL)과;상기 본드 패드와 상기 재배선 층을 통해 전기통신 되게 상기 유기물질의 상단에 용착되는 범프 하의 금속화 층(UBM)을; 포함하는 것을 특징으로 하는 반도체 장치.

- 제 1항에 있어서,상기 범프 하의 금속화 층(UBM)의 상단에 형성되고, 상기 제 1 다이에 전기적 접속도를 제공하는 솔더 범프를 더 포함하는 것을 특징으로 하는 반도체 장치.

- 제 1항에 있어서,상기 유기물질은 벤조사이클로부텐계(BCB), 폴리이미드(PI) 또는 아크릴 수지 재료를 포함하는 것을 특징으로 하는 반도체 장치.

- 제 1항에 있어서,상기 다이는 톱니형 스트리트 가이드를 따라 복수의 다이들에서 단일화되는 것을 특징으로 하는 반도체 장치.

- 제 1항에 있어서,상기 유기물질은 스핀 코팅 처리 또는 니들 디스펜싱 처리를 이용하여 적용되는 것을 특징으로 하는 반도체 장치.

- 제 1항에 있어서,상기 제 1 다이의 상기 상면 위에 형성되고, 본드 패드 열을 따라 지향되는 복수의 추가 본드 패드들과;UBM 열을 따라 지향되고, 상기 유기물질의 상단에 형성되는 복수의 추가 범프 하의 금속화 층들(UBMs)을; 더 포함하는 것을 특징으로 하는 반도체 장치.

- 제 1항에 있어서,상기 재배선 층은 상기 본드 패드와 전기 통신 되는 일단을 구비하는 재배선 트레이스를 포함하는 것을 특징으로 하는 반도체 장치.

- 톱니형 스트리트 가이드와 함께 지정되고, 웨이퍼의 활성 표면상에 형성되는 본드 패드를 구비하는 상기 웨이퍼를 제공하는 단계와;다이싱 테이프로 상기 웨이퍼를 테이핑하는 단계;복수의 다이들 각각 사이에 복수의 간격들을 갖는 상기 복수의 다이들에서 상기 톱니형 스트리트 가이드를 따라 상기 웨이퍼를 단일화하는 단계와;미리 지정된 거리까지 상기 복수의 간격들을 확장하기 위해 상기 다이싱 테이프를 신장하는 단계와;유기물질의 상면이 상기 복수의 다이들에서 제 1 다이의 상면과 실질적으로 동일평면인 상기 유기물질을 상기 복수의 간격들 각각에 용착하는 단계와;상기 유기물질 부분의 상단에 재배선 층을 패턴화하는 단계와;상기 본드 패드와 상기 재배선 층을 통해 전기통신 되게 상기 유기물질의 상단에 범프 하의 금속화 층(UBM)을 용착하는 단계를; 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 8항에 있어서,상기 범프 하의 금속화 층(UBM)의 상단에 솔더 범프를 형성하는 단계를 더 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 9항에 있어서,복수의 확장된 다이들을 위해 상기 유기물질 부분의 절삭에 의해 상기 웨이퍼를 재단일화하는 단계를 더 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 8항에 있어서,상기 유기물질은 벤조사이클로부텐계(BCB), 폴리이미드(PI) 또는 아크릴 수지 재료를 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 8항에 있어서,상기 유기물질은 스핀 코팅 처리 또는 니들 디스펜싱 처리를 이용하여 적용되는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 8항에 있어서,미리 지정된 거리까지 상기 복수의 간격들을 확장하기 위해 상기 다이싱 테이프를 신장하는 단계는 확장 테이블을 이용하여 실행되는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 10항에 있어서,상기 다이싱 테이프에서 상기 복수의 확장된 다이들 각각 피킹하는 단계를 더 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 반도체 장치 제조 방법에 있어서,톱니형 스트리트 가이드와 함께 지정되고, 웨이퍼의 활성 표면상에 형성되는 본드 패드를 구비하는 상기 웨이퍼를 제공하는 단계와;제 1 다이싱 테이프로 상기 웨이퍼를 테이핑하는 단계와;복수의 다이들 각각 사이에 제 1 간격들을 갖는 상기 복수의 다이들에서 상기 톱니형 스트리트 가이드를 따라 상기 웨이퍼를 단일화되는 단계와;상기 제 1 다이싱 테이프에서 상기 복수의 다이들을 피킹하는 단계와;상기 복수의 다이들 각각 사이에 미리 지정된 폭의 복수의 제 2 간격들을 얻기 위해 제 1 웨이퍼 지지 시스템 상에 상기 복수의 다이들을 배치되는 단계와;재코팅 된 웨이퍼를 위해 유기물질의 상면이 상기 복수의 다이들에서 제 1 다이의 상면과 실질적으로 동일평면인 상기 유기물질을 상기 복수의 간격들 각각에 용착하는 단계와;제 2 웨이퍼 지지 시스템 상으로 상기 재코팅 된 웨이퍼를 이송하는 단계와;상기 유기물질 부분 상에 재배선 층을 패턴화하는 단계와;상기 본드 패드와 상기 재배선 층을 통해 전기통신 되게 상기 유기물질의 상단에 범프 하의 금속화 층(UBM)을 용착하는 단계를; 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 15항에 있어서,상기 범프 하의 금속화 층(UBM)의 상단에 솔더 범프를 형성하는 단계를 더 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 16항에 있어서,복수의 확장된 다이들을 위해 상기 유기물질 부분의 절삭에 의해 상기 웨이퍼를 재단일화하는 단계를 더 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 17항에 있어서,상기 제 2 웨이퍼 지지 시스템에서 상기 복수의 확장된 다이들 각각 피킹하는 단계를 더 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 15항에 있어서,상기 제 1 웨이퍼 지지 시스템은 제 3 다이싱 테이프를 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 15항에 있어서,상기 제 1 또는 제 2 웨이퍼 지지 시스템은 유리, 실리콘 또는 세라믹 기판을 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 15항에 있어서,상기 유기물질은 벤조사이클로부텐계(BCB), 폴리이미드(PI) 또는 아크릴 수지 재료를 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 15항에 있어서,상기 유기물질은 스핀 코팅 처리 또는 니들 디스펜싱 처리를 이용하여 적용되는 것을 특징으로 하는 반도체 장치 제조 방법.

- 반도체 장치 제조 방법에 있어서,상면, 저면, 그리고 둘레 면을 갖는 다이를 제공하는 단계와;상기 상면 위에 형성되는 본드 패드를 제공하는 단계와;상기 제 1 다이에 연결되고, 상기 다이의 상기 둘레면 주위에 배치되는 유기물질을 제공하는 단계와;상기 유기물질 부분의 상단에 패턴화되는 재배선 층(RDL)을 제공하는 단계와;상기 본드 패드와 상기 재배선 층을 통해 전기통신 되게 상기 유기물질의 상단에 용착되는 범프 하의 금속화 층(UBM)을 제공하는 단계를; 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 23항에 있어서,상기 유기물질은 벤조사이클로부텐계(BCB), 폴리이미드(PI) 또는 아크릴 수지 재료를 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 23항에 있어서,상기 제 1 다이는 톱니형 스트리트 가이드를 따라 복수의 다이들에서 단일화되는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 23항에 있어서,상기 유기물질은 스핀 코팅 처리 또는 니들 디스펜싱 처리를 이용하여 적용되는 것을 특징으로 하는 반도체 장치 제조 방법.

- 제 23항에 있어서,상기 제 1 다이의 상기 상면 위에 형성되고, 본드 패드 열을 따라 지향되는 복수의 추가 본드 패드를 제공하는 단계와;UBM 열을 따라 지향되고, 상기 유기물질의 상단에 형성되는 복수의 추가 범프 하의 금속화 층들(UBMs)을 제공하는 단계를; 포함하는 것을 특징으로 하는 반도체 장치 제조 방법.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/744,743 US7687318B2 (en) | 2007-05-04 | 2007-05-04 | Extended redistribution layers bumped wafer |

| US11/744,743 | 2007-05-04 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20080098335A true KR20080098335A (ko) | 2008-11-07 |

| KR101497697B1 KR101497697B1 (ko) | 2015-03-02 |

Family

ID=39938940

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020080042039A Active KR101497697B1 (ko) | 2007-05-04 | 2008-05-06 | 반도체 장치 및 그 제조 방법 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US7687318B2 (ko) |

| KR (1) | KR101497697B1 (ko) |

| SG (3) | SG147384A1 (ko) |

| TW (1) | TWI425583B (ko) |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7723159B2 (en) * | 2007-05-04 | 2010-05-25 | Stats Chippac, Ltd. | Package-on-package using through-hole via die on saw streets |

| US8445325B2 (en) | 2007-05-04 | 2013-05-21 | Stats Chippac, Ltd. | Package-in-package using through-hole via die on saw streets |

| US7829998B2 (en) | 2007-05-04 | 2010-11-09 | Stats Chippac, Ltd. | Semiconductor wafer having through-hole vias on saw streets with backside redistribution layer |

| TWI387014B (zh) * | 2008-06-05 | 2013-02-21 | 南茂科技股份有限公司 | 具有犧牲基板之晶粒重新配置結構及其封裝方法 |

| US8021907B2 (en) * | 2008-06-09 | 2011-09-20 | Stats Chippac, Ltd. | Method and apparatus for thermally enhanced semiconductor package |

| US8298917B2 (en) * | 2009-04-14 | 2012-10-30 | International Business Machines Corporation | Process for wet singulation using a dicing singulation structure |

| US8420554B2 (en) * | 2010-05-03 | 2013-04-16 | Memc Electronic Materials, Inc. | Wafer support ring |

| JP5594661B2 (ja) * | 2010-06-15 | 2014-09-24 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5539077B2 (ja) * | 2010-07-09 | 2014-07-02 | ローム株式会社 | 半導体装置 |

| US9324659B2 (en) * | 2011-08-01 | 2016-04-26 | Stats Chippac, Ltd. | Semiconductor device and method of forming POP with stacked semiconductor die and bumps formed directly on the lower die |

| US8617927B1 (en) | 2011-11-29 | 2013-12-31 | Hrl Laboratories, Llc | Method of mounting electronic chips |

| KR101411813B1 (ko) | 2012-11-09 | 2014-06-27 | 앰코 테크놀로지 코리아 주식회사 | 반도체 디바이스 및 그 제조 방법 |

| US10079160B1 (en) | 2013-06-21 | 2018-09-18 | Hrl Laboratories, Llc | Surface mount package for semiconductor devices with embedded heat spreaders |

| TWI566339B (zh) * | 2014-11-11 | 2017-01-11 | 矽品精密工業股份有限公司 | 電子封裝件及其製法 |

| US10515939B2 (en) * | 2015-02-17 | 2019-12-24 | Mediatek Inc. | Wafer-level package having multiple dies arranged in side-by-side fashion and associated yield improvement method |

| US10037293B2 (en) | 2015-02-17 | 2018-07-31 | Nephos (Hefei) Co. Ltd. | Wafer-level package having asynchronous FIFO buffer used to deal with data transfer between different dies and associated method |

| US9385083B1 (en) | 2015-05-22 | 2016-07-05 | Hrl Laboratories, Llc | Wafer-level die to package and die to die interconnects suspended over integrated heat sinks |

| US10026672B1 (en) | 2015-10-21 | 2018-07-17 | Hrl Laboratories, Llc | Recursive metal embedded chip assembly |

| US9508652B1 (en) | 2015-11-24 | 2016-11-29 | Hrl Laboratories, Llc | Direct IC-to-package wafer level packaging with integrated thermal heat spreaders |

| US9698108B1 (en) * | 2015-12-23 | 2017-07-04 | Intel Corporation | Structures to mitigate contamination on a back side of a semiconductor substrate |

| US9985040B2 (en) * | 2016-01-14 | 2018-05-29 | Micron Technology, Inc. | Integrated circuitry and 3D memory |

| US10483239B2 (en) * | 2016-12-20 | 2019-11-19 | Sandisk Semiconductor (Shanghai) Co. Ltd. | Semiconductor device including dual pad wire bond interconnection |

| US10566268B1 (en) * | 2018-09-26 | 2020-02-18 | Nxp Usa, Inc. | Package to die connection system and method therefor |

| US10950562B1 (en) | 2018-11-30 | 2021-03-16 | Hrl Laboratories, Llc | Impedance-matched through-wafer transition using integrated heat-spreader technology |

| US20230317630A1 (en) * | 2022-03-31 | 2023-10-05 | Intel Corporation | Package structures with collapse control features |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0011418A1 (en) * | 1978-11-20 | 1980-05-28 | THE GENERAL ELECTRIC COMPANY, p.l.c. | Manufacture of electroluminescent display devices |

| JPH01280340A (ja) * | 1988-05-06 | 1989-11-10 | Nec Corp | 半導体装置の製造方法 |

| US6511901B1 (en) * | 1999-11-05 | 2003-01-28 | Atmel Corporation | Metal redistribution layer having solderable pads and wire bondable pads |

| TW451436B (en) * | 2000-02-21 | 2001-08-21 | Advanced Semiconductor Eng | Manufacturing method for wafer-scale semiconductor packaging structure |

| TW502344B (en) * | 2000-12-07 | 2002-09-11 | Advanced Semiconductor Eng | Chip scale package structure and its manufacturing method |

| JP3848080B2 (ja) * | 2000-12-19 | 2006-11-22 | 富士通株式会社 | 半導体装置の製造方法 |

| KR20020091327A (ko) * | 2001-05-31 | 2002-12-06 | 삼성전자 주식회사 | 측면 몸체부가 형성되어 있는 웨이퍼 레벨 패키지 및 그제조 방법 |

| US6787895B1 (en) * | 2001-12-07 | 2004-09-07 | Skyworks Solutions, Inc. | Leadless chip carrier for reduced thermal resistance |

| TW544882B (en) * | 2001-12-31 | 2003-08-01 | Megic Corp | Chip package structure and process thereof |

| US7208344B2 (en) * | 2004-03-31 | 2007-04-24 | Aptos Corporation | Wafer level mounting frame for ball grid array packaging, and method of making and using the same |

| US20050227382A1 (en) * | 2004-04-02 | 2005-10-13 | Hui Angela T | In-situ surface treatment for memory cell formation |

| JP2005322858A (ja) * | 2004-05-11 | 2005-11-17 | Shinko Electric Ind Co Ltd | 半導体装置の製造方法 |

| KR20060115095A (ko) * | 2005-05-04 | 2006-11-08 | 삼성전기주식회사 | 기밀특성이 우수한 표면탄성파 소자 패키지 |

| US7208345B2 (en) * | 2005-05-11 | 2007-04-24 | Infineon Technologies Ag | Method of manufacturing a semiconductor device comprising stacked chips and a corresponding semiconductor device |

| US7728437B2 (en) * | 2005-11-23 | 2010-06-01 | Fairchild Korea Semiconductor, Ltd. | Semiconductor package form within an encapsulation |

| US7750452B2 (en) * | 2007-05-04 | 2010-07-06 | Stats Chippac, Ltd. | Same size die stacked package having through-hole vias formed in organic material |

| US8390107B2 (en) * | 2007-09-28 | 2013-03-05 | Intel Mobile Communications GmbH | Semiconductor device and methods of manufacturing semiconductor devices |

| SG152086A1 (en) * | 2007-10-23 | 2009-05-29 | Micron Technology Inc | Packaged semiconductor assemblies and associated systems and methods |

| US8030136B2 (en) * | 2008-05-15 | 2011-10-04 | Stats Chippac, Ltd. | Semiconductor device and method of conforming conductive vias between insulating layers in saw streets |

| US8093151B2 (en) * | 2009-03-13 | 2012-01-10 | Stats Chippac, Ltd. | Semiconductor die and method of forming noise absorbing regions between THVS in peripheral region of the die |

-

2007

- 2007-05-04 US US11/744,743 patent/US7687318B2/en active Active

-

2008

- 2008-04-02 TW TW097111945A patent/TWI425583B/zh active

- 2008-04-14 SG SG200802844-1A patent/SG147384A1/en unknown

- 2008-04-14 SG SG201004169-7A patent/SG162789A1/en unknown

- 2008-04-14 SG SG2013070099A patent/SG194354A1/en unknown

- 2008-05-06 KR KR1020080042039A patent/KR101497697B1/ko active Active

-

2010

- 2010-02-11 US US12/704,345 patent/US8716853B2/en active Active

-

2014

- 2014-03-14 US US14/214,120 patent/US9406647B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| SG162789A1 (en) | 2010-07-29 |

| US20100140799A1 (en) | 2010-06-10 |

| TWI425583B (zh) | 2014-02-01 |

| US20140197540A1 (en) | 2014-07-17 |

| SG147384A1 (en) | 2008-11-28 |

| US20080272368A1 (en) | 2008-11-06 |

| KR101497697B1 (ko) | 2015-03-02 |

| TW200903677A (en) | 2009-01-16 |

| SG194354A1 (en) | 2013-11-29 |

| US9406647B2 (en) | 2016-08-02 |

| US8716853B2 (en) | 2014-05-06 |

| US7687318B2 (en) | 2010-03-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101497697B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| US11508635B2 (en) | Semiconductor package having routable encapsulated conductive substrate and method | |

| KR102597994B1 (ko) | 배선 구조체 및 이의 형성 방법 | |

| US7843052B1 (en) | Semiconductor devices and fabrication methods thereof | |

| KR102067840B1 (ko) | 반도체 디바이스 및 그 제조 방법 | |

| CN102543923B (zh) | 半导体器件及其制造方法 | |

| TWI427754B (zh) | 在鋸道上使用通孔晶粒之封裝中的封裝 | |

| KR101523383B1 (ko) | 반도체 소자 및 그 제조 방법 | |

| CN109904127B (zh) | 封装结构及封装方法 | |

| KR101514137B1 (ko) | 반도체 패키지 제조 방법 및 이를 이용한 반도체 패키지 | |

| US20180130769A1 (en) | Substrate Based Fan-Out Wafer Level Packaging | |

| CN104733379A (zh) | 在半导体管芯上形成细节距的rdl的半导体器件和方法 | |

| KR101235498B1 (ko) | 집적 수동 컴포넌트를 구비한 집적 회로를 패키징하기 위한 방법 및 시스템 | |

| KR101571604B1 (ko) | 단일 마스크 패키지 장치 및 방법 | |

| KR101758999B1 (ko) | 반도체 디바이스 및 그 제조 방법 | |

| CN104425419A (zh) | 半导体器件及其制造方法 | |

| US20240203919A1 (en) | Integrated circuit having exposed leads | |

| US20180130720A1 (en) | Substrate Based Fan-Out Wafer Level Packaging | |

| CN121035063A (zh) | 电子装置及制造电子装置的方法 | |

| KR20170036235A (ko) | 웨이퍼 레벨의 팬 아웃 패키지 및 그 제조 방법 | |

| KR20170036238A (ko) | 웨이퍼 레벨의 적층형 팬 아웃 패키지 및 그 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PA0109 | Patent application |

St.27 status event code: A-0-1-A10-A12-nap-PA0109 |

|

| PG1501 | Laying open of application |

St.27 status event code: A-1-1-Q10-Q12-nap-PG1501 |

|

| A201 | Request for examination | ||

| E13-X000 | Pre-grant limitation requested |

St.27 status event code: A-2-3-E10-E13-lim-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| PA0201 | Request for examination |

St.27 status event code: A-1-2-D10-D11-exm-PA0201 |

|

| E902 | Notification of reason for refusal | ||

| PE0902 | Notice of grounds for rejection |

St.27 status event code: A-1-2-D10-D21-exm-PE0902 |

|

| T11-X000 | Administrative time limit extension requested |

St.27 status event code: U-3-3-T10-T11-oth-X000 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| P11-X000 | Amendment of application requested |

St.27 status event code: A-2-2-P10-P11-nap-X000 |

|

| P13-X000 | Application amended |

St.27 status event code: A-2-2-P10-P13-nap-X000 |

|

| R17-X000 | Change to representative recorded |

St.27 status event code: A-3-3-R10-R17-oth-X000 |

|

| E701 | Decision to grant or registration of patent right | ||

| PE0701 | Decision of registration |

St.27 status event code: A-1-2-D10-D22-exm-PE0701 |

|

| GRNT | Written decision to grant | ||

| PR0701 | Registration of establishment |

St.27 status event code: A-2-4-F10-F11-exm-PR0701 |

|

| PR1002 | Payment of registration fee |

St.27 status event code: A-2-2-U10-U11-oth-PR1002 Fee payment year number: 1 |

|

| PG1601 | Publication of registration |

St.27 status event code: A-4-4-Q10-Q13-nap-PG1601 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| S20-X000 | Security interest recorded |

St.27 status event code: A-4-4-S10-S20-lic-X000 |

|

| FPAY | Annual fee payment |

Payment date: 20180208 Year of fee payment: 4 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 4 |

|

| FPAY | Annual fee payment |

Payment date: 20190212 Year of fee payment: 5 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 5 |

|

| S22-X000 | Recordation of security interest cancelled |

St.27 status event code: A-4-4-S10-S22-lic-X000 |

|

| R18-X000 | Changes to party contact information recorded |

St.27 status event code: A-5-5-R10-R18-oth-X000 |

|

| FPAY | Annual fee payment |

Payment date: 20200214 Year of fee payment: 6 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 6 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 7 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 8 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 9 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 10 |

|

| PR1001 | Payment of annual fee |

St.27 status event code: A-4-4-U10-U11-oth-PR1001 Fee payment year number: 11 |

|

| PN2301 | Change of applicant |

St.27 status event code: A-5-5-R10-R13-asn-PN2301 St.27 status event code: A-5-5-R10-R11-asn-PN2301 |

|

| P22-X000 | Classification modified |

St.27 status event code: A-4-4-P10-P22-nap-X000 |