KR101774256B1 - 산화물 반도체 박막 트랜지스터 및 그 제조 방법 - Google Patents

산화물 반도체 박막 트랜지스터 및 그 제조 방법 Download PDFInfo

- Publication number

- KR101774256B1 KR101774256B1 KR1020100113326A KR20100113326A KR101774256B1 KR 101774256 B1 KR101774256 B1 KR 101774256B1 KR 1020100113326 A KR1020100113326 A KR 1020100113326A KR 20100113326 A KR20100113326 A KR 20100113326A KR 101774256 B1 KR101774256 B1 KR 101774256B1

- Authority

- KR

- South Korea

- Prior art keywords

- active layer

- layer

- electrode

- thin film

- oxide semiconductor

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 111

- 239000010409 thin film Substances 0.000 title claims abstract description 109

- 238000004519 manufacturing process Methods 0.000 title description 18

- 239000000758 substrate Substances 0.000 claims abstract description 73

- 239000010408 film Substances 0.000 claims abstract description 57

- 230000001681 protective effect Effects 0.000 claims abstract description 19

- 239000000463 material Substances 0.000 claims description 29

- 230000002093 peripheral effect Effects 0.000 claims description 26

- 238000000034 method Methods 0.000 claims description 22

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 10

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 claims description 10

- 239000010936 titanium Substances 0.000 claims description 10

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 claims description 8

- 229910052733 gallium Inorganic materials 0.000 claims description 8

- 229910052732 germanium Inorganic materials 0.000 claims description 8

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 claims description 8

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 claims description 7

- 229910052698 phosphorus Inorganic materials 0.000 claims description 7

- 239000011574 phosphorus Substances 0.000 claims description 7

- 239000011734 sodium Substances 0.000 claims description 7

- 229910052725 zinc Inorganic materials 0.000 claims description 7

- 108091006149 Electron carriers Proteins 0.000 claims description 6

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 claims description 6

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 6

- 229910052793 cadmium Inorganic materials 0.000 claims description 6

- 239000010949 copper Substances 0.000 claims description 6

- 229910052735 hafnium Inorganic materials 0.000 claims description 6

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 claims description 6

- 229910052738 indium Inorganic materials 0.000 claims description 6

- 229910052744 lithium Inorganic materials 0.000 claims description 6

- 229910052707 ruthenium Inorganic materials 0.000 claims description 6

- 229910052708 sodium Inorganic materials 0.000 claims description 6

- 229910052718 tin Inorganic materials 0.000 claims description 6

- 229910052719 titanium Inorganic materials 0.000 claims description 6

- LEONUFNNVUYDNQ-UHFFFAOYSA-N vanadium atom Chemical compound [V] LEONUFNNVUYDNQ-UHFFFAOYSA-N 0.000 claims description 6

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 claims description 5

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 claims description 5

- BDOSMKKIYDKNTQ-UHFFFAOYSA-N cadmium atom Chemical compound [Cd] BDOSMKKIYDKNTQ-UHFFFAOYSA-N 0.000 claims description 5

- 229910052802 copper Inorganic materials 0.000 claims description 5

- 229910052759 nickel Inorganic materials 0.000 claims description 5

- 229910052763 palladium Inorganic materials 0.000 claims description 5

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 4

- 229910052757 nitrogen Inorganic materials 0.000 claims description 4

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 claims description 4

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 380

- 229910052751 metal Inorganic materials 0.000 description 35

- 239000002184 metal Substances 0.000 description 35

- 230000008569 process Effects 0.000 description 17

- 239000004973 liquid crystal related substance Substances 0.000 description 13

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 12

- 230000003071 parasitic effect Effects 0.000 description 12

- 239000011651 chromium Substances 0.000 description 11

- 238000000059 patterning Methods 0.000 description 11

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 8

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 8

- 229910052581 Si3N4 Inorganic materials 0.000 description 8

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 8

- 229910052782 aluminium Inorganic materials 0.000 description 8

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 8

- 239000003990 capacitor Substances 0.000 description 8

- 229910052750 molybdenum Inorganic materials 0.000 description 8

- 239000011733 molybdenum Substances 0.000 description 8

- MGRWKWACZDFZJT-UHFFFAOYSA-N molybdenum tungsten Chemical compound [Mo].[W] MGRWKWACZDFZJT-UHFFFAOYSA-N 0.000 description 8

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 8

- 229910052814 silicon oxide Inorganic materials 0.000 description 8

- 239000002356 single layer Substances 0.000 description 8

- 229910001887 tin oxide Inorganic materials 0.000 description 8

- 239000011701 zinc Substances 0.000 description 8

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 7

- 229910052804 chromium Inorganic materials 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 6

- 239000011810 insulating material Substances 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 239000010703 silicon Substances 0.000 description 6

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 6

- 239000011787 zinc oxide Substances 0.000 description 6

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 5

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 5

- BEQNOZDXPONEMR-UHFFFAOYSA-N cadmium;oxotin Chemical compound [Cd].[Sn]=O BEQNOZDXPONEMR-UHFFFAOYSA-N 0.000 description 4

- 229920001940 conductive polymer Polymers 0.000 description 4

- 238000000151 deposition Methods 0.000 description 4

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 4

- 229910001195 gallium oxide Inorganic materials 0.000 description 4

- YZZNJYQZJKSEER-UHFFFAOYSA-N gallium tin Chemical compound [Ga].[Sn] YZZNJYQZJKSEER-UHFFFAOYSA-N 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- YYMDQTCBBBXDRH-UHFFFAOYSA-N lanthanum;oxocopper Chemical compound [La].[Cu]=O YYMDQTCBBBXDRH-UHFFFAOYSA-N 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 230000004048 modification Effects 0.000 description 4

- YULBFWISFJEMQB-UHFFFAOYSA-N oxotin titanium Chemical compound [Sn]=O.[Ti] YULBFWISFJEMQB-UHFFFAOYSA-N 0.000 description 4

- KYKLWYKWCAYAJY-UHFFFAOYSA-N oxotin;zinc Chemical compound [Zn].[Sn]=O KYKLWYKWCAYAJY-UHFFFAOYSA-N 0.000 description 4

- 238000002161 passivation Methods 0.000 description 4

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 4

- 230000014509 gene expression Effects 0.000 description 3

- 239000011572 manganese Substances 0.000 description 3

- 238000005240 physical vapour deposition Methods 0.000 description 3

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 3

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- 229910004609 CdSn Inorganic materials 0.000 description 2

- 229910018565 CuAl Inorganic materials 0.000 description 2

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 2

- 229910005538 GaSn Inorganic materials 0.000 description 2

- 229910008433 SnCU Inorganic materials 0.000 description 2

- 229910008487 TiSn Inorganic materials 0.000 description 2

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- HOFIJBMBYYEBNM-UHFFFAOYSA-N copper;oxotin Chemical compound [Cu].[Sn]=O HOFIJBMBYYEBNM-UHFFFAOYSA-N 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 229910052748 manganese Inorganic materials 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 238000004549 pulsed laser deposition Methods 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 238000002207 thermal evaporation Methods 0.000 description 2

- 229910052720 vanadium Inorganic materials 0.000 description 2

- 229910052726 zirconium Inorganic materials 0.000 description 2

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 229910052789 astatine Inorganic materials 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000005401 electroluminescence Methods 0.000 description 1

- 238000005566 electron beam evaporation Methods 0.000 description 1

- 238000000313 electron-beam-induced deposition Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 230000008020 evaporation Effects 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 229910052809 inorganic oxide Inorganic materials 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 229910021645 metal ion Inorganic materials 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000001451 molecular beam epitaxy Methods 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 230000000087 stabilizing effect Effects 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

Abstract

산화물 반도체 박막 트랜지스터는 기판 상에 형성되고 제1 면적을 갖는 게이트 전극, 게이트 전극을 커버하는 게이트 절연막, 게이트 절연막 상에 형성되고 제1 면적보다 작은 제2 면적을 갖는 활성층, 활성층의 소스 영역에 접촉하는 소스 전극, 활성층의 드레인 영역에 접촉하는 드레인 전극 등을 구비한다. 활성층, 소스 전극 및 드레인 전극 상에는 보호막이 제공된다. 산화물 반도체 박막 트랜지스터는 고전압에 대한 높은 내구성 및 신뢰성을 가질 수 있다.

Description

본 발명은 트랜지스터 및 그 제조 방법에 관한 것으로서, 더욱 상세하게는 산화물 반도체 박막 트랜지스터 및 그 제조 방법에 관한 것이다.

산화물 반도체 박막 트랜지스터는 액정 표시 장치(LCD) 및 유기 전계 발광 표시 장치(OLED) 등과 같은 표시 장치에서 스위칭 소자 또는 구동 소자로서 많이 사용되고 있다. 특히, 산화물 반도체 박막 트랜지스터가 표시 장치의 게이트 스캔 회로(gate scan circuit) 및 백플레인(backplane) 등의 기본 구조로서 사용되기 위해서는, 게이트 전극에 인가되는 고전압에 대한 높은 내구성과 신뢰성을 가져야 한다. 그러나 종래의 산화물 반도체 박막 트랜지스터는 게이트 전극에 고전압이 인가되면, 쉽게 열화되거나 파괴되는 문제점이 있다.

본 발명의 일 목적은 고전압에 대한 높은 내구성과 신뢰성을 갖는 산화물 반도체 박막 트랜지스터를 제공하는 것이다.

본 발명의 다른 목적은 상기 산화물 반도체 박막 트랜지스터의 제조 방법을 제공하는 것이다.

다만, 본 발명의 해결하고자 하는 과제는 상기 언급된 과제에 한정되는 것이 아니며, 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위에서 다양하게 확장될 수 있을 것이다.

본 발명의 일 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터는, 기판 상에 배치되고 제1 면적을 갖는 게이트 전극, 상기 게이트 전극을 커버하는 게이트 절연막, 상기 게이트 절연막 상에 배치되고 상기 제1 면적보다 실질적으로 작은 제2 면적을 갖는 활성층, 상기 활성층의 소스 영역에 접촉되도록 상기 활성층 상에 배치되는 소스 전극, 상기 활성층의 드레인 영역에 접촉되게 상기 활성층 상에 배치되는 드레인 전극, 그리고 상기 활성층, 상기 소스 전극 및 상기 드레인 전극을 커버하는 보호막을 포함할 수 있다.

예시적인 실시예들에 있어서, 상기 게이트 절연막은 상기 활성층의 제2 면적보다 실질적으로 작은 제3 면적을 가질 수 있고 상기 기판에 대해 상방으로 돌출되는 돌출부를 포함할 수 있다.

예시적인 실시예들에 있어서, 상기 게이트 절연막의 돌출부에 의하여 상기 활성층의 주변부보다 상기 활성층의 중앙부가 상방으로 돌출되어, 상기 활성층이 꺾여진 형상을 가질 수 있다.

예시적인 실시예들에 있어서, 상기 활성층의 중앙부는 채널 영역을 포함할 수 있고, 상기 활성층의 주변부는 상기 소스 영역 및 상기 드레인 영역을 포함할 수 있다.

예시적인 실시예들에 있어서, 상기 산화물 반도체 박막 트랜지스터는 상기 활성층과 상기 소스 전극 및 상기 드레인 전극 사이에 배치되는 에치 스토퍼층(etch stopper layer)을 더 포함할 수 있다.

예시적인 실시예들에 있어서, 상기 에치 스토퍼층은 상기 소스 전극과 상기 드레인 전극을 상기 활성층에 접촉시키는 콘택 홀 구조(contact hole structure)를 가질 수 있다. 다른 예시적인 실시예들에 있어서, 상기 에치 스토퍼층은 상기 소스 전극과 상기 드레인 전극을 상기 활성층의 주변부에만 접촉시키는 아일랜드 구조(island structure)를 가질 수 있다.

예시적인 실시예들에 있어서, 상기 활성층은 인듐(In), 아연(Zn), 갈륨(Ga) 및 주석(Sn) 중에서 적어도 하나 이상을 포함하는 산화물 계열의 물질을 포함할 수 있다. 이 경우, 상기 산화물 계열의 물질은 리튬(Li), 나트륨(Na), 망간(Mn), 니켈(Ni), 팔라듐(Pd), 구리(Cu), 카드뮴(Cd), 탄소(C), 질소(N), 인(P), 티타늄(Ti), 지르코늄(Zr), 하프늄(Hf), 바나듐(V), 루테늄(Ru), 게르마늄(Ge) 및 불소(F) 중에서 적어도 하나 이상을 더 포함할 수 있다.

예시적인 실시예들에 있어서, 상기 활성층의 전자 캐리어 농도는 약 1012/cm3 ~ 1018/cm3 정도가 될 수 있다.

본 발명의 다른 목적을 달성하기 위하여, 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터의 제조 방법에 있어서, 기판의 상부에 제1 면적을 갖는 게이트 전극을 형성하고, 상기 게이트 전극을 커버하기 위하여 상기 게이트 전극의 상부에 게이트 절연막을 형성한다. 상기 게이트 절연막의 상부에 상기 제1 면적보다 실질적으로 작은 제2 면적을 갖는 활성층을 형성하고, 상기 활성층의 상부에 상기 활성층의 소스 영역 및 드레인 영역에 각각 접촉되는 소스 전극 및 드레인 전극을 형성한다. 상기 활성층, 상기 소스 전극 및 상기 드레인 전극을 커버하는 보호막을 형성한다.

예시적인 실시예들에 있어서, 상기 활성층과 상기 소스 전극 및 상기 드레인 전극 사이에는 에치 스토퍼층(etch stopper layer)이 추가적으로 형성될 수 있다.

예시적인 실시예들에 있어서, 상기 게이트 절연막은 상기 활성층의 제2 면적보다 실질적으로 작은 제3 면적을 가지고, 상방으로 돌출되는 돌출부를 포함할 수 있다.

예시적인 실시예들에 있어서, 상기 활성층은 상기 게이트 절연막의 돌출부에 의해 주변부보다 중앙부가 상방으로 돌출되는 절곡된 구조를 가질 수 있다.

예시적인 실시예들에 있어서, 상기 활성층의 중앙부는 채널 영역을 포함할 수 있고, 상기 활성층의 주변부는 상기 소스 영역 및 상기 드레인 영역을 포함할 수 있다.

본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터는 게이트 전극에 고전압이 인가되더라도 쉽게 열화되거나 파괴되지 않기 때문에, 표시 장치에서 고전압이 사용되는 게이트 스캔 회로 및 백플레인 등의 기본 구조로서 사용될 수 있다. 또한, 본 발명의 실시예들에 따르면, 간단한 공정들을 통해 고전압에 대한 높은 내구성과 신뢰성을 갖는 산화물 반도체 박막 트랜지스터를 제조할 수 있다.

다만, 본 발명의 효과는 상기 언급한 효과에 한정되는 것이 아니며, 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위에서 다양하게 확장될 수 있을 것이다.

도 1은 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터의 단면도이다.

도 2는 본 발명의 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터의 단면도이다.

도 3은 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터를 제조하는 방법을 설명하기 위한 순서도이다.

도 4a 내지 도 4g는 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터의 제조 방법을 설명하기 위한 단면도들이다.

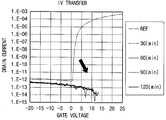

도 5는 종래의 산화물 반도체 박막 트랜지스터의 고전압에 대한 내구성 및 신뢰성을 나타내는 그래프이다.

도 6은 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터의 고전압에 대한 내구성 및 신뢰성을 나타내는 그래프이다.

도 7은 본 발명의 또 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터를 나타내는 단면도이다.

도 8은 본 발명의 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터를 제조 방법을 설명하기 위한 순서도이다.

도 9a 내지 도 9f는 본 발명의 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터의 제조 방법을 설명하기 위한 단면도들이다.

도 10은 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터를 구비하는 표시 장치의 백플레인을 나타내는 평면도이다.

도 2는 본 발명의 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터의 단면도이다.

도 3은 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터를 제조하는 방법을 설명하기 위한 순서도이다.

도 4a 내지 도 4g는 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터의 제조 방법을 설명하기 위한 단면도들이다.

도 5는 종래의 산화물 반도체 박막 트랜지스터의 고전압에 대한 내구성 및 신뢰성을 나타내는 그래프이다.

도 6은 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터의 고전압에 대한 내구성 및 신뢰성을 나타내는 그래프이다.

도 7은 본 발명의 또 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터를 나타내는 단면도이다.

도 8은 본 발명의 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터를 제조 방법을 설명하기 위한 순서도이다.

도 9a 내지 도 9f는 본 발명의 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터의 제조 방법을 설명하기 위한 단면도들이다.

도 10은 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터를 구비하는 표시 장치의 백플레인을 나타내는 평면도이다.

본문에 개시되어 있는 본 발명의 실시예들에 대해서, 특정한 구조적 내지 기능적 설명들은 단지 본 발명의 실시예를 설명하기 위한 목적으로 예시된 것으로, 본 발명의 실시예들은 다양한 형태로 실시될 수 있으며 본문에 설명된 실시예들에 한정되는 것으로 해석되어서는 아니 된다.

본 발명은 다양한 변경을 가할 수 있고 여러 가지 형태를 가질 수 있는바, 특정 실시예들을 도면에 예시하고 본문에 상세하게 설명하고자 한다. 그러나 이는 본 발명을 특정한 개시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다.

제 1, 제 2 등의 용어는 다양한 구성 요소들을 설명하는데 사용될 수 있지만, 상기 구성 요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성 요소를 다른 구성 요소로부터 구별하는 목적으로 사용될 수 있다. 예를 들어, 본 발명의 권리 범위로부터 이탈되지 않은 채 제1 구성 요소는 제 2 구성요소로 명명될 수 있고, 유사하게 제 2 구성요소도 제1 구성 요소로 명명될 수 있다.

어떤 구성 요소가 다른 구성 요소에 "연결되어" 있다거나 "접촉되어" 있다고 언급된 때에는, 그 다른 구성 요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성 요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성 요소가 다른 구성요소에 "직접 연결되어" 있다거나 "직접 접촉되어" 있다고 언급된 때에는, 중간에 다른 구성 요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성 요소들 간의 관계를 설명하는 다른 표현들, 즉 "~사이에"와 "바로 ~사이에" 또는 "~에 인접하는"과 "~에 직접 인접하는" 등도 마찬가지로 해석되어야 한다.

본 출원에서 사용한 용어는 단지 특정한 실시예들을 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 출원에서, "포함하다", "구비하다" 또는 "가지다" 등의 용어는 설시된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성 요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미이다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥상 가지는 의미와 일치하는 의미인 것으로 해석되어야 하며, 본 출원에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.

이하, 첨부한 도면들을 참조하여, 본 발명의 예시적인 실시예들에 따른 산화물 박막 트랜지스터 및 그 제조 방법에 대하여 상세하게 설명한다. 첨부된 도면상의 실질적으로 동일한 구성 요소들에 대해서는 동일한 참조 부호들을 사용하고 동일한 구성 요소들에 대해서 반복되는 설명은 생략한다.

도 1은 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터를 설명하기 위한 단면도이다.

도 1을 참조하면, 산화물 반도체 박막 트랜지스터(100)는 하부 게이트 구조(bottom gate structure)를 가질 수 있다. 이 경우, 산화물 반도체 박막 트랜지스터(100)는 기판(110), 게이트 전극(120), 게이트 절연막(130), 활성층(140), 에치 스토퍼층(150), 소스 전극(160), 드레인 전극(170) 및 보호막(180)을 포함할 수 있다.

일반적으로, 산화물 반도체 박막 트랜지스터는 비정질 실리콘 박막 트랜지스터(amorphous silicon thin film transistor)에 비하여 캐리어 이동도(carrier mobility)가 높고, 문턱 전압(threshold voltage)이 크게 쉬프트하지 않기 때문에 고해상도(high resolution)를 구현하는 표시 장치에서 널리 사용되고 있다. 그러나 종래의 산화물 반도체 박막 트랜지스터에 있어서, 게이트 전극과 활성층 사이에 발생하는 기생 커패시턴스 때문에, 게이트 전극의 면적을 활성층의 면적보다 크게 할 수 없다는 한계가 있다. 예를 들어, 종래의 산화물 반도체 박막 트랜지스터를 사용하는 표시 장치에서는, 상기 게이트 전극에 인가되는 전압이 변동함에 따라, 기생 커패시턴스에 의하여 픽셀 전극의 전압이 크게 변동하는 킥백(kickback) 현상이 발생할 수 있다. 이에 비하여, 예시적인 실시예들에 따른 산화물 반도체 박막 트랜지스터(100)에 있어서, 게이트 전극(120)이 활성층(140)의 면적보다 실질적으로 큰 면적을 가지며, 활성층(140) 상에 에치 스토퍼층(170)이 제공되기 때문에 후술하는 바와 같이 게이트 전극(120)과 활성층(140) 사이에 발생하는 기생 커패시턴스를 감소시킬 수 있다.

도 1에 도시한 바와 같이, 산화물 반도체 박막 트랜지스터(100)는 하부 게이트 구조 중에서 역 스태거드 구조(reverse staggered structure)를 가질 수 있다. 여기서, 기판(110) 상에 게이트 전극(120), 게이트 절연막(130), 활성층(140), 에치 스토퍼층(150), 소스 전극(160)과 드레인 전극(170) 및 보호막(180)이 순차적으로 제공될 수 있다.

기판(110)은 반도체 기판, 절연 기판 등을 포함할 수 있다. 예를 들면, 기판(110)은 유리 기판, 플라스틱 기판, 실리콘 기판, 게르마늄 기판 등을 포함할 수 있다.

게이트 전극(120)은 기판(110) 상에 배치되며, 활성층(140)의 제2 면적에 비하여 실질적으로 큰 제1 면적을 가질 수 있다. 게이트 전극(120)은 알루미늄(Al), 크롬(Cr), 몰리브덴(Mo), 몰리브덴 텅스텐(MoW) 등의 금속 또는 전도성 폴리머(conductive polymer)를 포함할 수 있다. 예시적인 실시예들에 있어서, 게이트 전극(120)은 기판(110) 상에 소정의 금속층을 형성하고, 이러한 금속층을 패터닝하는 방식으로 수득될 수 있다. 이 때, 상기 금속층은 단층 구조 또는 다층 구조를 가질 수 있다. 다른 예시적인 실시예들에 따르면, 기판(110)과 게이트 전극(120) 사이에 버퍼층(도시되지 않음)이 추가적으로 배치될 수 있다.

게이트 절연막(130)은 게이트 전극(120)을 커버(cover)하면서 기판(110) 상에 배치된다. 이 때, 게이트 절연막(130)은 산화물, 질화물, 산질화물 등과 같은 절연 물질을 포함할 수 있다. 예를 들면, 게이트 절연막(130)은 실리콘 산화물(SiOX), 실리콘 질화물(SiNX), 실리콘 산질화물(SiOXNY) 등을 포함할 수 있다. 게이트 절연막(130)은 게이트 전극(120)과 활성층(140)을 서로 전기적으로 절연시킬 수 있다. 예시적인 실시예들에 있어서, 게이트 절연막(130)은 게이트 전극(120)의 중앙부 상에서 기판(110)에 대해 실질적으로 수직하게 돌출되는 돌출부를 포함할 수 있다. 또한, 게이트 절연막(130)의 돌출부는 기판(110)에 대해 경사진 측벽을 가질 수 있다. 즉, 상기 돌출부의 하부 면적이 그 상부 면적에 비하여 실질적으로 클 수 있다.

본 발명의 실시예들에 있어서, 게이트 절연막(130)의 돌출부는 활성층(140)의 제2 면적보다 실질적으로 작은 제3 면적을 가질 수 있다. 이 때, 게이트 절연막(130)의 돌출부에 의해 게이트 절연막(130) 상에 제공되는 활성층(140)의 형상이 결정될 수 있다.

활성층(140)은 게이트 절연막(130) 상에 위치하며, 게이트 전극(120)의 제1 면적보다 실질적으로 작고 상기 돌출부의 제3 면적보다 실질적으로 큰 제2 면적을 가질 수 있다. 도 1에 도시된 바와 같이, 활성층(140)은 게이트 전극(120)에 공간적으로 중첩될 수 있다. 한편, 활성층(140)은 게이트 절연막(130)의 돌출부에 의하여 주변부보다 중앙부가 상부로 돌출되어 절곡된 형상을 가질 수 있다. 즉, 활성층(140)은 중앙부, 주변부 및 이들 사이에 위치하는 단차부를 구비할 수 있다. 활성층(140)은 채널 영역(channel region), 소스 영역(source region) 및 드레인 영역(drain region)을 제공할 수 있다. 이 경우, 상기 중앙부는 상기 채널 영역을 포함할 수 있고, 상기 주변부는 상기 소스 영역 및 상기 드레인 영역을 포함할 수 있다.

본 발명의 실시예들에 있어서, 활성층(140)은 산화물 계열의 물질을 포함할 수 있다. 예를 들면, 활성층(140)은 인듐(In), 아연(Zn), 갈륨(Ga) 및 주석(Sn) 중에서 적어도 하나의 금속 이상을 포함하는 금속 산화물 계열의 물질로 구성될 수 있다. 또한, 활성층(140)은 리튬(Li), 나트륨(Na), 망간(Mn), 니켈(Ni), 팔라듐(Pd), 구리(Cu), 카드뮴(Cd), 탄소(C), 질소(N), 인(P), 티타늄(Ti), 지르코늄(Zr), 하프늄(Hf), 바나듐(V), 루테늄(Ru), 게르마늄(Ge) 및 불소(F) 중에서 적어도 하나 이상을 포함할 수 있다. 예를 들면, 활성층(140)은 아연 산화물(ZnOX), 아연 갈륨 산화물(ZnGaXOY), 아연 인듐 산화물(ZnInXOY), 아연 주석 산화물(ZnSnXOY), 갈륨 인듐 아연 산화물(GaInXZnYOZ), 주석 산화물(SnOX), 카드뮴 주석 산화물(CdSnXOY), 갈륨 주석 산화물(GaSnXOY), 티타늄 주석 산화물(TiSnXOY), 구리 알루미늄 산화물(CuAlXOY), 주석 구리 산화물(SnCuXOY), 란탄 구리 산화물(LaCuXOY) 등을 포함할 수 있다. 다만, 전술한 산화물들은 예시적인 것들로서, 활성층(140)을 구성하는 산화물 계열의 물질이 이들에 한정되는 것이 아니다.

본 발명의 실시예들에 따르면, 전술한 산화물을 포함하는 활성층(140)의 전자 캐리어 농도는 약 1012/cm3 내지 약 1018/cm3 정도가 될 수 있다. 그 결과, 산화물 반도체 박막 트랜지스터(100)는 오프 상태에서 누설 전류가 감소될 수 있고, 온-오프 특성이 개선될 수 있으며, 핀치-오프 상태에서 포화 전류 및 스위칭 속도 등이 향상될 수 있다. 다른 예시적인 실시예들에 있어서, 활성층(140)과 게이트 절연막(130) 사이에 산화물로 이루어진 계면 안정층(도시되지 않음)이 추가적으로 배치될 수도 있다.

에치 스토퍼층(150)은 활성층(140) 상에 배치되며, 활성층(140)의 일부를 커버할 수 있다. 예를 들어, 에치 스토퍼층(150)은 활성층(140) 중에서 소스 전극(160) 및 드레인 전극(170)에 접촉되지 않는 비접촉 영역(non-contact region)을 커버할 수 있다. 예시적인 실시예들에 있어서, 에치 스토퍼층(150)은 게이트 절연막(130) 상에 활성층(140)에 대해 식각 선택비를 갖는 물질층을 형성한 후, 활성층(140)이 소스 전극(160) 및 드레인 전극(170)과 접촉하는 소스 영역과 드레인 영역 상에 위치하는 상기 물질층을 제거하여 수득될 수 있다. 그 결과, 에치 스토퍼층(150)에는 활성층(140)의 소스 영역 일부와 드레인 영역 일부가 노출되도록 하는 콘택 홀들이 형성될 수 있다. 도 1에서는 소스 전극(160)과 드레인 전극(170)이 활성층(140)에 홀 형태로 접촉되게 하는 콘택 홀 구조(contact hole structure)의 에치 스토퍼층(150)이 도시되어 있으나, 에치 스토퍼층(150)은 소스 전극(160)과 드레인 전극(170)이 활성층(140)의 주변 영역에만 접촉되게 하는 아일랜드 구조(island structure)를 가질 수도 있다. 다만, 이러한 에칭 스토퍼층(150)의 형상은 예시적인 것이며, 에치 스토퍼층(150)의 구조는 요구되는 조건에 따라 다양하게 변경될 수 있다. 이와 같이, 에치 스토퍼층(150)은 소스 전극(160) 및 드레인 전극(170)이 활성층(140)에 접촉되는 면적을 감소시킴으로써, 활성층(140)과 게이트 전극(120) 사이에 발생하는 기생 커패시턴스를 감소시킬 수 있다. 한편, 에치 스토퍼층(150)은 산화물 반도체 박막 트랜지스터(100)를 제조하기 위한 후속 공정 동안, 활성층(140)이 외부에 노출됨에 따라 발생되는 데미지(damage)를 방지하는 보호막의 역할도 수행할 수 있다.

소스 전극(160)과 드레인 전극(170)은 에치 스토퍼층(150) 상에 배치되며, 각기 활성층(140)의 소스 영역과 드레인 영역에 접촉될 수 있다. 예를 들면, 소스 전극(160)과 드레인 전극(170)은 각기 알루미늄(Al), 크롬(Cr), 몰리브덴(Mo), 몰리브덴 텅스텐(MoW) 등의 금속을 포함할 수 있다. 예시적인 실시예들에 있어서, 소스 전극(160)과 드레인 전극(170)은 에치 스토퍼층(150)에 형성된 콘 홀들을 매립하면서 에치 스토퍼층(150) 상에 금속층을 형성하고, 이와 같은 금속층을 패터닝함으로써 수득될 수 있다. 이 때, 상기 금속층은 단층 구조 또는 다층 구조를 가질 수 있다.

보호막(180)은 에치 스토퍼층(150), 소스 전극(160) 및 드레인 전극(170)을 커버하도록 이들의 상에 배치된다. 이 때, 에치 스토퍼층(150)은 활성층(140)이 소스 전극(160) 및 드레인 전극(170)에 접촉되지 않는 비접촉 영역을 커버하기 때문에, 보호막(180)이 활성층(140) 대신에 에치 스토퍼층(150)을 커버할 수 있다. 예를 들면, 보호막(180)은 실리콘 산화물, 실리콘 질화물, 유기 절연물 등을 소정 두께로 증착하여 수득될 수 있다.

전술한 바와 같이, 산화물 반도체 박막 트랜지스터(100)는 게이트 전극(120)의 제1 면적이 활성층(140)의 제2 면적보다 실질적으로 크기 때문에 게이트 전극(120)에 고전압이 인가되더라도 쉽게 열화되거나 파괴되지 않을 수 있다. 또한, 에치 스토퍼층(150)에 의하여 소스 전극(160)과 드레인 전극(170)이 활성층(140)에 접촉되는 영역이 감소하기 때문에 게이트 전극(120)과 활성층(140) 사이에 발생하는 기생 커패시턴스를 감소시킬 수 있다. 이에 따라, 산화물 반도체 박막 트랜지스터(100)는 고전압에 대한 높은 내구성과 신뢰성을 가질 수 있으므로, 표시 장치에서 고전압이 사용되는 게이트 스캔 회로 및 백플레인 등의 기본 구조로서 사용될 수 있다.

도 2는 본 발명의 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터를 설명하기 위한 단면도이다.

도 2를 참조하면, 산화물 반도체 박막 트랜지스터(200)는 하부 게이트 구조를 가질 수 있다. 산화물 반도체 박막 트랜지스터(200)는 기판(210), 게이트 전극(220), 게이트 절연막(230), 활성층(240), 에치 스토퍼층(250), 소스 전극(260), 드레인 전극(270) 및 보호막(280)을 포함할 수 있다.

도 1을 참조하여 설명한 산화물 반도체 박막 트랜지스터(100)는 소스 전극(160)과 드레인 전극(170)이 활성층(140)에 홀 형태로 접촉되도록 하는 콘택 홀 구조의 에치 스토퍼층(150)을 구비한다. 이에 비하여, 도 2에 예시적으로 도시한 산화물 반도체 박막 트랜지스터(200)는 소스 전극(260)과 드레인 전극(270)이 활성층(140)의 주변 영역에만 접촉되도록 하는 아일랜드 구조의 에치 스토퍼층(250)을 구비한다.

상술한 구성들을 갖는 산화물 반도체 박막 트랜지스터들(100, 200)에 있어서, 게이트 전극들(120, 220)의 제1 면적이 활성층들(140, 240)의 제2 면적보다 실질적으로 커서 게이트 전극들(120, 220)에 고전압이 인가되더라도 쉽게 열화되거나 파괴되지 않을 수 있다. 또한, 산화물 반도체 박막 트랜지스터들(100, 200)은 에치 스토퍼층들(150, 250)에 의하여 소스 전극들(160, 260)과 드레인 전극들(170, 270)이 활성층들(140, 240)에 접촉되는 콘택 영역이 감소되기 때문에 게이트 전극들(120, 220)과 활성층들(140, 240) 사이에 발생하는 기생 커패시턴스들을 감소시킬 수 있다. 그 결과, 산화물 반도체 박막 트랜지스터들(100, 200)은 고전압에 대한 높은 내구성과 신뢰성을 확보할 수 있으므로, 액정 표시 장치 및 유기 전계 발광 표시 장치 등과 같은 표시 장치에서 고전압이 인가되는 게이트 스캔 회로 및 백플레인 등의 기본 구조로서 사용될 수 있다.

도 3은 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터의 제조 방법을 설명하기 위한 순서도이다. 도 3에 있어서, 도 1을 참조하여 설명한 산화물 반도체 박막 트랜지스터와 실질적으로 동일하거나 유사한 구성을 가지는 산화물 반도체 박막 트랜지스터의 제조 방법에 대하여 예시적으로 설명한다.

도 3을 참조하면, 기판 상에 제1 면적을 갖는 게이트 전극을 형성한(단계 S110) 후, 상기 게이트 전극을 커버하도록 기판 상에 게이트 절연막을 형성한다(단계 S120). 이 경우, 상기 게이트 전극은 후속하여 형성되는 활성층의 제2 면적보다 실질적으로 큰 제1 면적을 갖도록 형성된다. 예시적인 실시예들에 있어서, 상기 게이트 전극은 상기 기판 상에 소정의 금속층을 형성하고, 형성된 금속층을 패터닝하여 형성될 수 있다. 상기 게이트 절연막은 상기 게이트 전극을 충분히 커버할 수 있는 두께로 형성될 수 있다. 예시적인 실시예들에 있어서, 상기 게이트 절연막은 상기 게이트 전극의 중앙부 상에 상기 활성층의 제2 면적보다 실질적으로 작은 제3 면적을 갖는 돌출부를 포함하도록 형성될 수 있다. 이 때, 상기 게이트 절연막의 돌출부는 상기 기판에 대해 실질적으로 수직하게 돌출됨으로써, 상기 게이트 절연막 상에 형성되는 상기 활성층의 형상을 결정할 수 있다. 다른 예시적인 실시예들에 따르면, 상기 기판과 상기 게이트 전극 사이에 버퍼층을 추가적으로 형성할 수 있으며, 상기 활성층과 상기 게이트 절연막 사이에 계면 안정층을 형성할 수도 있다.

상기 게이트 절연막 상에 상기 게이트 전극의 제1 면적보다 실질적으로 작은 제2 면적을 갖는 활성층을 형성한다(단계 S130). 예시적인 실시예들에 있어서, 상기 활성층은 상기 게이트 절연막의 돌출부에 의해 주변부보다 중앙부가 상부로 돌출되어 절곡되는 구조를 가질 수 있다. 예를 들면, 상기 활성층은 상기 게이트 절연막의 돌출부에 의해 그 주변부보다 중앙부가 상부로 돌출되어 꺾여진 형상을 가질 수 있다. 즉, 상기 활성층은 중앙부, 주변부 및 이들 사이에 형성되는 단차부를 포함할 수 있으며, 상기 게이트 전극에 공간적으로 중첩될 수 있다.

상기 활성층 상에 에치 스토퍼층을 형성한(단계 S140) 다음, 상기 에치 스토퍼층 상에 상기 활성층의 소스 영역과 드레인 영역에 각각 접촉되는 소스 전극 및 드레인 전극을 형성한다(단계 S150). 상기 에치 스토퍼층은 상기 활성층을 부분적으로 커버하도록 형성될 수 있다. 예시적인 실시예들에 있어서, 상기 에치 스토퍼층은 상기 게이트 절연막 및 상기 활성층 상에 이들에 대해 식각 선택비를 갖는 물질층을 형성하고, 상기 활성층이 상기 소스 전극 및 상기 드레인 전극과 접촉하는 소스 영역과 드레인 영역의 상부에 위치하는 물질막을 제거여 형성될 수 있다. 상기 소스 전극과 상기 드레인 전극은 상기 에치 스토퍼층에 형성된 콘택 홀을 채우면서 상기 에치 스토퍼층 상에 금속층을 형성하고, 상기 금속층을 패터닝하여 수득될 수 있다.

이후에, 상기 에치 스토퍼층, 상기 소스 전극 및 상기 드레인 전극을 커버하는 보호막을 형성한다(단계 S160). 이 경우, 상기 에치 스토퍼층은 상기 활성층이 상기 소스 및 드레인 전극에 접촉되지 않는 비접촉 영역을 커버하기 때문에, 상기 보호막은 상기 활성층 대신에 상기 에치 스토퍼층을 커버할 수 있다. 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터의 제조 방법에 있어서, 상기 게이트 전극이 상기 활성층보다 실질적으로 큰 면적을 갖도록 형성하고, 상기 에치 스토퍼층이 형성되기 때문에, 고전압에 대한 높은 내구성과 신뢰성을 갖는 산화물 반도체 박막 트랜지스터를 제조할 수 있다.

도 4a 내지 도 4g는 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터의 제조 방법을 설명하기 위한 단면도들이다.

도 4a를 참조하면, 먼저 기판(110)을 마련한다. 예를 들면, 기판(110)으로 유리 기판, 플라스틱 기판 등의 절연 기판이나 실리콘 기판, 게르마늄 기판 등과 같은 반도체 기판을 이용할 수 있다.

도 4b를 참조하면, 후속하여 형성되는 활성층(140)의 제2 면적보다 실질적으로 큰 제1 면적을 가지는 게이트 전극(120)을 기판(110) 상에 형성한다. 따라서 활성층(140)은 게이트 전극(120)과 공간적으로 중첩될 수 있다. 예를 들면, 게이트 전극(120)은 알루미늄(Al), 크롬(Cr), 몰리브덴(Mo), 몰리브덴 텅스텐(MoW) 등의 금속 또는 전도성 폴리머 등을 사용하여 형성될 수 있다. 예시적인 실시예들에 있어서, 게이트 전극(120)은 기판(110) 상에 제1 금속층을 형성한 후, 사진 식각 공정 등으로 상기 제1 금속층을 패터닝하여 형성될 수 있다. 게이트 전극(120)은 단층 구조 또는 다층 구조를 가질 수 있다. 다른 예시적인 실시예들에 따르면, 기판(110)과 게이트 전극(120) 사이에 버퍼층(도시되지 않음)이 형성될 수 있다. 상기 버퍼층은 기판(110)에 대한 게이트 전극(120)의 접착력을 향상시킬 수 있으며, 후속하는 공정 동안 게이트 전극(120)으로부터 금속 이온들 및/또는 도전성 이온들이 기판(110)으로 확산되는 현상을 방지할 수 있다. 기판(110) 상에 상기 버퍼층이 형성되는 경우, 게이트 전극(120)은 상기 버퍼층 상에 상기 제1 금속층을 형성한 다음, 상기 제1 금속층을 식각하여 수득될 수 있다.

도 4c를 참조하면, 기판(110) 상에 게이트 전극(120)을 덮는 게이트 절연막(130)을 형성한다. 게이트 절연막(130)은 산화물, 질화물, 산질화물 등을 사용하여 형성될 수 있다. 예를 들면, 게이트 절연막(130)은 실리콘 산화물, 실리콘 질화물, 실리콘 산질화물 등을 사용하여 형성될 수 있다. 게이트 절연막(130)은 게이트 전극(120)을 후속하는 활성층(140)으로부터 전기적으로 절연시키는 기능을 수행할 수 있다.

게이트 절연막(130)은 게이트 전극(120)의 중앙부 상에서 기판(110)에 대해 실질적으로 수직하게 돌출되는 돌출부를 포함하도록 형성될 수 있다. 이 경우, 상기 돌출부는 소정의 각도로 경사진 측벽을 가질 수 있다. 게이트 절연막(130)의 돌출부는 활성층(140)의 제2 면적보다 실질적으로 작은 제3 면적으로 형성될 수 있다. 이와 같은 돌출부에 의해 게이트 절연막(130) 상에 형성되는 활성층(140)의 형상이 변화될 수 있다. 예를 들면, 게이트 절연막(130)의 돌출부에 의해 활성층(140)의 주변부보다 활성층(140)의 중앙부가 기판(110)으로부터 상방으로 돌출되어 꺾여진 형상을 가질 수 있다. 다른 예시적인 실시예들에 따르면, 게이트 절연막(130)과 활성층(140) 사이에 계면 안정층(도시되지 않음)이 추가적으로 형성될 수 있다. 예를 들면, 상기 계면 안정층은 산화물 계열의 물질을 사용하여 형성될 수 있다.

도 4d를 참조하면, 활성층(140)을 게이트 절연막(130) 상에 형성한다. 상술한 바와 같이, 활성층(140)과 게이트 전극(120)은 공간적으로 중첩될 수 있다. 이 때, 활성층(140)의 제2 면적은 게이트 전극(120)의 제1 면적보다 실질적으로 작고, 게이트 절연막(130)에 형성되는 돌출부의 제3 면적보다 실질적으로 클 수 있다. 또한, 활성층(140)은 게이트 절연막(130)의 돌출부에 의해 그 주변부보다 중앙부가 상부로 돌출되어 꺾여진 구조를 가질 수 있다. 즉, 활성층(140)은 중앙부, 주변부 및 이들 사이에 위치하는 단차부를 포함할 수 있다. 활성층(140)이 채널 영역, 소스 영역 및 드레인 영역을 제공할 경우, 활성층(140)의 중앙부는 상기 채널 영역을 포함할 수 있고, 활성층(140)의 주변부는 상기 소스 영역과 상기 드레인 영역을 포함할 수 있다.

활성층(140)은 산화물 계열의 물질을 사용하여 형성될 수 있다. 예를 들면, 활성층(140)은 인듐(In), 아연(Zn), 갈륨(Ga), 주석(Sn) 중에서 적어도 하나 이상을 포함하는 산화물 계열의 물질을 사용하여 형성될 수 있다. 또한, 활성층(140)의 상기 산화물 계열의 물질은 리튬(Li), 나트륨(Na), 망간(Mn), 니켈(Ni), 팔라듐(Pd), 구리(Cu), 카드뮴(Cd), 탄소(C), 질소(N), 인(P), 티타늄(Ti), 지르코늄(Zr), 하프늄(Hf), 바나듐(V), 루테늄(Ru), 게르마늄(Ge) 및 불소(F) 중에서 적어도 하나 이상을 포함할 수 있다. 예를 들어, 활성층(140)은 아연 산화물(ZnOX), 아연 갈륨 산화물(ZnGaXOY), 아연 인듐 산화물(ZnInXOY), 아연 주석 산화물(ZnSnXOY), 갈륨 인듐 아연 산화물(GaInXZnYOZ), 주석 산화물(SnOX), 카드뮴 주석 산화물(CdSnXOY), 갈륨 주석 산화물(GaSnXOY), 티타늄 주석 산화물(TiSnXOY), 구리 알루미늄 산화물(CuAlXOY), 주석 구리 산화물(SnCuXOY), 란탄 구리 산화물(LaCuXOY) 등을 사용하여 형성될 수 있다. 다만, 활성층(140)을 형성하기 위한 산화물 계열의 물질이 이들에 의해 한정되는 것이 아니다.

본 발명의 실시예들에 있어서, 활성층(140)은 게이트 절연막(130) 상에 산화물 계열의 물질을 스퍼터링(sputtering) 공정, 전자빔 증착(electron beam evaporation) 공정, 열 증착(thermal evaporation) 공정, 레이저 분자빔 증착(laser molecular beam epitaxy evaporation) 공정, 펄스 레이저 증착(pulsed laser deposition) 공정 등과 같은 물리적 기상 증착(physical vapor deposition; PVD)으로 증착하여 형성될 수 있다. 상술한 산화물 계열의 물질을 포함하는 활성층(140)은 약 1012/cm3 내지 약 1018/cm3 정도의 전자 캐리어 농도를 가질 수 있다. 그 결과, 상기 산화물 반도체 박막 트랜지스터의 오프 상태에서 누설 전류가 감소될 수 있으며, 온-오프 특성이 개선될 수 있으며, 핀치-오프 상태에서 포화 전류 및 스위칭 속도 등이 향상될 수 있다.

도 4e를 참조하면, 활성층(140) 상에 에치 스토퍼층(150)을 형성한다. 에치 스토퍼층(150)은 활성층(140)을 부분적으로 커버할 수 있다. 예를 들어, 에치 스토퍼층(150)은 활성층(140)이 후혹하여 형성되는 소스 전극(160) 및 드레인 전극(170)과 접촉하지 않는 비접촉 영역을 커버할 수 있다. 에치 스토퍼층(150)을 형성하는 과정에 있어서, 게이트 절연막(130) 및 활성층(140)에 대해 식각 선택비를 갖는 물질을 사용하여 게이트 절연막(130)과 활성층(140) 상에 물질층을 형성한 후, 활성층(140)이 소스 전극(160) 및 드레인 전극(170)에 각기 접촉되는 소스 영역과 드레인 영역 상에 위치하는 상기 물질층을 식각하여 형성될 수 있다. 따라서 에치 스토퍼층(150)에는 활성층(140)의 소스 영역의 일부와 드레인 영역 일부를 노출시키는 콘택 홀들이 형성될 수 있다. 소스 전극(160)과 드레인 전극(170)은 상기 콘택 홀들을 통해 각기 상기 소스 영역과 상기 드레인 영역에 접촉될 수 있다. 그러나 상기 콘택 홀들의 위치와 형상은 에치 스토퍼층(150)의 구조에 따라 달라질 수 있다. 도 4e에서는 소스 전극(160)과 드레인 전극(170)이 활성층(140)에 접촉되게 하는 콘택 홀들을 포함하는 에치 스토퍼층(150)이 도시되어 있으나, 도 2에 도시한 바와 같이, 에치 스토퍼층(150)은 소스 전극(160)과 드레인 전극(170)을 활성층(140)의 주변부에만 접촉되게 하는 아일랜드 형태를 가질 수도 있다. 이와 같이, 에치 스토퍼층(150)의 구조는 요구되는 조건에 따라 다양하게 변경될 수 있다.

전술한 바와 같이, 산화물 반도체 박막 트랜지스터의 게이트 전극(120)의 제1 면적이 활성층(140)의 제2 면적보다 실질적으로 크기 때문에, 게이트 전극(120)과 활성층(140) 사이에 소정의 기생 커패시턴스가 발생될 수 있다. 여기서, 상술한 구조를 갖는 에치 스토퍼층(150)을 통하여 소스 전극(160) 및 드레인 전극(170)이 활성층(140)에 접촉되는 면적을 감소시킴으로써, 활성층(140)과 게이트 전극(120) 사이에서 발생하는 기생 커패시턴스를 감소시킬 수 있다. 또한, 에치 스토퍼층(150)이 산소와의 결합력을 갖는 무기 산화물로 형성될 수 있기 때문에, 산화물 반도체 박막 트랜지스터를 제조하는 동안 에치 스토퍼층(150)에 의해 활성층(140)이 노출됨에 따라 발생하는 데미지를 방지할 수 있다.

도 4f를 참조하면, 소스 전극(160)과 드레인 전극(170)을 에치 스토퍼층(150) 상에 형성한다. 예를 들면, 소스 전극(160)과 드레인 전극(170)은 각기 알루미늄(Al), 크롬(Cr), 몰리브덴(Mo), 몰리브덴 텅스텐(MoW) 등의 금속을 사용하여 형성될 수 있다. 예시적인 실시예들에 있어서, 소스 전극(160)과 드레인 전극(170)은 에치 스토퍼층(150)에 형성된 콘택 홀들을 채우도록 에치 스토퍼층(150) 상에 제2 금속층을 형성한 다음, 상기 제2 금속층을 패터닝하여 형성될 수 있다. 소스 및 드레인 전극(160, 170)은 각기 단층 구조 또는 다층 구조를 가질 수 있다. 소스 전극(160) 및 드레인 전극(170)은 각기 에치 스토퍼층(150)의 콘택 홀들을 통해 활성층(140)의 소스 영역과 드레인 영역에 접촉될 수 있다. 예를 들어, 소스 전극(160) 및 드레인 전극(170)은 상기 콘택 홀들을 매립하면서 활성층(140)에 접촉할 수 있다. 다른 예시적인 실시예들에 따라 에치 스토퍼층(150)이 아일랜드 구조를 가지는 경우, 소스 전극(160) 및 드레인 전극(170)은 활성층(140)의 주변부에만 접촉될 수 있다.

도 4g를 참조하면, 에치 스토퍼층(150), 소스 전극(160) 및 드레인 전극(170)을 커버하는 보호막(180)을 형성한다. 에치 스토퍼층(150)이 소스 전극(160) 및 드레인 전극(170)에 접촉되지 않는 활성층(140)의 비접촉 영역을 커버하기 때문에, 보호막(180)이 활성층(140) 대신 에치 스토퍼층(150)을 커버할 수 있다. 예를 들면, 보호막(180)은 실리콘 산화물, 실리콘 질화물, 유기 절연 물질 등을 사용하여 형성될 수 있다.

상술한 바와 같이, 산화물 반도체 박막 트랜지스터는 게이트 전극(120)의 제1 면적이 활성층(140)의 제2 면적보다 실질적으로 크기 때문에 게이트 전극(120)에 고전압이 인가되더라도 쉽게 열화되거나 파괴되지 않으며, 에치 스토퍼층(150)에 의하여 소스 전극(160)과 드레인 전극(170)이 활성층(140)에 접촉되는 면적이 감소하기 때문에 게이트 전극(120)과 활성층(140) 사이에 발생하는 기생 커패시턴스를 감소시킬 수 있다. 이에 따라, 상기 산화물 반도체 박막 트랜지스터는 고전압에 대한 높은 내구성과 신뢰성을 확보할 수 있어, 표시 장치에서 고전압이 사용되는 게이트 스캔 회로 및 백플레인 등의 기본 구성 요소로 사용될 수 있다.

도 5는 종래의 산화물 반도체 박막 트랜지스터의 고전압에 대한 내구성 및 신뢰성을 나타내는 그래프이고, 도 6은 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터의 고전압에 대한 내구성 및 신뢰성을 나타내는 그래프이다. 도 5 및 도 6에 있어서, 상기 산화물 반도체 박막 트랜지스터들의 게이트 전극들에 인가되는 게이트 전압(Vg)에 따라 드레인 전극들에 흐르는 드레인 전류(Id)의 변화와 스트레스 시간(stress time)에 따른 문턱 전압(Vth)의 변화를 나타내는 그래프(이하, 전류-전압 트랜스퍼 특성이라고 함)가 예시되어 있다. 이러한 전류-전압 트랜스퍼 특성은 채널 폭 대 길이의 비가 약 50:10 정도인 산화물 반도체 박막 트랜지스터에 대하여 약 2 시간 정도의 스트레스 시간 동안 게이트-소스 전압(Vgs)을 45V 정도로 인가함으로써 측정하였다. 이 때, 기준 파형(REF)은 기준 상태의 전류-전압 트랜스퍼 특성을 나타내고, 30분 파형(30(min))은 30분 정도가 경과된 후에 변화된 전류-전압 트랜스퍼 특성을 나타낸다. 또한, 60분 파형(60(min))은 60분 정도가 경과된 후에 변화된 전류-전압 트랜스퍼 특성을 나타내고, 90분 파형(90(min))은 90분 정도가 경과된 후에 변화된 전류-전압 트랜스퍼 특성을 나타내며, 120분 파형(120(min))은 120분 정도가 경과된 후에 변화된 전류-전압 트랜스퍼 특성을 나타낸다.

도 5에 도시한 바와 같이, 종래의 산화물 반도체 박막 트랜지스터는 게이트 전극에 고전압이 지속적으로 인가되는 경우, 소자가 열화되거나 파괴되어 기준 상태의 전류-전압 트랜스퍼 특성을 유지할 수 없게 된다. 실제로, 액정 표시 장치 및 유기 전계 발광 표시 장치 등과 같은 표시 장치에서, 게이트 스캔 회로의 기본 구조로서 사용되는 산화물 반도체 박막 트랜지스터에 약 45V 정도의 게이트-소스 전압(Vgs)이 인가되는 구간은 하나의 프레임(frame)마다 한 번씩 반복될 수 있다. 종래의 산화물 반도체 박막 트랜지스터는 이러한 고전압 구간에서 열화되거가 파괴되기 때문에, 상기 표시 장치에 게이트 블록 결함(gate block defect; GBD) 및 게이트 오픈(gate open; G/O) 등과 같은 불량을 초래할 수 있다. 또한, 메모리용 표시 장치가 연구됨에 따라, 메모리용 표시 장치의 백플레인의 기본 구조로서 사용되는 산화물 반도체 박막 트랜지스터에 약 40V 이상의 구동 전압이 인가되고 있다. 그러나 종래의 산화물 반도체 박막 트랜지스터는 이러한 고전압의 구동 전압에 의하여 열화되거가 파괴되기 때문에, 상기 메모리용 표시 장치가 정상적으로 동작하지 못하는 원인이 될 수 있다.

반면에, 도 6에 도시한 바와 같이, 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터는 게이트 전극에 고전압이 지속적으로 인가되는 경우에도, 소자가 열화되거나 파괴되지 않고, 기준 상태의 전류-전압 트랜스퍼 특성을 실질적으로 유지할 수 있다. 예를 들어, 상기 산화물 반도체 박막 트랜지스터에 약 45V 정도의 게이트-소스 전압(Vgs)이 지속적으로 인가되고 있음에도 불구하고, 문턱 전압(Vth)은 초기의 약 1.35V 정도에서 2시간 정도가 경과 후에도 약 3.9V 정도를 유지하여 대략 2.6V 정도의 변화만을 수반하고 있다. 이와 같이, 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터에 있어서, 게이트 전극의 제1 면적이 활성층의 제2 면적보다 실질적으로 크고, 상기 게이트 전극과 상기 활성층 사이에 발생하는 기생 커패시컨스를 감소시키기 위한 에치 스토퍼층이 제공됨으로써, 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터는 고전압에 대한 높은 내구성과 신뢰성을 확보할 수 있다. 따라서 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터는 종래의 산화물 반도체 박막 트랜지스터와는 달리, 액정 표시 장치 및 유기 전계 발광 표시 장치 등과 같은 표시 장치에서 고전압이 인가되는 게이트 스캔 회로 및 백플레인 등의 기본 구조로서 이용될 수 있다.

도 7은 본 발명의 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터를 나타내는 단면도이다.

도 7을 참조하면, 산화물 반도체 박막 트랜지스터(300)는 하부 게이트 구조를 가질 수 있다. 산화물 반도체 박막 트랜지스터(300)는 기판(310), 게이트 전극(320), 게이트 절연막(330), 활성층(340), 소스 전극(360), 드레인 전극(370) 및 보호막(380)을 포함할 수 있다.

산화물 반도체 박막 트랜지스터(300)는 역 스태거드 구조를 가질 수 있으며, 이 경우에는 기판(310) 상에 게이트 전극(320), 게이트 절연막(330), 활성층(340), 소스 전극(360)과 드레인 전극(370) 및 보호막(380)이 순차적으로 배치될 수 있다. 기판(310)은 유리 기판, 플라스틱 기판, 반도체 기판 등을 포함할 수 있다.

게이트 전극(320)은 기판(310) 상에 배치되며, 활성층(340)의 제2 면적보다 실질적으로 큰 제1 면적을 가질 수 있다. 게이트 전극(320)은 알루미늄, 크롬, 몰리브덴, 몰리브덴 텅스텐 등의 금속 및/또는 전도성 폴리머 등으로 구성될 수 있다. 게이트 전극(320)은 기판(310) 상에 소정의 금속을 증착하고, 증착된 금속을 패터닝하여 수득될 수 있다. 예를 들면, 게이트 전극(320)은 단층 구조 또는 다층 구조를 가질 수 있다. 다른 예시적인 실시예들에 있어서, 기판(310)과 게이트 전극(320) 사이에 버퍼층(도시되지 않음)이 배치될 수 있다.

게이트 절연막(330)은 게이트 전극(320)을 덮으면서 기판(310) 상에 배치된다. 게이트 절연막(330)은 실리콘 산화물, 실리콘 질화물, 실리콘 산질화물 등과 같은 절연 물질로 구성될 수 있다. 게이트 절연막(330)은 게이트 전극(320)과 활성층(340)을 전기적으로 절연시킬 수 있다. 게이트 절연막(330)에는 게이트 전극(320)의 중앙부에 대응되는 위치에 활성층(340)의 제2 면적보다 작은 제3 면적을 갖는 돌출부가 형성될 수 있다. 게이트 절연막(330)의 돌출부에 의해 게이트 절연막(330) 상에 위비하는 활성층(340)의 형상이 결정될 수 있다.

활성층(340)은 게이트 절연막(330) 상에 배치된다. 활성층(340)은 게이트 전극(320)의 제1 면적보다 실질적으로 작지만, 게이트 절연막(130)의 돌출부의 제3 면적보다는 실질적으로 큰 제2 면적을 가질 수 있다. 이에 따라, 활성층(340)과 게이트 전극(320)은 서로 공간적으로 중첩될 수 있다. 또한, 게이트 절연막(330)의 돌출부에 의해 활성층(340)의 주변부보다 활성층(340)의 중앙부가 상부로 돌출되어 경사진 형상을 가질 수 있다. 즉, 활성층(340)은 중앙부, 주변부 및 중앙부와 주변부 사이에 위치하는 단차부를 포함할 수 있다. 활성층(340)에는 채널 영역, 소스 영역 및 드레인 영역이 제공될 수 있으며, 이 경우에 활성층(340)의 중앙부는 상기 채널 영역을 포함할 수 있고, 활성층(340)의 주변부는 상기 소스 및 드레인 영역을 포함할 수 있다. 활성층(340)은 산화물 계열의 물질로 구성될 수 있다. 예를 들면, 활성층(340)은 인듐, 아연, 갈륨 및 주석 중에서 적어도 하나 이상을 포함하는 산화물 계열의 물질로 형성될 수 있으며, 상기 산화물 계열의 물질은 리튬, 나트륨, 망간, 니켈, 팔라듐, 구리, 카드뮴, 탄소, 질소, 인, 티타늄, 지르코늄, 하프늄, 바나듐, 루테늄, 게르마늄 및 불소 중에서 적어도 하나 이상을 포함할 수 있다. 예를 들어, 활성층(340)은 아연 산화물, 아연 갈륨 산화물, 아연 인듐 산화물, 아연 주석 산화물, 갈륨 인듐 아연 산화물, 주석 산화물, 카드뮴 주석 산화물, 갈륨 주석 산화물, 티타늄 주석 산화물, 구리 알루미늄 산화물, 주석 구리 산화물, 란탄 구리 산화물 등을 포함할 수 있다. 여기서, 산화물 계열의 물질로 이루어진 활성층(340)의 전자 캐리어 농도는 약 1012/cm3~1018/cm3 정도가 될 수 있다. 이에 따라, 산화물 반도체 박막 트랜지스터(300)는 오프 상태에서 누설 전류가 감소될 수 있고, 온-오프 특성이 개선될 수 있으며, 핀치-오프 상태에서 포화 전류 및 스위칭 속도 등이 향상될 수 있다. 다른 실시예들에 따르면, 활성층(340)과 게이트 절연막(330) 사이에 산화물로 이루어진 계면 안정층(도시되지 않음)이 추가적으로 배치될 수 있다.

소스 전극(360)과 드레인 전극(370)은 활성층(340) 상에 배치되며, 각기 활성층(340)의 소스 영역과 드레인 영역에 접촉될 수 있다. 소스 전극(360)과 드레인 전극(370)은 알루미늄, 크롬, 몰리브덴, 몰리브덴 텅스텐 등과 같은 금속으로 구성될 수 있다. 소스 전극(360)과 드레인 전극(370)은 각기 단층 구조 또는 다층 구조를 가질 수 있다. 소스 전극(360)과 드레인 전극(370)이 활성층(340)에 접촉되는 면적은 소스 전극(360)과 드레인 전극(370)을 형성하기 위한 금속층의 패터닝 과정에서 결정될 수 있다.

보호막(380)은 활성층(340), 소스 전극(360) 및 드레인 전극(370) 상에 배치된다. 예를 들면, 보호막(380)은 실리콘 산화물, 실리콘 질화물, 유기 절연물 등으로 구성될 수 있다.

본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터(300)는 게이트 전극(320)의 제1 면적이 활성층(340)의 제2 면적보다 실질적으로 크기 때문에 게이트 전극(320)에 고전압이 인가되더라도 쉽게 열화되거나 파괴되지 않을 수 있다. 또한, 소스 전극(360)과 드레인 전극(370)이 활성층(340)에 접촉되는 면적을 조절하여 게이트 전극(320)과 활성층(340) 사이에 발생하는 기생 커패시턴스를 감소시킬 수 있다. 따라서 산화물 반도체 박막 트랜지스터(300)는 고전압에 대한 높은 내구성과 신뢰성을 가질 수 있기 때문에, 표시 장치에서 고전압이 사용되는 게이트 스캔 회로 및 백플레인 등의 기본 구조로서 사용될 수 있다.

도 8은 본 발명의 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터의 제조 방법을 설명하기 위한 순서도이다. 도 8에 있어서, 도 7을 참조하여 설명한 산화물 반도체 박막 트랜지스터(300)와 실질적으로 동일하거나 유사한 구조를 가지는 산화물 반도체 박막 트랜지스터의 제조 방법을 예시적으로 설명한다.

도 8을 참조하면, 기판의 상에 제1 면적을 갖는 게이트 전극을 형성한(단계 S310) 후, 상기 게이트 전극을 덮으면서 상기 기판 상에 게이트 절연막을 형성한다(단계 S320). 기판(310)의 상부에 제1 면적을 갖는 게이트 전극(320)이 형성(단계 S310)될 수 있다. 상기 게이트 전극의 제1 면적이 후속하여 형성되는 활성층의 제 2 면적보다 실질적으로 크도록 형성된다. 예시적인 실시예들에 따른 게이트 전극의 형성 과정에 있어서, 상기 기판 상에 소정의 금속층을 형성한 다음, 상기 금속층을 패터닝하여 상기 게이트 전극을 형성할 수 있다. 상기 게이트 절연막은 상기 게이트 전극을 충분히 커버할 수 있는 두께로 형성될 수 있다. 상기 게이트 절연막은 상기 게이트 전극(320)의 중앙부 상부에 위치하는 돌출부를 가질 수 있다. 상기 게이트 절연막의 돌출부는 상기 활성층의 제2 면적보다 실질적으로 작은 제3 면적을 가질 수 있다. 상기 돌출부 상기 기판에 대해 실질적으로 수직하게 돌출되어 그 상부에 형성되는 상기 활성층의 구조를 결정할 수 있다.

상기 게이트 절연막 상에 상기 게이트 전극의 제1 면적보다 실질적으로 작은 제2 면적을 갖는 상기 활성층을 형성한다(단계 S330). 상기 활성층은 상기 게이트 전극에 공간적으로 중첩될 수 있다. 상기 활성층은 상기 게이트 절연막의 돌출부에 의해 주변부보다 중앙부가 실질적으로 돌출되어 절곡된 형상을 가질 수 있다. 즉, 상기 게이트 절연막의 돌출부에 의하여 상기 활성층의 주변부보다 상기 활성층의 중앙부가 돌출될 수 있다. 이러한 활성층(340)의 중앙부와 주변부 사이에는 단차부가 형성될 수 있다.

상기 활성층 상에 상기 활성층의 소스 영역 및 드레인 영역에 각기 접촉되는 소스 전극 및 드레인 전극을 형성한다(단계 S340). 상기 소스 전극 및 상기 드레인 전극을 형성하는 과정에 있어서, 상기 활성층 상에 소정의 금속층을 형성한 후, 상기 금속층을 패터닝하여 상시 소스 및 드레인 전극을 형성할 수 있다. 이 경우, 상기 소스 전극 및 상기 드레인 전극이 상기 활성층에 접촉되는 면적은 상기 금속층을 패터닝하는 동안 결정될 수 있다.

이 후에, 활성층(340), 소스 전극(360) 및 드레인 전극(370)을 커버하는 보호막(380)을 형성한다(단계 S350). 또한, 상기 기판과 상기 게이트 전극 사이에는 버퍼층이 형성될 수 있으며, 상기 게이트 절연막과 상기 활성층 사이에는 계면 안정층이 형성될 수도 있다.

상기 산화물 반도체 박막 트랜지스터에 있어서, 상기 게이트 전극이 상기 활성층보다 실질적으로 큰 면적을 가지고, 상기 소스 및 드레인 전극이 상기 활성층에 접촉되는 면적을 작게 조절할 수 있다. 따라서 고전압에 대한 높은 내구성과 신뢰성을 갖는 산화물 반도체 박막 트랜지스터를 제조할 수 있다.

도 9a 내지 도 9f는 본 발명의 다른 실시예들에 따른 산화물 반도체 박막 트랜지스터의 제조 방법을 설명하기 위한 단면도들이다.

도 9a를 참조하면, 기판(310)을 준비한다. 기판(310)은 유리 기판, 플라스틱 기판, 반도체 기판 등을 포함할 수 있다.

도 9b를 참조하면, 후속하여 형성되는 활성층(340)의 제2 면적보다 실질적으로 큰 제1 면적을 갖는 게이트 전극(320)을 기판(310) 상에 형성한다. 활성층(340)과 게이트 전극(320)은 서로 공간적으로 중첩될 수 있다. 게이트 전극(320)은 알루미늄, 크롬, 몰리브덴, 몰리브덴 텅스텐 등의 금속 및/또는 전도성 폴리머를 사용하여 형성될 수 있다. 게이트 전극(320)은 단층 구조 또는 다층 구조를 가질 수 있다. 다른 예시적인 실시예들에 따르면, 추가적인 버퍼층(도시되지 않음)을 기판(310)과 게이트 전극(320) 사이에 형성할 수 있다.

도 9c를 참조하면, 기판(310) 상에 게이트 전극(320)을 커버하는 게이트 절연막(330을 형성한다. 게이트 절연막(330)은 실리콘 산화물, 실리콘 질화물, 실리콘 산질화물 등과 같은 절연 물질을 사용하여 형성될 수 있다. 게이트 절연막(330)은 게이트 전극(320)을 활성층(340)으로부터 절연시킬 수 있다. 게이트 전극(320)의 중앙부에 대응되는 게이트 절연막(330)은의 중앙부에는 돌출부가 형성될 수 있다. 상기 돌출부는 활성층(340)의 제2 면적보다 실질적으로 작은 제3 면적을 가질 수 있다. 이러한 돌출부에 따라 게이트 절연막(330) 상에 형성되는 활성층(340)의 형상이 변화될 수 있다. 예를 들면, 활성층(340)은 게이트 절연막(330)의 돌출부에 의해 주변부보다 중앙부가 상부로 돌출되는 구조를 가질 수 있다. 다른 예시적인 실시예들에 따르면, 게이트 절연막(330) 상에는 산화물 계열의 물질로 이루어진 계면 안정층(도시되지 않음)이 형성될 수 있다.

도 9d를 참조하면, 활성층(340)을 게이트 절연막(330) 상에 형성한다. 전술한 바와 같이, 활성층(340)은 게이트 전극(320)에 공간적으로 중첩될 수 있다. 활성층(340)의 제2 면적은 게이트 전극(320)의 제1 면적보다 실질적으로 작을 수 있으며, 게이트 절연막(330)의 돌출부의 제3 면적보다 실질적으로 클 수 있다. 따라서 활성층(340)은 게이트 절연막(330)의 돌출부에 의하여 중앙부가 상부로 돌출되는 꺾여진 형상을 가질 수 있다. 활성층(340)의 중앙부와 주변부 사이에는 단차부가 형성될 수 있다. 활성층(340)이 채널 영역, 소스 영역 및 드레인 영역을 구비하는 경우, 활성층(340)의 중앙부는 상기 채널 영역을 포함할 수 있고, 활성층(340)의 주변부는 상기 소스 및 드레인 영역을 포함할 수 있다.

활성층(340)은 산화물 계열의 물질을 사용하여 형성될 수 있다. 예시적인 실시예들에 있어서, 활성층(340)은 인듐, 아연, 갈륨 및 주석 중에서 적어도 하나 이상을 포함하는 산화물 계열의 물질로 형성될 수 있고, 상기 산화물 계열의 물질은 리튬, 나트륨, 망간, 니켈, 팔라듐, 구리, 카드뮴, 탄소, 질소, 인, 티타늄, 지르코늄, 하프늄, 바나듐, 루테늄, 게르마늄 및 불소 중에서 적어도 하나 이상을 더 포함할 수 있다. 예를 들어, 활성층(340)은 아연 산화물, 아연 갈륨 산화물, 아연 인듐 산화물, 아연 주석 산화물, 갈륨 인듐 아연 산화물, 주석 산화물, 카드뮴 주석 산화물, 갈륨 주석 산화물, 티타늄 주석 산화물, 구리 알루미늄 산화물, 주석 구리 산화물, 란탄 구리 산화물 등을 포함할 수 있다. 활성층(340)은 스퍼터링 공정, 전자빔 증착 공정, 열 증착 공정, 레이저 분자빔 증착 공정, 펄스 레이저 증착 공정 등과 같은 물리적 기상 증착 공정을 통해 형성될 수 있다. 상기 산화물 계열의 물질을 포함하는 활성층(340)은 약 1012/cm3~1018/cm3 정도의 전자 캐리어 농도를 가질 수 있다. 그 결과, 산화물 반도체 박막 트랜지스터(300)는 오프 상태에서 누설 전류가 감소될 수 있고, 온-오프 특성이 개선될 수 있으며, 핀치-오프 상태에서 포화 전류 및 스위칭 속도 등이 향상될 수 있다.

도 9e를 참조하면, 소스 전극(360)과 드레인 전극(370)을 활성층(340) 상에 형성한다. 소스 전극(360)과 드레인 전극(370)은 각기 알루미늄, 크롬, 몰리브덴, 몰리브덴 텅스텐 등의 금속을 사용하여 형성될 수 있다. 소스 및 드레인 전극(360, 370)을 형성하는 과정에 있어서, 활성층(340) 상에 소정의 금속층을 형성한 후, 상기 금속층을 패터닝하여 소스 및 드레인 전극(360, 370)을 수득할 수 있다. 소스 및 드레인 전극(360, 370) 각기 단층 구조 또는 다층 구조를 가질 수 있다. 소스 및 드레인 전극(360, 370)이 활성층(340)에 접촉하는 면적은 상기 금속층의 패터닝 시에 결정될 수 있다.

도 9f를 참조하면, 활성층(340), 소스 전극(360) 및 드레인 전극(370) 상에 보호막(380)을 형성한다. 보호막(380)은 실리콘 산화물, 실리콘 질화물, 유기 절연물 등을 소정 두께로 증착하여 형성될 수 있다.

전술한 바와 같이, 산화물 반도체 박막 트랜지스터(300)는 게이트 전극(320)의 제1 면적이 활성층(340)의 제2 면적보다 실질적으로 크기 때문에 게이트 전극(320)에 고전압이 인가되더라도 쉽게 열화되거나 파괴되지 않는다. 또한, 소스 전극(360)과 드레인 전극(370)이 활성층(340)에 접촉되는 면적을 감소시킬 수 있기 때문에 게이트 전극(320)과 활성층(340) 사이에 발생하는 기생 커패시턴스가 감소될 수 있다. 이에 따라, 산화물 반도체 박막 트랜지스터(300)는 고전압에 대한 높은 내구성과 신뢰성을 확보하여, 표시 장치에서 고전압이 사용되는 게이트 스캔 회로 및 백플레인 등의 기본 구조로서 사용될 수 있다.

도 10은 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터를 구비하는 표시 장치의 백플레인을 설명하기 평면도이다.

도 10을 참조하면,상기 표시 장치의 백플레인(1000)은 서로 교차되는 게이트 라인들(GL)과 데이터 라인들(DL)에 의해 정의되는 소정 영역들에 복수의 픽셀들(P1, P2)을 구비할 수 있다. 이 때, 픽셀들(P1, P2) 각각은 스위칭 소자, 액정 커패시터 및 스토리지 커패시터를 포함할 수 있는데, 스위칭 소자로서 산화물 반도체 박막 트랜지스터(TFT)가 사용될 수 있다.

산화물 반도체 박막 트랜지스터(TFT)는 하부 표시판에 구비될 수 있고, 게이트 라인(GL), 데이터 라인(DL) 및 액정 커패시터에 연결될 수 있다. 따라서 산화물 반도체 박막 트랜지스터(TFT)는 게이트 라인(GL)으로부터 공급되는 게이트 신호에 응답하여 데이터 라인(DL)으로부터 공급되는 데이터 신호를 액정 커패시터에 공급할 수 있다. 예를 들면, 산화물 반도체 박막 트랜지스터(TFT)는 게이트 전극을 통하여 게이트 라인(GL)에 연결될 수 있고, 소스 전극을 통하여 데이터 라인(DL)에 연결될 수 있으며, 드레인 전극을 통하여 액정 커패시터에 연결될 수 있다. 일반적으로, 액정 커패시터는 픽셀 전극에 인가되는 데이터 신호와 공통 전극에 인가되는 공통 전압의 전위차로 충전되며, 이러한 충전 전압에 기초하여 액정층의 광투과율을 조절할 수 있다. 이를 위하여, 액정 커패시터는 하부 표시판에 구비된 픽셀 전극과 상부 표시판에 구비된 공통 전극을 포함할 수 있고, 픽셀 전극과 공통 전극 사이에는 액정층을 포함할 수 있다. 다만, 도 10에서는 액정 커패시터로서 산화물 반도체 박막 트랜지스터(TFT)에 연결된 픽셀 전극만이 예시적으로 도시되어 있다.

도 10에 도시된 바와 같이, 산화물 반도체 박막 트랜지스터(TFT)는 하부 게이트 구조(특히, 역 스태거드 구조)를 가질 수 있으며, 기판, 게이트 전극, 게이트 절연막, 활성층, 소스 전극, 드레인 전극 및 보호막을 포함하거나 또는 기판, 게이트 전극, 게이트 절연막, 활성층, 에치 스토퍼층, 소스 전극, 드레인 전극 및 보호막을 포함할 수 있다. 다만, 이러한 산화물 반도체 박막 트랜지스터(TFT)의 구성에 대해서는 상술한 바 있으므로, 중복되는 설명은 생략한다.

상술한 바와 같이, 산화물 반도체 박막 트랜지스터(TFT)는 게이트 전극의 제1 면적이 활성층의 제2 면적보다 실질적으로 커서 게이트 전극에 고전압이 인가되더라도 쉽게 열화되거나 파괴되지 않을 수 있다. 또한, 산화물 반도체 박막 트랜지스터(TFT)는 에치 스토퍼층 또는 소스 전극과 드레인 전극의 패터닝에 의하여 소스 전극과 드레인 전극이 활성층에 컨택하는 영역을 작기 때문에 게이트 전극과 활성층 사이에 발생하는 기생 커패시턴스가 감소될 수 있다.

본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터는 표시 장치 및 이를 포함하는 전자 기기에 넓게 적용될 수 있다. 예를 들어, 본 발명의 실시예들에 따른 산화물 반도체 박막 트랜지스터는 컴퓨터 모니터, 텔레비전, 노트북, 디지털 카메라, 휴대폰, 스마트폰, 피디에이(personal digital assistants; PDA), 피엠피(portable multimedia player; PMP), MP3 플레이어, 차량용 네비게이션, 비디오 폰 등에 폭 넓게 적용될 수 있다.

이상에서는 본 발명의 실시예들을 참조하여 설명하였지만, 해당 기술 분야에서 통상의 지식을 가진 자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

100 ,200, 300:산화물 반도체 박막 트랜지스터

110, 210, 310:기판

120, 220, 320:게이트 전극

130, 230, 330:게이트 절연막

140, 240, 340:활성층

150, 250:에치 스토퍼층

160, 260, 360:소스 전극

170, 270, 370:드레인 전극

180, 280, 380:보호막

110, 210, 310:기판

120, 220, 320:게이트 전극

130, 230, 330:게이트 절연막

140, 240, 340:활성층

150, 250:에치 스토퍼층

160, 260, 360:소스 전극

170, 270, 370:드레인 전극

180, 280, 380:보호막

Claims (15)

- 기판 상에 형성되고, 제1 면적을 갖는 게이트 전극;

상기 기판 상에서 상기 게이트 전극을 커버하는 게이트 절연막;

상기 게이트 절연막 상에 배치되고, 상기 제1 면적보다 작은 제2 면적을 갖는 활성층;

상기 활성층 상에 배치되고, 상기 활성층의 소스 영역에 접촉되는 소스 전극;

상기 활성층 상에 배치되고, 상기 활성층의 드레인 영역에 접촉되는 드레인 전극; 및

상기 활성층, 상기 소스 전극 및 상기 드레인 전극을 커버하는 보호막을 포함하고,

상기 게이트 절연막은 상부로 돌출된 돌출부를 포함하고, 상기 돌출부는 상기 제2 면적보다 작은 제3 면적을 가지며,

상기 활성층은 상기 돌출부에 의해 주변부보다 중앙부가 상부로 돌출된 형상을 갖는 것을 특징으로 하는 산화물 반도체 박막 트랜지스터. - 삭제

- 삭제

- 제 1 항에 있어서, 상기 활성층의 상기 중앙부는 채널 영역을 포함하고, 상기 활성층의 상기 주변부는 상기 소스 영역 및 상기 드레인 영역을 포함하는 것을 특징으로 하는 산화물 반도체 박막 트랜지스터.

- 제 1 항에 있어서,

상기 활성층과 상기 소스 전극 및 상기 드레인 전극 사이에 형성되는 에치 스토퍼층(etch stopper layer)을 더 포함하는 것을 특징으로 하는 산화물 반도체 박막 트랜지스터. - 제 5 항에 있어서, 상기 에치 스토퍼층은 상기 소스 전극과 상기 드레인 전극을 상기 활성층에 접촉시키는 콘택 홀 구조를 갖는 것을 특징으로 하는 산화물 반도체 박막 트랜지스터.

- 제 5 항에 있어서, 상기 에치 스토퍼층은 상기 소스 전극과 상기 드레인 전극을 상기 활성층의 상기 주변부에만 접촉시키는 아일랜드 구조(island structure)를 갖는 것을 특징으로 하는 산화물 반도체 박막 트랜지스터.

- 제 1 항에 있어서, 상기 활성층은 인듐(In), 아연(Zn), 갈륨(Ga) 및 주석(Sn) 중에서 선택된 적어도 하나 이상을 함유하는 산화물 계열의 물질을 포함하는 것을 특징으로 하는 산화물 반도체 박막 트랜지스터.

- 제 8 항에 있어서, 상기 산화물 계열의 물질은 리튬(Li), 나트륨(Na), 망간(Mn), 니켈(Ni), 팔라듐(Pd), 구리(Cu), 카드뮴(Cd), 탄소(C), 질소(N), 인(P), 티타늄(Ti), 지르코늄(Zr), 하프늄(Hf), 바나듐(V), 루테늄(Ru), 게르마늄(Ge) 및 불소(F) 중에서 선택된 적어도 하나 이상을 더 포함하는 것을 특징으로 하는 산화물 반도체 박막 트랜지스터.

- 제 8 항에 있어서, 상기 활성층의 전자 캐리어 농도는 1012/cm3~1018/cm3인 것을 특징으로 하는 산화물 반도체 박막 트랜지스터.

- 기판 상에 제1 면적을 갖는 게이트 전극을 형성하는 단계;

상기 기판 상에 상기 게이트 전극을 커버하는 게이트 절연막을 형성하는 단계;

상기 게이트 절연막 상에 상기 제1 면적보다 작은 제2 면적을 갖는 활성층을 형성하는 단계;

상기 활성층 상에 상기 활성층의 소스 영역 및 드레인 영역에 각기 접촉되는 소스 전극 및 드레인 전극을 형성하는 단계; 및

상기 활성층, 상기 소스 전극 및 상기 드레인 전극 상에 보호막을 형성하는 단계를 포함하고,

상기 게이트 절연막은 상부로 돌출된 돌출부를 포함하고, 상기 돌출부는 상기 제2 면적보다 작은 제3 면적을 가지며,

상기 활성층은 상기 돌출부에 의해 주변부보다 중앙부가 상부로 돌출된 형상을 갖는 것을 특징으로 하는 산화물 반도체 박막 트랜지스터의 제조 방법. - 제 11 항에 있어서,

상기 활성층과 상기 소스 전극 및 상기 드레인 전극 사이에 에치 스토퍼층을 형성하는 단계를 더 포함하는 것을 특징으로 하는 산화물 반도체 박막 트랜지스터의 제조 방법. - 삭제

- 삭제

- 제 11 항에 있어서, 상기 활성층의 상기 중앙부는 채널 영역을 포함하고, 상기 활성층의 상기 주변부는 상기 소스 영역 및 상기 드레인 영역을 포함하는 것을 특징으로 하는 산화물 반도체 박막 트랜지스터의 제조 방법.

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020100113326A KR101774256B1 (ko) | 2010-11-15 | 2010-11-15 | 산화물 반도체 박막 트랜지스터 및 그 제조 방법 |

| US13/075,117 US8450733B2 (en) | 2010-11-15 | 2011-03-29 | Oxide semiconductor thin film transistor, and method of manufacturing the same |

| JP2011078504A JP2012109516A (ja) | 2010-11-15 | 2011-03-31 | 酸化物半導体薄膜トランジスタ及びその製造方法 |

| TW100122812A TWI539607B (zh) | 2010-11-15 | 2011-06-29 | 氧化物半導體薄膜電晶體以及製造其之方法 |

| CN201110208118.XA CN102468341B (zh) | 2010-11-15 | 2011-07-19 | 氧化物半导体薄膜晶体管及其制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020100113326A KR101774256B1 (ko) | 2010-11-15 | 2010-11-15 | 산화물 반도체 박막 트랜지스터 및 그 제조 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20120051942A KR20120051942A (ko) | 2012-05-23 |

| KR101774256B1 true KR101774256B1 (ko) | 2017-09-05 |

Family

ID=46046980

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020100113326A KR101774256B1 (ko) | 2010-11-15 | 2010-11-15 | 산화물 반도체 박막 트랜지스터 및 그 제조 방법 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8450733B2 (ko) |

| JP (1) | JP2012109516A (ko) |

| KR (1) | KR101774256B1 (ko) |

| CN (1) | CN102468341B (ko) |

| TW (1) | TWI539607B (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11950487B2 (en) | 2018-09-21 | 2024-04-02 | Samsung Display Co., Ltd. | Display apparatus and method of manufacturing the same |

Families Citing this family (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8333913B2 (en) * | 2007-03-20 | 2012-12-18 | Idemitsu Kosan Co., Ltd. | Sputtering target, oxide semiconductor film and semiconductor device |

| KR101182232B1 (ko) | 2010-06-30 | 2012-09-12 | 삼성디스플레이 주식회사 | 유기전계발광 표시장치 |

| KR20120045178A (ko) * | 2010-10-29 | 2012-05-09 | 삼성전자주식회사 | 박막 트랜지스터 및 이의 제조 방법 |

| KR101450686B1 (ko) * | 2012-07-19 | 2014-10-14 | 제이에스알 가부시끼가이샤 | 반도체 소자, 감방사선성 수지 조성물, 경화막 및 표시 소자 |

| CN103855172B (zh) * | 2012-12-03 | 2016-11-23 | 群康科技(深圳)有限公司 | X光侦测装置 |

| KR101982727B1 (ko) * | 2012-12-11 | 2019-05-27 | 엘지디스플레이 주식회사 | 어레이 기판 |

| CN103187423B (zh) | 2013-02-04 | 2016-03-23 | 合肥京东方光电科技有限公司 | 一种氧化物薄膜晶体管阵列基板及其制作方法、显示面板 |

| KR101421288B1 (ko) * | 2013-02-28 | 2014-07-18 | 엘지디스플레이 주식회사 | 금속 산화물 반도체를 포함하는 박막 트랜지스터 기판 |

| KR20140125181A (ko) * | 2013-04-18 | 2014-10-28 | 삼성디스플레이 주식회사 | 평판표시장치용 백플레인 및 그의 제조방법 |

| CN103258859B (zh) * | 2013-05-23 | 2016-06-29 | 北京交通大学 | 一种氧化铟基薄膜晶体管及其制作方法 |

| KR20150010065A (ko) * | 2013-07-18 | 2015-01-28 | 삼성디스플레이 주식회사 | 산화물 반도체 소자의 제조 방법 및 산화물 반도체 소자를 포함하는 표시 장치의 제조 방법 |

| JP6264090B2 (ja) * | 2013-07-31 | 2018-01-24 | 株式会社リコー | 電界効果型トランジスタ、及び電界効果型トランジスタの製造方法 |

| JP2015038925A (ja) * | 2013-08-19 | 2015-02-26 | 株式会社東芝 | 半導体装置 |

| KR102112283B1 (ko) | 2013-08-20 | 2020-05-19 | 삼성디스플레이 주식회사 | 박막 트랜지스터를 포함하는 표시 기판 및 이의 제조 방법 |

| KR20150030034A (ko) | 2013-09-11 | 2015-03-19 | 삼성디스플레이 주식회사 | 표시장치 및 그 제조방법 |

| CN103618004B (zh) * | 2013-10-16 | 2016-05-18 | 京东方科技集团股份有限公司 | 一种薄膜晶体管及其制作方法、阵列基板和显示装置 |

| CN104752514B (zh) * | 2013-12-26 | 2018-05-25 | 昆山工研院新型平板显示技术中心有限公司 | 一种薄膜晶体管及其制备方法和应用 |

| KR102180511B1 (ko) * | 2014-02-10 | 2020-11-19 | 삼성디스플레이 주식회사 | 박막 트랜지스터 표시판 및 이의 제조 방법 |

| CN104064601B (zh) * | 2014-06-30 | 2017-12-26 | 上海天马微电子有限公司 | Tft、tft阵列基板及其制造方法、显示面板、显示装置 |

| CN104218095B (zh) | 2014-09-01 | 2016-05-25 | 京东方科技集团股份有限公司 | 一种薄膜晶体管及其制备方法、阵列基板和显示装置 |

| CN107146818B (zh) * | 2017-06-27 | 2020-02-18 | 京东方科技集团股份有限公司 | 一种薄膜晶体管、其制作方法、阵列基板及显示装置 |

| CN108051951B (zh) * | 2017-12-29 | 2022-12-13 | 西安智盛锐芯半导体科技有限公司 | Led光源、背光模组及液晶显示装置 |

| CN108258055A (zh) * | 2018-01-15 | 2018-07-06 | 北京交通大学 | 锌铟锡氧化物基薄膜晶体管及其制作方法 |

| CN108987468A (zh) * | 2018-06-26 | 2018-12-11 | 浙江大学 | 一种i-v族共掺杂非晶氧化物半导体薄膜与薄膜晶体管 |

| KR20210073178A (ko) * | 2019-12-10 | 2021-06-18 | 삼성전자주식회사 | 스크라이브 레인을 갖는 반도체 소자들 및 그 형성 방법 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090256147A1 (en) * | 2008-03-13 | 2009-10-15 | Min-Kyu Kim | Thin film transistor and method of manufacturing the same |

| US20100044699A1 (en) * | 2008-08-21 | 2010-02-25 | Samsung Mobile Display Co., Ltd. | Thin film transistor and method of fabricating the same |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0595002A (ja) * | 1991-10-02 | 1993-04-16 | Sharp Corp | 薄膜トランジスタ |

| JP3548237B2 (ja) * | 1994-08-29 | 2004-07-28 | シャープ株式会社 | 薄膜トランジスタ |

| US5641974A (en) * | 1995-06-06 | 1997-06-24 | Ois Optical Imaging Systems, Inc. | LCD with bus lines overlapped by pixel electrodes and photo-imageable insulating layer therebetween |

| JP3939140B2 (ja) * | 2001-12-03 | 2007-07-04 | 株式会社日立製作所 | 液晶表示装置 |

| JP2003273364A (ja) * | 2002-03-19 | 2003-09-26 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタ及び液晶表示装置 |

| KR100494455B1 (ko) * | 2003-06-11 | 2005-06-10 | 엘지.필립스 엘시디 주식회사 | 반사투과형 액정표시장치용 어레이기판 및 그 제조방법 |

| KR100659759B1 (ko) * | 2004-10-06 | 2006-12-19 | 삼성에스디아이 주식회사 | 바텀 게이트형 박막트랜지스터, 그를 구비하는평판표시장치 및 박막트랜지스터의 제조방법 |

| KR20070000025A (ko) * | 2005-06-24 | 2007-01-02 | 삼성전자주식회사 | 박막 트랜지스터 표시판 및 그 제조 방법 |

| US8530891B2 (en) * | 2007-04-05 | 2013-09-10 | Idemitsu Kosan Co., Ltd | Field-effect transistor, and process for producing field-effect transistor |

| KR101389923B1 (ko) * | 2008-04-21 | 2014-04-29 | 삼성디스플레이 주식회사 | 고개구율 어레이 기판, 액정 표시 장치 및 이들의 제조방법 |

| US8039842B2 (en) * | 2008-05-22 | 2011-10-18 | Semiconductor Energy Laboratory Co., Ltd. | Thin film transistor and display device including thin film transistor |

| JP5584960B2 (ja) * | 2008-07-03 | 2014-09-10 | ソニー株式会社 | 薄膜トランジスタおよび表示装置 |

| KR101671660B1 (ko) * | 2008-11-21 | 2016-11-01 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치, 표시 장치 및 전자 기기 |

-

2010

- 2010-11-15 KR KR1020100113326A patent/KR101774256B1/ko active IP Right Grant

-

2011

- 2011-03-29 US US13/075,117 patent/US8450733B2/en active Active

- 2011-03-31 JP JP2011078504A patent/JP2012109516A/ja active Pending

- 2011-06-29 TW TW100122812A patent/TWI539607B/zh active

- 2011-07-19 CN CN201110208118.XA patent/CN102468341B/zh active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090256147A1 (en) * | 2008-03-13 | 2009-10-15 | Min-Kyu Kim | Thin film transistor and method of manufacturing the same |

| US20100044699A1 (en) * | 2008-08-21 | 2010-02-25 | Samsung Mobile Display Co., Ltd. | Thin film transistor and method of fabricating the same |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11950487B2 (en) | 2018-09-21 | 2024-04-02 | Samsung Display Co., Ltd. | Display apparatus and method of manufacturing the same |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20120051942A (ko) | 2012-05-23 |

| JP2012109516A (ja) | 2012-06-07 |

| CN102468341B (zh) | 2016-10-05 |

| US8450733B2 (en) | 2013-05-28 |

| US20120119206A1 (en) | 2012-05-17 |

| TWI539607B (zh) | 2016-06-21 |

| CN102468341A (zh) | 2012-05-23 |

| TW201238053A (en) | 2012-09-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101774256B1 (ko) | 산화물 반도체 박막 트랜지스터 및 그 제조 방법 | |

| KR101272892B1 (ko) | 어레이 기판 | |

| US10553727B2 (en) | Thin film transistor, method of manufacturing the same, and organic light emitting display device including the same | |

| CN101043047B (zh) | 显示装置及其制造方法 | |

| US9240486B2 (en) | Thin-film transistor, method for manufacturing the same and display device including the same | |

| KR101073565B1 (ko) | 유기 발광 표시장치 및 이의 제조방법 | |

| US11177293B2 (en) | Array substrate and fabricating method thereof, and display device | |

| US9312353B2 (en) | Double gate type thin film transistor and organic light emitting diode display including the same | |

| JPWO2011043300A1 (ja) | 半導体装置およびその製造方法 | |

| US20060283833A1 (en) | Wiring for display device and thin film transistor array panel with the same, and manufacturing method thereof | |

| US20090206421A1 (en) | Organic light emitting display and manufacturing method thereof | |

| US11205729B2 (en) | Semiconductor device and method for manufacturing same | |

| KR20200058622A (ko) | 다결정 실리콘층의 제조 방법, 표시 장치 및 표시 장치의 제조 방법 | |

| US9508828B2 (en) | Array substrate and method of fabricating the same | |

| US11569324B2 (en) | Active matrix substrate and method for manufacturing same | |

| US20210399142A1 (en) | Thin Film Transistor Array Substrate and Display Device | |

| US8389454B2 (en) | Manufacturing and cleansing of thin film transistor panels | |

| US10409126B2 (en) | Thin film transistor unaffected by light and display apparatus having the same | |

| US20120104384A1 (en) | Thin-film transistor and method for manufacturing the same | |

| KR20170080047A (ko) | 산화물 박막 트랜지스터와 그를 포함하는 표시 장치 및 그 제조방법 | |

| WO2017131078A1 (ja) | アクティブマトリクス基板およびその製造方法 | |

| US10930720B2 (en) | Display device and manufacturing method thereof | |

| KR20110097121A (ko) | 어레이 기판 | |

| TWI836608B (zh) | 顯示裝置 | |

| US20200373431A1 (en) | Thin film transistor, method for manufacturing same, and display apparatus |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| N231 | Notification of change of applicant | ||

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant |