KR101323222B1 - 기판상에 형성되는 구조체의 열적 프로세싱을 위한 장치 및 방법 - Google Patents

기판상에 형성되는 구조체의 열적 프로세싱을 위한 장치 및 방법 Download PDFInfo

- Publication number

- KR101323222B1 KR101323222B1 KR1020107024018A KR20107024018A KR101323222B1 KR 101323222 B1 KR101323222 B1 KR 101323222B1 KR 1020107024018 A KR1020107024018 A KR 1020107024018A KR 20107024018 A KR20107024018 A KR 20107024018A KR 101323222 B1 KR101323222 B1 KR 101323222B1

- Authority

- KR

- South Korea

- Prior art keywords

- substrate

- region

- energy

- thermal processing

- regions

- Prior art date

Links

- 239000000758 substrate Substances 0.000 title claims abstract description 420

- 238000000034 method Methods 0.000 title claims abstract description 162

- 238000012545 processing Methods 0.000 title claims abstract description 78

- 230000005855 radiation Effects 0.000 claims description 45

- 239000004065 semiconductor Substances 0.000 claims description 44

- 230000005670 electromagnetic radiation Effects 0.000 claims description 18

- 238000012546 transfer Methods 0.000 claims description 13

- 238000001816 cooling Methods 0.000 claims description 7

- 238000010438 heat treatment Methods 0.000 claims description 7

- 239000012530 fluid Substances 0.000 claims description 4

- 230000008569 process Effects 0.000 abstract description 108

- 238000000137 annealing Methods 0.000 abstract description 67

- 239000012535 impurity Substances 0.000 abstract description 44

- 230000007547 defect Effects 0.000 abstract description 13

- 238000009792 diffusion process Methods 0.000 abstract description 11

- 230000015572 biosynthetic process Effects 0.000 abstract description 5

- 238000009827 uniform distribution Methods 0.000 abstract description 3

- 238000010309 melting process Methods 0.000 abstract 1

- 239000000463 material Substances 0.000 description 102

- 230000008018 melting Effects 0.000 description 65

- 238000002844 melting Methods 0.000 description 65

- 238000000576 coating method Methods 0.000 description 40

- 239000011248 coating agent Substances 0.000 description 38

- 230000008859 change Effects 0.000 description 36

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 31

- 229910052710 silicon Inorganic materials 0.000 description 31

- 239000010703 silicon Substances 0.000 description 31

- 238000000265 homogenisation Methods 0.000 description 19

- 230000003287 optical effect Effects 0.000 description 16

- 235000012431 wafers Nutrition 0.000 description 16

- 238000000151 deposition Methods 0.000 description 14

- 239000007943 implant Substances 0.000 description 14

- 230000006870 function Effects 0.000 description 12

- 239000013078 crystal Substances 0.000 description 10

- 238000005229 chemical vapour deposition Methods 0.000 description 8

- 238000004891 communication Methods 0.000 description 8

- 238000000231 atomic layer deposition Methods 0.000 description 7

- 239000013590 bulk material Substances 0.000 description 7

- 230000000694 effects Effects 0.000 description 7

- 239000000203 mixture Substances 0.000 description 7

- 230000002745 absorbent Effects 0.000 description 6

- 239000002250 absorbent Substances 0.000 description 6

- 238000010521 absorption reaction Methods 0.000 description 6

- 230000008021 deposition Effects 0.000 description 6

- 229910052732 germanium Inorganic materials 0.000 description 6

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 6

- 238000010884 ion-beam technique Methods 0.000 description 6

- 238000005224 laser annealing Methods 0.000 description 6

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 5

- 229910052799 carbon Inorganic materials 0.000 description 5

- 150000001875 compounds Chemical class 0.000 description 5

- 238000005137 deposition process Methods 0.000 description 5

- 238000010894 electron beam technology Methods 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 239000000155 melt Substances 0.000 description 5

- 230000015654 memory Effects 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 238000012986 modification Methods 0.000 description 5

- 230000002829 reductive effect Effects 0.000 description 5

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 5

- 229910010271 silicon carbide Inorganic materials 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 230000000670 limiting effect Effects 0.000 description 4

- 239000010936 titanium Substances 0.000 description 4

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 229910052785 arsenic Inorganic materials 0.000 description 3

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 3

- 239000000969 carrier Substances 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 230000010287 polarization Effects 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 238000002310 reflectometry Methods 0.000 description 3

- 238000007788 roughening Methods 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 229910052787 antimony Inorganic materials 0.000 description 2

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 230000008020 evaporation Effects 0.000 description 2

- 238000001704 evaporation Methods 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 238000003672 processing method Methods 0.000 description 2

- 230000035939 shock Effects 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 238000010301 surface-oxidation reaction Methods 0.000 description 2

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- AXQKVSDUCKWEKE-UHFFFAOYSA-N [C].[Ge].[Si] Chemical compound [C].[Ge].[Si] AXQKVSDUCKWEKE-UHFFFAOYSA-N 0.000 description 1

- 238000002835 absorbance Methods 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 230000004075 alteration Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000005280 amorphization Methods 0.000 description 1

- 229910003481 amorphous carbon Inorganic materials 0.000 description 1

- 239000002194 amorphous carbon material Substances 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 230000001174 ascending effect Effects 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 230000006399 behavior Effects 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- -1 but not limited to Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 239000012809 cooling fluid Substances 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 230000001066 destructive effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 239000005383 fluoride glass Substances 0.000 description 1

- 230000004907 flux Effects 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- HZXMRANICFIONG-UHFFFAOYSA-N gallium phosphide Chemical compound [Ga]#P HZXMRANICFIONG-UHFFFAOYSA-N 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 239000011261 inert gas Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000011068 loading method Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- QJGQUHMNIGDVPM-UHFFFAOYSA-N nitrogen group Chemical group [N] QJGQUHMNIGDVPM-UHFFFAOYSA-N 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 238000012805 post-processing Methods 0.000 description 1

- 238000004886 process control Methods 0.000 description 1

- 230000002787 reinforcement Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- ABTOQLMXBSRXSM-UHFFFAOYSA-N silicon tetrafluoride Chemical compound F[Si](F)(F)F ABTOQLMXBSRXSM-UHFFFAOYSA-N 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000007711 solidification Methods 0.000 description 1

- 230000008023 solidification Effects 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000010897 surface acoustic wave method Methods 0.000 description 1

- 238000010408 sweeping Methods 0.000 description 1

- 230000002123 temporal effect Effects 0.000 description 1

- 238000007669 thermal treatment Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 230000001052 transient effect Effects 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/324—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823418—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the source or drain structures, e.g. specific source or drain implants or silicided source or drain structures or raised source or drain structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823418—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the source or drain structures, e.g. specific source or drain implants or silicided source or drain structures or raised source or drain structures

- H01L21/823425—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the source or drain structures, e.g. specific source or drain implants or silicided source or drain structures or raised source or drain structures manufacturing common source or drain regions between a plurality of conductor-insulator-semiconductor structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823475—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type interconnection or wiring or contact manufacturing related aspects

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Recrystallisation Techniques (AREA)

- Crystals, And After-Treatments Of Crystals (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Abstract

본원발명은 기판의 희망 영역 상에서 어닐링 프로세스를 실행하기 위해 사용되는 하나 또는 그보다 많은 장치 및 다양한 방법들을 기술한다. 일 실시예에서, 이전 프로세싱 단계로부터 형성된 바람직하지 않은 손상을 제거하고, 기판의 다양한 영역에서 불순물을 보다 균일하게 분포하고, 및/또는 기판의 다양한 영역을 활성화시키기 위하여, 기판의 특정 희망 영역을 우선적으로 용융시키도록 기판의 표면에 일정량의 에너지가 전달된다. 우선 용융 프로세스는 용융된 영역에서 불순물의 보다 균일한 분포를 가능하게 하는데, 이는 기판의 용융된 영역에서 불순물 원자의 증가된 확산 속도 및 용해성에 기인한다. 따라서 용융된 영역의 형성은 1) 불순물 원자가 보다 균일하게 재분포하도록 하며, 2) 이전 프로세싱 단계에서 형성된 결함이 제거되도록 하며, 3) 과도하게 급격한(hyper-abrupt) 불순물 농도를 갖는 영역이 형성되게 한다.

Description

본원발명의 실시예들은 일반적으로 반도체 장치를 제조하기 위한 방법에 관련된다. 보다 구체적으로는, 본원발명은 기판을 열적으로 프로세싱하기 위한 방법에 관한 것이다.

집적회로(IC) 시장은 보다 큰 메모리 용량, 보다 빠른 스위칭 속도(switching speed), 및 보다 작은 피쳐(feature) 크기를 계속해서 요구하고 있다. 이러한 요구를 해결하기 위해 본 산업에서 취해진 주요 단계들 중 하나는 대형 노(furnaces) 내에서의 실리콘 웨이퍼 배치(batch) 프로세싱을 작은 챔버 내에서의 단일 웨이퍼 프로세싱으로 변경한 것이다.

이러한 단일 웨이퍼 프로세싱 동안, 웨이퍼는 통상적으로 높은 온도로 가열되어, 웨이퍼 내에 형성된 복수의 IC 장치에서 다양한 화학적 및 물리적 반응이 이루어질 수 있다. 특히 흥미로운 것은, IC 장치의 바람직한 전기적 성능은 임플란트된 영역이 어닐링(annealing)될 것을 요구한다는 점이다. 어닐링은 이전에 비정질(amorphous)로 제조된 웨이퍼의 영역을 보다 결정성인 구조로 재형성하고, 기판 또는 웨이퍼의 결정성 격자 내에 불순물의 원자를 주입함으로써 불순물을 활성화시킨다. 어닐링과 같은 열적 프로세스는 짧은 시간 동안 비교적 많은 양의 열 에너지를 웨이퍼로 제공할 것을 요구하며, 이후 열적 프로세스를 종료하기 위해 신속한 웨이퍼 냉각을 요구한다. 현재 사용되는 열적 프로세스의 예로는, 신속 열적 프로세싱(Rapid Thermal Processing; RTP) 및 임펄스 (스파이크) 어닐링(impulse (spike) annealing)을 포함한다. 이러한 프로세스가 광범위하게 이용되는 반면, 현재의 기술은 이상적이지 않다. 이는 웨이퍼의 온도를 너무 느리게 변화시키고(ramp) 웨이퍼를 상승된 온도에 너무 오랫동안 노출시키는 경향이 있다. 이러한 문제점은 웨이퍼 크기의 증가, 스위칭 속도의 증가, 및/또는 피쳐 크기의 감소와 더불어 더욱 심각해진다.

일반적으로, 이러한 열적 프로세스는 예정된 열적 처리방식(thermal recipe)에 따라 제어된 조건 하에서 기판을 가열한다. 이러한 열적 처리방식은 기본적으로 반도체 기판이 온도 변화의 속도, 즉 온도 상승 및 온도 강하 속도로 가열되어야 하는 온도 및 열적 프로세싱 시스템이 특정 온도에 머무르는 시간으로 구성된다. 예를 들어, 열적 처리방식은 기판이 각각의 현저한 온도에서 60초까지의 또는 그 이상의 범위에 이르는 프로세싱 시간 동안, 실내 온도로부터 1200 ℃ 또는 그보다 높은 현저한 온도로 가열될 것을 요구할 수 있다.

더욱이, 반도체 기판의 상이한 영역 사이에서 물질의 최소 인터-디퓨젼(inter-diffusion)과 같은 일정한 목적을 만족시키기 위하여, 각각의 반도체 기판이 높은 온도에 놓이게 되는 시간의 양은 제한되어야만 한다. 이를 달성하기 위하여, 위 및 아래 모두로의 온도 변화 속도는 바람직하게 높다. 즉, 가능한 한 짧은 시간 내에 기판의 온도를 낮은 온도로부터 높은 온도로, 또는 그 반대로 조절할 수 있는 것이 바람직하다.

빠른 온도 변화 속도에 대한 요구는 신속 열적 프로세싱(RTP)의 개발을 야기하였는데, 여기서 통상적인 온도 상승 속도는 종래의 노에 대한 5-15℃/m(분) 와 비교하여, 200 내지 400 ℃/s(초) 의 범위에 있다. 통상적인 온도 하강 속도는 80-150 ℃/s 범위이다. RTP 의 단점은 이러한 방식이 실리콘 웨이퍼의 상부 수 마이크론(few microns)에만 IC 장치가 존재함에도 불구하고 전체 웨이퍼를 가열한다는 점이다. 이는 하나가 얼마나 빠르게 웨이퍼를 가열하고 냉각할 수 있는가를 제한한다. 더욱이, 일단 이러한 전체 웨이퍼가 상승된 온도에 있게 되면, 열은 주위 공간이나 구조체 내로 방산될 수 있을 뿐이다. 결과적으로, 오늘날의 최신 기술 수준의 RTP 시스템은 가까스로 400 ℃/s 의 상승 속도와 150 ℃/s 의 하강 속도를 달성하고 있을 뿐이다.

종래의 RTP 유형의 프로세스에서 발생된 문제점 중 일부를 해결하기 위하여 다양한 스캐닝 레이저 어닐링 기술(scanning laser anneal techniques)이 기판의 표면(들)을 어닐링하는데 사용되어 왔다. 일반적으로, 이러한 기술은 작은 영역에 전달되는 에너지에 대하여 기판이 병진이동하거나 스캐닝되는 동안 기판의 표면상의 작은 영역으로 일정한 에너지 플럭스를 전달한다. 기판 표면을 가로지르는 스캐닝된 영역의 중첩 최소화의 복잡성 및 엄격한 균일성 요구조건으로 인하여, 이러한 유형의 프로세스는 기판의 표면상에 형성되는 접촉 수준 장치의 열적 프로세싱에 효과적이지 않다.

이상과 관련하여, 높은 상승 및 하강 속도로 반도체 기판을 어닐링하기 위한 방법이 필요하다. 이는 성능 향상을 초래하는 보다 소형인 장치의 제조에 대한 보다 좋은 제어를 제공할 것이다.

본원발명은 일반적으로 기판의 열적 프로세싱 방법으로서, 하나 또는 그보다 많은 영역 내에 제2 물질을 배치함으로써 제1 물질로부터 형성된 기판 내의 상기 하나 또는 그보다 많은 영역을 변화시키는 단계로서, 제2 물질로 기판 내의 하나 또는 그보다 많은 영역을 변화시키는 것은 상기 하나 또는 그보다 많은 영역 내에 포함된 제1 물질의 용융점을 낮추도록 구성되는, 하나 또는 그보다 많은 영역을 변화시키는 단계, 상기 기판의 하나 또는 그보다 많은 영역 내에 제3 물질을 배치하는 단계, 및 상기 하나 또는 그보다 많은 영역과 열적으로 연통하는 기판의 표면에 일정량의 전자기 에너지를 전달하는 단계로서, 상기 전자기 에너지의 양이 상기 하나 또는 그보다 많은 영역 내의 제1 물질이 용융되게 하도록 구성되는, 전자기 에너지 전달 단계를 포함하는, 기판의 열적 프로세싱 방법을 제공한다.

본원발명의 실시예는 추가로, 기판의 열적 프로세싱 방법으로서, 각각의 제1 영역 내에 포함된 물질의 용융점이 기판의 제2 영역 내에 포함된 물질보다 더 낮은 온도에서 용융되도록 변화된 하나 또는 그보다 많은 제1 영역을 갖는 기판을 제공하는 단계로서, 상기 제2 영역 및 각각의 제1 영역이 대체로 기판의 표면에 인접하는, 기판 제공 단계, 기판의 표면 위로 코팅을 증착하는 단계로서, 상기 코팅이 상기 기판의 표면과 다른 흡수 및 반사 계수를 갖는, 코팅 증착 단계, 상기 각각의 제1 영역 또는 제2 영역에 대체로 인접하는 기판의 표면으로부터 상기 코팅의 일부를 제거하는 단계, 및 하나 또는 그보다 많은 상기 제1 영역 및 제2 영역을 포함하는 기판의 표면상의 면적에 일정량의 전자기 에너지를 전달하는 단계로서, 상기 일정량의 전자기 에너지가 상기 하나 또는 그보다 많은 제1 영역 내의 물질을 우선적으로 용융시키는, 전자기 에너지 제공 단계를 포함하는 기판의 열적 프로세싱 방법을 제공한다.

본원발명의 실시예는 추가로, 반도체 기판의 열적 프로세싱 방법으로서, 기판 물질로부터 형성된 기판을 제공하는 단계, 상기 기판의 표면상에 제1 물질로 제조된 매설 영역을 형성하는 단계로서, 상기 제1 물질이 제1 열 전도성을 갖는, 매설 영역 형성 단계, 상기 매설 영역 위에 제2 물질로 제조된 제2 층을 증착하는 단계로서, 상기 제2 물질이 제2 열 전도성을 갖는, 증착 단계, 상기 기판의 표면상에 반도체 장치를 형성하는 단계로서, 형성된 반도체 장치의 일부가 상기 제2 층의 일부를 포함하는, 반도체 장치 형성 단계, 및 상기 제2 층과 열적으로 연통된 기판의 표면에 일정량의 전자기 에너지를 전달하는 단계로서, 상기 전자기 에너지의 양이 상기 매설 영역과 열적으로 연통하는 제2 물질의 일부가 그 용융점에 도달할 수 있도록 구성되는, 전자기 에너지 전달 단계를 포함하는, 반도체 기판의 열적 프로세싱 방법을 제공한다.

본원발명의 실시예는 추가로, 기판의 열적 프로세싱 방법으로서, 기판 지지부 상에 기판을 위치시키는 단계로서, 상기 기판이 제1 영역 및 제2 영역을 포함하는 기판의 표면상에 형성되는 복수의 피쳐를 갖는, 기판 위치 단계, 상기 제1 영역 및 제2 영역 위에 코팅을 증착하는 단계로서, 상기 코팅을 형성하는 물질이 희망 열 용량을 갖는, 코팅 증착 단계, 상기 제1 영역 위의 코팅이 희망 두께를 가지도록 상기 코팅의 일부를 제거하는 단계로서, 상기 코팅의 일부를 제거한 이후에, 상기 기판 표면을 가로지르는 평균 열 용량이 대체로 균일한, 코팅 제거 단계, 및 상기 제1 영역 및 제2 영역을 포함하는 면적에 일정량의 전자기 에너지를 전달하는 단계로서, 상기 전자기 에너지의 양이 상기 제1 영역 내의 물질을 용융시키는, 전자기 에너지 전달 단계를 포함하는, 기판의 열적 프로세싱 방법을 제공한다.

본원발명의 실시예는 추가로, 기판의 열적 프로세싱 방법으로서, 기판 표면상에 형성되는 제1 피쳐 및 제2 피쳐를 갖는 기판을 제공하는 단계로서, 상기 제2 피쳐가 제1 영역 및 제2 영역을 포함하는, 기판 제공 단계, 상기 기판을 기판 지지부 상에 위치시키는 단계, 상기 제1 및 제2 피쳐 위에 코팅을 증착하는 단계, 상기 제1 피쳐의 표면이 노출되고 상기 코팅이 상기 제2 영역 위에 배치되도록 상기 코팅의 일부를 제거하는 단계, 및 상기 제1 피쳐 및 제2 피쳐를 포함하는 면적에 일정량의 전자기 에너지를 전달하는 단계로서, 상기 전자기 에너지의 양이 상기 제2 피쳐의 제1 영역 내의 물질을 용융시키는, 전자기 에너지 전달 단계를 포함하는 기판의 열적 프로세싱 방법을 제공한다.

본원발명의 실시예는 추가로, 기판의 열적 프로세싱 방법으로서, 기판의 후방 표면으로 하나 또는 그보다 많은 희망 파장에서 제1 양의 전자기 에너지를 전달하여 상기 기판의 전방 표면에 대체로 인접하는 하나 또는 그보다 많은 영역에 있는 물질을 용융시키는 단계를 포함하며, 상기 후방 표면 및 전방 표면이 기판의 반대측 상에 위치하며 상기 기판의 전방 표면이 그 위에 형성되는 하나 또는 그보다 많은 반도체 장치를 포함하는 기판의 열적 프로세싱 방법을 제공한다.

본원발명의 실시예는 추가로, 기판의 열적 프로세싱 방법으로서, 제1 양의 전자기 에너지를 기판 표면상의 제1 영역으로 전달하는 단계로서, 상기 제1 양의 전자기 에너지가 상기 제1 영역 내의 기판 물질을 용융시키고 결정성 기판 물질이 비정질이 되도록 하는, 제1 양의 전자기 에너지 전달 단계, 상기 비정질 제1 영역 내에 제2 물질을 임플란트하는 단계, 및 상기 제1 영역으로 제2 양의 전자기 에너지를 전달하는 단계로서, 상기 제2 양의 전자기 에너지가 상기 제1 영역 내의 물질을 용융시키는, 제2 양의 에너지 전달 단계를 포함하는 기판의 열적 프로세싱 방법을 제공한다.

본원발명의 실시예는 추가로, 반도체 기판의 열적 프로세싱 장치로서, 기판 지지 표면을 갖는 기판 지지부, 상기 기판 지지부 상에 배치되는 기판을 가열하도록 구성되는 가열 부재, 및 상기 기판 지지 표면상에 배치되는 기판의 표면상의 영역으로 일정량의 복사선을 전달하도록 구성되는 강한 광원을 포함하는 반도체 기판의 열적 프로세싱 장치를 제공한다.

본원발명의 실시예는 추가로, 반도체 기판의 열적 프로세싱 장치로서, 기판 지지 표면상에 배치되는 기판의 표면상의 영역으로 제1 양의 에너지를 전달하도록 구성되는 제1 강한 광원, 기판 지지 표면상에 배치되는 기판의 표면상의 영역으로 제2 양의 에너지를 전달하도록 구성되는 제2 강한 광원, 및 상기 기판 표면상의 영역으로 전달되는 제1 양의 에너지를 모니터하고 상기 영역 내에 희망 온도를 얻도록 상기 제2 양의 에너지의 크기 및 상기 제1 양과 제2 양의 에너지 전달 사이의 시간을 제어하도록 구성되는 제어기를 포함하는 반도체 기판의 열적 프로세싱 장치를 제공한다.

본원발명의 실시예는 추가로, 반도체 기판의 열적 프로세싱 장치로서, 그 내부에 형성되는 개구 및 기판 지지 표면을 갖는 기판 지지부, 및 상기 기판의 전방 표면 반대측에 위치하는 기판의 후방 표면 및 상기 기판 지지부 내에 형성되는 상기 개구를 통해 상기 기판의 제1 면적으로 일정량의 복사선을 전달하도록 구성되는 제1 광원으로서, 상기 기판의 전방 표면이 그 위에 형성되는 하나 또는 그보다 많은 반도체 장치를 포함하고 상기 일정량의 복사선이 상기 제1 면적 내에 포함되는 영역을 용융시키도록 구성되는 제1 광원을 포함하는 반도체 기판의 열적 프로세싱 장치를 제공한다.

본원발명의 실시예는 추가로, 기판의 열적 프로세싱 방법으로서, 기판 지지부 상에 기판을 위치시키는 단계, 및 상기 기판의 제1 영역과 열적으로 연통된 기판 표면상의 제1 면적으로 복수의 전자기 에너지 펄스를 전달하는 단계로서, 상기 기판 표면으로 전자기 에너지의 제1 펄스를 전달하는 단계, 상기 기판 표면으로 전자기 에너지의 제2 펄스를 전달하는 단계, 및 상기 제1 영역 내에 포함되는 물질이 용융되도록 상기 제1 펄스의 개시 시점과 상기 제2 펄스의 개시 시점 사이의 시간을 조정하는 단계를 포함하는, 복수의 전자기 에너지 펄스 전달 단계를 포함하는 기판의 열적 프로세싱 방법을 제공한다.

본원발명의 실시예는 추가로, 기판의 열적 프로세싱 방법으로서, 기판 지지부 상에 기판을 위치시키는 단계, 및 기판의 제1 영역 및 제2 영역과 열적으로 연통된 기판 표면에 전자기 에너지를 전달하는 단계로서, 상기 제2 영역보다 상기 제1 영역에 포함된 물질을 우선적으로 용융시키기 위하여 제1 파장에서 제1 양의 전자기 에너지를 전달하는 단계, 및 상기 제2 영역보다 상기 제1 영역에 포함된 물질을 우선적으로 용융시키기 위하여 제2 파장에서 제2 양의 전자기 에너지를 전달하는 단계를 포함하며, 상기 제1 양의 에너지 전달 단계 및 제2 양의 에너지 전달 단계가 시간상으로 중첩되는, 전자기 에너지 전달 단계를 포함하는 기판의 열적 프로세싱 방법을 제공한다.

본원발명의 실시예는 추가로, 기판의 열적 프로세싱 방법으로서, 기판 지지부 상에 기판을 위치시키는 단계, 및 기판의 제1 영역 및 제2 영역과 열적으로 연통된 기판 표면에 전자기 에너지를 전달하는 단계로서, 상기 제1 영역에 포함된 물질을 우선적으로 용융시키기 위하여 시간에 따라 전자기 에너지 펄스의 형태를 조정하는 단계를 포함하는 전자기 에너지 전달 단계를 포함하는 기판의 열적 프로세싱 방법을 제공한다.

본원 발명의 상기 열거된 특징들이 상세히 이해될 수 있는 방식으로 앞서 간략히 요약된 본원 발명의 보다 구체적인 설명이 실시예들을 참조로 하여 이루어질 수 있는데, 이러한 실시예들의 일부는 첨부된 도면들에 예시되어 있다. 그러나, 첨부된 도면들은 본원 발명의 단지 전형적인 실시예들을 도시하는 것이므로 본원 발명의 범위를 제한하는 것으로 간주되지 않아야 한다는 것이 주목되어야 하는데, 이는 본원 발명이 다른 균등하게 유효한 실시예들을 허용할 수 있기 때문이다.

도 1은 본 명세서의 실시예 내에 기술된 기판의 한정된 영역 상에 일정량의 에너지를 투사하도록 조정된 에너지원의 등척도를 도시한다.

도 2a-2f는 본 명세서의 실시예 내에 기술된 기판 표면 상의 영역의 개략적인 측면도를 도시한다.

도 3a는 본 명세서의 실시예 내에 있는 도 2a에 도시된 기판의 영역으로의 깊이에 대한 농도의 그래프를 도시한다.

도 3b는 본 명세서의 실시예 내에 있는 도 2b에 도시된 기판의 영역으로의 깊이에 대한 농도의 그래프를 도시한다.

도 3c는 본 명세서의 실시예 내에 있는 도 2c에 도시된 기판의 영역으로의 깊이에 대한 농도의 그래프를 도시한다.

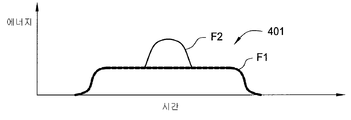

도 4a-4g는 본 명세서의 실시예 내에 기술된 전자기 에너지 펄스의 개략적인 다이어그램을 도시한다.

도 5a-5c는 본 명세서의 실시예 내에 기술된 기판 표면상의 영역의 개략적인 측면도를 도시한다.

도 6a는 본 명세서에 포함된 실시예 내에 기술된 기판 표면상에 하나 또는 그보다 많은 희망 층을 형성하는 방법을 도시한다.

도 6b-6d는 본 명세서에 기술된 실시예 내의 도 6a에 도시된 방법과 관련하여 기술된 기판 영역의 개략적 측면도를 도시한다.

도 6e는 본 명세서에 포함된 실시예 내에 기술된 기판 표면상에 하나 또는 그보다 많은 희망 층을 형성하는 방법을 도시한다.

도 6f-6g는 본 명세서에 기술된 실시예 내의 도 6e에 도시된 방법과 관련하여 기술된 기판 영역의 개략적 측면도를 도시한다.

도 7은 본 명세서의 실시예 내에 기술된 기판 표면상의 영역의 개략적 측면도를 도시한다.

도 8은 본 명세서의 실시예 내에 기술된 기판 표면상의 영역의 개략적 측면도를 도시한다.

도 9는 본 명세서의 실시예 내에 기술된 기판의 한정된 영역 상에 일정량의 에너지를 투사하도록 구성된 에너지원을 갖는 시스템의 개략적인 측면도를 도시한다.

도 1은 본 명세서의 실시예 내에 기술된 기판의 한정된 영역 상에 일정량의 에너지를 투사하도록 조정된 에너지원의 등척도를 도시한다.

도 2a-2f는 본 명세서의 실시예 내에 기술된 기판 표면 상의 영역의 개략적인 측면도를 도시한다.

도 3a는 본 명세서의 실시예 내에 있는 도 2a에 도시된 기판의 영역으로의 깊이에 대한 농도의 그래프를 도시한다.

도 3b는 본 명세서의 실시예 내에 있는 도 2b에 도시된 기판의 영역으로의 깊이에 대한 농도의 그래프를 도시한다.

도 3c는 본 명세서의 실시예 내에 있는 도 2c에 도시된 기판의 영역으로의 깊이에 대한 농도의 그래프를 도시한다.

도 4a-4g는 본 명세서의 실시예 내에 기술된 전자기 에너지 펄스의 개략적인 다이어그램을 도시한다.

도 5a-5c는 본 명세서의 실시예 내에 기술된 기판 표면상의 영역의 개략적인 측면도를 도시한다.

도 6a는 본 명세서에 포함된 실시예 내에 기술된 기판 표면상에 하나 또는 그보다 많은 희망 층을 형성하는 방법을 도시한다.

도 6b-6d는 본 명세서에 기술된 실시예 내의 도 6a에 도시된 방법과 관련하여 기술된 기판 영역의 개략적 측면도를 도시한다.

도 6e는 본 명세서에 포함된 실시예 내에 기술된 기판 표면상에 하나 또는 그보다 많은 희망 층을 형성하는 방법을 도시한다.

도 6f-6g는 본 명세서에 기술된 실시예 내의 도 6e에 도시된 방법과 관련하여 기술된 기판 영역의 개략적 측면도를 도시한다.

도 7은 본 명세서의 실시예 내에 기술된 기판 표면상의 영역의 개략적 측면도를 도시한다.

도 8은 본 명세서의 실시예 내에 기술된 기판 표면상의 영역의 개략적 측면도를 도시한다.

도 9는 본 명세서의 실시예 내에 기술된 기판의 한정된 영역 상에 일정량의 에너지를 투사하도록 구성된 에너지원을 갖는 시스템의 개략적인 측면도를 도시한다.

본원발명은 일반적으로 기판상에 반도체 장치를 제조하기 위한 프로세스에 사용되는 임플란트 어닐링(implant anneal) 단계의 성능을 향상시킨다. 일반적으로 본원발명의 방법은 선택된 영역을 재용융(re-melt)시켜 응고시키기에 충분한 에너지를 상기 선택된 영역에 전달하여 기판의 상기 선택된 영역을 우선적으로 어닐링하는데 사용될 수 있다.

일반적으로 용어 "기판"은, 본 명세서에서 사용될 때, 다소의 천연적인 전기 전도성을 갖는 임의의 물질이나 전기를 전도할 수 있는 능력을 제공하도록 변경될 수 있는 물질로부터 형성될 수 있다. 통상적인 기판 물질은, 반도체에 제한되는 것은 아니지만, 실리콘(Si) 및 게르마늄(Ge), 및 반도체 특성을 나타내는 다른 화합물을 포함한다. 이러한 반도체 화합물은 일반적으로 Ⅲ-Ⅴ족 화합물 및 Ⅱ-VI족 화합물을 포함한다. 대표적인 Ⅲ-Ⅴ족 반도체 화합물로는 비화갈륨(GaAs), 인화갈륨(GaP), 및 질화 갈륨(GaN)이 포함되나, 이에 한정되는 것은 아니다. 일반적으로, 용어 "반도체 기판"은 상부에 배치된 증착된 층을 갖는 기판과 함께 벌크 반도체 기판을 포함한다. 이를 위하여, 본원발명의 방법에 의하여 프로세싱된 일부 반도체 기판에서 증착된 층은 호모에피택시얼(homoepitaxial)(예를 들어 실리콘 상의 실리콘) 또는 헤테로에피택시얼(heteroepitaxial)(예를 들어 실리콘 상의 비화갈륨) 성장 중의 하나에 의해서 형성된다. 예를 들어, 본원발명의 방법은 헤테로에피택시얼 방법에 의해 형성된 비화갈륨 및 질화갈륨 기판에 사용될 수 있다. 유사하게, 본원발명의 방법은 절연 기판상에 형성된 비교적 얇은 결정성 실리콘 층(예를 들어, 실리콘-온-인슐레이터(silicon-on-insulator)[SOI] 기판) 상에, 박막 트랜지스터(TFTs)와 같은 집적 장치를 형성하기 위해 적용될 수도 있다.

본원발명의 일 실시예에서, 일정량의 에너지가 기판 표면으로 전달되어 이전의 프로세싱 단계로부터 생성된 바람직하지 않은 손상(예를 들어 임플란트 프로세스로부터의 결정 손상)을 제거하도록 기판의 특정 희망 영역을 우선적으로 용융시키고, 기판의 다양한 영역에 불순물(dopants)을 보다 균일하게 분포시키며, 및/또는 기판의 다양한 영역을 활성화시킨다. 우선적 용융 프로세스(preferential melt processes)는, 기판의 용융된 영역에서 불순물 원자의 향상된 확산속도 및 가용성(可溶性, solubility)으로 인하여, 용융된 영역에서 불순물의 보다 균일한 분포를 가능하게 할 것이다. 따라서 용융 영역의 형성은: 1)불순물 원자가 보다 균일하게 재분포되도록 하며, 2)이전 프로세싱 단계에서 형성된 결함이 제거되도록 하며, 3)과도하게 급격한(hyper-abrupt) 불순물 농도를 갖는 영역이 형성되게 한다. 과도하게 급격한 불순물 농도를 갖는 영역에서의 불순물 농도의 구배(gradient)는, 장치 내에서 하나의 영역으로부터 다른 영역으로 농도가 급격하게 변화하므로 매우 크다(예를 들어 2 nm/10단위 농도(nm/decade of concentration) 미만).

본원발명에 기재된 기술을 사용함으로써 종래의 장치보다 더 높은 불순물 농도를 함유하는 접합부(junction)가 형성될 수 있는데, 이는, 도핑(doping) 수준의 증가에 의한 기판 물질 내에서의 결함 농도의 증가와 같은, 형성된 접합부의 공통적인 부정적 속성이 본원발명에 기재된 프로세싱 기술을 사용함으로써 허용 가능한 수준으로 용이하게 감소될 수 있기 때문이다. 따라서 보다 높은 불순물 수준 및 불순물 농도의 급격한 변화는 기판의 다양한 영역의 전도성을 증가시킬 수 있으며, 이로써, 기판의 다양한 영역으로 불순물의 확산을 최소화하면서도, 장치 수율(device yield)에 부정적인 영향을 미치지 않고 장치 속도(device speed)를 향상시킨다. 결과적인 보다 높은 불순물 농도는 형성된 장치의 전도성을 증가시키며 그 성능을 향상시킨다. 통상적으로, 보다 높은 불순물 농도는 통상적인 RTP 프로세스 동안 기판의 벌크 물질로 즉각적으로 확산시킬 수 없기 때문에, RTP 프로세스를 사용하여 형성된 장치는 약 1×1015 원자/cm2 보다 더 큰 불순물 농도를 사용하지 않을 것이고, 대신 불순물 원자의 덩어리(clusters) 및 기타 유형의 결함을 초래할 것이다. 본 명세서에 기술된 하나 또는 그보다 많은 어닐링 프로세스의 실시예를 사용하면, 더욱 많은 불순물(5-10배까지 보다 많은 불순물, 즉 1×1016 원자/cm2)이 희망 기판 표면 내로 성공적으로 주입될 수 있는데, 이는 액화된 영역이 응고되기 전에 불순물이 액체를 통하여 보다 균일하게 분포될 수 있도록 기판의 영역이 우선적으로 용융되기 때문이다.

도 1은 본원발명의 일 실시예의 등척도를 도시하는데, 여기서는 어닐링 영역(12) 내의 특정 희망 영역을 우선적으로 용융시키기 위하여 기판(10)의, 어닐링 영역(12) 또는 한정된 영역 상에 일정량의 에너지를 투사하도록 에너지원(20)이 구성된다. 일 예시에서는, 도 1에 도시된 바와 같이, 어닐링 영역(12)과 같은 기판의 하나 또는 그보다 많은 한정된 영역들만이 임의의 주어진 시간에서 에너지원(20)으로부터의 복사선(radiation)에 노출된다. 본원발명의 일 태양에서는, 기판(10)의 복수의 영역들이 에너지원(20)으로부터 전달되는 희망 양의 에너지에 순차적으로 노출되어 기판의 희망 영역을 우선적으로 용융시킨다. 일반적으로, 전자기 복사선 공급원(radiation source)의 출력에 대해 기판을 병진이동시킴(translating)으로써(예를 들어, 통상적인 X/Y 스테이지, 정밀 스테이지) 및/또는 기판에 대해 복사선 공급원의 출력을 상대적으로 병진이동시킴으로써, 기판의 표면상의 영역이 순차적으로 노출될 수 있다. 통상적으로, 별도의 정밀 스테이지(precision stage)(도시되지 않음)의 일부일 수 있는, 하나 또는 그보다 많은 종래의 전기 엑츄에이터(17)(예를 들어, 선형 모터, 리드 스크루(lead screw), 및 서보 모터)가 기판(10)의 위치 및 이동을 제어하는데 사용된다. 기판(10)을 지지하고 위치 설정하는데 사용될 수 있는 종래의 정밀 스테이지는, 및 열 교환 장치(15)는, 캘리포니아 로너트 파크(Rohnert park)의 Parker Hannifin Corporation 으로부터 구입할 수 있다.

도 1은 본원발명의 일 실시예의 등척도를 도시하는데, 여기서는 어닐링 영역(12) 내의 특정 희망 영역을 우선적으로 용융시키기 위하여 기판(10)의, 어닐링 영역(12) 또는 한정된 영역 상에 일정량의 에너지를 투사하도록 에너지원(20)이 구성된다. 일 예시에서는, 도 1에 도시된 바와 같이, 어닐링 영역(12)과 같은 기판의 하나 또는 그보다 많은 한정된 영역들만이 임의의 주어진 시간에서 에너지원(20)으로부터의 복사선(radiation)에 노출된다. 본원발명의 일 태양에서는, 기판(10)의 복수의 영역들이 에너지원(20)으로부터 전달되는 희망 양의 에너지에 순차적으로 노출되어 기판의 희망 영역을 우선적으로 용융시킨다. 일반적으로, 전자기 복사선 공급원(radiation source)의 출력에 대해 기판을 병진이동시킴(translating)으로써(예를 들어, 통상적인 X/Y 스테이지, 정밀 스테이지) 및/또는 기판에 대해 복사선 공급원의 출력을 상대적으로 병진이동시킴으로써, 기판의 표면상의 영역이 순차적으로 노출될 수 있다. 통상적으로, 별도의 정밀 스테이지(precision stage)(도시되지 않음)의 일부일 수 있는, 하나 또는 그보다 많은 종래의 전기 엑츄에이터(17)(예를 들어, 선형 모터, 리드 스크루(lead screw), 및 서보 모터)가 기판(10)의 위치 및 이동을 제어하는데 사용된다. 기판(10)을 지지하고 위치 설정하는데 사용될 수 있는 종래의 정밀 스테이지는, 및 열 교환 장치(15)는, 캘리포니아 로너트 파크(Rohnert park)의 Parker Hannifin Corporation 으로부터 구입할 수 있다.

삭제

일 태양에서, 어닐링 영역(12)은 기판의 표면상에 형성되는 반도체 장치(예를 들어, 메모리 칩) 또는 다이(die)(13)(예를 들어 도 1에는 40개의 "다이"가 도시되어 있다)의 크기에 부합하도록 크기가 정해진다. 일 태양에서는, 어닐링 영역(12)의 경계가 각각의 다이(13)의 경계를 형성하는 "커프(kurf)" 또는 "스크라이브(scribe)" 라인(10A) 내에 알맞도록 정렬되고 크기가 정해진다. 일 실시예에서는, 어닐링 프로세스를 실행하기에 앞서, 통상적으로 기판의 표면상에 있는 정렬 표식(marks) 및 다른 종래의 기술을 이용하여 기판이 에너지원(20)의 출력과 정렬되어, 어닐링 영역(12)이 다이(13)에 적절하게 정렬될 수 있다. 어닐링 영역(12)이 다이(13) 사이의, 스크라이브 또는 커프 라인과 같은, 자연적으로 발생하는 사용되지 않은 공간/경계에서만 중첩되도록 어닐링 영역(12)을 순차적으로 배치함으로써, 장치가 기판상에 형성되는 영역에서 에너지를 중첩시킬 필요가 감소되며, 이로써 중첩된 어닐링 영역들 사이의 프로세스 결과에서의 변동이 감소된다. 이러한 기술은, 기판의 표면을 가로질러 레이저 에너지를 일소(sweep)하는 종래의 프로세스에 비하여 장점을 갖는데, 이는 기판의 희망 영역을 가로질러 균일한 어닐링을 보장하기 위하여 인접하여 스캔된 영역들 사이의 중첩을 빈틈없이 제어해야 할 필요성이 다이(13) 사이의 사용되지 않은 공간에 대한 중첩의 제한으로 인하여 문제가 되지 않기 때문이다. 또한 중첩(overlap)을 다이(13) 사이의 사용되지 않은 공간/경계에 제한함으로써 기판의 모든 영역을 가로지르는 인접한 중첩 영역을 활용하는 종래의 스캐닝 어닐링 유형의 방법(scanning anneal type methods)에 비하여 프로세스 균일성 결과를 향상시킨다. 따라서, 에너지원(20)으로부터 기판의 프로세스 임계 영역으로 전달되는 에너지에 대한 노출의 변화되는 양에 기인하여, 프로세스 변동(process variation)의 양이 최소화되는데, 이는 순차적으로 배치된 어닐링 영역(12)들 사이에서 전달된 에너지의 어떠한 중첩도 최소화될 수 있기 때문이다. 일 예시에서, 순차적으로 배치된 어닐링 영역(12) 각각은 약 22mm × 약 33mm 의 크기(예를 들어 726 mm2 의 면적)인 직사각형 영역이다. 일 태양에서, 기판 표면상에 형성되는, 순차적으로 배치된 어닐링 영역(12)의 각각의 영역은 약 4 mm2(예를 들어 2mm × 2mm) 내지 약 1000 mm2(예를 들어 25mm × 40mm)이다.

에너지원(20)은 일반적으로 기판 표면의 특정 희망 영역을 우선적으로 용융시키기 위해 전자기 에너지를 전달하도록 구성된다. 전자기 에너지의 통상적인 공급원은, 이에 제한되는 것은 아니지만, 광학 복사선 공급원(optical radiation source)(예를 들어, 레이저), 전자 빔 공급원, 이온 빔 공급원, 및/또는 마이크로파 에너지 공급원을 포함한다. 일 태양에서, 기판(10)은 희망 시간 주기 동안 하나 또는 그보다 많은 적절한 파장에서 복사선을 방출하는 레이저로부터의 에너지 펄스에 노출된다. 일 태양에서, 에너지원(20)으로부터의 에너지 펄스는 어닐링 영역(12)을 가로질러 전달된 에너지의 양 및/또는 펄스의 주기에 걸쳐 전달된 에너지의 양이 특정 희망 영역의 우선적인 용융을 향상시키기에 최적화되도록 조정된다. 일 태양에서, 레이저의 파장은 복사선의 상당한 부분이 기판(10) 상에 배치되는 실리콘 층에 의하여 흡수되도록 동조된다. 실리콘 함유 기판 상에서 실행되는 레이저 어닐링 프로세스에 있어서, 복사선의 파장은 통상적으로 약 800 nm 보다 더 작으며, 강한 자외선(UV), 적외선(IR) 또는 다른 희망 파장에서 전달될 수 있다. 일 실시예에서, 에너지원(20)은, 레이저와 같은, 약 500 nm 내지 약 11 마이크로미터의 파장에서 복사선을 전달하도록 구성된 강한 광원(light source)이다. 어느 경우에서건, 어닐링 프로세스는 일반적으로 약 1초 또는 그 미만 정도와 같은 비교적 짧은 시간 동안에 기판의 주어진 영역 상에서 이루어진다.

일 태양에서, 기판의 표면에 전달된 에너지의 양은 용융 깊이가 비정질화 임플란트 단계(amorphization implant step)에 의하여 한정된 비정질 깊이(amorphous depth)를 넘어서 연장하지 않도록 구성된다. 보다 깊은 용융 깊이는 도핑된 비정질 층으로부터 도핑되지 않은 용융층 내로의 불순물의 확산을 용이하게 한다. 이와 같은 바람직하지 않은 확산은 반도체 기판상에서의 회로의 전기적 특성을 급격하게 그리고 해롭게 변화시킬 수 있다. 일부 어닐링 프로세스에서는, 기판의 표면을 급격하게 한정된 깊이, 예를 들어 0.5 마이크로미터 미만까지 용융시키기 위하여 매우 짧은 시간 동안에 기판의 표면으로 에너지가 전달된다. 정확한 깊이는 제조되는 전자 장치의 크기에 의해 결정된다.

어닐링 프로세스 동안의 기판의 온도 제어

일 실시예에서, 도 1에 도시된, 기판(10)의 표면을 열 교환 장치(15)의 기판 지지 표면(16)과 열적 접촉하도록 배치함으로써 열적 프로세스 동안에 기판의 온도를 열적으로 제어하는 것이 바람직할 수 있다. 열 교환 장치(15)는 어닐링 프로세스 동안에 또는 이에 앞서 기판을 가열 및/또는 냉각시키도록 일반적으로 구성된다. 이러한 구성에서, 캘리포니아 산타 클라라(Santa Clara)의 Applied Materials Inc. 로부터 구입할 수 있는 종래의 기판 히터와 같은 열 교환 장치(15)가 기판의 어닐링된 영역의 후프로세스 특성(post-processing properties)을 향상시키는데 사용될 수 있다. 일반적으로, 기판(10)은 열 교환 장치(15)를 포함하는 프로세스 챔버(도시되지 않음)의 봉해진 프로세싱 환경(enclosed processing environment)(도시되지 않음) 내에 배치된다. 프로세싱 동안에 내부에 기판이 존재하는 상기 프로세싱 환경은 진공화될 수 있거나 또는, 산소와 같이, 프로세싱 동안 바람직하지 않은 가스의 낮은 부분압을 갖는 불활성 가스를 포함할 수 있다.

일 실시예에서, 기판은 용융 온도에 도달하기 위해 요구되는 에너지가 최소화되도록 어닐링 프로세스를 수행하기에 앞서 예열(preheat)될 수 있으며, 이는 기판의 급격한 가열 및 냉각에 기인한 어떠한 유도 응력도 감소시킬 수 있고 또한 기판의 재응고된 영역에서의 결함 밀도를 감소시킬 수도 있다. 일 태양에서, 열 교환 장치(15)는 기판 지지 표면(16) 상에 배치되는 기판을 가열하도록 구성된 저항성 가열 부재(15A) 및 온도 제어기(15C)를 포함한다. 온도 제어기(15C)는 제어기(21)(아래에서 설명됨)와 연통한다. 일 태양에서, 기판을 약 20℃ 내지 약 750℃의 온도로 예열하는 것이 바람직할 수 있다. 기판이 실리콘 함유 물질로부터 형성되는 일 태양에서는, 기판을 약 20℃ 내지 약 500℃의 온도로 예열하는 것이 바람직할 수 있다.

다른 실시예에서, 어닐링 프로세스 동안에 기판에 추가되는 에너지에 기인한 임의의 인터디퓨젼(interdiffusion)을 감소시키기 위해서 및/또는 도 8과 관련하여 기술된 바와 같이 프로세싱 동안에 다양한 영역의 비정질화를 증가시키도록 용융 이후의 재성장 속도를 증가시키기 위해서 프로세싱 동안에 기판을 냉각시키는 것이 바람직할 수 있다. 일 구성에서, 열 교환 장치(15)가 기판 지지 표면(16) 상에 배치되는 기판을 냉각시키도록 구성된 하나 또는 그보다 많은 유체 채널(15B) 및 극저온 냉각기(15D)를 포함한다. 일 태양에서, 제어기(21)와 연통하는 종래의 극저온 냉각기(15D)가 하나 또는 그보다 많은 유체 채널(15B)을 통하여 냉각 유체를 전달하도록 구성된다. 일 태양에서, 기판을 약 -240℃ 내지 약 20℃의 온도로 냉각하는 것이 바람직할 수 있다.

제어기(21)(도 1)는 일반적으로 본 명세서에 기술된 열적 프로세싱 기술의 자동화 및 제어를 용이하게 하도록 구성되며, 통상적으로 중앙 처리 장치(CPU)(도시되지 않음), 메모리(도시되지 않음), 및 지지 회로(또는 I/O)(도시되지 않음)를 포함할 수 있다. CPU는 다양한 프로세스 및 하드웨어(예를 들어 종래의 전자기 복사선 탐지기, 모터, 레이저 하드웨어)를 제어하기 위해 산업 환경(settings)에서 사용되는 임의의 형태의 컴퓨터 프로세서 중 하나일 수 있으며, 프로세스를 모니터할 수 있다(예를 들어 기판 온도, 기판 지지부 온도, 펄스 레이저로부터의 에너지의 양, 탐지기 신호). 메모리(도시되지 않음)는 CPU에 연결되며, 국부(local) 또는 원격(remote) 방식의 랜덤 액세스 메모리(RAM), 판독 전용 기억장치(ROM), 플로피 디스크, 하드 디스크, 또는 임의의 다른 형태의 디지털 기억장치와 같은 하나 또는 그보다 많은 용이하게 입수가능한 메모리일 수 있다. 소프트웨어 명령 및 데이터는 CPU에 명령을 내리기 위하여 코드화되어 메모리 내에 저장될 수 있다. 지원 회로(도시되지 않음)도 종래의 방식으로 프로세서를 지원하기 위하여 역시 CPU에 연결된다. 지원 회로는 종래의 캐쉬(cache), 전력 공급기(power supplies), 클럭 회로(clock circuits), 입력/출력 회로, 하위 시스템, 등등을 포함할 수 있다. 제어기에 의해 판독가능한 프로그램(또는 컴퓨터 명령)은 기판상에서 어떠한 작업이 수행될 수 있는가를 결정한다. 바람직하게는, 프로그램이 제어기에 의해 판독가능한 소프트웨어이고 기판 위치, 각각의 전자기 펄스로 전달되는 에너지의 양, 하나 또는 그보다 많은 전자기 펄스의 타이밍, 각각의 펄스에 대한 시간의 함수로서의 파장 및 강도, 기판의 다양한 영역의 온도, 및 이들의 임의의 조합을 모니터하고 제어하기 위한 코드를 포함한다.

선택적 용융

형성된 장치의 다양한 영역 사이의 인터-디퓨젼(inter-diffusion)을 최소화하고, 기판 물질에서의 결함을 제거하고, 기판의 다양한 영역에서 불순물을 보다 균일하게 분포시키기 위한 노력에서, 하나 또는 그보다 많은 프로세싱 단계가 기판의 다양한 영역 상에서 수행되어 이들이 어닐링 프로세스 동안에 에너지원으로부터 전달되는 에너지에 노출될 때 우선적으로 재용융될 수 있게 한다. 어닐링 프로세스 동안에 기판의 제1 영역 및 제2 영역 모두가 대략 동일한 양의 에너지에 노출될 때 기판의 제1 영역이 기판의 제2 영역보다 우선적으로 용융되도록 기판의 제1 영역의 특성을 변경하는 프로세스는, 이하에서 이들 두 영역 사이의 용융점 차이(melting point contrast)를 형성하는 것으로 기술된다. 일반적으로, 기판의 희망 영역을 우선적으로 용융시킬 수 있게 하도록 변경될 수 있는 기판의 특성은, 기판의 희망 영역 내에서 하나 또는 그보다 많은 요소를 임플란트, 드라이빙-인(driving-in) 및/또는 공동 증착(co-depositing)하고, 기판의 희망 영역에 물리적인 손상을 형성하고, 그리고 기판의 희망 영역에 용융점 차이를 형성하도록 형성된 장치 구조를 최적화하는 것을 포함한다. 이러한 변경 프로세스의 각각이 순차적으로 검토될 것이다.

도 2a-2c는 본원발명의 일 실시예가 포함된 장치 제조 시퀀스의 서로 상이한 단계에서 전자 장치(200)의 횡단면도를 도시한다. 도 2a는 MOS 장치의 소스 및 드레인 영역과 같은 두 개의 도핑 영역(doped region)(201)(예를 들어 도핑 영역(201A-201B)), 게이트(215), 및 게이트 산화층(gate oxide layer)(216)을 갖는 기판(10)의 표면(205) 상에 형성되는 통상적인 전자 장치(200)의 측면도를 도시한다. 도핑 영역(201A-201B)은 일반적으로 희망 불순물 물질을 기판(10)의 표면(205) 내로 임플란트함으로써 형성된다. 일반적으로, 통상적인 n-형 불순물(도너 유형 종(donor type species))은 비소(As), 인(P), 및 안티몬(Sb)을 포함할 수 있으며, 통상적인 p-형 불순물(억셉터 유형 종(acceptor type species))은 도핑 영역(201A-201B)을 형성하기 위하여 반도체 기판(10) 내로 도입되는 붕소(B), 알루미늄(Al), 및 인듐(In)을 포함할 수 있다. 도 3a는 도핑 영역(201A)을 통해 연장하는 경로(203)를 따라 표면(205)으로부터 기판(10) 내로 이어지는 깊이의 함수로서의 불순물 물질의 농도의 일 예시(예를 들어 곡선 C1)를 도시한다. 도핑 영역(201A)은 임플란트 프로세스 이후에, 접합부 깊이(D1)를 갖는데, 이는 불순물 농도가 무시할 만한 양으로 줄어드는(drop off) 지점으로 정의될 수 있다. 도 2a-2f는 본원발명의 다양한 양태 중 일부를 도시하기 위한 의도일 뿐이며, 본 명세서에 기술된 발명의 다양한 실시예를 사용하여 형성될 수 있는 장치의 영역, 구조의 유형, 또는 장치의 유형에 관해서 제한하고자 하는 의도는 아님을 주의해야 한다. 일 예시에서, 도핑 영역(201)(예를 들어, MOS 장치의 소스 또는 드레인 영역)은 본 명세서에 기술된 발명의 범위로부터 변경되지 않고 게이트(215)(예를 들어 MOS 장치 내의 게이트)의 위치에 대하여 상승되거나 하강될 수 있다. 반도체 장치의 크기가 감소함에 따라 기판(10)의 표면(205) 상에 형성되는 전자 장치(200)의 구조적 요소의 위치 및 기하형태는 장치 제조성 또는 장치 성능을 향상시키기 위하여 변경될 수 있다. 또한 도 2a-2e에 도시된 바와 같이, 단지 단일 도핑 영역(201A)만의 변경은 본 명세서에 기술된 발명의 범위에 관해 한정하기 위한 의도가 아니며, 이는 단지 본원발명의 실시예가 반도체 장치를 제조하는데 있어서 어떻게 사용될 수 있는가를 예시하기 위한 의도임을 주의해야 한다.

도 2b는 기판(10)의 이산 영역(예를 들어 변경된 영역(210))의 특성을 선택적으로 변경하도록 구성된 프로세싱 단계 동안의, 도 2a에 도시된 전자 장치(200)의 측면도를 도시하는데, 상기 영역은 이 경우에 용융점 차이를 형성하기 위하여 단일 도핑 영역(201A)을 포함하는 영역이다. 변경 프로세스를 수행한 이후에 변경된 영역(210) 및 변경되지 않은 영역(211) 사이의 용융점 차이가 형성될 것이다. 일 실시예에서, 변경 프로세스는 기판의 표면상에 증착됨에 따라 물질을 층에 추가하는 단계(들)를 포함하며, 여기서 주입된 물질은 변경된 영역(210) 내에서 영역(202)의 용융점을 낮추도록 기판 물질과 함께 혼합물(alloy)을 형성하도록 구성된다. 일 태양에서, 주입된 물질은 애피택시얼 층 증착 프로세스 동안에 증착된 층에 첨가된다.

다른 실시예에서, 변경 프로세스는 변경된 영역(210) 내에서 영역(202)의 용융점을 낮추도록 기판 물질과 함께 혼합물을 형성하도록 구성된 물질을 임플란트(도 2b의 A 참조)하는 단계를 포함한다. 일 태양에서, 변경 프로세스는 도 2b에 도시된 바와 같이, 혼합물을 형성하는 물질을 깊이(D2)로 임플란트하도록 구성된다. 도 3b는 표면(205)으로부터 경로(203)를 따라 기판(10)을 통하는 깊이의 함수로서 임플란트된 혼합물 형성 물질(예를 들어 곡선 C2) 및 불순물 물질의 농도(예를 들어 곡선 C1)의 일 예시를 도시한다. 일 태양에서, 기판(10)이 실리콘 함유 물질로부터 형성되며, 사용될 수 있는 임플란트된 혼합물 형성 물질은, 예를 들어, 게르마늄(Ge), 비소(As), 갈륨(Ga), 탄소(C), 주석(Sn), 및 안티몬(Sb)을 포함한다. 일반적으로, 혼합물을 형성하는 물질은 기판 베이스 물질의 존재하에 가열될 때 변경된 영역(210)에서 영역(202)의 용융점을 변경되지 않은 영역(211)에 비하여 낮아지도록 하는 임의의 물질일 수 있다. 일 태양에서, 실리콘 기판의 영역은 변경된 영역 및 변경되지 않은 영역 사이의 용융점을 감소시키기 위하여 약 1% 내지 약 20%의 게르마늄을 첨가함으로써 변경된다. 이러한 농도의 게르마늄의 첨가는 변경되지 않은 영역에 대해 변경된 영역의 용융점을 약 300℃ 만큼 낮출 것으로 여겨진다. 일 태양에서, 실리콘 기판 내에 형성된 영역(202)은 게르마늄(Ge)과 탄소(C)를 함유하고, 이로써 영역(202)의 용융점을 변경되지 않은 영역(211)에 비하여 낮추도록 SiXGeyCz 혼합물을 형성할 것이다. 다른 태양에서는, 실리콘 기판의 영역이 변경된 영역 및 변경되지 않은 영역 사이의 용융점을 감소시키기 위하여 약 1% 또는 그보다 낮은 비소의 첨가에 의하여 변경된다.

다른 실시예에서, 변경 프로세스는 기판의 결정 구조를 손상시켜 영역을 보다 비정형으로 만들기 위하여 다양한 변경된 영역(예를 들어 변경된 영역(210))에서 기판(10) 물질에 일부 손상을 야기하는 단계를 포함한다. 단결정 실리콘 기판을 손상시키는 것과 같은 기판의 결정 구조에 대한 손상의 야기는 기판의 원자 결합 구조 내의 변화로 인하여 손상되지 않은 영역에 비하여 이러한 영역의 용융점을 낮추고 이로써 이들 두 영역 사이에서 열역학 특성 차이를 야기할 것이다. 일 태양에서, 도 2b의 변경된 영역(210)에 대한 손상은 기판의 표면에 손상을 형성할 수 있는 투사물(projectile)로 기판(10)의 표면(205)을 가격(bombarding)함으로써(도 2b의 "A" 참조) 수행된다. 일 태양에서, 투사물은 변경된 영역(210) 내의 영역(202)에 손상을 야기하도록 실리콘 함유 기판 내로 임플란트되는 실리콘(Si) 원자이다. 다른 태양에서, 기판 물질에 대한 손상은 변경된 영역(210)의 영역(202)에 손상을 야기하도록 임플란트 프로세스, 이온 빔, 또는 바이어스된 플라스마를 사용하여, 아르곤(Ar), 크립톤(Kr), 크세논(Xe) 또는 심지어 질소(N2)와 같은 가스 원자로 표면을 가격함으로써 형성된다. 일 태양에서, 변경 프로세스는 도 2b에 도시된 바와 같이, 깊이(D2)까지 야기된 손상을 갖는 영역(202)을 형성하도록 구성된다. 약 5×1014 내지 약 1×1016 /cm2의 변위(dislocation) 또는 공극(vacancy) 밀도는 변경되지 않은 영역(211)과 변경된 영역(210) 사이의 용융점 차이를 형성하는데 유용할 수 있다고 여겨진다. 일 태양에서, 도 3b는 표면(205)으로부터 그리고 경로(203)를 따라 기판(10)을 통하는 깊이의 함수로서 결함 밀도(예를 들어 곡선 C2) 및 불순물 물질의 농도(예를 들어 곡선 C1)의 일 예시를 도시한다.

도 2a-2b는 도핑 프로세스 이후에 변경 프로세스가 수행되는 프로세스 시퀀스를 도시하는데, 이러한 프로세스 시퀀스는 본 명세서에 기술된 본원발명의 범위를 제한하고자 하는 의도는 아님을 주의해야 한다. 예를 들어, 일 실시예에서, 도 2a에 도시된 도핑 프로세스를 수행하기에 앞서 도 2b에 기술된 변경 프로세스를 수행하는 것이 바람직하다.

도 2c는 레이저로부터의 광학 복사선과 같은 에너지원으로부터 방출되는 복사선 "B"에 노출되는, 도 2b에 도시된 전자 장치(200)의 측면도를 도시한다. 이러한 단계 동안에, 기판(10)을 가로질러 배치되는 변경된 영역(들)(예를 들어 변경된 영역(210)) 및 변경되지 않은 영역들(예를 들어 변경되지 않은 영역(211))은, 변경되지 않은 영역(211)이 고체 상태로 남아 있는 동안에, 복사선 "B"의 펄스가 가해진 이후 변경된 영역(들)(210)의 영역(202)이 선택적으로 용융되어 재응고되게 하는 양의 에너지에 노출된다. 에너지의 양, 에너지 밀도 및 복사선 "B" 이 가해지는 기간은 영역(202)의 희망 깊이, 영역(202)을 형성하기 위해 사용되는 물질, 전자 장치(200)를 형성하는데 사용되는 다른 물질, 및 형성된 전자 장치(200) 내에서의 구성요소의 열 전달 특성을 파악함으로써 영역(202)을 우선적으로 용융시키도록 설정될 수 있다. 도 2c 및 3c에 도시된 바와 같이, 복사선 "B"에 노출되면 영역(202)의 재용융 및 응고는 불순물 원자의 농도(예를 들어 곡선 C1) 및 혼합물 형성 원자의 농도(예를 들어 곡선 C2)가 영역(202)에서 보다 균일하게 재분포되도록 한다. 또한, 영역(202) 및 기판 벌크 물질(221) 사이의 불순물 농도는 급격하게 한정된 경계(즉, "과도하게 급격한(hyper-abrupt)" 접합부)를 가지며, 이로써 기판 벌크 물질(221) 내로의 바람직하지 않은 확산을 최소화한다. 용융점 차이를 향상시키기 위하여 기판(10) 내로 손상이 야기되는, 앞서 기술된 일 실시예에서, 재응고 이후의 결함의 농도(예를 들어 곡선 C2)는 무시할만한 수준으로 바람직하게 줄어들게 될 것이다.

열적 단열 기술

다른 실시예에서, 형성된 장치의 상이한 영역의 다양한 열적 특성이 한 영역을 다른 영역에 비하여 우선적으로 용융시키도록 조정된다. 일 태양에서, 서로 상이한 열 전도성(k)을 갖는 물질을 이용해 장치의 서로 상이한 영역을 형성함으로써 용융점 차이가 형성된다. 전도에 의해 전달되는 열은 다음의 방정식:

Q = kAΔT/Δx

에 의해 지배되는데, 여기서 Q는 본체를 통한 열 유동 시간 비율(time rate)이며, k는 물질 온도 및 물질의 속성에 따른 전도 상수이며, A는 열 유동이 통과하는 면적이며, Δx는 이를 통해 열이 통과하는 대상 본체의 두께이며, ΔT는 이를 통해 열이 전달되는 온도 차이임을 주의해야 한다. 따라서, k가 물질의 특성이므로 기판의 다양한 영역의 물질의 변경 또는 선택은 다양한 영역에 대한 용융점 차이를 증가시키도록 기판의 서로 상이한 영역으로의 및 서로 상이한 영역으로부터의 열 유동을 제어할 수 있게 한다. 즉, 기판의 일 영역에서의 물질이 다른 영역에서의 물질에 비하여 보다 높은 열 전도성을 갖는 곳에서는, 레이저 어닐링 프로세스 동안에 전도성 손실(conductive losses)을 통해 보다 많은 열 에너지를 잃게 될 것이며, 이로써 보다 낮은 열 전도성을 갖는 다른 영역이 도달하게 될 온도와 동일한 온도에 도달하지 못할 것이다. 보다 높은 열 전도성 영역과 밀접하게 접촉하는 영역은 용융되는 것으로부터 방지될 수 있는 반면, 보다 낮은 열 전도성 영역과 밀접하게 접촉하는 다른 영역은 레이저 어닐링 프로세스 동안에 그 용융점에 도달하게 될 것이다. 전자 장치(200)의 다양한 영역의 열 전도성을 제어함으로써 용융점 차이가 증가될 수 있다. 가변 열 전도성을 갖는 영역의 형성은, 상이한 열 전도성을 갖는 이러한 영역들을 형성하도록 전자 장치(200)의 다양한 하부층(underlying layers)에서 종래의 증착, 패터닝(pattering) 및 식각 기술을 수행함으로써 수행될 수 있다. 상이한 열 전도성을 갖는 하부층은 종래의 화학 기상 증착(CVD) 프로세스, 원자층 증착(ALD) 프로세스, 임플란트 프로세스, 및 애피택시얼 증착 기술을 사용함으로써 형성될 수 있다.

도 2d는 기판 벌크 물질(221)보다 낮은 열 전도성을 갖는 매설 영역(224)을 갖는 전자 장치(200)의 측면도를 도시한다. 이러한 경우에 에너지원으로부터 방출되는 복사선 "B"는 기판의 표면(205)에서 흡수되어 기판(10)을 통해 전도되며, 이로써 매설 영역(224) 위의 영역(즉, 도핑 영역(201A))에서의 열 유동(Q1)은 보다 낮은 전도성의 매설층을 갖지 않는 영역으로부터의 열 유동(Q2)보다 더 적다. 따라서, 매설 영역(224) 위의 영역으로부터 손실되는 열이 기판의 다른 영역보다 더 적으므로, 이러한 영역은 장치의 다른 영역보다 더 높은 온도에 도달할 것이다. 에너지원(20)에 의해 전달되는 에너지의 양을 제어함으로써 매설층 위의 영역에서의 온도는 이러한 영역의 온도를 다른 영역에 비하여 우선적으로 용융시키게 하는 수준으로 상승될 수 있다. 일 태양에서, 매설 영역(224)은 이산화규소(SiO2), 질화규소(SiN), 게르마늄(Ge), 비화갈륨(GaAs), 이들의 조합 또는 이들의 유도체와 같은 절연성 물질로 제조된다. 따라서 용융될 영역의 기판 물질의 실제 용융점이 변경되지 않는다 하더라도, 선택적으로 용융되게 하는, 기판 표면의 다른 영역으로부터의, 열적 거동에서의 정량화할 수 있고 반복가능한(quantifiable and repeatable) 현저한 차이가 여전히 존재한다. 다른 실시예에서, 매설 영역(224)은 기판 벌크 물질(221)보다 더 높은 전도성을 가질 수 있는데, 이는 이후 매설층을 갖지 않는 영역이 매설층 위의 영역에 비하여 우선적으로 용융될 수 있게 할 수 있다.

표면 특성의 변경

표면 특성의 변경

삭제

일 실시예에서, 기판(10)의 다양한 영역(202) 위의 표면의 특성은 하나 또는 그보다 많은 희망 영역 사이의 용융점 차이를 변화시키도록 변경된다. 일 태양에서, 희망 영역에서 기판 표면의 방사율(emissivity)은 프로세스 동안에 기판 표면으로부터 전달되는 에너지의 양을 변화시키도록 변경된다. 이러한 경우에, 다른 영역보다 더 낮은 방사율을 갖는 영역은 에너지원(20)으로부터 받은 흡수된 에너지를 재복사(reradiate) 할 수 없음으로 인해서 보다 높은 프로세싱 온도에 도달하게 될 것이다. 기판 표면의 용융을 수반하는 어닐링 프로세스를 수행할 때, 기판 표면에서 달성되는 프로세싱 온도는 매우 높을 수 있으며(예를 들어, 실리콘에 대하여 ~ 1414℃), 따라서 방사율을 변화시키는 효과는 복사 열 전달이 주요 열 손실 메커니즘이므로 용융점 차이에 극적인 효과를 미칠 수 있다. 따라서, 기판 표면의 서로 상이한 영역의 방사율에서의 변화는 기판의 다양한 영역에 의해 달성되는 궁극적 온도에 상당한 영향력을 가질 수 있다. 낮은 방사율을 갖는 영역은 어닐링 프로세스 동안에 용융점 위로 상승 될 수 있는 반면, 동일한 양의 에너지를 흡수한, 높은 방사율을 갖는 영역은 실질적으로 용융점 아래에서 머무를 수 있다. 방사율 차이(emissivity contrast) 또는 다양한 표면의 방사율을 변화시키는 것은 기판 표면상에 낮거나 높은 방사율 코팅을 선택적으로 증착하거나 및/또는 기판 표면을 변경하는 것(예를 들어, 표면 산화, 표면 러프닝(roughening))을 통해서 달성될 수 있다.

일 실시예에서, 하나 또는 그보다 많은 영역에서의 기판 표면의 반사율(reflectivity)이 기판(10)이 에너지원으로부터의 에너지에 노출될 때 흡수된 에너지의 양을 변화시키기 위해 변경된다. 기판 표면의 반사율을 변화시킴으로써, 흡수된 에너지의 양 그리고 이로써 기판 표면에서 및 그 하부의 영역에서 기판에 의해 달성되는 최대 온도는 반사율에 기초하여 달라질 것이다. 이러한 경우에 보다 낮은 반사율을 갖는 표면은 보다 높은 반사율을 갖는 다른 영역보다 더 용융되기 쉬울 것이다. 기판 표면의 반사율의 변화는 기판 표면상에 낮거나 높은 반사율 코팅을 선택적으로 증착하거나 및/또는 기판 표면을 변경하는 것(예를 들어, 표면 산화, 표면 러프닝(roughening))을 통해서 달성될 수 있다. 높은 흡수성(비 반사성) 코팅이 어닐링 프로세스 동안에 용융되도록 의도된 영역에 선택적으로 가해질 수 있다.

도 2e는 코팅(225)이 선택적으로 증착되거나 균일하게 증착되어 이후 선택적으로 제거됨으로써, 기판(10)의 표면(205) 상의 다른 영역과는 상이한 방사율 및/또는 반사율을 갖는 층을 남기는 일 실시예를 도시한다. 이러한 경우에, 코팅(225) 아래의 도핑 영역(201A)에서의 열 유동(Q1)은 기판의 다른 영역에서 흡수된 에너지(Q2)에 대한 코팅의 특성에 기초하여 조정될 수 있다. 이러한 방식으로 코팅(225)으로부터 반사된 열 또는 열 손실(Q3)은 다른 영역으로부터 손실된 열(Q4)에 비하여 변화될 수 있다. 일 태양에서, 탄소 함유 코팅이 CVD 증착 프로세스를 이용하여 기판 표면상에 증착된다.

도 2f는 기판 표면의 광학 특성(예를 들어 방사율, 반사율)을 변경시키는 코팅(226)이 기판 표면에 걸쳐, 예를 들어 도 2a에 도시된 장치에 걸쳐 증착되고, 이후 일정량의 물질이 제거되어 상이한 광학 특성을 갖는 영역을 형성하는 일 실시예를 도시한다. 예를 들어, 도 2f에 도시된 바와 같이, 코팅(226)이 게이트(215)의 표면으로부터 제거되어짐으로써, 투사 복사선 "B"에 노출된 게이트의 표면(205) 및 코팅(226)의 표면이 남겨진다. 이러한 경우에, 코팅(226) 및 게이트의 표면(205)은 상이한 방사율 및/또는 상이한 반사율과 같은 상이한 광학 특성을 갖는다. 상이한 광학 특성을 갖는 영역을 형성하거나 노출시키는데 사용되는 제거 프로세스가 습식 식각 또는 화학 기계적 연마(CMP) 프로세스와 같은 종래의 물질 제거 프로세스를 이용하여 수행될 수 있다. 이러한 경우에 코팅(226) 아래의 도핑 영역(201A-201B)에서의 열 유동(Q1) 및 흡수는 기판의 게이트(215) 영역에서의 흡수 및 열 유동(Q2)에 비하여 코팅의 특성에 기초하여 조정될 수 있다. 이러한 방식으로 코팅(226)으로부터 반사된 열 또는 열 손실(Q3)이 게이트(215) 영역으로부터 반사된 열 또는 열 손실(Q4)에 비하여 변화될 수 있다.

일 실시예에서, 코팅(226)은 투사 복사선의 하나 또는 그보다 많은 파장에 노출되는 기판의 다양한 영역의 광학 특성(예를 들어, 방사율, 흡수성, 반사율)을 홀로 또는 함께 변화시키는, 희망 두께의 하나 또는 그보다 많은 증착층을 포함한다. 일 태양에서, 코팅(226)은 투사 복사선 "B"의 하나 또는 그보다 많은 파장을 홀로 또는 함께 우선적으로 흡수하거나 반사하는 층을 포함한다. 일 실시예에서, 코팅(226)은 불화규소 유리(FSG), 비정질 탄소, 이산화규소, 탄화 규소, 규소 탄소 게르마늄 화합물(SiCGe), 질소 함유 탄화규소(SiCN), 산타 클라라의 Applied Materials, Inc. 로부터 구입가능한 프로세스에 의해 제조된 BLOkTM 절연 물질(dielectric material), 또는 화학적 기상 증착(CVD) 프로세스나 원자층 증착(ALD) 프로세스를 이용하여 기판 표면상에 증착되는 탄소 함유 코팅과 같은 절연 물질(dielectric material)을 포함한다. 일 태양에서, 코팅(226)은, 이에 제한되는 것은 아니지만, 티타늄(Ti), 질화 티타늄(TiN), 탄탈(Ta), 코발트(Co), 또는 루테늄(Ru)과 같은 금속을 포함한다.

본 명세서에서 논의된 하나 또는 그보다 많은 다양한 실시예들은 프로세스 윈도우(process window)의 추가적인 증가를 위하여 서로 함께 사용될 수 있다는 것을 주의해야 한다. 예를 들어, 선택적으로 증착된 광 흡수 코팅은 어닐링 프로세스의 프로세스 윈도우를 넓히기 위하여 특정 희망 영역의 도핑과 함께 사용될 수 있다.

우선적 용융을 달성하기 위한 에너지원 출력의 동조

상술한 바와 같이, 에너지원(20)은 일반적으로 기판(10)의 특정 희망 영역을 우선적으로 용융시키기 위하여 전자기 에너지를 전달하도록 구성된다. 전자기 에너지의 통상적인 공급원은, 이에 제한되는 것은 아니지만, 광학 복사선 공급원(예를 들어 레이저(UV 파장, IR 파장 등)), 전자 빔 공급원, 이온 빔 공급원, 및/또는 마이크로파 에너지 공급원을 포함한다. 본원발명의 일 실시예에서, 에너지원(20)은 기판의 희망 영역을 용융점까지 선택적으로 가열하기 위하여 레이저와 같은 광학 복사선을 전달하도록 구성된다.

일 태양에서, 기판(10)은 하나 또는 그보다 많은 적절한 파장에 있는 복사선을 방출하는 레이저로부터의 에너지 펄스에 노출되며, 방출된 복사선은 특정 희망 영역의 우선적인 용융을 강화시키기 위해 희망 에너지 밀도(W/cm2) 및/또는 펄스 지속기간(pulse duration)을 갖는다. 실리콘 함유 기판 상에서 수행되는 레이저 어닐링 프로세스에 대해서, 복사선의 파장은 통상적으로 약 800 nm 보다 작다. 어느 경우에서건, 어닐링 프로세스는 일반적으로 약 1초 또는 그 미만 정도와 같은 비교적 짧은 시간 동안 기판의 주어진 영역 상에서 이루어진다. 어닐링 프로세스에 사용되는 희망 파장 및 펄스 프로파일(pulse profile)은 기판의 물질 특성의 관점에서 레이저 어닐링 프로세스의 광학적 및 열적 모델링에 기초하여 결정될 수 있다.

도 4a-4d는 향상된 용융점 차이를 달성하기 위하여 그리고 어닐링 프로세스 결과를 향상시키기 위하여 에너지원(20)으로부터 어닐링 영역(12)으로 전달되는(도 1) 에너지 펄스의 다양한 특성이 시간의 함수로서 조정되는 다양한 실시예를 도시한다. 일 실시예에서, 용융되도록 의도된 기판의 영역으로 입력되는 열을 강화하고 다른 영역으로 입력되는 열을 최소화하도록 시간의 함수로서 레이저 펄스의 형태를 변화시키는 것 및/또는 전달된 에너지의 파장을 변화시키는 것이 바람직하다. 또한 일 태양에서, 기판으로 전달되는 에너지를 변화시키는 것도 바람직할 수 있다.

도 4a는 에너지원(20)으로부터 기판(10)으로 전달될 수 있는(도 1 참조) 전자기 복사선(예를 들어 펄스(401))의 단일 펄스의 시간에 대한 전달된 에너지의 그래프를 그래프식으로 도시한다. 도 4a에 도시된 펄스는 일반적으로 전체 펄스 지속기간(t1) 동안 일정량의 에너지(E1)를 전달하는 직사각형 펄스이다.

일 태양에서, 펄스(401)의 형태는 기판(10)에 전달됨에 따라 시간의 함수로서 변화될 수 있다. 도 4b는 하나의 에너지원(20)으로부터 기판(10)으로 전달될 수 있는 전자기 복사선의 상이한 형태를 갖는 두 펄스(401A, 401B)의 그래프를 그래프식으로 도시한다. 이러한 예시에서, 각각의 펄스는 각각의 곡선 아래의 면적에 의해 나타나듯이, 동일한 전체 에너지 출력을 포함할 수 있지만, 다른 펄스에 비하여 하나의 펄스에 기판(10)의 영역을 노출시키는 효과는 어닐링 프로세스 동안에 나타나는 용융점 차이를 향상시킬 수 있다. 따라서, 각각의 펄스에서 전달되는 에너지의 형태, 최고 전력 수준, 및/또는 양을 조절함으로써 어닐링 프로세스가 향상될 수 있다. 일 태양에서, 펄스는 정규곡선 형태(gaussian shape)를 갖는다.

도 4c는 사다리꼴 형태의 전자기 복사선 펄스(예를 들어 펄스(401))를 그래프식으로 도시한다. 이러한 경우에, 펄스(401)의 두 개의 상이한 부분(예를 들어 (402) 및 (404))에서, 전달된 에너지는 시간의 함수로서 변화된다. 도 4c가 시간에 대한 에너지가 선형 방식(linear fashion)으로 변화하는 펄스(401) 프로파일을, 또는 형태를 도시하고 있지만, 펄스로 전달되는 에너지의 시간 변화는, 예를 들어 제2차(second degree), 제3차, 또는 제4차 형태의 곡선을 가질 수 있으므로, 이는 본원발명의 범위를 제한하고자 하는 것은 아니다. 다른 태양에서, 시간의 함수로서 펄스로 전달되는 에너지의 프로파일이, 또는 형태가 2차(second order), 3차, 또는 지수함수 형태의 곡선일 수 있다. 다른 실시예에서, 희망 어닐링 결과를 달성하기 위하여 프로세싱 동안에 상이한 형태를 갖는 펄스(예를 들어, 직사각형 및 삼각형 변조 펄스, 사인곡선 및 직사각형 변조 펄스, 직사각형, 삼각형 및 사인함수 변조 펄스 등등)를 사용하는 것이 바람직할 수 있다.

장치의 다양한 영역의 특성에 따라서, 전달된 전자기 복사선 펄스의 형태가 어닐링 프로세스 결과를 향상시키도록 조절될 수 있다. 예를 들어, 도 4b를 참조하면, 어닐링 프로세스 동안에 용융될 기판의 다양한 영역이 낮은 열 전도성을 갖는 영역에 의하여 장치의 다른 영역으로부터 열적으로 단열되는 일부 상황에서는, 펄스(401B)와 유사한 형태를 갖는 펄스의 사용이 유리할 수 있다. 보다 긴 지속시간을 갖는 펄스가 유리할 수도 있는데, 이는 용융될 영역이 열적으로 보다 단열되어 용융될 영역에서의 온도가 용융점 온도까지 상승하도록 하는 반면에, 기판의 열적으로 보다 전도성이 있는 물질 영역이 전도에 의해 열을 방산하는데 있어서 보다 많은 시간을 가질 것이기 때문이다. 이러한 경우에 펄스의 지속기간(duration), 최고 전력 수준(peak power level) 및 총 에너지 출력은 용융되도록 의도되지 않은 영역이 그 용융점에 도달하지 않도록 적절히 선택될 수 있다. 가변 방사율의 표면이 용융점 차이를 형성하기 위해 사용되는 경우에 펄스의 형태를 조절하는 프로세스도 또한 유리할 수 있다.

도 4c를 참조하면, 일 실시예에서, 부분(401)의 경사, 부분(401)의 형태, 부분(403)의 형태, 전력 수준에서의 시간(예를 들어, 에너지 수준(E1)에서의 부분(403)), 부분(404)의 경사, 및/또는 부분(404)의 형태가 어닐링 프로세스를 제어하기 위하여 조정된다. 어닐링된 영역 내의 물질이 입자 및 프로세스 결과 변화성(variability) 관련으로 인해서 프로세싱 동안에 증발하도록 하는 것은 일반적으로 바람직하지 않다는 것을 주의해야 한다. 따라서 어닐링된 영역의 과열(superheat) 및 물질의 증발을 일으키지 않고 어닐링된 영역의 온도를 그 용융점으로 신속하게 가져가도록 에너지 펄스의 형태를 조정하는 것이 바람직하다. 도 4g에 도시된 바와 같이, 일 실시예에서 어닐링 영역 내의 물질의 증발을 방지하면서 어닐링 영역을 그 용융점으로 신속하게 이동시켜, 이후 희망 시간 주기(예를 들어 t1) 동안 용융된 상태로 물질을 유지하는데 사용되는 복수의 부분(즉, 부분(402), (403A), (403B), (403C), 및 (404))을 갖도록 펄스(401)의 형태가 조정될 수 있다. 시간의 길이, 상기 부분들의 형태, 및 각각의 펄스 부분의 지속기간은, 크기, 용융 깊이, 및 어닐링 영역 내에 함유된 물질이 변화됨에 따라 변할 수 있다.

다른 태양에서, 복사 에너지의 복수의 파장이 결합되어 기판의 희망 영역으로의 에너지 전달을 향상시켜 향상된 용융점 차이를 달성시키고, 및/또는 어닐링 프로세스 결과를 향상시킬 수 있다. 일 태양에서, 각각의 결합된 파장에 의해 전달되는 에너지의 양은 용융점 차이를 향상시키고 어닐링 프로세스 결과를 향상시키도록 변화된다. 도 4d는 용융점 차이를 향상시키기 위하여 및/또는 어닐링 프로세스 결과를 향상시키기 위하여 기판(10)으로 단위 시간당 상이한 양의 에너지를 전달할 수 있는 두 개의 파장을 펄스(401)가 포함하는 일 예시를 도시한다. 이러한 예시에서, 주파수(F1)가 펄스의 주기에 걸쳐 일정한 수준에서 기판에 가해지고, 펄스의 주기 동안 시간의 주기에 대해 최고값에 달하는 부분을 제외하고 대부분의 주기 동안 일정한 수준에서 기판(10)에 다른 주파수(F2)가 가해진다.

도 4e는 두 개의 상이한 주파수(F3 및 F4)에서 에너지를 전달하는 두 개의 순차적인 부분을 갖는 펄스(401)의 그래프를 그래프식으로 도시한다. 따라서, 기판의 다양한 영역이 상이한 파장에서 상이한 비율로 에너지를 흡수할 수 있으므로, 도 4d 및 4e에 도시된 바와 같이, 가변 에너지 양을 전달할 수 있는 복수의 파장을 포함하는 펄스의 사용은 희망 어닐링 프로세스 결과를 달성하는데 유리할 수 있다.

일 실시예에서, 두 개 또는 그보다 많은 전자기 복사선 펄스가 상이한 시간에서 기판의 영역에 전달되어 기판 표면상의 영역의 온도가 용이하게 제어될 수 있다. 도 4f는 시간상에서 가변 거리로, 또는 주기(t)로 떨어져 전달되어 기판 표면상의 일정 영역을 선택적으로 용융시키는 두 개의 펄스(401A 및 401B)의 그래프를 그래프식으로 도시한다. 이러한 구성에서, 순차적인 펄스 사이의 주기(t)를 조정함으로써, 기판 표면상의 영역에 의해 도달되는 최고 온도가 용이하게 제어될 수 있다. 예를 들어, 펄스 사이의 주기(t)를, 또는 주파수를 감소시킴으로써 제1 펄스(401A)에 전달되는 열이 제2 펄스(401B)가 전달되기에 앞서 열을 방산시키는데 보다 적은 시간을 가지게 되며, 이는 펄스 사이의 주기가 증가될 때보다 기판 내에서 달성되는 최고 온도가 보다 높게 되도록 할 것이다. 이러한 방식으로 주기를 조정함으로써 에너지 및 용융 온도가 용이하게 제어될 수 있다. 일 태양에서, 각각의 펄스가 자체로는 기판이 용융 온도에 도달하도록 하기에 충분한 에너지를 포함하지 않지만 이들 펄스의 결합은 영역(202)이 용융 온도에 도달하도록 하는 것을 보장하는 것이 바람직할 수 있다. 두 개 또는 그보다 많은 펄스와 같은, 복수의 펄스를 전달하는 이러한 프로세스는 단일 에너지 펄스를 전달하는 것에 비하여 기판 물질이 겪게 되는 열적 충격을 감소시키는 경향이 있을 것이다. 열적 충격은 기판의 손상을 초래할 수 있으며 기판 상에서 수행되는 후속적인 프로세싱 단계에서 결함을 형성할 입자를 발생시킬 수 있다.

도 4f를 참조하면, 일 실시예에서, 두 개 또는 그보다 많은, 레이저와 같은, 에너지원이 순차적으로 작동하여 기판 표면의 열적 프로파일을 시간의 함수로서 형성한다. 예를 들어, 하나의 레이저 또는 레이저 배열이 기판 표면을 시간(t1) 동안 온도(T0)로 상승시키는 펄스(401A)를 전달할 수 있다. 시간(t1)의 종료시에 또는 이에 앞서, 제2 펄스(402B)가 제2 레이저로부터, 또는 나란히(in tandem) 작동하는 복수의 레이저로부터 전달되며, 이는 기판 온도를 시간(t2) 동안 온도(T1)가 되게 한다. 따라서 열적 프로파일은 복수의 레이저로부터 전달되는 에너지의 순차적인 펄스를 제어함으로써 형성될 수 있다. 이러한 프로세스는, 이에 제한되는 것은 아니지만, 불순물 확산 및 불순물 확산의 방향을 제어하는 것의 적용과 같은 열적 프로세싱 이점을 가질 수 있다.

전자기 복사선 펄스

실리콘 함유 기판, 또는 열적 프로세싱을 요구하는 다른 물질로 이루어진 기판의 표면에 충분한 전자기 복사선(광선)을 전달하기 위하여, 이하의 프로세스 제어가 사용될 수 있다.

일 실시예에서, 두 개 또는 그보다 많은, 레이저와 같은, 전자기 에너지원이 순차적으로 작동하여 열적으로 프로세싱되는 표면의 열적 프로파일을 형성하며, 여기서 레이저는 펄스-펄스(pulse-to-pulse) 에너지 변화를 교정하는 방식으로 작동된다. 일 태양에서, 도 1 및 9에 개략적으로 도시된 공급원(20)은, 이에 제한되는 것은 아니지만, 광학 방사선 공급원(예를 들어, 레이저), 전자 빔 공급원, 이온 빔 공급원, 및/또는 마이크로파 에너지 공급원과 같은, 두 개 또는 그보다 많은 전자기 에너지 공급원을 포함한다. 펄스화된 레이저(pulsed laser)와 같은 장치로부터의 펄스로부터 펄스로의(pulse-to-pulse) 에너지는 각각의 펄스의 백분율 변화(percent variation)를 가질 수 있다. 펄스 에너지에서의 변화는 기판 열적 프로세스에 대해 수용가능하지 않을 수 있다. 이러한 펄스 변화를 교정하기 위하여, 하나 또는 그보다 많은 레이저(들)가 기판 온도를 상승시키는 펄스를 전달한다. 이후 전자 제어기(예를 들어 도 1의 제어기(21))가 전달된 펄스 및 전달되고 있는 펄스의 에너지, 또는 상승 시간(rise time)을 모니터하도록 구성되고, 이후 열적 프로파일(예를 들어 시간의 함수로서 기판의 영역의 온도)을 프로세스 목표 내에 있도록 "정돈(trim)" 또는 조정하는데 요구되는 에너지의 양을 계산하고 열적 프로세싱을 완료하기 위한 최종 에너지를 전달하도록 제2 소형 레이저 또는 일련의 소형 레이저들에 명령을 내리는데 사용된다. 전자 제어기는 일반적으로 하나 또는 그보다 많은 종래의 복사선 탐지기를 사용하여 기판에 전달된 펄스의 에너지 및/또는 파장을 모니터한다. 또한 소형 레이저는 펄스 출력 에너지에서 최고점으로부터 최고점으로의(peak-to-peak) 변화를 가질 수도 있으나, 이들은 표면 처리(treatment)의 시작시 초기 펄스(또는 펄스들)보다 펄스당 실질적으로 보다 적은 에너지를 전달하므로, 이러한 오차는 일반적으로 프로세스 한도 내에 놓이게 될 것이다. 따라서 전자 제어기는 펄스에 의해 전달된 에너지에서의 변화를 보상하도록 구성되고, 이로써 열적 프로세스 동안에 희망 에너지 수준이 전달되는 것을 보장한다.

일 태양에서, 상술한 두 개 또는 그보다 많은 에너지원은 컬러 주파수의 대역폭을 갖는 레이저 광선의 단일 컬러 (파장), 다중 파장, 단일 또는 다중의 일시적 및 공간적 레이저 모드, 및 편광 상태(polarization state)를 이용하여 구현될 수도 있다.

레이저 또는 레이저들의 출력은 기판 표면으로 전달하기 위한 정확한 공간적 및 시간적 에너지 프로파일을 갖지 아니하기 쉬울 것이다. 따라서, 레이저의 출력을 형성하기 위해 마이크로렌즈를 이용하는 시스템이 기판 표면에서 균일한 공간적 에너지 분포를 생성하기 위하여 사용된다. 마이크로렌즈의 유리 유형 및 기하형태의 선택은 기판 표면으로 펄스화된 레이저 에너지를 전달하기 위해 필요한 광학 열(optical train)에서의 열적 렌싱(thermal lensing) 효과를 보상할 수 있다.

스페클(speckle)로 알려진, 기판 표면에서의 펄스 에너지의 고주파수 변동이 투사 에너지의 보강 및 상쇄 위상 간섭의 인접 영역에 의하여 생성된다. 스페클 보상은 이하의 것들을 포함할 수 있다: 빠른 변동이 레이저 펄스 또는 펄스들의 열적 프로세싱 시간보다 실질적으로 빠르게 되도록 기판에서 위상을 신속하게 변화시키기 위한 표면 음파 장치; 레이저 펄스의 펄스 첨가; 예를 들어 레이저 펄스의 교번하는 편광, 선형적으로 편광되지만 비평행 조건(nonparallel condition)에서 그 편광 상태(e-벡터)를 갖는 복수의 동시적인 또는 지연된 펄스의 전달.

패턴화된 기판상에 형성되는 열적 안정화 구조

도 5a-5c에 도시된 바와 같이, 일 실시예에서, 기판의 표면이 전자기 복사선 공급원(도시되지 않음)으로부터 전달되는 전자기 에너지(150)에 노출될 때, 용융된 실리콘 영역(112)의 깊이에서의, 또는 부피에서의 변화를 감소시키기 위하여 기판의 표면상에 균질화 층(homogenizing layer)(도 5b의 도면부호 110)이 증착된다. 용융된 영역의 깊이에서의, 또는 부피에서의 변화는 패턴화된 기판(patterned substrate)의 다양한 영역의 질량 밀도에서의 변화, 복사 에너지가 가해지는 물질의 흡수 계수(absorption coefficient), 그리고 물질의 다양한 물리적 및 열적 특성(예를 들어, 열 전도성, 열 용량, 물질의 두께)에 의하여 영향을 받는다. 일반적으로 전자기 복사선 공급원은 기판 표면의 일부를 열적으로 프로세싱하거나 어닐링하기 위하여 기판 표면에 전자기 에너지를 전달하도록 구성된다. 통상적인 전자기 복사선 공급원은, 이에 제한되는 것은 아니지만, 광학 복사선 공급원(예를 들어, 레이저), 전자 빔, 이온 빔, 또는 마이크로파 공급원을 포함할 수 있다.

도 5a-5c 및 6a-6c에 도시된 기판(100)의 표면(102) 상에 형성되는 장치 구조는, 예를 들어 실리콘 영역(112)(예를 들어, MOS 장치의 소스 또는 드레인 영역)이 본 명세서에 기술된 본원발명의 범위로부터 벗어나지 않으면서 피쳐(101)(예를 들어, MOS 장치의 게이트)의 위치에 대해 상대적으로 상승되거나 하강될 수 있으므로, 본 명세서에 기술된 본원발명의 범위를 제한하고자 하는 의도는 아니다. 반도체 장치의 크기가 감소함에 따라 기판 표면상에 형성된 장치의 구조적 요소의 위치 및 기하형태가 장치 제조성 또는 장치 성능을 향상시키도록 변화된다.

도 5a는 기판(100)의 표면(102) 상에 형성되는 복수의 실리콘 영역(112) 및 피쳐(101)를 갖는 기판(100)의 횡단면도를 도시한다. 도 5a에 도시된 바와 같이, 표면(102)은 가변적인 거리로 측방향으로 이격되는 복수의 피쳐(101)를 갖는다. 일 태양에서, 피쳐(101)는 "게이트"이며, 실리콘 영역(112)은 금속 산화물 반도체(MOS) 장치를 기판 표면상에 형성하는데 사용되는 "소스 및 드레인 영역"이다. 도 5a에 도시된 구성에서, 투사 전자기 에너지(150)는 표면(102)에 가해져서 기판 표면(102)의 일부 영역이 투사 에너지를 흡수하여 용융 영역(113)을 형성할 수도 있게 한다. 투사 전자기 에너지(150)에 노출되는 다양한 물질의 물리적, 열적 및 광학적 특성은 표면(102)상의 다양한 영역이 전달된 에너지에 노출될 때 용융될 것인가를 결정할 것이다. 피쳐(101)가 폴리실리콘 게이트일 경우, 800 nm 보다 작은 파장에 있는 레이저로부터의 흡수 에너지는 MOS 장치의 소스나 드레인 영역에서 발견되는 것과 같은 N-형 또는 P-형 도핑 실리콘을 함유하는 실리콘 영역(112)에 의해 흡수되는 에너지보다 상당히 적게 될 것이라고 여겨진다. 따라서, 피쳐(101)의 열 용량 및 열적 질량, 그리고 실리콘 영역(112)에 대한 그 상대적 위치에 기인하여, 피쳐(101)에 인접한 영역에 전달된 전자기 에너지(150)는 용융된 영역(113)으로부터 멀어지는 열 확산으로 인해 보다 차갑게 유지될 것이라고 여겨진다. 피쳐(101)에 대한 열 손실은 용융 영역(113)을 형성하기에 유용한 에너지를 감소시키고, 이로써 용융 영역(113)의 깊이 및/또는 부피에 영향을 미칠 것이다. 따라서, 기판 표면상의 패턴 밀도에서의 변화를 감소시키기 위한 방안이 필요하다.

도 5b는 기판(100)의 표면(102) 상에 형성되는 균질화 층(120), 실리콘 영역(112), 및 복수의 피쳐(101)를 갖는 기판(100)의 횡단면도를 도시한다. 도 5b는 균질화 층(120)의 첨가를 제외하고는 도 5a와 유사하다. 일반적으로 균질화 층(120)은 기판(100)의 표면(102)의 열 용량을 더욱 균일하게 하는데 사용된다. 일 실시예에서, 균질화 층(120)을 형성하는 물질 및 두께는 기판 표면을 가로질러 가변적인 질량 밀도의 효과를 감소시키고 이로써 용융 영역(113)의 깊이 및/또는 부피에서의 변화를 감소시키기 위하여 기판 표면의 열 용량을 균형 맞추도록 선택된다. 일반적으로, 균질화 층(120) 물질은 후속되는 어닐링 프로세스 동안 용융되지 않고, 어닐링 프로세스가 수행된 이후에 기판의 표면으로부터 선택적으로 제거될 수 있도록 선택된다. 일 태양에서, 균질화 층(120)은 예를 들어 폴리실리콘 함유 물질과 같은, 피쳐(101)를 형성하는 물질과 구성에 있어서 유사한 물질이다. 다른 태양에서, 균질화 층(120)은 탄화실리콘 함유 물질 또는 금속(예를 들어, 티타늄, 질화티타늄, 탄탈, 텅스텐)이다.

바람직하게는, 장치 구조의 열 용량이 균일하게 되도록 균질화 층(120)의 두께(예를 들어, d1)가 선택된다. 일 태양에서, 균질화 층(120)의 두께(d1)는 다음 식에 따라 결정된다:

d1 = (α1)0.5 ×[d2/((α)0.5)]

여기서,

d2 = 피쳐(101)의 두께 (도 5b 참조)

α1 = κ1/(ρ1Cp1) 그리고

α2 = κ2/(ρ2Cp2)

여기서 κ1은 균질화 층을 형성하는데 사용되는 물질의 열 전도성과 같고, ρ1은 균질화 층(120)을 형성하는데 사용되는 물질의 질량 밀도와 같고, Cp1은 균질화 층(120)을 형성하는데 사용되는 물질의 열 용량과 같고, κ2은 피쳐(101)를 형성하는데 사용되는 물질의 열 전도성과 같고, ρ2은 피쳐(101)를 형성하는데 사용되는 물질의 질량 밀도와 같고, Cp2은 피쳐(101)를 형성하는데 사용되는 물질의 열 용량과 같다.

도 6a는 기판(100)의 표면(102) 상에 균질화 층(120)을 형성하는데 사용될 수 있는 일련의 방법 단계들을 도시한다. 도 6a 및 6b에 도시된, 단계(190)에서, 화학적 기상 증착(CVD), 플라스마 강화 CVD, 원자층 증착(ALD), 플라스마 강화 ALD, 또는 스핀 코팅(spin coating) 유형의 증착 프로세스와 같은 종래의 증착 프로세스를 이용하여 기판(100)의 표면(102)(예를 들어 피쳐(101)) 위로 균질화 층(120)이 증착된다. 도 6a 및 도 6c에 도시된 단계(192)에서, 균질화 층(120)을 포함하는 기판(100)의 표면(102)이 화학 기계적 연마(CMP) 프로세스를 이용하여 평탄화된다. 도 6a 및 6d에 도시된 단계(194)에서, 이후 희망 두께(d1)가 달성될 때까지 습식 식각 또는 건식 식각 유형의 프로세스와 같은 선택적 물질 제거 프로세스를 사용하여 균질화 층이 선택적으로 식각된다. 그 다음, 용융 영역(113)에 함유된 물질의 균일한 어닐링/용융을 야기하도록 일정량의 투사 전자기 에너지가 기판 표면의 표면에 전달될 수 있다.

균질층

위의 흡수층 (

Absorption

Layer

Over

Homogeneous

Layer

)

도 5c는 기판 표면상의 다양한 영역의 광학 특성을 조정하기 위하여 부가된 층(125)이 상부에 증착되는, 도 5b에 도시된 장치를 포함하는 기판(100)의 횡단면도이다. 일 태양에서, 층(125)이 기판(100)의 다양한 영역에 전달되는 전자기 에너지(150)의 흡수를 향상시키도록 부가된다. 일 실시예에서, 층(125)은 상술한 층(226) 또는 코팅(225)과 동일하다. 도 5c에 도시된 바와 같이, 층(125)은 균질화 층(120) 상에 우선적으로 형성되어 실리콘 영역(112)에 전달되는 에너지의 선택도(selectivity)를 향상시킨다. 층(125)의 희망 두께는 전달된 전자기 에너지(150)의 파장이 변화함에 따라 변화될 수 있다.

도 6a-6g를 참조하면, 일 실시예에서, 단계(190) 내지 단계(194)를 수행한 이후에, 단계(196) 및 단계(198)가 선택적으로 증착된 흡수층(125)을 형성하는데 사용될 수 있다. 도 6e 및 6f에 도시된 단계(196)에서, 층(125)이 상술한 단계(190-194)에서 형성된 균질화 층(120) 및 피쳐(101) 위로 증착된다. 도 6e 및 6g에 도시된 단계(198)에서, 화학 기계적 연마(CMP) 프로세스를 사용하여 통상적으로 완료되는 평탄화 프로세스와 같은 물질 제거 단계를 수행함으로써 피쳐(101)의 상부 표면으로부터 층(125)이 제거된다. 일 태양에서, 층(125) 및 균질화 층(120)과 직접 접촉하지 않는 용융 영역 사이의 영역에 비하여 용융 영역(103)에 상이한 양의 열이 흡수되고 전달되도록 함으로써 기판 표면상의 하나 또는 그보다 많은 희망 영역들 사이의 용융점 차이를 변경하기 위해 증착층(125)이 사용된다.

회절

격자 (

Diffraction

Grating

)

상이한 크기, 형태 및 분리된 거리의 피쳐가 전자기 복사선에 노출될 때 발생하는 한가지 문제점은 전자기 복사선의 파장에 따라서 피쳐에 가해지는 에너지의 양이, 희망 영역으로 전달되는 에너지의 양, 또는 에너지 밀도(예를 들어, Watts/m2)을 바람직하지 않게 변화시키는 회절 효과로 인해 보강 또는 상쇄 간섭(constructive or destructive interference)을 받을 수 있다는 것이다. 도 7을 참조하면, 피쳐(101)의 간격은 투사 복사선의 파장이 표면에 걸쳐 변화하여 기판(100)의 표면(102)을 가로질러 전달되는 에너지 밀도에서의 변화를 야기하도록 상이할 수 있다.

도 7에 도시된 바와 같이, 일 실시예에서, 층(726)은 모든 피쳐(101)의 높이를 초과하는 두께로 성장하여 기판의 표면상에 형성되는 장치(예를 들어 피쳐(101)) 사이의 불규칙한 간격에 의해 형성되는 회절 효과를 감소시킨다. 도시되지 않은 일 태양에서, 층(726)의 표면(720)이 더욱 평탄화되어(예를 들어 CMP 프로세스) 기판(10)의 표면(720)에서의 임의의 본질적으로 지형적인(topographical) 변화를 감소시킨다. 일반적으로, 어닐링 프로세스 동안 전달되는 에너지의 파장의 약 1/4보다 작은(< 1/4λ) 기판 표면을 가로지르는 최고점으로부터 최저점으로의(peak-to-valley) 변화(도 7의 "PV" 참조)를 갖도록 기판 표면상에서의 지형적인 변화를 감소시키는 것이 바람직하다. 또한, 어닐링 프로세스 동안에 전달되는 에너지 파장의 약 5배보다 큰(예를 들어, > 5λ), 기판 표면을 가로지르는 최고점 사이의 평균 주기(도 7의 "PP" 참조)를 갖는 것도 바람직하다. 일 예시에서, 800 nm 파장의 레이저 공급원을 사용할 때, 약 4000 nm 보다 큰 최고점 변화 사이의 주기 및 약 200 nm 보다 작은 최고점으로부터 최저점까지의 변화로 표면(720) 내의 본질적으로 지형적인 변화를 감소시키는 것이 바람직하다. 일 태양에서, 층(726)은 CVD 증착 프로세스에 의해 증착된 탄소층이거나 상술한 층(125), 코팅(225), 및 층(226)과 함께 설명되는 물질이다.

일 실시예에서, 투사 전자기 복사선에 노출되는 기판의 표면상에 형성되는 장치의 구성은 상이한 구역 사이의 용융점 차이를 향상시키기 위해 희망 회절 패턴이 형성되도록 구체적으로 구성되고 배치된다. 따라서 다양한 피쳐의 물리적 배치는 기판 표면을 어닐링하는데 사용되는 투사 복사선 "B"(도 7)의 희망 파장, 또는 파장들에 대해 조절된다.

기판 내의 비정질 영역 형성

일 실시예에서, 후속되는 임플란트(implantation) 프로세싱 단계 동안에 형성되는 손상의 양을 감소시키고 기판의 다른 영역에 대하여 비정질 영역(140)의 용융점 차이를 증가시키기 위하여 최초의 단결정 또는 다결정 물질에 비정질 영역(140)을 선택적으로 형성하도록 하나 또는 그보다 많은 프로세싱 단계가 수행된다. 비정질 실리콘 층과 같은, 비정질 영역으로 불순물을 임플란트하는 것은 결정 격자 구조(예를 들어, 단결정 실리콘)에서 발견되는 다양한 평면을 가로지르는 밀도 변화의 결함으로 인하여, 고정된 이온 에너지에서 희망 불순물의 임플란트 깊이를 균질화하는 경향이 있을 것이다. 비정질 층에서의 임플란트는 결정 구조 내의 종래의(traditional) 임플란트 프로세스에서 흔히 발견되는 결정 손상을 감소시키는 경향이 있을 것이다. 따라서, 비정질 영역(140)이 상술한 바와 같이 어닐링 유형 프로세스를 사용하여 후속적으로 재용융되면, 형성된 영역은 보다 균질한 도핑 프로파일 및 감소된 결함 수를 가지며 재결정화될 수 있다. 또한 재용융 프로세스는 임플란트 프로세스로부터 형성되는 임의의 손상을 제거한다. 또한 비정질 영역(140)의 형성은 영향받은 영역의 용융점도 감소시킬 것이며, 이로써 비정질 영역(140) 및 인접한 단결정 영역(141) 사이의 용융점 차이를 향상시킬 수 있다.

일 실시예에서, 희망 영역(예를 들어 비정질 영역(140))에 비정질 실리콘 층을 선택적으로 수정하고 형성하기 위하여 기판(10)에 짧은 에너지 조사(dose)(도 8의 "B")가 전달된다. 일 태양에서, 기판 내에 비정질 영역을 생성하도록 영향받은 비정질 영역(140)의 신속한 용융 및 냉각을 야기하기에 충분히 짧은 시간 주기 동안 희망 영역에 전자기 에너지의 펄스, 또는 조사(dose)가 전달된다. 이러한 경우에, 에너지 펄스는 비정질 영역을 생성하기 위해 가열된 영역에서 높은 재성장 속도를 생성하는 그러한 짧은 지속기간을 갖는다. 일 태양에서, 가열된 영역에서의 재성장 속도는 약 12m/sec 보다 크다.

일 태양에서, 에너지 펄스가 약 10-8 초보다 작은 주기 동안 실리콘 기판의 희망 영역에 전달된다. 이러한 태양에서, 약 10-8 초보다 작은 주기 동안 약 109 W/cm2 보다 더 큰, 그리고 바람직하게는 약 109 내지 약 1010 W/cm2 사이의 최고 전력을 전달하는 레이저로부터 에너지 펄스가 전달될 수 있다. 일 태양에서, 비정질 실리콘 층을 형성하기 위하여 전달된 조사(dose)의 전력, 펄스 지속기간, 형태는 희망 크기, 형태 및 깊이의 비정질 영역(140)을 달성하도록 변화될 수 있다. 일 태양에서, 전달된 에너지 조사의 파장은 희망 용융 프로파일을 달성하기 위해 선택되거나 변화된다. 일 태양에서, 파장은 UV 또는 IR 파장 내에 있을 수 있다. 일 태양에서는, 레이저의 파장이 약 800 nm 보다 작을 수 있다. 다른 태양에서, 파장이 약 532 nm 또는 약 193 nm 일 수 있다.

일 실시예에서, 기판 표면의 다양한 영역에 비정질 영역을 우선적으로 형성하기 위해 마스크가 사용된다.

전자기 복사선 전달

도 9는 어닐링 영역(12) 내의 특정 희망 영역을 우선적으로 용융시키기 위하여 후측 표면(901)으로부터 기판(10)의 어닐링 영역(12)에 일정량의 에너지를 전달하도록 에너지원(20)이 구성되는 일 실시예를 도시하는 프로세싱 챔버 영역의 횡단면도이다. 일 태양에서, 어닐링 영역(12)과 같은 기판의 하나 또는 그보다 많은 한정된 영역이 임의의 주어진 시간에서 에너지원(20)으로부터의 복사선에 노출된다. 일 태양에서, 기판(10)의 복수의 영역이 에너지원(20)으로부터 후측 표면(901)을 통해 전달되는 희망 양의 에너지에 순차적으로 노출되어 기판의 희망 영역의 우선적인 용융을 야기한다. 일 태양에서, 어닐링 영역(12)은 기판(10)의 상부 표면(902) 상에 형성되는 다이(예를 들어 도 1의 도면부호 13), 또는 반도체 장치의 크기에 맞도록 크기가 정해진다. 일 태양에서는, 어닐링 영역(12)의 경계가 각각의 다이의 경계를 한정하는 "커프(kurf)" 또는 "스크라이브(scribe)" 라인 내에 들어맞도록 정렬되고 크기가 정해진다. 따라서, 에너지원(20)으로부터의 에너지에 대한 노출량의 변화에 기인하는 프로세스 변화의 양이 최소화되는데, 이는 순차적으로 배치된 어닐링 영역(12) 사이의 임의의 중첩이 최소화될 수 있기 때문이다. 일 예시에서는, 어닐링 영역(12)이 약 22 mm × 약 33 mm 크기의 직사각형 영역이다.

일 실시예에서, 기판(10)은 기판(10)의 후측 표면(901)이 에너지원(20)으로부터 전달되는 에너지를 수용하도록 하는 개구(912)를 갖는 기판 지지부(910) 상에 형성되는 기판 지지 영역(911)에 위치한다. 이러한 구성에서, 복사선 "B"은 방출된 에너지의 일부를 흡수하도록 구성된 영역(903)을 가열하도록 에너지원(20)으로부터 방출된다. 에너지원(20)은 일반적으로 기판 표면의 특정 희망영역을 우선적으로 용융시키기 위하여 전자기 에너지를 전달하도록 구성된다. 전자기 에너지의 통상적인 공급원은, 이에 제한되는 것은 아니지만, 광학 복사선 공급원(예를 들어, 레이저), 전자 빔 공급원, 이온 빔 공급원, 및/또는 마이크로파 에너지 공급원을 포함한다. 일 태양에서, 기판(10)은 희망 시간 주기 동안 하나 또는 그보다 많은 적절한 파장에서 복사선을 방출하는 레이저로부터의 에너지 펄스에 노출된다. 일 태양에서, 에너지원(20)으로부터의 에너지 펄스는 어닐링 영역(12)을 가로질러 전달된 에너지의 양 및/또는 펄스의 주기에 걸쳐 전달된 에너지의 양이 특정 희망 영역의 우선적인 용융을 강화시키기에 최적화되도록 조절된다. 일 태양에서, 레이저의 파장은 복사선의 상당한 부분이 기판(10) 상에 배치되는 실리콘 층에 의하여 흡수되도록 동조(tune)된다. 실리콘 함유 기판 상에서 수행되는 레이저 어닐링 프로세스에 있어서, 복사선의 파장은 통상적으로 약 800 nm 보다 작으며, 강한 자외선(UV), 적외선(IR) 또는 다른 희망 파장에서 전달될 수 있다. 어느 경우에서건, 어닐링 프로세스는 일반적으로 약 1초 또는 그 미만 정도와 같은 비교적 짧은 시간 동안에 기판의 주어진 영역 상에서 이루어진다.

일 태양에서, 에너지원(20)으로부터 방출된 복사선의 파장은 기판을 형성하는 벌크 물질이 투사 방출된 복사선의 노출에 의하여 우선적으로 용융될 상부 표면(902) 근방의 영역보다 투사 복사선을 보다 잘 투과하도록 선택된다. 일 태양에서, 우선적으로 용융될 영역은, 임플란트 프로세스 동안에 형성되는 불순물 물질 또는 이온화 결정 손상(예를 들어, 결정 결함, 프랭클 결함(Frenkel defects), 공극(vacancies))과 같은, 기판의 후측을 통해 전달되는 일정량의 에너지를 흡수하는 물질을 함유한다. 일반적으로 불순물 물질은 반도체 프로세싱에서 사용되는 붕소, 인, 또는 다른 흔히 이용되는 불순물 물질일 수 있다. 일 실시예에서, 기판을 형성하는 벌크 물질은 실리콘 함유 물질이며 방출된 복사선의 파장은 약 1마이크로미터보다 크다. 다른 태양에서, 에너지원(20)은 9.4 내지 10.6 마이크로미터 주위로 센터링되는 주 파장 대역(principal wavelength bands)을 방출하도록 구성되는 CO2 레이저를 포함한다. 또 다른 태양에서, 에너지원(20)이 적외선 영역에서의 파장을 전달하도록 구성되는데, 이는 일반적으로 약 750 nm 내지 약 1 mm에 위치한다.

일 실시예에서, 기판(10) 상의 어닐링 영역(12) 위에 흡수 코팅(도시되지 않음)이 배치되어 기판의 후방을 통해 전달되는 투사 복사선이 기판을 통과하기 전에 흡수될 수 있다. 일 태양에서, 흡수 코팅이 티타늄, 질화 티타늄, 탄탈, 또는 다른 적절한 금속 물질과 같은 금속이다. 다른 태양에서, 흡수 코팅이 탄화 실리콘 물질, 비정질 탄소 물질, 또는 반도체 장치 제조에서 흔히 이용되는 다른 적절한 물질이다.

일 실시예에서, 광선의 두 개의 파장이 기판의 희망 영역에 전달되어 광선의 제1 파장이 희망 어닐링 영역에서 발견되는 다른 이온화 결정 손상이나 불순물로부터 기판 내에 자유 캐리어(free carriers)(예를 들어, 전자 또는 홀)를 생성하는데 사용되고, 이로써 생성된 자유 캐리어는 제2 파장에서 기판의 후방을 통해 전달되는 에너지를 흡수할 것이다. 일 태양에서, 제1 파장은 "녹색 광선"의 파장(예를 들어 약 490 nm 내지 약 570 nm) 및/또는 보다 짧은 파장이다. 일 실시예에서, 제1 파장은, 도 9에 도시된 바와 같이, 에너지원(20)으로부터 기판의 반대측 상에 위치하는 제2 공급원(920)으로부터 기판의 희망 영역에 바람직한 전력 밀도(W/cm2)에서 전달된다. 다른 실시예에서, 두 개의 파장(예를 들어, 제1 및 제2 파장)이 에너지원(20)으로부터 기판의 후측을 통해 전달된다. 또 다른 실시예에서, 바람직한 전력 밀도(W/cm2)에 있는 두 개의 파장(예를 들어 제1 및 제2 파장)이 두 개의 독립된 전자기 에너지 공급원(도시되지 않음)으로부터 기판의 후측을 통해 전달된다.

전술한 설명은 본원발명의 실시예에 관한 것이지만, 다른 또는 추가적인 본원발명의 실시예도 본원발명의 기본 사상으로부터 벗어나지 않고도 창안될 수 있으며, 그 범위는 이하의 청구범위에 의하여 결정된다.

Claims (16)

- 기판을 수용하기 위한 기판 지지 표면을 구비하는 기판 지지부;

상기 기판 지지부 내에 형성되는 하나 또는 그보다 많은 냉각 채널;

상기 기판의 전방 표면으로부터 처리 영역으로 제1 광 파장에 있는 제1 양의 에너지를 전달하도록 구성되는 제1 광원;

상기 기판의 후방 표면으로부터 상기 처리 영역으로 제2 양의 에너지를 전달하도록 구성되는 제2 광원; 및

제어기;

를 포함하는 열적 프로세싱 장치로서,

상기 기판의 후방 표면은 전방 표면의 맞은 편(opposite)에 있고, 상기 제 2 광원은 상기 제1 광 파장보다 긴 제2 광 파장에 있는 에너지를 제공하며,

상기 기판 지지부는 내부에 상기 기판 지지부를 20℃ 내지 600℃의 온도로 가열하는 가열 부재를 포함하고,

상기 냉각 채널은 열 교환 유체를 수용하여 상기 기판 지지부를 -240℃ 내지 20℃의 온도로 냉각하며,

상기 제어기는 상기 처리 영역으로 전달되는 상기 제1 양의 에너지를 모니터하고, 상기 처리 영역의 온도에 기초하여 상기 제2 양의 에너지의 크기 및 상기 제1 양과 제2 양의 에너지의 전달 시간을 독립적으로 제어하도록 구성되는,

열적 프로세싱 장치.

- 삭제

- 제1항에 있어서,

상기 처리 영역이 4 mm2 내지 1000 mm2의 면적을 갖는,

열적 프로세싱 장치.

- 삭제

- 삭제

- 제1항에 있어서,

상기 제1 및 제2 광원이 500 nm 내지 11 마이크로미터의 파장에 있는 복사선을 전달하도록 구성되는,

열적 프로세싱 장치.

- 반도체 기판을 수용하기 위한 기판 지지 표면을 갖는 기판 지지부로서, 개구가 형성된 기판 지지부;

상기 기판 지지부 내에 형성되는 하나 또는 그보다 많은 냉각 채널; 및

제1 광원; 및

제2 광원; 을 포함하는 반도체 기판의 열적 프로세싱 장치로서,

상기 기판 지지부는 내부에 상기 기판 지지부를 20℃ 내지 600℃의 온도로 가열하는 가열 부재를 포함하고,

상기 냉각 채널은 열 교환 유체를 수용하여 상기 기판 지지부를 -240℃ 내지 20℃의 온도로 냉각하며,

상기 제1 광원은 상기 기판 지지부 내에 형성된 상기 개구를 통해 상기 기판의 전방 표면 상의 상기 기판의 제1 면적으로 일정량의 복사선을 전달하도록 구성되며,

상기 일정량의 복사선은 상기 제1 면적 내에 포함된 영역을 용융시키도록 구성되고,

상기 제2 광원은 상기 기판의 전방 표면의 맞은 편에 있는 상기 기판의 배면(rear surface)으로부터 상기 기판의 제1 면적으로 희망 파장에 있는 일정량의 전자기 복사선을 전달하도록 구성되는,

반도체 기판의 열적 프로세싱 장치.

- 제7항에 있어서,

상기 제1 광원이 1 마이크로미터보다 더 큰 파장에 있는 복사선을 전달하도록 구성되는,

반도체 기판의 열적 프로세싱 장치.

- 제7항에 있어서,

상기 제1 광원이 500 nm 내지 11 마이크로미터의 파장에 있는 복사선을 전달하도록 구성되는,

반도체 기판의 열적 프로세싱 장치.

- 제7항에 있어서,

상기 제1 면적이 4 mm2 내지 1000 mm2인,

반도체 기판의 열적 프로세싱 장치.

- 제7항에 있어서,

상기 기판 지지부에 부착되는 스테이지를 더 포함하고,

상기 스테이지가 상기 기판 지지 표면에 평행한 하나 이상의 방향으로 상기 기판을 위치시키도록 구성되는,

반도체 기판의 열적 프로세싱 장치.

- 삭제

- 제7항에 있어서,

상기 제2 광원이 590 nm 보다 더 작은 파장에 있는 전자기 복사선을 상기 제1 면적으로 전달하도록 구성되는,

반도체 기판의 열적 프로세싱 장치.

- 제7항에 있어서,

상기 제2 광원이 상기 기판의 전방 표면에 인접하는,

반도체 기판의 열적 프로세싱 장치.

- 삭제

- 제1항에 있어서,

상기 제1 양의 에너지는 상기 기판 내의 처리 영역을 용융시키도록 선택되는,

열적 프로세싱 장치.

Applications Claiming Priority (9)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US78074506P | 2006-03-08 | 2006-03-08 | |

| US60/780,745 | 2006-03-08 | ||

| US11/459,856 US20070212859A1 (en) | 2006-03-08 | 2006-07-25 | Method of thermal processing structures formed on a substrate |

| US11/459,852 US20070221640A1 (en) | 2006-03-08 | 2006-07-25 | Apparatus for thermal processing structures formed on a substrate |

| US11/459,856 | 2006-07-25 | ||

| US11/459,847 | 2006-07-25 | ||

| US11/459,852 | 2006-07-25 | ||

| US11/459,847 US7569463B2 (en) | 2006-03-08 | 2006-07-25 | Method of thermal processing structures formed on a substrate |

| PCT/US2007/062672 WO2007103643A2 (en) | 2006-03-08 | 2007-02-23 | Method and apparatus for thermal processing structures formed on a substrate |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020087024646A Division KR101113533B1 (ko) | 2006-03-08 | 2007-02-23 | 기판상에 형성되는 구조체의 열적 처리를 위한 장치 및 방법 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20100133454A KR20100133454A (ko) | 2010-12-21 |

| KR101323222B1 true KR101323222B1 (ko) | 2013-10-30 |

Family

ID=38475646

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020107024018A KR101323222B1 (ko) | 2006-03-08 | 2007-02-23 | 기판상에 형성되는 구조체의 열적 프로세싱을 위한 장치 및 방법 |

| KR1020087024646A KR101113533B1 (ko) | 2006-03-08 | 2007-02-23 | 기판상에 형성되는 구조체의 열적 처리를 위한 장치 및 방법 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020087024646A KR101113533B1 (ko) | 2006-03-08 | 2007-02-23 | 기판상에 형성되는 구조체의 열적 처리를 위한 장치 및 방법 |

Country Status (4)

| Country | Link |

|---|---|

| EP (1) | EP1992013A2 (ko) |

| JP (1) | JP5558006B2 (ko) |

| KR (2) | KR101323222B1 (ko) |

| WO (1) | WO2007103643A2 (ko) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20090120924A1 (en) * | 2007-11-08 | 2009-05-14 | Stephen Moffatt | Pulse train annealing method and apparatus |

| US9498845B2 (en) | 2007-11-08 | 2016-11-22 | Applied Materials, Inc. | Pulse train annealing method and apparatus |

| US9012315B2 (en) * | 2013-08-09 | 2015-04-21 | Taiwan Semiconductor Manufacturing Company Limited | Methods and systems for dopant activation using microwave radiation |

| KR102216675B1 (ko) * | 2014-06-12 | 2021-02-18 | 삼성디스플레이 주식회사 | 디스플레이 패널의 리페어 장치 및 디스플레이 패널의 리페어 방법 |

| EP3611757A1 (en) * | 2018-08-16 | 2020-02-19 | Laser Systems & Solutions of Europe | Method for forming a doped region on a semiconductor material |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20010074629A (ko) * | 1998-08-27 | 2001-08-04 | 마클 데이빗 에이. | 크기가 축소된 집적 회로의 제조에 사용하기에 적합한가스 주입 레이저 어닐링 방법 |

| US20040188396A1 (en) | 2002-11-06 | 2004-09-30 | Somit Talwar | Laser scanning apparatus and methods for thermal processing |

| US20050087893A1 (en) | 1999-10-25 | 2005-04-28 | Chung Seung-Pil | Method of removing oxide layer and semiconductor manufacturing apparatus for removing oxide layer |

| US20050103998A1 (en) | 2003-09-29 | 2005-05-19 | Somit Talwar | Laser thermal annealing of lightly doped silicon substrates |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5696835A (en) * | 1979-12-29 | 1981-08-05 | Fujitsu Ltd | Manufacture of semiconductor device |

| JPS5727035A (en) * | 1980-07-25 | 1982-02-13 | Hitachi Ltd | Manufacture of semiconductor device |

| GB8515814D0 (en) * | 1985-06-21 | 1985-07-24 | British Telecomm | Fabrication of optical waveguides |

| US4849371A (en) * | 1986-12-22 | 1989-07-18 | Motorola Inc. | Monocrystalline semiconductor buried layers for electrical contacts to semiconductor devices |

| US5182170A (en) * | 1989-09-05 | 1993-01-26 | Board Of Regents, The University Of Texas System | Method of producing parts by selective beam interaction of powder with gas phase reactant |

| JP3326654B2 (ja) * | 1994-05-02 | 2002-09-24 | ソニー株式会社 | 表示用半導体チップの製造方法 |

| KR20000048110A (ko) * | 1998-12-15 | 2000-07-25 | 카네코 히사시 | 고체촬상장치 및 그 제조방법 |

| WO2001082346A1 (fr) * | 2000-04-24 | 2001-11-01 | Beijing Normal University | Procede de fabrication d'un materiau en silicium sur isolant (soi) |

| US6486066B2 (en) * | 2001-02-02 | 2002-11-26 | Matrix Semiconductor, Inc. | Method of generating integrated circuit feature layout for improved chemical mechanical polishing |

| US6902966B2 (en) * | 2001-10-25 | 2005-06-07 | Advanced Micro Devices, Inc. | Low-temperature post-dopant activation process |

| EP1459366A2 (en) * | 2001-11-30 | 2004-09-22 | Koninklijke Philips Electronics N.V. | Method of forming a doped region in a semiconductor body comprising a step of amorphization by irradiation |

| JP2003229568A (ja) * | 2002-02-04 | 2003-08-15 | Hitachi Ltd | 半導体装置の製造方法および半導体装置 |

| JP2004363355A (ja) * | 2003-06-05 | 2004-12-24 | Hitachi Ltd | 半導体装置及びその製造方法 |

| DE60330965D1 (de) * | 2003-10-17 | 2010-03-04 | Imec | Verfahren zur Herstellung eines Halbleitersubstrats mit einer Schichtstruktur von aktivierten Dotierungsstoffen |

| JP4700324B2 (ja) * | 2003-12-25 | 2011-06-15 | シルトロニック・ジャパン株式会社 | 半導体基板の製造方法 |

| CN1947276A (zh) * | 2004-04-27 | 2007-04-11 | 皇家飞利浦电子股份有限公司 | 通过熔融技术制备有机半导体器件的方法 |

-

2007

- 2007-02-23 WO PCT/US2007/062672 patent/WO2007103643A2/en active Application Filing

- 2007-02-23 KR KR1020107024018A patent/KR101323222B1/ko active IP Right Grant

- 2007-02-23 KR KR1020087024646A patent/KR101113533B1/ko not_active IP Right Cessation

- 2007-02-23 EP EP07757396A patent/EP1992013A2/en not_active Withdrawn

- 2007-02-23 JP JP2008558449A patent/JP5558006B2/ja not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20010074629A (ko) * | 1998-08-27 | 2001-08-04 | 마클 데이빗 에이. | 크기가 축소된 집적 회로의 제조에 사용하기에 적합한가스 주입 레이저 어닐링 방법 |

| US20050087893A1 (en) | 1999-10-25 | 2005-04-28 | Chung Seung-Pil | Method of removing oxide layer and semiconductor manufacturing apparatus for removing oxide layer |