KR100887893B1 - 새로운 agc 트랜스임피던스 증폭기 - Google Patents

새로운 agc 트랜스임피던스 증폭기 Download PDFInfo

- Publication number

- KR100887893B1 KR100887893B1 KR1020010075633A KR20010075633A KR100887893B1 KR 100887893 B1 KR100887893 B1 KR 100887893B1 KR 1020010075633 A KR1020010075633 A KR 1020010075633A KR 20010075633 A KR20010075633 A KR 20010075633A KR 100887893 B1 KR100887893 B1 KR 100887893B1

- Authority

- KR

- South Korea

- Prior art keywords

- gain

- current

- gain stage

- voltage

- amplifier

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45076—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier

- H03F3/4508—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier using bipolar transistors as the active amplifying circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03G—CONTROL OF AMPLIFICATION

- H03G3/00—Gain control in amplifiers or frequency changers without distortion of the input signal

- H03G3/20—Automatic control

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45394—Indexing scheme relating to differential amplifiers the AAC of the dif amp comprising FETs whose sources are not coupled, i.e. the AAC being a pseudo-differential amplifier

Abstract

입력과 출력 사이의 극 비율 (pole ratio)이 안정되도록 증폭기의 이득 제어 저항을 조정하고 출력 전류를 조정하는데 이득 보상 기술을 사용함으로서 넓은 동적 범위와 안정성이 이루어진다. 이득의 조정은 이득 스테이지와 입력 전압을 증폭하지 않은 더미 이득 스테이지 증폭기 (dummy gain stage amplifier) 사이의 피크 전압을 결정함으로서 실행된다. 피크 전압은 이득 제어 기준 전압에 비교되고, 비교 출력은 가변 이득과 이득 보상 모두를 조절하는데 사용된다. 가변 이득은 증폭기의 피드백 루프 (feedback loop)에서 FET 가변 저항기를 사용하여 실행된다. 이득 보상 기술은 전류 미러 (current mirror)의 입력에 제공되는 전류량을 조정하는 구동 트랜지스터의 전압 레벨을 조정하는데 FET 가변 저항기를 사용한다. 미러 전류(mirrored current)는 이어서 증폭기로부터 바이어스 (bias) 전류를 유출하는데 사용된다.

전류 미러, 더미, 이득, 피드백 루프

Description

도 1a는 동적 이득을 증가시키는데 전형적인 분류 피드백 네트워크 (shunt feedback network)를 사용하는 전형적인 증폭기 회로의 블록도.

도 1b는 증폭기를 안정화시키기 위한 알려진 FET 배열의 회로도.

도 2는 더 넓은 동적 범위를 이루도록 회로의 전체적인 이득을 변화시키는 또 다른 알려진 증폭기 회로의 블록도.

도 3은 증폭기의 동적 범위를 증가시키기 위한 특정한 실시의 회로도.

도 4는 반도체 트랜스듀서 (transducer) 입력 회로의 주요 임피던스들에 대한 회로 모델도.

도 5는 이득 스테이지 (트랜지스터 및 Rc) 및 피드백 저항기(Rf)의 출력을 구동하는 단위 이득 전압 버퍼를 갖는 전치증폭기 (preamplifier)의 회로도.

도 6은 클램핑 (clamping)에 의해 발생된 왜곡을 설명하는 그래프.

도 7은 트라이오드 (triode)와 포화 영역들 사이의 분할을 도시한 FET 특성을 설명하는 그래프.

도 8은 본 발명의 실시예를 구현한 회로도.

도 9는 극 비율 (pole ratio)에 영향을 주는 인자들 및 극 비율의 그래프.

도 10a는 본 발명의 다른 이득 보상 실시예에 대한 회로 구성성분의 예를 갖는 블록도.

도 10b는 본 발명의 다른 이득 보상 실시예를 구현한 회로도.

도 11은 도 5에 도시된 종래 기술에 대한 fin:fout 극 비율, 바람직한 실시예에 대한 극 비율, 및 제 1의 다른 이득 보상 실시예에 대한 극 비율을 비교하는 그래프.

도 12는 도 5에 도시된 종래 기술에 대한 입력 증폭의 두 극단들(extremes)에서 과도 파형들을 도시하는 그래프.

도 13은 바람직한 실시예 대한 입력 진폭의 똑같은 두 극단들에서 과도 파형들을 도시하는 그래프.

도 14는 제 1의 다른 이득 보상 실시예에 대한 입력 진폭의 똑같은 두 극단들에서 과도 파형들을 도시하는 그래프.

* 도면의 주요부분에 대한 부호의 설명 *

100 : 이득 스테이지 110 : 버퍼 스테이지

120 : 분류 피드백 200 : 버퍼 스테이지

800 : 더미 이득 스테이지 1084 : 증폭기

본 발명은 전체적으로 참조문헌으로써 본 명세서에 포함되는 다음의 계류중 인 미국 예비 특허 출원의 우선권을 주장한다:

Chatwin, 예비 출원 일련 번호 제 60/250,611호, "새로운 AGC 트랜스임피던스 증폭기 (A Novel AGC Transimpedance Amplifier)", attorney docket no. SONY-10900, 2000년 12월 1일 출원.

본 발명은 전자 회로 증폭기들에 관한 것이다. 본 발명은 특히 안정성을 유지하면서 증폭기들의 동적 범위를 증가시키는 것에 관한 것이다. 본 발명은 많은 종류의 회로들, 특히 광학 트랜스듀서 (optical transducer) 내에서 유용하다.

많은 종류의 전기 회로들은 입력 신호들을 수신하고, 이들 신호들을 또 다른 포맷으로 변환한다 (예를 들면, 광학적인 것에서 전기적, 레벨 변환들 등). 전형적인 광학 저장 장치 또는 전송 채널은 수신기에서 더 처리될 수 있도록 데이터 변조된 광을 대응하는 전기 신호로 변환하는데 일부 형태의 광학 대 전기 시스템을 사용할 수 있다. 한 종류의 변환 시스템은 전류 흐름이 이에 빛을 조사함으로서 변조되어 수신기로 출력되는 반도체 트랜스듀서를 사용한다. 그러나, 출력 전류 진폭이 너무 작아서 수신기에 데이터 회복 회로를 포함한 회로들에 유용하게 직접 인가될 수 없으므로, 일정 형태의 증폭이 실행되어야 한다. 출력 전류 진폭은 많은 인자들에 의존한다. 한가지 중요한 인자는 트랜스듀서에 입사되는 광진폭이다. 입사광은 전송 광의 크기, 광전송기와 수신 트랜스듀서 사이의 거리와 같은 인자에 의존하여 임의의 진폭이 될 수 있다. 그러나, 전형적인 증폭기는 회로들에 인가될 모든 출력 신호들을 증폭하기 위해 요구되는 동적 범위가 부족하다.

실시예가 도 1a에 도시된 실시예인 미국 특허 제 5,532,471호는 이러한 증폭 요구조건들을 해결하도록 시도하는 것이다. 공통 이미터 이득 스테이지(100)는 입력으로의 분류 피드백 네트워크 (shunt feedback network; 120)를 구동시키도록 전압 버퍼(110)에 이어진다. 피드백 네트워크(120)는 가변 저항기 FET 디바이스와 병렬로 고정된 저항기를 포함한다. 피드백 네트워크의 유효 저항은 출력 신호의 평균 진폭에 의해 제어되는데, 그 목적은 동적 범위를 증가시키기 위한 것이다.

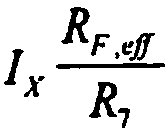

이러한 실시는 넓은 동적 범위를 이루지만, 복잡해진다. 증폭기(2)를 안정화시키기 위해, 추가 FET들이 피드백 저항기를 트래킹(tracking)하는데 사용된다. 하나는 다음의 비율이 최소 2.75 이상으로 보장될 수 있도록 Rc를 줄이는데 사용된다.

다른 FET는 오픈 루프(open loop) 증폭기 이득 "a"를 더 감소시킴으로써 극 주파수 비율을 더 증가시키도록 이득 스테이지를 점차적으로 변질시키는데 사용된다. 추가 회로 복잡성은 도 1b에서 설명되고, 추가 반전 소자(118)에 대한 요구에서 그 자체를 명확히 나타낸다. (106)에 의해 발생되는 증가적인 이미터 변질은 입력 전압이 더 높은 입력 증폭으로 증가되게 한다. 이는 더 큰 전압이 합성 이미터 저항 (104, 106)을 통해 강하(drop)되므로 트랜스듀서에서 역바이어스 전압을 감소시킨다.

미국 특허 5,737,111은 도 1a 및 도 1b와 유사하게, 피드백 저항기를 구동시키는 전압 버퍼 스테이지로 이어지는 똑같은 CE 이득 스테이지를 사용한다. 그러 나, 더 큰 입력 신호를 수용하기 위해, 이는 신호 진폭을 클램프(clamp) 처리하도록 피드백 저항기에 걸쳐 일부 형태의 제한 다이오드를 갖는다. 클램핑 메카니즘에 의해 주어지는 신호 왜곡을 극복하기 위해, 임의의 진폭 한계값이 교차될 때 더 큰 증폭 전류 입력 신호로부터 DC 전류를 감산함으로서, DC 회복 메카니즘이 주어진다.

Meyer et al., IEEE Journal of Solid State Circuits, vol. 29, No. 6, 1994년 6월, 페이지 701, "광대역 저잡음 가변-이득 BiCMOS 트랜스임피던스 증폭기 (A Wideband Low-Noise Variable-Gain BiCMOS Transimpedence Amplifier)"는 보다 복잡한 실시이다. 도 2에 도시된 바와 같이, 전압 버퍼 스테이지(200)는 이득 스테이지(210)에 선행되고, 이는 넓은 동적 범위를 수용하도록 전체적인 이득을 변화시키는 설비를 갖는다. 그러나, 이는 주요 피드백 저항기(230)를 트래킹하는 가변 저항기로 4개의 FET를 사용하여 이루어진다.

특히, 도 3에 대해, Meyer에서, 주요 피드백 소자는 Rc이다. RD는 대역폭을 제어하고 입력 및 출력 극 사이의 분리를 유지함으로서 안전성을 보장하도록 Rc를 트래킹한다. RA는 입력 달링톤(input darlington)의 gm - 즉, 루프 이득 -을 더 감소시키는 국부적인 분기이다. RB는 입력 gm 스테이지를 변질시킴으로서 증폭기의 입력에서 큰 신호 처리 기능을 증가시키고 스테이지 gm을 감소시켜 RA와 유사한 목적을 이룬다.

마지막 가변 저항기 RE는 출력 스테이지의 차동 이득을 감소시킴으로서 출력 신호를 더 감쇠시키는데 사용된다.

Khoman Phang et al., IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, Vol. 46, No. 7, 1999년 7월 "무선 적외선 통신을 위한 CMOS 광학적 전치증폭기 (A CMOS Optical Preamplifier for Wireless Infrared Communications)"에서, 가변 이득 접근법이 사용된다. 이 접근법은 차동 구성으로 연결된 2개의 직렬 공통 소스 이득 스테이지를 포함한다.

IEEE Journal of Solid State Circuits, vol. 35, No. 9, 2000년 9월, 페이지 1260, "40-Gb/s 광섬유 TDM 링크에서 수신기를 위한 InP-기반의 HBT 기술에서의 고이득 트랜스임피던스 증폭기 (High-Gain Transimpedance Amplifier in InP-Based HBT Technology for the Receiver in 40-Gb/s Optical-Fiber TDM Links)", Jens Mullirich는 Phang와 유사한 접근법을 설명한다. 차동 증폭기를 갖고, 가변 이득 제어를 가지지 않지만, 평균 신호 검출기가 있다. 이때, 발생된 평균 전압 신호는 바이어스 전압으로 반대 증폭기 입력에 인가된다.

상기 해결법 각각은 광학 트랜스듀서와 같은 응용에 대해 더 넓은 동적 범위를 제공한다. 그러나, 상이한 회로는 비용을 증가시킬 뿐만 아니라 대역폭과 잡음 사이의 최적 교환을 감소할 정도의 복잡성을 갖는다.

본 발명자는 안정성을 나타내는 저비용 광역 동적 범위의 증폭기에 대한 필 요성을 실현하였다. 본 발명은 입력 및 출력 사이의 극 비율 (pole ratio)이 안정되도록 증폭기의 이득 제어 저항을 조정하고 이득 스테이지 바이어스 전류 및 스테이지 이득을 감소시키는데 이득 보상 기술을 사용함으로서 광역 동적 범위 및 안정성을 갖는 증폭기를 제공한다.

본 발명은 자동 이득 제어(automatic gain control, AGC) 회로로 실현되고, 이는 AGC 회로의 입력에 연결된 이득 스테이지 증폭기, 및 이득 스테이지 증폭기에 연결되고 이득 스테이지 증폭기의 이득을 변화시키도록 구성된 이득 제어 메카니즘을 갖는 이득 스테이지; 및 이득 스테이지 증폭기의 출력에 연결되고 이득 스테이지 증폭기의 출력에 기초하여 가변 이득 제어 메카니즘의 이득을 조정하는 전압을 출력하도록 구성된 이득 제어 회로를 구비한다.

본 발명은 자동 이득 제어(AGC) 회로로 실현되고, 이는 이득 스테이지 증폭기의 출력 전압 레벨에 기초하여 이득 스테이지 증폭기의 이득량을 변화시키는 수단; 및 이득 스테이지 증폭기의 출력 전압 레벨에 기초하여 이득 스테이지 증폭기의 바이어스 전류를 줄이는 수단을 구비한다.

본 발명은 또한 이득 스테이지 증폭기에 인가되는 입력의 광역 동적 범위에 걸쳐 이득 스테이지 증폭기의 이득을 제어하는 방법을 포함하고, 이는 이득 스테이지 증폭기의 출력 전압 레벨에 기초하여 이득 스테이지 증폭기의 이득량을 변화시키는 단계, 및 이득 스테이지 증폭기의 출력 전압 레벨에 기초하여 이득 스테이지 증폭기의 바이어스 전류를 줄이는 단계를 구비한다.

이후의 첨부된 도면과 관련한 상세한 설명을 참조하여 본 발명을 더욱 용이 하게 이해할 수 있으므로, 본 발명과 그 수반되는 이점을 보다 완전하게 인식할 수 있을 것이다.

이제는 본 발명에 기초한 기준을 참고로 증폭 회로의 관찰 및 분석이 논의된다. 상기에 기술된 바와 같이, 본 발명은 특히 광학 트랜스듀서 (optical transducer) 디바이스에서의 증폭 열할에 매우 적합하다. 광학 트랜스듀서는 광신호를 수신하고 이를 전류로 변환하여 입력 회로에 인가한다. 입력 회로에 인가된 전류는 너무 작아서 데이터 회복 회로에 유용하게 인가될 수 없으므로, 이들 입력 전류는 증폭될 필요가 있다.

그러나, 광신호가 상당한 강도 변화를 가져 넓은 범위의 입력 전류가 주어질 수 있으므로, 증폭 회로는 수신된 광신호의 강도에 의존하여 광역 동적 범위의 입력 전류를 처리할 수 있을 필요가 있다. 수신된 신호 강도는 예를 들어, 전송기로부터의 거리, 회로 구성성분의 질 등의 함수로 변하게 된다. 대부분의 경우, 수신 시스템은 전송기로부터의 거리를 미리 알지 못하므로, 설계가 입력 신호 강도의 전체 범위를 수용하도록 탄력성을 갖는 것이 중요하다.

쇼트키 다이오드(schottky diode)로 전압 출력을 클램핑(clamping) 처리하는 것으로부터 이득 제어 회로를 실시하는 것과 같이, 다양한 해결법이 제안되었다. 그러나, 상기에 논의된 바와 같이, 이전에 제안된 해결법은 복잡하거나, 다른 불편한 점이 이상적이지 못한 해결법을 제공하게 된다.

입력 회로의 또 다른 중요한 특성은 낮은 입력 임피던스이다. 반도체 트랜스듀서는 전형적으로 역바이어스 다이오드로, 큰 DC 저항을 갖는다. 반도체 트랜 스듀서와 증폭기 입력 사이의 연결은 대역이 제한된다.

동일한 참고 번호가 동일한 또는 그에 대응하는 부분을 나타내는 도면들을 다시 참고로, 보다 특정하게 도 4를 참고로, 반도체 트랜스듀서 입력 회로(400)의 기본적인 임피던스에 대한 회로 모델이 설명된다. 입력 회로(400)는 반도체 트랜스듀서의 소스 저항 RS(410), 증폭기 입력 임피던스 RIN(420), 또한 트랜스듀서, 상호접속부, 및 증폭기와 연관된 캐패시턴스 CS(430)의 병렬 조합에 의해 결정되는 대역 제한 입력을 갖는다.

입력 회로(400)에서, 트랜스듀서로부터 증폭기 입력까지의 연결에 대한 고주파수 롤 오프 (roll off) 주파수 fIN은 다음의 식으로 결정된다:

이와 같이, 전형적인 값의 CS = 1pF, RS = 200Kohm, 100Kohm의 범위에 있는 RS와 RIN의 병렬 조합에 대해, -3dB 주파수는 1.6MHz의 범위에 있게 된다. 타켓 대역폭이 2GHz인 증폭기에서, 입력 임피던스 RIN는 RIN과 RS의 병렬 조합이 80ohm 정도가 되도록 감소되어야 한다. 그러나, 이 대역폭 개선에 대한 대가로, 증폭기 입력에서는 전압 진폭이 많이 감소된다.

증폭 회로의 또 다른 중요 특성은 모든 조건하에서 안정된다는 것이다. 가변 이득 스테이지로 사용될 때, 증폭기는 모든 입력 진폭 및 이득에서 안정되어야 한다. 증폭기 회로(500)의 실질적인 실시는 이득 스테이지 (트랜지스터(510) 및 RC(520))와, 피드백 저항기 Rf(540)의 출력을 구동하는 단위 이득 전압 버퍼(530)를 갖는 전치증폭기 (preamplifier)의 형태로 도 5에 도시된다. 도 5에서, 피드백 네트워크는 증폭기 폐쇄 루프 이득을 설정하는데 사용된다. 그러나, 이는 또한 루프 이득의 인자 만큼 증폭기의 입력 임피던스 RIN를 감소시킨다. 회로(500)에는 2개의 주파수 극점들(frequency poles)이 존재한다 - 입력에 하나 (fIN) 및 출력에 하나 (fOUT). 회로 입력 저항 RIN (도 5의 RIN과 똑같은)은 다음과 같이 루프 이득에 의해 나누어진 RF로 지배되고:

여기서, Av는 루프 이득이다. 그래서, 입력 극점은 주파수 fIN에서 다음과 같이 주어진다:

출력 극점 fOUT은 이득 스테이지 콜렉터 로드 RC 및 그와 연관된 여진량 CC에 의해 결정된다:

RF의 폭넓은 변화에 걸쳐 안정된 동작을 보장하기 위해, 이 극 비율 fOUT:fIN

은 모든 동적 조건에 걸쳐 2.75 이상이 되어야 한다.

극 비율을 대입하고 이득 스테이지 전압 이득으로 Av = gmRC를 정의함으로서(여기에서 gm은 디바이스(510)의 오픈 루프 이득 스테이지 트랜스컨덕턴스이다), 다음을 얻게 된다:

이는 피드백 RF가 더 큰 입력 신호를 수용하도록 감소되면, 비율 fOUT:fIN이 감소되어 보다 쉽게 불안정해지게 됨을 나타낸다. 특히, RF에서의 5:1의 변화는 극 비율에서의 5:1 변화에 대응하게 된다. 그러므로, fIN = 2GHz 및 5:1의 동적 범위로 설정된 2GHz 최소 대역폭을 갖는 증폭기는 전체 동적 범위에 걸쳐 안정성을 유지하기 위해 fIN 보다 2.75x5배 더 크거나 27.5GHz인 fOUT을 요구한다. 이는 값비싼 처리 및/또는 큰 전력 낭비 및/또는 복잡한 회로 및/또는 다른 주요 매개변수 - 특히 잡음 -에서의 엄격한 교환을 요구한다.

증폭 회로의 또 다른 바람직한 특성은 적어도 잡음 대 신호량을 제시하는 것이다. 낮은 입력 임피던스 요구는 증폭기 입력에서의 전압 진폭이 실질적으로 감쇠되게 한다. 그래서, 20μA 피크-대-피크의 전형적인 입력 전류 진폭 is 및 100ohm의 RIN에 대해, 입력 전압은 2mV 피크-대-피크의 범위에 있게 된다. 이는 이어서 증폭기의 최대 감도를 결정하게 된다. 증폭기에 의해 부가되는 잡음이 작으면 작을수록, 소정의 최소 SNR을 유지하면서 최소 신호 진폭이 더 작아질 수 있으 므로, 대역폭과 감소 사이의 교환예에서 감도가 더 커진다.

바람직하게, 반도체 트랜스듀서에 걸친 최소 DC 바이어스 전압은 적어도 2V일 필요가 있다. 이 증폭기와 사용되는 반도체 광다이오드 (photodiode)는 전형적으로 최소 성능을 위해 역바이어스 전압을 요구한다. 이는 PN 접합의 어느 한측에 공핍 영역이 형성되도록 허용한다. 이는 여진 캐패시턴스 CS를 감소시켜 광다이오드의 고주파수 동작을 증진시키는 효과를 갖는다. 더 큰 역전압에 부가하여, 빛에서 전류로의 변환에 대한 광다이오드의 선형성이 증가된다. 통상적으로, 광다이오드 속도는 역바이어스를 감소시킴에 따라 감소되므로, 최소 역바이어스가 유지되어야 한다.

증폭 회로의 동적 범위는 출력 전압을 제한함으로서 개선될 수 있다. 그러나, 클램프 회로에 의존하여, 증폭 출력 전압을 제한하면, 진폭 왜곡이 일어난다. 도 6을 참고로, 클램핑에 의해 발생되는 왜곡을 설명하는 그래프(600)가 도시된다. 단극성 전류는 병렬 RC를 통해 드롭되어 2Vpp 신호를 생성한다. DC 회복 회로로 실시된 결과의 파형은 "클램핑되지 않은 신호(UNCLAMPED SIGNAL)"(610)라 칭하여져 도시된다. 파형은 대칭적인 상승 및 하강 엣지 (615, 620)를 가짐을 주목한다. 또한, 음과 양의 진폭이 동일하게 반대된다.

RC 네트워크에 걸쳐 일반 다이오드를 적용함으로서, 클램프가 실시되었다. 이는 "클램핑된 신호(CLAMPED SIGNAL)"(630)이라 칭하여진 자취의 감소된 진폭에 의해 나타내질 수 있다. 불행하게도, 이는 상승 및 하강 엣지가 비대칭되게 한다. 즉, 0점 교차점들은 이제 클램핑되지 않은 신호(UMCLAMPED SIGNAL; 610)와 다르고, 펄스는 효과적으로 넓어졌다.

이 펄스폭 또는 듀티 사이클 왜곡(duty cycle distortion)은 바람직하지 못하고 수신기 신호 경로에 문제점을 일으키게 된다. 그러므로, 클램핑이 대칭적으로 실행될 수 없으면, 클램핑이 DC 회복 루프를 포함하더라도, 덜 바람직한 형태의 이득 제어가 유지된다. DC 회복 루프는 긴 시간 주기 (수 천 데이터 비트 정도)에 걸쳐 평균화된 평균 출력 또는 일부 다른 기준 레벨이 0이 되도록 증폭기의 입력에 오프셋을 부가하게 노력한다. 목적은 "0점" 교차와 같이 그 입력이 들어오는 신호의 중간 부분에 중심을 두도록 증폭기에 바이어스 처리하는 것이다.

AGC 제어 루프 구현

다른 이득 제어 메카니즘이 구현될 수 있지만, 본 발명에서는 AGC 증폭기의 이득이 바람직하게 합성 피드백 저항기로 제어된다. 이 합성 저항기는 고정된 저항기와 병렬로 연결된 전계 효과 트랜지스터 (Field Effect Transistor, FET)를 구비한다. 유효 저항은 FET 게이트 단자상의 전압에 의해 제어된다. AGC 제어 루프는 증폭기 출력에서의 진폭이 일부 일정한 기준 레벨에 있도록 제어하게 노력한다. 다른 말로 하면, AGC 루프는 동작할 때 이득을 제어하여 합성 피드백 저항기의 FET 부분에 걸쳐 일정한 피크 Vds를 유지하게 된다.

도 7은 다양한 게이트 전압에 대한 Id/Vds 특성을 도시한다. 낮은 왜곡을 유지하기 위해, FET는 입력 신호의 모든 부분에 대해 트라이오드 모드(triode mode)에 있어야 한다. 입력 신호로 인하여 임의의 부분의 파형에서 Vds가 Vds,sat 보다 더 커지면, 왜곡은 수용될 수 없는 레벨로 갑자기 증가하게 된다. 이와 같이, 아래 곡선을 사용하여, VGS = 1.0V 또는 1.5V와 같이, AGC가 이득을 1.0Vpp로 제한하도록 설정되면, FET는 그 신호 부분에 대해 트라이오드 모드로 동작하고, 다른 부분에 대해서는 포화 모드로 동작하게 된다. 이 왜곡은 두가지 동작 모드에서 매우 다른 채널 저항 특성으로 인하여 주어진다. 이들 VGS의 낮은 값들은 AGC 루프가 막 시작되어 이득에 걸친 제어를 실시할 때 발생된다. 그러므로, 제어 루프가 결코 낮은 값의 VGS로 시작되지 않도록 보장하거나 AGC 기준 진폭을 수십 내지 수백 mV의 매우 작은 Vds로 제한할 필요가 있다.

이득을 제어하는데 평균적인 진폭 기술을 사용하는 AGC 루프에서, AGC 기준 전압은 Vds,sat 선 이하이지만, 아직까지 신호 진폭 일부가 Vds = Vds,sat 선과 교차하여 포화 영역에 들어가는 것이 가능하다. 그러나, 피크 Vds 진폭이 AGC를 제어하는데 사용되는 피크 진폭 기술을 사용하여, 이 효과가 최소화될 수 있다.

상기에 논의된 종래 기술에서, 이전 방법은 다른 크기를 갖는 두 FET의 합성 저항기를 병렬로 만들고 입력 진폭이 증가함에 따라 더 큰 것에 이어서 더 작은 것을 먼저 스위치 온 상태로 함으로서 이 비선형성을 극복한다. 그러나, 이는 복잡한 부품 배열이다.

낮은 잡음, 넓은 대역폭, 및 설계 복잡성

넓은 대역폭과 낮은 잡음은 서로 배타적인 요구조건이다. 이는 특정한 응용에 대해 최적의 협의에 이르도록 다른 것과 거래되어야 한다. 이 최적의 협의는 회로 복잡성, 제작 처리, 및 수개의 다른 인자들에 의존한다. 일반적으로, 신호 경로에 더 많은 구성성분이 있으면, 더 많은 잡음 소스가 주어진다. 부가하여, 이들 추가 구성성분이 피드백 루프의 일부이면, 전체 동작 조건에 걸쳐 안정화될 때 더 큰 어려움을 겪을 수 있다. 간략하게, 잡음과 안정성 모두에 있어서, 덜 복잡한 것이 더 좋다. 예를 들어, Meyer 등을 다시 참고로, 피드백 루프에서 2개의 버퍼 스테이지와 이득 스테이지가 사용되어, 기생 노드들(parasitic nodes)의 수를 증가시키고 회로 설계를 복잡하게 만든다. 유사하게, 5개의 FET는 이득을 제한하고 루프를 안전화시키도록 다양한 제어 기능을 실행한다.

그러나, 본 발명은 회로 복잡성을 줄이고 스테이지를 더 적게 하여 이들 조건을 이룬다. 본 발명은 이상적으로 하나의 이득 스테이지와 가능한한 적은 신호 노드를 갖는 바람직한 옵션을 이루고 전체 이득에 걸쳐 일정한 fOUT:fIN 극 비율에 가깝게 유지함으로서 간단하게 안정화되는 기하형을 설계하도록 노력한다.

트랜스듀서 바이어스 전압

이 특정한 디바이스는 낮은 3V 공급으로 동작하므로, 트랜스듀서에 걸쳐 최소 2V 바이어스를 유지하려면, 입력 단자 전압이 1V를 넘지 말아야 한다. 이는 트랜스듀서가 입력 단자로부터 양의 단자에 연결되도록 허용한다. 입력과 양의 공급 사이의 2V 역바이어스가 유지될 수 없으면, 증폭기 사용자는 트랜스듀서를 바이어스 처리하도록 더 높은 공급 전압을 추가로 제공할 필요가 있다 - 이것은 최적의 해결법이 아니다. 이 1V 입력 단자 전압을 최소 변형으로 유지하기 위해서는 입력 트랜스콘덕터 (transconductor)의 이미터 회로에서 사용되어야 한다.

전체적인 기하형

도 8에는 본 발명의 한 실시예가 도시되고, 이는 예를 들어 입력 트랜지스터(Q1), 피드백 저항(RF1), 및 콜렉터 로드 저항기(RC1)로 구성되고 단자 'in'에서 입력 신호가 인가되는 이득 스테이지(800)로 구성된다. 각각이 공급, 온도, 및 처리 변화에 걸쳐 Q1, RF1, 및 RC1을 따라가는 Q2, RF2, 및 RC2로 구성된 더미 (dummy) 이득 스테이지(820)가 있다. 이득 스테이지 (800, 820)의 출력 신호는 이어서 차동 전압 버퍼(840)를 통해 연결된다. 다이오드 (D1, D2)는 레벨 쉬프터 (level shifter)로 동작한다. 차동 전압 버퍼(840)의 출력에서는 신호가 대칭적인 차동 신호 (out, outb)로 변환된다. 이 신호는 또한 차동 출력 스테이지(844)로 인가되기 이전에 이미터 폴로워 버퍼 (emitter follower buffer; 842)로 더 버퍼 처리된다.

차동 전압 버퍼 출력 신호는 또한 신호의 피크 진폭을 측정하도록 피크 검출기(846)에 인가된다. 신호의 측정된 피크 진폭값은 이어서 기준 전압 VAGC과 비교되고, 증폭기(848)에 의해 증폭되어 게이트 전압(850)을 생성한다. 피크 검출기(846) 및 증폭기(848)의 조합은 이득 제어 회로를 구비한다. 게이트 전압(850)은 가변 저항기들 (802, 822, 832)에 인가된다. 본 실시예에서, 가변 저항기(802)는 피드백 저항기(RF1) 및 FET(M0)의 조합을 구비하는 합성 저항기이다. 가변 저항기(822)는 RF2 및 FET(M1)의 조합이고, 가변 저항기(832)는 RF3와 FET(M3)의 조합이다. 가변 저항기 (802, 822, 832)에서 대응하는 FET (M0, M1, 및 M3)의 게이트에 게이트 전압(850)을 인가하는 것은 전압(VAGC)에 의해 설정된 자동 이득 제어 루프를 실시한다. 피드백은 각 이득 스테이지(800) 및 더미 이득 스테이지(820)에서 M0 및 M1에 의해 각각 조정되고, 이득 보상은 M3에 의해 이득 보상 회로(830)에서 조정된다.

가변 저항기 소자들은 N형 또는 P형 FET가 될 수 있다. 입력 트랜지스터 Q1는 NFET 디바이스로 대치될 수 있다. 부가하여, 회로는 예정되고 P형 디바이스가 Q1 대신에 사용될 수 있다. 본 설명에 기초하여, 당업자는 다양한 다른 부분을 대치하여 유사한 결과를 만들 수 있고, 이는 본 발명의 의도 및 범위에서 벗어나지 않는다.

제 1 스테이지 안정성

이제는 상세한 내용을 논의하여 제 1 스테이지 AC 특성 및 안정성을 계산한다. 입력 트랜지스터(Q1)의 트랜스콘덕턴스 (transconductance)(gm)는 포워드 (forward) 신호 경로이다. 신호 전류는 M0 및 RF1의 피드백 저항기 병렬 조합을 통해 Q1의 콜렉터로 흐른다. 그러므로, 신호 전류 진폭이 바이어싱 콜렉터 전류(IB)와 비교할 만할 때, Q1의 gm은 변조된다. 그래서, gm은 다음과 같이 표현된다:

AGC 루프는 회로의 출력에 일정한 피크 전압을 유지하도록 노력한다. 피크 전압은 평균 입력 전류의 2배인 것으로 가정된다. 그러므로, RF1 및 M0의 병렬 조합에 의해 발생되는 유효 피드백 저항은 다음과 같이 주어진다:

여기서, VAGC는 AGC 기준 전압이다.

콜렉터 로드 회로에서의 임피던스는 다음과 같이 표현된다:

여기서, RC는 저항기 RC1이다.

이때, 전압 이득은 AV = gmRC,eff로 표현될 수 있다. 그러므로, 입력 저항은 간단히 루프 이득으로 나눈 유효 피드백 저항이다:

결과적으로, 대략적인 제 1 차 측정치의 안전성으로 사용되는 출력 극점에 대한 입력 극점의 주파수 비율은 다음과 같이 표현된다:

괄호안의 항은 결코 4 이하로 가지 않고, gm이 신호 진폭에 따라 변하지 않으면, RC 및 gm의 값은 임의의 값의 RF,eff에 걸친 소정의 CS:CC

캐패 시턴스 비율에서 2.75의 원하는 극 비율 최소치를 수용하도록 변할 수 있다. 그러나, gm은 입력 신호 진폭이 증가됨에 따라 증가되어, 극 비율을 감소시키도록 동작한다.

그러므로, Iin이 Q1 바이어스 전류와 비교할 만 할 때 충분히 높은 극 비율을 유지하고 gm 변화를 보상하도록 추가 제어가 제공된다. 특히, 도 8의 Gm 보상 회로(830)는 바이어스 전류를 Q1으로 감소시키는데 사용되므로, 높은 입력 신호 진폭에서 gm을 감소시킨다.

저항기(R10)는 합성 저항기 (RF3, M3)에 걸친 전압 강하를 설정하는 값 IX의 전류원으로 작용한다. 이 합성 저항기는 대략 똑같은 종류 및 크기이고 단자 전압이 유사할 때 다른 합성 피드백 저항기를 추적한다. Q6은 RF3, M3에 걸친 전압이 R7에 걸쳐지게 하여 Q6을 통한 콜렉터 전류가 대략 임을 결정하도록 연결된다. 저항기(R18)는 또한 유사한 크기의 전류 IX를 R10에 의해 제공되는 전류로 제공하는 간단한 전류원으로 동작한다. 이는 Q6의 콜렉터 전압이 Q6의 베이스와 유사한 경우이다. 그래서, 전류 미러 (current mirror)의 입력으로 전해지는 순 전류는 이다. 이 전류는 Q1 및 Q2의 콜렉터에서 이득 스테이지 및 더미 스테이지로 주입되는 경우 전류 미러에 의해 M배로 곱하여진다. 주입된 전류는 이들 디바이스의 콜렉터 바이어스 전류를 감소시키므로, 그들의 gm을 RF,eff의 함 수로 감소시킨다.

곱셈량 M은 최소 RF,eff의 조건하에서 Q1 및 Q2가 계속하여 요구되는 대역폭에 걸쳐 신호를 적절하게 전달하기에 충분한 바이어스 전류를 갖도록 정해져야 한다. 반대 극단에서, RF,eff가 최대값에 있을 때, Gm 보상 회로는 off 되어야 한다. 이는 예를 들어 RF,eff > R7일 때 일어난다. 이득 = M인 전류 미러의 입력측은 단지 전류만을 내려오게 할 수 있으므로, 차단된다.

이때, 극 비율은 다음의 표현식에 의해 결정된다:

극 비율은 다음을 포함하는 다수의 인자들로 구성됨을 주목한다:

모든 RF,eff에 걸쳐 고정된 캐패시터 비율 CS:CC;

모든 RF,eff에 걸쳐 또한 고정된 νT:RC의 비율;

적절한 값의 Iin에 대해, 대략 RF,eff에 반비례하는 분모에 IB를 갖는 인자. 이 인자는 "1/IB..."로 나타내진다; 또한, 4의 값으로 제한되고 "RC/RF+..."로 나타내지는 RC/RF,eff를 갖는 인자.

이들 인자와 RF,eff 및 Iin에 대한 그들의 관계는 실시예에서 사용되는 전형적인 값을 가지고 도 9에서 설명된다.

실시예

이 설계는 NPN ft = 25GHz의 BiCMOS 처리에서 제작되었다. 회로 매개변수에서의 중재로, 구성성분의 값에 대해 다음을 선택하게 하였다:

| Cs 0.8pF | RF,eff(max) 1㏀ | Rc 219Ω | IB 4.6mA | VAGC 50mV |

| Cc 50fF | RF,eff(min) 200Ω | R7 1㏀ | Ix 80uA | M 64 |

대응하는 극 비율은 도 9에 도시되고, 10μA 내지 2mA까지의 피크 대 피크의 입력 전류값에 대해, 비율은 2.75내에 들지 않는 것으로 나타난다. 본 설명에 기초하여 실시자에게 명확한 바와 같이, 많은 다른 구성성분값이 대치되어 유사한 결과를 제공할 수 있다.

그래서, 본 발명은 복잡하지 않은 구성성분의 배열로 넓은 동적 범위와 안정성을 제공한다. 대부분의 저잡음 신호 이득을 제공하는 증폭기의 제 1 스테이지는 루프에 추가 버퍼 또는 이득 스테이지를 포함하지 않고 최소 구성성분의 간략화된 회로로 실시된다.

다른 이득 설정을 통한 루프 안정성은 2가지 기술을 사용하여 이루어진다: 보상 회로를 사용하여 입력 트랜지스터의 gm을 변화시키는 것과, 입력 트랜스콘덕터 Q1의 출력에 직접 피드백 저항기를 연결시킴으로서, 피드백 저항기가 자동적으로 루프 이득을 감소시키는 것. 이득 변화 및 루프 안정성은 모두 유사한 단자 전압 및 동작 조건하에서 동작하는 똑같은 가변 저항기의 3가지 예로 제어된다. 이는 트래킹을 용이하게 하여, 이득 제어 회로가 간략화될 수 있음을 의미한다.

다시 도 8을 참고로, 본 발명의 바람직한 실시예에 대한 회로도가 설명된다. 회로는 이득 스테이지, 더미 스테이지, 및 차동 전압 버퍼를 포함한다. 차동 전압 버퍼는 여러 방법으로 구성될 수 있다. 바람직하게, 차동 전압 버퍼는 각 측면을 바이어스 처리하도록 이미터 변형 저항기 및 활성 전류원 (I0, I1)과 미분쌍으로 구성된다. 전류원은 동작하기 위해 약 500mV의 선두 여분 공간 (headroom)을 요구한다. 그러나, Q17, Q16의 베이스가 직접 제 1 및 더미 이득 스테이지의 출력에 연결되면, 예를 들어 Q1 및 Q2의 콜렉터에 연결되면, Q17, Q16의 이미터는 수십 mV 범위의 GND 전위에 가까워져 전류원이 동작될 수 없게 된다. 결과적으로, 레벨 쉬프트 다이오드 D1 및 D2는 전류원이 충분한 동작 선두 여분 공간을 갖도록 대략 700mV 만큼 차동 전압 버퍼의 공통 모드 입력 전압을 상승시키도록 요구된다. 이것이 수용가능한 성능을 제공하지만, 이는 약간 더 복잡해지고 (다이오드) 더 많은 신호 노드가 필요한 결점을 갖는다.

도 10a는 본 발명의 다른 이득 보상 실시예의 회로 구성성분예를 갖는 블록도이다. 다른 방법의 이득 보상 실시예는 이득 스테이지의 스케일 조정된 복제 스테이지(1080), 피드백 네트워크(1082), 증폭기(1084), 및 보상 전류 제공기 세트(1086)를 포함한다. 증폭기(1084)는 입력들 Input+, Input-, 및 Output을 갖는 전류 컨베이어로 배열된다.

증폭기(1084)는 공통 베이스 입력 (1003, 1004)을 갖는다. 증폭기 "output" 핀 전압은 "Input+"과 "Input-" 사이의 전압차가 증가될 때 증가된다. 증폭기는 (1004)의 활성 로드에 대해 전류원을 사용하므로 높은 이득을 갖는다.

피드백 네트워크는 피드백 저항기 (M3, RF3)로 완전한 이득/더미 스테이지 (Q4, R2)의 복제 스테이지를 구비한다. 디바이스(1008)는 증폭기 (1000 내지 1007)로부터의 출력 전압을 RF3//M3를 통해 흐르고 (1011)을 통해 출력되어 RF3//M3에 걸쳐 전압 강하를 일으키는 전류로 변환한다. 이 전압 강하는 이어서 증폭기 (1000 내지 1007)의 입력으로 피드백된다.

증폭기 (1000 내지 1007) 및 피드백 네트워크는 (1002)에 걸친 일정한 전압 강하가 RF3//M3 가변 저항기의 조합에 각인될 때 안정된 동작점에 이르도록 구성된다. 그래서, (1008)에 의해 RF3//M3를 통하여 주어지는 전류는 실제로 이득 제어 회로에 의해 제어되는 RF3//M3의 유효 저항으로 나눈 (1002)에 걸친 전압과 동일하다. 그러므로, (1008, 1009)를 통한 전류는 피크 입력 신호 전류의 배수와 똑같다. (1009)를 통한 전류는 이어서 이득 및 더미 스테이지에 인가되어, 이들 스테이지의 gm을 감소하고 전체적인 증폭기를 제어 및 안정화하는데 도움이 된다. 도표 1은 도 10a의 이득 보상 실시예에 대한 전형적인 구성성분값의 세트를 제공한다.

도표 1

1000,1001,1005,1006 2μA 정전류원

1002 150Kohm 저항기

1003,1004 일반 NPN 트랜지스터, 동일한 크기

1007 2pF 캐패시터

1008,1009 W/L = 72u/1.2u PFET 트랜지스터

1010,1011 2mA를 전도할 수 있는 일반 NPN 트랜지스터

1012,1013 일반 NPN 트랜지스터, 1010, 1011의 2배 면적

RC1,RC2,R2 220ohm

Q1,Q2,Q4 5mA를 전도할 수 있는 일반 NPN 저잡음 트랜지스터

RF1,RF2,RF3 1Kohm

M0,M1,M3 W/L = 64u/1.1u NFET 트랜지스터

도 10b는 본 발명의 제 1 다른 실시예를 실시한 회로도이다. 전류원은 차동 전압 버퍼로부터 제거되어, 레벨 쉬프트 다이오드에 대한 필요성을 없앴다. 차동 전압 버퍼의 제 1 다른 실시예는 이전의 이미터 변형 저항기를 2개 부분으로 분할하고 중심 탭을 GND에 단락시킨다. 따라서, 새로운 실시의 이미터 변형 저항기 - R12, R15 -가 변형 저항기 및 전류 소스로 동작한다. Q1의 콜렉터에 대한 신호 편위가 너무 느려서 Q17이 전도성으로부터 벗어나지 않도록 보장하기 위해 주의하여야 한다. 이 조건은 gm 보상 구조를 수정함으로서 지켜질 수 있다.

도 10b는 또한 본 발명의 다른 이득 보상 구조에 대한 실시예의 회로도를 포함한다. 보상 전류는 콜렉터에서 전류를 추출하는 대신에 피드백 저항기를 통해 낮춤으로서 Q1 및 Q2로부터 바이어스 전류를 추출한다. 이 구조는 차동 전압 버퍼의 입력 트랜지스터가 Q1의 콜렉터에서 큰 신호 편위 동안 턴 오프되는 것을 방지한다. 예를 들어, 이 조건은 단지 레벨 쉬프트 다이오드가 주어지지 않을 때만 문제가 된다.

반복하여, 다른 이득 보상 구조의 목적은 평균적인 입력 전류 진폭을 정확하게 측정하고 일부 최대치에 종속되는 입력 신호에서 배수를 공제하는 것이다. (1004, 1003, 1002, 1008)로 형성된 증폭기는 피드백 루프의 일부이다. M3, RF3, 및 Q4는 루프를 완성하는 피드백 소자를 형성한다. M3, RF3, Q4, 및 R2는 이득 스테이지 및 더미 이득 스테이지를 정확하게 스케일 조정하여 복제한 스테이지이다. 이는 M3 및 RF3의 병렬 조합이 신호 이득 스테이지와 정확하게 똑같은 특성을 가져야 함을 의미한다.

이와 같이, 피드백 루프 (1003, 1004, 1002, 1008, RF3, M3)는 M3 및 RF3의 병렬 조합에서 (1002)에 걸친 전압 강하를 각인하도록 노력한다. 전류원 (1000, 1001, 1005, 1006)은 Q4 바이어스 전류와 비교해 모두 작은 크기 (약 2μA)를 갖는다. 저항기(1002)는 그의 전압 강하가 AGC 전압의 일부 배수 m1과 동일하도록 선택된다. 이 전압 강하는 스케일 조정된 복제 스테이지 M3, RF3에 걸쳐 루프에 의해 강요된다. 이는 (1008)을 통한 전류가 피크 입력 신호 전류에 비례함을 의미한다. 이는 AGC 루프가 활성화될 때 M0, M1, M3 게이트 전압을 변조시킴으로서 RF1, M0에 걸쳐 일정한 피크 전압을 유지하도록 노력하기 때문이다.

(1008)에서의 비례적인 재생산 피크 신호 전류는 (1009)에 의해 복사되어 전류 미러 (1010, 1011, 1012, 1013)에 전달된다. 소스 (1012, 1013)는 이 미러 전류를 이득 스테이지 및 더미 이득 스테이지 베이스 밖으로 내려 Q1 및 Q2의 gm을 감소시킨다.

이는 증가된 입력 신호 진폭이 있을 때 Q1, Q2 콜렉터에서의 전압을 증가시키는 이점을 갖고, 전도성에서 벗어나는 것으로부터 다른 실시의 차동 전압 버퍼의 입력 디바이스를 보호하여 많은 신호 왜곡의 발생을 방지하는데 도움이 된다. 도 11은 큰 입력 신호 하에서의 안정성을 나타내어 극 비율에서 다른 회로 구성의 효과를 설명한다. 특히, 그래프 Y축은 유효 콜렉터 저항(RC,eff)에 대한 폐쇄 루프 입력 임피던스(Rin)의 비율이다. 이 인자는 fout:fin 극 비율에 비례한다. X축은 입력 신호 전류를 나타낸다.

가장 아래에 있는 자취는 특히 도 5에 도시된 종래 기술에서부터의 전형적인 특성을 도시한다. 이는 AGC가 활성화 상태일 때 (90μApp < 입력 전류 < 800μApp), 입력 전류 진폭이 증가함에 따라 극 비율이 비례하여 변하고 안정성이 저하됨을 명확하게 나타낸다. 이 효과는 도 12에서 과도 대안도를 참고로 더 설명된다. 낮은 입력 전류에서 (- 50μApp), 차동 출력 전압은 안정되게 보인다 - 오버슈트 (overshoot)나 공명 (ringing)이 없다. 그러나, 500μApp 입력 전류로는 차동 출력 전압이 실질적인 오버슈트 및 공명과 매우 다르게 보인다. 그래서, 안정성이 해결된다.

도 11을 다시 참고로, 위에 있는 자취는 바람직한 실시예 (도 8)에서의 극 비율에 비례한다. 일단 AGC가 활성화되면, 극 비율은 증가되고 1mApp 입력 전류 부근에서 피크가 된다. 전체 범위의 입력 전류에 걸친 변화는 종래 기술에 대한 것 보다 상당히 더 적다. 이는 전체 범위의 입력 전류에 걸쳐 훨씬 더 안정한 증폭기임을 나타낸다. 이는 낮은 입력 전류 (50μApp) 및 훨씬 더 높은 전류 500μApp에서 순간적인 대안도를 도시하는 도 13을 참고로 더 설명된다. 종래 기술과 유사하게, 50μApp 파형은 오버슈트나 공명 없이 안정된다. 그러나, 종래 기술과 다르게, 500μApp 파형도 또한 공명 및 미세 오버슈트 없이 매우 안정된다.

마지막으로, 다시 도 11을 참고로, 중간에 있는 자취는 제 1 다른 (도 10) 극 비율에 비례한다. 이 자취는 다른 2개 보다 더 적은 변화를 갖는다. 이 회로는 도 14의 그래프를 조사하여 안정되는 것으로 설명될 수 있고, 여기서 이전의 2가지 경우와 같이, 50μApp 자취는 오버슈트나 공명을 나타내지 않고 안정된 증폭기로부터의 출력을 예시한다. 더 높은 입력 전류 (500μApp) 자취도 또한 공명 및 약간의 오버슈트도 없이 안정된다.

여기서는 비록 광학 트랜스듀서의 증폭 응용을 주로 참고하여 본 발명이 설명되었지만, 본 발명은 특히 넓은 동적 범위에 걸쳐 입력을 갖는 회로에서 안정성으로부터 이득을 보는 임의의 회로에 폭넓은 응용성을 갖는다.

명확하게, 상기 지시에 대해 본 발명의 다양한 수정 및 변화가 가능하다. 그러므로, 첨부된 청구항의 범위내에서, 본 발명이 여기에 특정하게 설명된 것 이외의 방법으로 실시될 수 있는 것으로 이해되어야 한다.

입력과 출력 사이의 극 비율이 안정되도록 이득 보상 기술을 사용함으로써 넓은 동적 범위 및 안정성을 획득할 수 있다.

Claims (30)

- 자동 이득 제어(automatic gain control, AGC) 회로에 있어서:이득 스테이지로서,상기 AGC 회로의 입력에 연결된 이득 스테이지 증폭기,상기 이득 스테이지 증폭기를 바이어스 처리하도록 구성된 이득 스테이지 전류원, 및상기 이득 스테이지 증폭기에 연결되고 상기 이득 스테이지 증폭기의 이득을 변화시키도록 구성된 이득 제어 메카니즘 부분을 갖는 상기 이득 스테이지; 및상기 이득 스테이지 증폭기의 출력에 연결된 입력을 갖고 상기 이득 스테이지 증폭기의 출력에 기초하여 이득 제어 전압을 생성하도록 구성된 이득 제어 회로로서, 상기 이득 제어 전압이 상기 이득 제어 메카니즘 부분에 연결되어 상기 이득 제어 메카니즘 부분의 이득을 조정하는데 사용되는, 상기 이득 제어 회로를 포함하는, AGC 회로.

- 제 1 항에 있어서,상기 이득 스테이지 증폭기는 상기 AGC 회로의 입력에 접속된 게이트를 갖는 트랜지스터이고;상기 이득 제어 메카니즘 부분은 상기 이득 제어 회로의 출력 전압에 의해 제어된 일정량의 저항을 갖는 가변 피드백 저항기인, AGC 회로.

- 제 2 항에 있어서,상기 가변 피드백 저항기는 저항기와 병렬인 FET 트랜지스터를 포함하고, 상기 FET의 게이트가 상기 이득 제어 회로의 출력 전압에 접속되고,상기 가변 피드백 저항기는 상기 이득 스테이지 증폭기의 콜렉터와 베이스 사이에 접속되는, AGC 회로.

- 제 1 항에 있어서,상기 이득 제어 회로는;상기 이득 스테이지의 출력에 연결되고 상기 이득 스테이지 증폭기의 피크 출력을 검출하도록 구성된 피크 검출기, 및상기 피크 출력을 이득 제어 기준 전압과 비교하고 비교 출력을 상기 이득 제어 메카니즘 부분에 인가하도록 구성된 비교기를 포함하는, AGC 회로.

- 제 4 항에 있어서,상기 이득 스테이지와 동등한 이득 특성을 가지며 더미 스테이지(dummy stage)의 출력에서 이득 스테이지 기준 전압을 생성하도록 구성된 더미 이득 스테이지를 더 포함하고;상기 더미 이득 스테이지는,더미 증폭기,상기 더미 증폭기를 바이어스 처리하도록 구성된 더미 전류원, 및상기 더미 증폭기에 연결되고 상기 더미 증폭기의 이득을 변화시키도록 구성된 더미 이득 제어 메카니즘 부분을 포함하고;상기 피크 검출기는 상기 더미 이득 스테이지의 출력에 또한 연결되고 상기 이득 스테이지 출력 및 상기 더미 이득 스테이지 출력을 비교하여 상기 피크 출력을 검출하도록 구성되고;상기 이득 제어 회로는 더미 이득 스테이지 가변 이득 제어 메카니즘 부분의 이득을 조정하도록 또한 구성되는, AGC 회로.

- 제 1 항에 있어서,미리결정된 임계값 이상의 입력 신호 레벨들로 상기 이득 스테이지 증폭기의 바이어스 전류를 감소시키도록 구성된 이득 보상 회로를 더 포함하는, AGC 회로.

- 제 6 항에 있어서,상기 이득 보상 회로는:입력 전류 부분 및 미러(mirrored) 전류 부분을 갖고, 상기 미러 전류 부분은 상기 이득 스테이지 증폭기의 콜렉터에 접속되는 전류 미러,상기 입력 전류 부분에 연결된 미러 구동 회로, 및상기 미러 구동 회로에 접속되고 상기 이득 제어 회로의 출력에 기초하여 상기 미러 구동 회로에 의해 제공된 전류량을 상기 전류 미러의 입력 전류 부분으로 조절하도록 구성된 이득 보상 제어기를 포함하는, AGC 회로.

- 제 7 항에 있어서,상기 미러 구동 회로는 상기 전류 미러의 전류 입력에 접속된 구동 트랜지스터를 포함하고, 상기 구동 트랜지스터는 상기 이득 보상 제어기에 의해 제어되어 상기 입력 전류 부분에 흐르는 전류량을 제어하는, AGC 회로.

- 제 8 항에 있어서,상기 이득 보상 제어기는 상기 구동 트랜지스터의 베이스에 접속된 전압 레벨을 포함하고, 상기 전압 레벨은 상기 이득 제어 회로의 출력에 기초하는, AGC 회로.

- 제 8 항에 있어서,상기 이득 보상 제어기는, 하나의 단부가 전류원 및 상기 구동 트랜지스터의 베이스에 접속되고 제 2 단부가 기준 레벨 전압에 접속되는 구동 가변 저항기를 포함하고, 상기 구동 가변 저항기의 저항 양이 상기 이득 제어 회로의 출력에 의해 제어되는, AGC 회로.

- 제 10 항에 있어서,상기 구동 가변 저항기는 고정된 저항기와 병렬인 FET이고, 상기 이득 제어 회로의 출력에 접속된 상기 FET의 게이트를 갖는, AGC 회로.

- 제 8 항에 있어서,상기 구동 트랜지스터의 콜렉터는 제 2 전류원 및 상기 전류 미러의 입력에 접속되고;상기 구동 트랜지스터의 이미터는 저항을 통해 상기 기준 레벨 전압에 접속되는, AGC 회로.

- 제 10 항에 있어서,상기 기준 레벨 전압은 접지인, AGC 회로.

- 제 1 항에 있어서,상기 이득 스테이지의 구성요소들과 동등하게 구성되고 상기 이득 스테이지와 동등한 이득 특성을 갖는 더미 증폭기, 더미 전류원, 및 더미 이득 제어 메카니즘 부분을 갖는 더미 이득 스테이지; 및상기 이득 스테이지의 출력에 연결된 제 1 입력과 상기 더미 이득 스테이지의 출력에 연결된 제 2 입력을 갖는 차동 전압 버퍼로서, 상기 이득 스테이지 및 더미 이득 스테이지 출력들을 버퍼 처리하여 이들을 상기 이득 제어 회로에 제공하도록 구성된 상기 차동 전압 버퍼를 더 포함하고;상기 이득 제어 회로는 상기 이득 스테이지 및 더미 스테이지 버퍼 처리 출력들에 기초하여 상기 이득 제어 전압을 생성하고;상기 이득 제어 전압은 상기 더미 이득 제어 메카니즘 부분에 또한 연결되어 상기 더미 이득 제어 메카니즘의 이득을 조정하는데 사용되는, AGC 회로.

- 제 14 항에 있어서,상기 차동 전압 버퍼는,상기 이득 스테이지의 출력에 접속된 베이스, 제 1 저항 전류원에 접속된 콜렉터, 및 활성 전류원과 이미터 변형 저항기(emitter degeneration resistor)의 제 1 단부에 연결된 이미터를 갖는 제 1 차동 트랜지스터, 및상기 더미 이득 스테이지의 출력에 접속된 베이스, 제 2 저항 전류원에 접속된 콜렉터, 및 제 2 활성 전류원과 상기 이미터 변형 저항기의 제 2 단부에 접속된 이미터를 갖는 제 2 차동 트랜지스터를 포함하고;상기 차동 트랜지스터들의 콜렉터들은 상기 이득 제어 회로의 입력들에 연결되고 그에 의해 제공된 신호들은 상기 이득 제어 전압을 생성하는데 사용되는, AGC 회로.

- 제 15 항에 있어서,상기 이득 스테이지 증폭기와 상기 이득 스테이지 전류원 사이에 연결된 제 1 레벨 쉬프트 다이오드로서, 상기 제 1 차동 트랜지스터의 베이스가 상기 제 1 레벨 쉬프트 다이오드와 상기 이득 스테이지 전류원의 접합부에 또한 연결되는 상기 제 1 레벨 쉬프트 다이오드; 및상기 더미 이득 스테이지 증폭기와 상기 더미 전류원 사이에 연결되는 제 2 레벨 쉬프트 다이오드로서, 상기 제 2 차동 트랜지스터의 베이스가 상기 제 2 레벨 쉬프트 다이오드와 상기 더미 전류원의 접합부에 또한 연결되는 상기 제 2 레벨 쉬프트 다이오드를 더 포함하는, AGC 회로.

- 제 14 항에 있어서,상기 차동 전압 버퍼는,상기 이득 스테이지 증폭기의 출력에 접속된 베이스, 제 1 저항 전류원에 접속된 콜렉터, 제 1 저항기의 제 1 단부에 접속된 이미터, 및 접지에 접속된 상기 제 1 저항기의 제 2 단부를 갖는 제 1 차동 트랜지스터, 및상기 더미 이득 스테이지의 출력에 접속된 베이스, 제 2 저항 전류원에 접속된 콜렉터, 제 2 저항기의 제 1 단부에 접속된 이미터, 및 접지에 접속된 상기 제 2 저항기의 제 2 단부를 갖는 상기 제 2 차동 트랜지스터를 포함하고;상기 차동 트랜지스터들의 콜렉터들은 상기 이득 제어 회로의 입력들에 연결되고 그에 의해 제공된 신호들은 상기 이득 제어 전압을 생성하는데 사용되는, AGC 회로.

- 제 5 항에 있어서,상기 이득 제어 전압에 기초하여 상기 이득 스테이지 증폭기 및 상기 더미 이득 스테이지 증폭기의 바이어스 전류를 감소시키도록 구성된 이득 보상 회로를 더 포함하는, AGC 회로.

- 제 18 항에 있어서,상기 이득 보상 회로는:상기 이득 스테이지와 동일한 구성을 갖는 이득 스테이지의 복제(replica) 회로;상기 이득 제어 회로로부터 이득 조정량을 나타내는 특성들을 갖는 상기 이득 스테이지의 복제 회로의 요소의 전압을 측정하고, 설정된 전압과 상기 측정된 전압 사이의 차이에 따른 조정 전압을 제공하도록 구성된 증폭기;상기 조정 전압에 기초하여 상기 복제 회로의 요소에 전류를 제공하도록 구성된 피드백 네트워크; 및상기 이득 스테이지 및 더미 이득 스테이지 각각에 상기 복제 회로의 요소 전류와 동일한 바이어스 감소 전류들을 제공하도록 구성된 전류 디바이스를 포함하는, AGC 회로.

- 제 19 항에 있어서,상기 증폭기는 전류 컨베이어(current conveyor)를 포함하는, AGC 회로.

- 제 19 항에 있어서,상기 바이어스 감소 전류는, 상기 AGC의 입력에서 이득 제어 메카니즘 부분 및 이득 스테이지 증폭기에 연결되고, 상기 이득 제어 메카니즘 부분을 통해 바이어스 전류를 감소시키도록 구성되고, 상기 더미 이득 제어 메카니즘 부분 및 더미 증폭기에 연결되고, 상기 더미 이득 제어 메카니즘 부분을 통해 바이어스 전류를 감소시키도록 구성되는, AGC 회로.

- 제 19 항에 있어서,상기 복제 회로의 요소는 상기 이득 스테이지의 복제 회로의 가변 피드백 저항기를 포함하는, AGC 회로.

- 이득 스테이지 증폭기에 인가된 넓은 동적 범위의 입력들을 통해 상기 이득 스테이지 증폭기의 이득 제어 방법에 있어서:상기 이득 스테이지 증폭기의 출력 전압 레벨에 기초하여 상기 이득 스테이지 증폭기의 이득량을 변화시키는 단계; 및상기 이득 스테이지 증폭기의 출력 전압 레벨에 기초하여 상기 이득 스테이지 증폭기의 바이어스 전류를 감소시키는 단계를 포함하는, 이득 제어 방법.

- 제 23 항에 있어서,이득량을 변화시키는 상기 단계는:상기 이득 스테이지 증폭기와 상기 인가된 입력들 없이 상기 이득 스테이지 증폭기와 동일한 구성을 갖는 더미 이득 증폭기 사이에서 피크 전압 레벨을 검출하는 단계;상기 피크 전압 레벨을 기준 전압과 비교하는 단계; 및상기 비교된 전압을 상기 이득 스테이지 증폭기의 이득을 조정하는 가변 피드백 디바이스에 인가하는 단계를 포함하는, 이득 제어 방법.

- 제 24 항에 있어서,상기 인가 단계는 상기 비교된 전압을 상기 이득 스테이지 증폭기의 피드백 저항기와 병렬인 FET의 게이트에 인가하는 단계를 포함하는, 이득 제어 방법.

- 제 23 항에 있어서,상기 이득 스테이지 증폭기의 바이어스 전류를 감소시키는 상기 단계는:상기 이득 스테이지 증폭기와 상기 인가된 입력들 없이 상기 이득 스테이지 증폭기와 동일한 구성을 갖는 더미 이득 증폭기 사이에서 피크 전압 레벨을 검출하는 단계;상기 피크 전압 레벨을 기준 전압과 비교하는 단계;상기 비교된 전압을 전류 디바이스로부터 출력 전류량을 조정하는 가변 전압 디바이스에 인가하는 단계;상기 전류 디바이스의 출력을 전류 미러에 대한 소스로서 입력하는 단계; 및상기 바이어스 전류로부터의 전류를 감산하기 위해 상기 미러 전류를 인가하는 단계를 포함하는, 이득 제어 방법.

- 제 24 항에 있어서,상기 이득 스테이지 증폭기의 바이어스 전류를 감소시키는 상기 단계는;상기 비교된 전압을 전류 디바이스로부터 출력 전류량을 조정하는 가변 전압 디바이스에 인가하는 단계;상기 전류 디바이스의 출력을 이중 전류 미러(double current mirror)에 대한 소스로서 입력하는 단계;상기 이득 스테이지 증폭기의 상기 바이어스 전류로부터 전류를 감산하기 위해 상기 제 1 미러 전류를 인가하는 단계; 및상기 더미 이득 증폭기의 바이어스 전류로부터 전류를 감산하기 위해 상기 제 2 미러 전류를 인가하는 단계를 포함하는, 이득 제어 방법.

- 자동 이득 제어 (AGC) 회로에 있어서:이득 스테이지 증폭기의 출력 전압 레벨에 기초하여 상기 이득 스테이지 증폭기의 이득량을 변화시키는 수단; 및상기 이득 스테이지 증폭기의 출력 전압 레벨에 기초하여 상기 이득 스테이지 증폭기의 바이어스 전류를 감소시키는 수단을 포함하는, AGC 회로.

- 제 28 항에 있어서,상기 이득 스테이지 증폭기와 상기 인가된 입력들 없이 상기 이득 스테이지 증폭기와 동일한 구성을 갖는 더미 이득 증폭기 사이에서 피크 전압 레벨을 검출하는 수단;상기 피크 전압 레벨을 기준 전압과 비교하는 수단; 및상기 비교된 전압을 상기 이득 스테이지 증폭기의 이득을 조정하는 가변 피드백 디바이스에 인가하는 수단을 더 포함하는, AGC 회로.

- 제 28 항에 있어서,상기 이득 스테이지 증폭기와 상기 인가된 입력들 없이 상기 이득 스테이지 증폭기와 동일한 구성을 갖는 더미 이득 증폭기 사이에서 피크 전압 레벨을 검출하는 수단;상기 피크 전압 레벨을 기준 전압과 비교하는 수단;상기 비교된 전압을 전류 디바이스로부터 출력 전류량을 조정하는 가변 전압 디바이스에 인가하는 수단;상기 전류 디바이스의 출력을 전류 미러에 대한 소스로서 입력하는 수단; 및상기 바이어스 전류로부터 전류를 감산하기 위해 상기 미러 전류를 인가하는 수단을 더 포함하는, AGC 회로.

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US25061100P | 2000-12-01 | 2000-12-01 | |

| US60/250,611 | 2000-12-01 | ||

| US09/910,660 | 2001-07-20 | ||

| US09/910,660 US6583671B2 (en) | 2000-12-01 | 2001-07-20 | Stable AGC transimpedance amplifier with expanded dynamic range |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20020043189A KR20020043189A (ko) | 2002-06-08 |

| KR100887893B1 true KR100887893B1 (ko) | 2009-03-16 |

Family

ID=22948452

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020010075633A KR100887893B1 (ko) | 2000-12-01 | 2001-12-01 | 새로운 agc 트랜스임피던스 증폭기 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6583671B2 (ko) |

| JP (1) | JP4032720B2 (ko) |

| KR (1) | KR100887893B1 (ko) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20200062788A (ko) * | 2018-11-27 | 2020-06-04 | 아주대학교산학협력단 | 단일 전송선을 이용한 실시간 양방향 데이터 전송 회로 및 그 방법 |

Families Citing this family (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7078967B2 (en) * | 1999-12-30 | 2006-07-18 | Nokia Corporation | Control of bias voltage |

| SG93224A1 (en) * | 2000-02-02 | 2002-12-17 | Koninkl Philips Electronics Nv | Measuring antenna signal strength with automatic gain control receiver |

| US7171170B2 (en) | 2001-07-23 | 2007-01-30 | Sequoia Communications | Envelope limiting for polar modulators |

| US6798290B2 (en) * | 2001-08-31 | 2004-09-28 | Sequoia Communications | Translinear variable gain amplifier |

| US6985703B2 (en) | 2001-10-04 | 2006-01-10 | Sequoia Corporation | Direct synthesis transmitter |

| JP3857099B2 (ja) * | 2001-10-09 | 2006-12-13 | 株式会社アドバンテスト | データ伝送装置、光電変換回路、及び試験装置 |

| EP1322036A1 (fr) * | 2001-12-20 | 2003-06-25 | Koninklijke Philips Electronics N.V. | Dispositif comportant un amplificateur symétrique |

| KR100613141B1 (ko) * | 2002-07-19 | 2006-08-17 | 인티그런트 테크놀로지즈(주) | 선형성이 개선된 가변 이득 증폭기 |

| US7489916B1 (en) | 2002-06-04 | 2009-02-10 | Sequoia Communications | Direct down-conversion mixer architecture |

| US6882218B2 (en) * | 2002-08-26 | 2005-04-19 | Broadcom Corporation | Transimpedance amplifier and offset correction mechanism and method for lowering noise |

| US6980055B2 (en) * | 2003-08-11 | 2005-12-27 | Texas Instruments Incorporated | CMOS differential buffer circuit |

| US6894568B2 (en) * | 2003-08-20 | 2005-05-17 | Intel Corporation | Transimpedance amplifier with receive signal strength indicator |

| US6864751B1 (en) * | 2003-09-08 | 2005-03-08 | Texas Instruments Deutschland Gmbh | Transimpedance amplifier with adjustable output amplitude and wide input dynamic-range |

| US7496338B1 (en) | 2003-12-29 | 2009-02-24 | Sequoia Communications | Multi-segment gain control system |

| US7609118B1 (en) | 2003-12-29 | 2009-10-27 | Sequoia Communications | Phase-locked loop calibration system |

| US7522017B1 (en) | 2004-04-21 | 2009-04-21 | Sequoia Communications | High-Q integrated RF filters |

| US7332971B2 (en) * | 2004-06-10 | 2008-02-19 | Agency For Science, Technology And Research | Multi-gigabit/s transimpedance amplifier for optical networks |

| US7672648B1 (en) | 2004-06-26 | 2010-03-02 | Quintics Holdings | System for linear amplitude modulation |

| US7196582B2 (en) * | 2004-10-29 | 2007-03-27 | Broadcom Corporation | Method and system for low noise amplifier (LNA) and power amplifier (PA) gain control |

| US7479815B1 (en) | 2005-03-01 | 2009-01-20 | Sequoia Communications | PLL with dual edge sensitivity |

| US7548122B1 (en) | 2005-03-01 | 2009-06-16 | Sequoia Communications | PLL with switched parameters |

| US7675379B1 (en) | 2005-03-05 | 2010-03-09 | Quintics Holdings | Linear wideband phase modulation system |

| US7595626B1 (en) | 2005-05-05 | 2009-09-29 | Sequoia Communications | System for matched and isolated references |

| US20070205200A1 (en) * | 2006-03-02 | 2007-09-06 | Brain Box Concepts | Soap bar holder and method of supporting a soap bar |

| WO2007137094A2 (en) | 2006-05-16 | 2007-11-29 | Sequoia Communications | A multi-mode vco for direct fm systems |

| US8269562B1 (en) * | 2006-06-30 | 2012-09-18 | Ixys Ch Gmbh | Open-loop transimpedance amplifier for infrared diodes |

| US7522005B1 (en) | 2006-07-28 | 2009-04-21 | Sequoia Communications | KFM frequency tracking system using an analog correlator |

| US7679468B1 (en) | 2006-07-28 | 2010-03-16 | Quintic Holdings | KFM frequency tracking system using a digital correlator |

| US7894545B1 (en) | 2006-08-14 | 2011-02-22 | Quintic Holdings | Time alignment of polar transmitter |

| US7920033B1 (en) | 2006-09-28 | 2011-04-05 | Groe John B | Systems and methods for frequency modulation adjustment |

| US20090058531A1 (en) * | 2007-08-31 | 2009-03-05 | Nanoamp Solutions Inc. (Cayman) | Variable gain amplifier |

| US8081030B2 (en) * | 2008-12-19 | 2011-12-20 | Honeywell International Inc. | Multi-mode amplifier |

| US7893759B1 (en) | 2009-03-18 | 2011-02-22 | Honeywell International Inc. | Current conveyor based instrumentation amplifier |

| JP5475525B2 (ja) * | 2010-04-01 | 2014-04-16 | 日本電信電話株式会社 | 利得可変増幅器および光受信器 |

| JP2013115562A (ja) * | 2011-11-28 | 2013-06-10 | Sumitomo Electric Ind Ltd | トランスインピーダンスアンプ |

| US9030263B2 (en) | 2013-03-15 | 2015-05-12 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Transimpedance amplifier (TIA) circuit and method |

| US9112462B2 (en) | 2013-05-15 | 2015-08-18 | Honeywell International Inc. | Variable-gain dual-output transconductance amplifier-based instrumentation amplifiers |

| FR3026250A1 (fr) * | 2014-09-19 | 2016-03-25 | St Microelectronics Sa | Dispositif electronique pour une chaine de reception de signaux radiofrequence, comprenant un etage amplificateur transconducteur a faible bruit |

| WO2017025598A1 (en) * | 2015-08-11 | 2017-02-16 | Koninklijke Philips N.V. | Capacitive micromachined ultrasonic transducers with increased patient safety |

| CN106941379A (zh) * | 2017-05-05 | 2017-07-11 | 烽火通信科技股份有限公司 | 一种用于apd跨阻放大器的自动增益控制电路 |

| CN108173524B (zh) * | 2018-02-08 | 2021-02-19 | 厦门亿芯源半导体科技有限公司 | 适用于高带宽tia的双环路自动增益控制电路 |

| CN110545083A (zh) * | 2018-05-28 | 2019-12-06 | 深圳市芯波微电子有限公司 | 跨阻放大器 |

| US10958177B2 (en) * | 2019-05-31 | 2021-03-23 | Dialog Semiconductor Inc. | Optocoupler current transfer ratio compensation |

| CN112039452B (zh) * | 2020-09-07 | 2022-08-23 | 电子科技大学 | 一种宽带跨阻放大器 |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0878980A (ja) * | 1994-08-30 | 1996-03-22 | Oki Electric Ind Co Ltd | ゲイン可変増幅回路 |

| US5801587A (en) * | 1996-09-26 | 1998-09-01 | Exar Corporation | Variable gain peak detector |

| KR19980068704A (ko) * | 1997-02-22 | 1998-10-26 | 김광호 | 전압증폭기를 이용한 자동이득조절기 |

| US5844444A (en) * | 1997-02-14 | 1998-12-01 | Macronix International Co., Ltd. | Wide dynamic input range transconductor-based amplifier circuit for speech signal processing |

| KR19980086741A (ko) * | 1997-05-06 | 1998-12-05 | 윌리엄 비. 켐플러 | 자동 이득 제어를 위한 개선된 피크 검출기 |

| JPH11122188A (ja) * | 1997-10-20 | 1999-04-30 | Fujitsu Ltd | 光信号受信装置および方法 |

| JPH11234056A (ja) * | 1997-11-13 | 1999-08-27 | Matsushita Electric Ind Co Ltd | 光受信用前置増幅器とオフセット電圧可変のピーク検出器 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3679986A (en) * | 1970-09-04 | 1972-07-25 | Ibm | Non-linear feedback gain control and peak detector system |

| JPS5721379Y2 (ko) * | 1977-02-01 | 1982-05-10 | ||

| US4326226A (en) * | 1980-05-08 | 1982-04-20 | Storage Technology Corporation | Constant bandwidth automatic gain control |

| US5168148A (en) * | 1990-12-28 | 1992-12-01 | Symbol Technologies, Inc. | Automatic gain control circuit |

| US5483200A (en) * | 1993-06-08 | 1996-01-09 | Sharp Kabushiki Kaisha | Light-receiving and amplifying device capable of switching between gain levels at high speed and obtaining a sufficient signal-to-noise ratio over a wide range in quantity of incident light |

| US5451901A (en) * | 1994-07-01 | 1995-09-19 | Cirrus Logic Inc. | Transconductance amplifiers and exponential variable gain amplifiers using the same |

| US5923164A (en) * | 1996-10-15 | 1999-07-13 | Balluff, Inc. | Apparatus and method for automatically tuning the gain of an amplifier |

| JPH10322152A (ja) * | 1997-05-19 | 1998-12-04 | Fujitsu Ltd | デジタルagc回路 |

-

2001

- 2001-07-20 US US09/910,660 patent/US6583671B2/en not_active Expired - Fee Related

- 2001-12-01 KR KR1020010075633A patent/KR100887893B1/ko not_active IP Right Cessation

- 2001-12-03 JP JP2001369349A patent/JP4032720B2/ja not_active Expired - Fee Related

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0878980A (ja) * | 1994-08-30 | 1996-03-22 | Oki Electric Ind Co Ltd | ゲイン可変増幅回路 |

| US5801587A (en) * | 1996-09-26 | 1998-09-01 | Exar Corporation | Variable gain peak detector |

| US5844444A (en) * | 1997-02-14 | 1998-12-01 | Macronix International Co., Ltd. | Wide dynamic input range transconductor-based amplifier circuit for speech signal processing |

| KR19980068704A (ko) * | 1997-02-22 | 1998-10-26 | 김광호 | 전압증폭기를 이용한 자동이득조절기 |

| KR19980086741A (ko) * | 1997-05-06 | 1998-12-05 | 윌리엄 비. 켐플러 | 자동 이득 제어를 위한 개선된 피크 검출기 |

| JPH11122188A (ja) * | 1997-10-20 | 1999-04-30 | Fujitsu Ltd | 光信号受信装置および方法 |

| JPH11234056A (ja) * | 1997-11-13 | 1999-08-27 | Matsushita Electric Ind Co Ltd | 光受信用前置増幅器とオフセット電圧可変のピーク検出器 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20200062788A (ko) * | 2018-11-27 | 2020-06-04 | 아주대학교산학협력단 | 단일 전송선을 이용한 실시간 양방향 데이터 전송 회로 및 그 방법 |

| KR102147936B1 (ko) * | 2018-11-27 | 2020-08-26 | 아주대학교산학협력단 | 단일 전송선을 이용한 실시간 양방향 데이터 전송 회로 및 그 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002232244A (ja) | 2002-08-16 |

| US6583671B2 (en) | 2003-06-24 |

| KR20020043189A (ko) | 2002-06-08 |

| US20020101285A1 (en) | 2002-08-01 |

| JP4032720B2 (ja) | 2008-01-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100887893B1 (ko) | 새로운 agc 트랜스임피던스 증폭기 | |

| US6072366A (en) | Receiver capable of outputting a high quality signal without regard to an input signal level | |

| KR100900205B1 (ko) | 넓은 동적 범위 트랜스임피던스 증폭기 | |

| US5844445A (en) | Feedback type pre-amplifier | |

| US4564818A (en) | Transimpedance amplifier having an improved gain/bandwidth product | |

| US7973602B2 (en) | Variable gain amplifier | |

| US6292058B1 (en) | Signal amplifying circuit connected to a transfer circuit having a known non-linear transfer characteristic | |

| US7948323B2 (en) | Linear transimpedance amplifier with wide dynamic range for high rate applications | |

| US10355655B2 (en) | Transimpedance amplifier (TIA) circuit having reduced power consumption, improved linearization and reduced peaking | |

| JP7115065B2 (ja) | トランスインピーダンスアンプ | |

| US4718119A (en) | AGC circuit including a precision voltage clamp and method | |

| NL193076C (nl) | Versterkerregelketen. | |

| US5351012A (en) | Low input resistance current-mode feedback operational amplifier input stage | |

| US6879217B2 (en) | Triode region MOSFET current source to bias a transimpedance amplifier | |

| JPH0134501B2 (ko) | ||

| CN113659949A (zh) | 一种跨阻放大器电路的自动增益控制电路及方法 | |

| US11349444B2 (en) | Transimpedance amplifier circuit | |

| US5874861A (en) | Amplifier circuit | |

| US7221229B2 (en) | Receiver circuit having an optical reception device | |

| CN116633284A (zh) | 一种高增益跨阻放大器及高增益光电转换器 | |

| JP2019036817A (ja) | トランスインピーダンス増幅回路、及び利得可変増幅器 | |

| JP6706105B2 (ja) | トランスインピーダンスアンプおよび光信号受信装置 | |

| JP3844544B2 (ja) | 光受信回路 | |

| US5119041A (en) | High gain differential current amplifier having a low output voltage | |

| JP4271364B2 (ja) | 受光増幅回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| E902 | Notification of reason for refusal | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| LAPS | Lapse due to unpaid annual fee |