KR100435978B1 - 반도체장치 - Google Patents

반도체장치 Download PDFInfo

- Publication number

- KR100435978B1 KR100435978B1 KR1019970018462A KR19970018462A KR100435978B1 KR 100435978 B1 KR100435978 B1 KR 100435978B1 KR 1019970018462 A KR1019970018462 A KR 1019970018462A KR 19970018462 A KR19970018462 A KR 19970018462A KR 100435978 B1 KR100435978 B1 KR 100435978B1

- Authority

- KR

- South Korea

- Prior art keywords

- leads

- lead

- pair

- semiconductor

- semiconductor chip

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K5/00—Casings, cabinets or drawers for electric apparatus

- H05K5/02—Details

- H05K5/0256—Details of interchangeable modules or receptacles therefor, e.g. cartridge mechanisms

- H05K5/026—Details of interchangeable modules or receptacles therefor, e.g. cartridge mechanisms having standardized interfaces

- H05K5/0265—Details of interchangeable modules or receptacles therefor, e.g. cartridge mechanisms having standardized interfaces of PCMCIA type

- H05K5/0269—Card housings therefor, e.g. covers, frames, PCB

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/60—Attaching or detaching leads or other conductive members, to be used for carrying current to or from the device in operation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/495—Lead-frames or other flat leads

- H01L23/49541—Geometry of the lead-frame

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/181—Printed circuits structurally associated with non-printed electric components associated with surface mounted components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05554—Shape in top view being square

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49175—Parallel arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01014—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01028—Nickel [Ni]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01031—Gallium [Ga]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01032—Germanium [Ge]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01039—Yttrium [Y]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01055—Cesium [Cs]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01058—Cerium [Ce]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/1015—Shape

- H01L2924/1016—Shape being a cuboid

- H01L2924/10161—Shape being a cuboid with a rectangular active surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19041—Component type being a capacitor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19043—Component type being a resistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

- H01L2924/30111—Impedance matching

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09218—Conductive traces

- H05K2201/09236—Parallel layout

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09654—Shape and layout details of conductors covering at least two types of conductors provided for in H05K2201/09218 - H05K2201/095

- H05K2201/09772—Conductors directly under a component but not electrically connected to the component

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10621—Components characterised by their electrical contacts

- H05K2201/10689—Leaded Integrated Circuit [IC] package, e.g. dual-in-line [DIL]

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Abstract

반도체장치에 관한 것으로서, 고밀도 실장이 가능한 반도체장치를 제공하기 위해, 실장기판의 실장면상에 여러개 실장되는 반도체장치에 있어서 평면의 직사각형 형상의 봉지체에 의해 반도체칩을 봉지하고, 봉지체의 한측면에 그의 측면을 따라서 반도체칩의 외부단자와 전기적으로 접속된 외부리이드를 여러개 배열하고, 봉지체의 한측면과 대향하는 다른 측면에 그 측면을 따라서 반도체칩의 외부단자와 전기적으로 접속되지 않는 외부리이드를 여러개 배열한 구조로 구성하는 것에 의해, 한쪽의 반도체장치의 외부리이드와 다른 쪽의 반도체장치의 외부리이드 사이의 격리영역 및 배선의 배열 영역을 축소 또는 폐지할 수 있으므로, 이것에 상당하는 분만큼 반도체장치의 고밀도 실장이 가능하게 되고 메모리카드의 평면사이즈를 축소할 수 있다. 또, 봉지체의 한측면에 배열된 외부리이드와 봉지체의 다른 측면에 배열된 외부리이드에 의해 실장기판상에 반도체장치을 인정한 상태로 고정시킬 수 있으므로, 반도체장치의 내충격성을 높일 수 있다는 효과가 얻어진다.

Description

본 발명은 반도체장치에 관한 것으로서, 특히 실장기판의 실장면상에 여러개 실장되는 반도체장치에 적용해서 유효한 기술에 관한 것이다.

전자기기의 소형화나 박형화에 적합한 반도체장치로서 TSOP(Thin Small Out-line Package)구조의 반도체장치가 있다. 이 TSOP구조의 반도체장치는 예를 들면 DRAM(Dynamic Random Access Memory)으로 구성된 반도체칩을 수지로 이루어지는 봉지체에 의해 봉지하고 있다.

상기 봉지체는 평면이 직사각형 형상으로 형성되어 있다. 봉지체의 한 측면에는 그 측면을 따라서 여러개의 외부리이드가 배열되어 있다. 이 여러개의 외부리이드의 각각은 갈매기날개형상으로 성형되고, 반도체칩의 주면의 한변측에 배열된 여러개의 외부단자(본딩패드)의 각각과 전기적으로 접속되어 있다. 또, 봉지체의 한측면과 대향하는 다른 측면에는 그 측면을 따라서 여러개의 외부리이드가 배열되어 있다. 이 여러개의 외부리이드의 각각은 갈매기날개형상으로 성형되고, 반도체칩의 주면의 다른 변측에 배열된 여러개의 외부단자의 각각과 전기적으로 접속되어 있다. 즉, TSOP구조의 반도체장치는 봉지체의 서로 대향하는 2개의 측면의 각각에 반도체칩과 전기적으로 접속된 외부리이드를 여러개 배열한 2방향 리이드 배열구조로 구성되어 있다.

이와 같이 구성된 TSOP구조의 반도체장치는 예를 들면 퍼스널컴퓨터, 오피스컴퓨터 등의 전자기기에 증설 접속되는 메모리카드의 실장기판상에 여러개 규칙적으로 실장된다. 이 실장은 통상 실장기판의 실장면상에 배치된 전극패드(배선의 랜드영역)상에 페이스트형상의 땜납을 스크린인쇄법에 의해 형성하고, 이 땜납으로 실장기판의 전극패드와 반도체장치의 외부리이드를 고착시키는 것에 의해 실행된다.

또한, TSOP구조의 반도체장치에 대해서는 예를 들면 닛케이BP사 발행의 닛케이 마이크로디바이스(1990년 6월호, 제34페이지∼제45페이지)에 기재되어 있다.

상기 TSOP구조의 반도체장치는 봉지체의 서로 대향하는 2개의 측면의 각각에반도체칩의 외부단자와 전기적으로 접속된 외부리이드를 여러개 배열하고 있으므로, 이하의 문제가 발생한다.

[1] TSOP구조의 반도체장치를 실장기판의 실장면상에 방향을 일치시킨 상태에서 봉지체의 한측면과 직교하는 방향으로 여러개 실장한 경우, 인접하는 반도체장치 사이에 있어서 반도체칩의 외부단자와 전기적으로 접속된 외부리이드끼리가 대향하는 상태로 된다. 이 때문에, 메모리카드에 있어서는 실장시에 있어서의 반도체장치의 위치어긋남이나 땜납이 삐져나오는 것(땜납의 돌출)등을 고려해서 한쪽의 반도체장치의 외부리이드와 다른 쪽의 반도체장치의 외부리이드 사이에 격리(spacing)영역을 마련해서 인접하는 반도체장치 사이에서의 단락을 방지하고 있다. 그러나, 격리영역은 각 반도체장치 사이마다 마련되지 않으면 않되어 이 격리영역에 상당하는 분만큼 실장기판상에서의 반도체장치의 실장밀도가 저하한다.

[2] TSOP구조의 반도체장치를 실장기판의 실장면상에 방향을 일치시킨 상태에서 봉지체의 한측면과 직교하는 방향으로 여러개 실장한 경우, 인접하는 반도체장치 사이에 있어서 한쪽의 반도체장치의 봉지체의 한측면에 배열된 외부리이드와 다른 쪽의 반도체장치의 봉지체의 한측면에 배열된 외부리이드 사이에 한쪽의 반도체장치의 봉지체의 다른 측면에 배열된 외부리이드가 존재하는 상태로 된다. 즉, 동일 기능을 갖는 외부리이드 사이에 다른 기능을 갖는 외부리이드가 존재하는 상태로 된다. 이 때문에, 메모리카드에 있어서는 실장기판상으로 연장하는 배선을 배열하여(둘러쳐서) 각 반도체장치의 동일 기능의 외부리이드를 전기적으로 접속하고 있다. 그러나, 배선의 배열(둘러침)은 배선의 섬유면적의 증가로 되므로, 이것에상당하는 분만큼 실장기판상에서의 반도체장치의 실장밀도가 저하한다.

본 발명의 목적은 고밀도 실장이 가능한 반도체장치를 제공하는 것이다.

본 발명의 상기 및 그 밖의 목적과 새로운 특징은 본 명세서의 기술 및 첨부도면에 의해 명확하게 될 것이다.

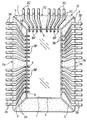

도 1은 본 발명의 실시형태1인 반도체장치의 봉지체의 상부를 제거한 상태의 평면도,

도 2는 도 1에 도시한 A-A선의 위치에서 자른 단면도,

도 3은 상기 반도체장치를 실장기판의 실장면상에 여러개 실장한 메모리카드의 평면도,

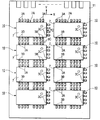

도 4는 상기 메모리카드의 주요부 확대평면도,

도 5는 본 발명의 실시형태2인 반도체장치의 봉지체의 상부를 제거한 상태의 평면도,

도 6은 상기 반도체장치를 실장기판의 실장면상에 여러개 실장한 메모리카드의 평면도,

도 7은 상기 메모리카드의 주요부 확대평면도,

도 8은 본 발명의 실시형태3인 반도체장치의 봉지체의 상부를 제거한 상태의 평면도,

도 9는 본 발명의 실시형태4인 반도체장치의 봉지체의 상부를 제거한 상태의 평면도,

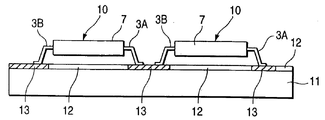

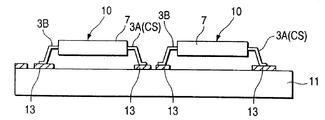

도 10a는 도 4에 있어서의 A-A선에 대응하는 단면도,

도 10b는 도 4에 있어서의 B-B선에 대응하는 단면도,

도 11은 본 발명의 메모리카드MC가 적용되는 전자기기의 외관도,

도 12는 메모리카드MC의 평면도,

도 13 및 도 14는 도 12의 A-A선, B-B선에 대응하는 단면도,

도 15는 본 발명의 실시형태5인 반도체장치의 외관도,

도 16은 도 15의 리이드핀의 명칭 및 기능을 설명한 설명도,

도 17은 도 15의 반도체장치에 탑재된 플래시메모리칩의 평면블럭도,

도 18은 본 발명의 메모리카드의 표면측의 평면도,

도 19는 본 발명의 메모리카드의 이면측의 평면도,

도 20은 도 18, 도 19의 A-A선에 대응하는 단면도,

도 21은 본 발명의 메모리카드(ATA카드)의 시스템구성을 도시한 블럭도.

본 원에 있어서 개시되는 발명 중 대표적인 것의 개요를 간단히 설명하면 다음과 같다.

실장기판의 실장면상에 여러개 실장되는 반도체장치에 있어서, 평면이 직사각형 형상인 봉지체에 의해 반도체칩을 봉지하고, 상기 봉지체의 한측면에 그 측면을 따라서 상기 반도체칩의 외부단자와 전기적으로 접속된 외부리이드를 여러개 배열하고, 상기 봉지체의 한측면과 대향하는 다른 측면에 그 측면을 따라서 상기 반도체칩의 외부단자와 전기적으로 접속되지 않는 외부리이드를 여러개 배열한 구조로 구성한다.

상술한 수단에 의하면, 반도체장치를 실장기판의 실장면상에 방향을 일치시킨 상태에서 봉지체의 한측면과 직교하는 방향으로 여러개 실장한 경우, 이 방향과 인접하는 반도체장치 사이에 있어서 한쪽의 반도체장치의 봉지체의 한측면에 배열된 외부리이드와 다른 쪽의 반도체장치의 봉지체의 다른 측면에 배열된 외부리이드가 대향하는 상태로 되지만, 한쪽의 반도체장치의 외부리이드는 그의 반도체칩의 외부단자와 전기적으로 접속되고, 다른 쪽의 반도체장치의 외부리이드는 그의 반도체칩의 외부단자와 전기적으로 접속되어 있지 않으므로, 반도체칩의 외부단자와 전기적으로 접속된 외부리이드끼리가 대향하는 일은 없다. 따라서, 한쪽의 반도체장치의 외부리이드와 다른 쪽의 반도체장치의 외부리이드 사이의 격리영역을 축소 또는 폐지하고 실장시에 반도체장치의 위치어긋남이나 땜납의 돌출 등이 발생해도, 봉지체의 한측면과 직교하는 방향으로 실장된 여러개의 반도체장치의 각각에 있어서 인접하는 반도체장치 사이에서의 단락은 발생하지 않는다. 이 결과, 한쪽의 반도체장치의 외부리이드와 다른 쪽의 반도체장치의 외부리이드 사이의 격리영역을 축소 또는 폐지할 수 있으므로, 이것에 상당하는 분만큼 반도체장치의 고밀도 실장이 가능하게 된다.

또, 반도체장치를 실장기판의 실장면상에 방향을 일치시킨 상태에서 봉지체의 한측면과 직교하는 방향으로 여러개 실장한 경우, 인접하는 반도체장치 사이에 있어서 한쪽의 반도체장치의 봉지체의 한측면에 배열된 외부리이드와 다른 쪽의 반도체장치의 봉지체의 한측면에 배열된 외부리이드 사이에 한쪽의 반도체장치의 봉지체의 다른 측면에 배열된 외부리이드가 존재하지만, 이 한쪽의 반도체장치의 봉지체의 다른 측면에 배열된 외부리이드는 그의 반도체칩의 외부단자와 전기적으로 접속되어 있지 않으므로, 한쪽의 반도체장치의 외부리이드와 다른 쪽의 반도체장치의 외부리이드 사이에 이들과 다른 기능을 갖는 외부리이드가 존재하는 일은 없다. 따라서, 실장기판상으로 연장하는 배선을 배열하지 않고 봉지체의 한측면과 직교하는 방향으로 실장된 각 반도체장치의 동일 기능의 외부리이드를 전기적으로 접속할 수 있다. 이 결과, 배선의 배열영역을 축소 또는 폐지할 수 있으므로, 이것에 상당하는 분만큼 반도체장치의 고밀도 실장이 가능하게 된다.

[발명의 실시형태]

이하, 도면을 참조해서 본 발명의 실시형태를 상세하게 설명한다.

또한, 발명의 실시형태를 설명하기 위한 모든 도면에 있어서 동일 기능을 갖는 것에는 동일 부호를 붙이고 그의 반복적인 설명은 생략한다.

실시형태1

도 1은 본 발명의 실시형태1인 반도체장치의 봉지체의 상부를 제거한 상태의 평면도이고, 도 2는 도 1에 도시한 A-A선의 위치에서 자른 단면도이다.

도 1 및 도 2에 도시한 바와 같이 본 실시형태의 반도체장치(10)은 TSOP구조로 구성되어 있다. 이 TSOP구조의 반도체장치(10)은 4개의 탭지지용 리이드(5)의 각각에 의해 지지된 탭(4)의 한 표면상에 반도체칩(1)을 탑재하고 있다. 반도체칩(1)은 도시하고 있지 않지만, Ag페이스트 등의 접착층을 개재해서 탭(4)의 한 표면에 고착되어 있다.

상기 반도체칩(1)은 예를 들면 평면이 직사각형 형상으로 형성된 단결정 규소기판으로 이루어지는 반도체기판을 주체로 하여 구성되어 있다. 반도체기판의 주면(소자형성면)에는 예를 들면 기억회로 시스템으로서 DRAM이 구성되어 있다. 또, 반도체기판의 주면상에는 배선층, 절연층의 각각을 여러단 적층한 다층 배선층이 형성되어 있다.

상기 반도체칩(1)의 주면의 한변측(한쪽의 긴 변측)에는 외부단자(본딩패드)BP가 그의 한변을 따라서 여러개 배열되어 있다. 이 여러개의외부단자BP의 각각은 다층배선의 최상층의 배선층에 형성되고, 기억회로 시스템과 전기적으로 접속되어 있다.

상기 반도체칩(1)의 한변의 외측에는 그의 한변을 따라서 여러개의 내부리이드(2A)가 배열되어 있다. 이 여러개의 내부리이드(2A)의 각각은 반도체칩(1)의 주면의 한변측에 배열된 여러개의 외부단자BP의 각각과 본딩와이어(6)을 거쳐서 전기적으로 접속되어 있다.

상기 반도체칩(1)의 한변과 대향하는 다른 변(다른 쪽의 긴 변)의 외측에는 그의 다른 변을 따라서 여러개의 내부리이드(2B)가 배열되어 있다. 이 여러개의 내부리이드(2B)의 각각은 반도체칩(1)의 외부단자BP와 전기적으로 접속되어 있지 않다.

상기 반도체칩(1), 내부리이드(2A), 내부리이드(2B), 탭(4), 탭지지용 리이드(5) 및 본딩와이어(6) 등은 평면이 직사각형 형상으로 형성된 봉지체(7)에 의해 봉지되어 있다. 이 봉지체(7)은 이것에 한정되지 않지만 예를 들면 트랜스퍼 성형법에 의해 형성된다. 트랜스퍼 성형법은 예를 들면 페놀계 경화제, 실리콘 고무 및 필러가 첨가된 에폭시계의 수지를 사용해서 봉지체를 성형하는 기술이다.

상기 봉지체(7)의 한측면(7A)에는 그의 측면을 따라서 여러개의 외부리이드(3A)가 배열되어 있다. 또, 봉지체(7)의 한측면(7A)와 대향하는 다른 측면(7B)에는 그의 측면을 따라서 여러개의 외부리이드(3B)가 배열되어 있다. 이 외부리이드(3A), (3B)의 각각은 갈매기날개형상으로 성형되어 있다.

상기 여러개의 외부리이드(3A)의 각각은 반도체칩(1)의 한변의 외측에 배열된 여러개의 내부리이드(2A)의 각각과 일체화되어 있다. 또, 상기 여러개의 외부리이드(3B)의 각각은 반도체칩(1)의 다른 변의 외측에 배열된 여러개의 내부리이드(2B)의 각각과 일체화되어 있다. 즉, 본 실시형태의 반도체장치(10)은 봉지체(7)의 한측면(7A)에 그의 측면을 따라서 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3A)를 여러개 배열하고, 봉지체(7)의 한측면과 대향하는 다른 측면(7B)에 그의 측면을 따라서 반도체칩(1)의 외부단자BP와 전기적으로 접속되지 않는 외부리이드(3B)를 여러개 배열한 2방향 리이드 배열구조로 구성되어 있다.

상기 외부리이드(3A), 외부리이드(3B), 탭지지용 리이드(5)의 각각은 반도체장치의 제조단계에 있어서 리이드프레임의 프레임과 일체화되어 있다. 이 외부리이드(3A), (3B), 탭지지용 리이드(5)의 각각은 내부리이드(2A), (2B), 탭(4), 탭지지용 리이드(5) 및 본딩와이어(6) 등을 봉지체(7)에 의해 봉지한 후 리이드프레임의 프레임에서 절단되고, 그 후 외부리이드(3A), (3B)의 각각은 갈매기날개형상으로 성형된다. 또한, 리이드프레임은 예를 들면 Cu계 합금 또는 Fe-Ni(예를 들면 Ni함유율 42 또는 50[%])합금으로 형성된다.

상기 외부리이드(3A) 및 외부리이드(3B)에는 어드레스신호, 로우어드레스 스트로브신호, 컬럼어드레스 스트로브신호, 출력인에이블신호, 라이트인에이블신호, 데이타입출력신호 등이 인가된다.

이와 같이 구성된 반도체장치(10)은 1개의 메모리시스템으로서 예를 들면 도 11에 도시한 바와 같이 퍼스널컴퓨터, 오피스컴퓨터 등의 전자기기PC에 증설 접속되는 메모리카드(전자장치)MC의 실장기판상에 여러개 규칙적으로 실장된다. 이 실장은 통상 실장기판의 실장면상에 배치된 전극패드(배선의 랜드영역)상에 페이스트형상의 땜납을 스크린인쇄법에 의해 형성하고, 이 땜납으로 실장기판의 전극패드와 반도체장치의 외부리이드를 고착시키는 것에 의해 실행된다.

상기 전자기기PC는 액정디스플레이(16), 키보드(17), 컨트롤패드(18) 및 메모리카드MC를 접속하기 위한 슬롯(19) 등을 갖는다.

상기 메모리카드MC의 커넥터측(20)이 상기 슬롯(19)에 삽입되고, 상기 전자기기PC와 메모리카드MC 사이에서 화상데이타 등의 데이타의 수수가 실행된다.

상기 메모리카드MC의 외관은 도 12, 도 13 및 도 14에 도시한 바와 같이 대략 판형상의 장방형을 이루고 있고, 예를 들면 플라스틱제의 외부프레임(15)를 스텐레스제의 커버(14) 사이에 끼운 중공의 구조체로 되어 있다. 이 구조체 중에는 실장기판(11)이 배치되어 있다. 상기 실장기판(11)의 한쪽끝은 상기 외부프레임(15)에 고정되어 있다. 상기 실장기판(11)상에는 다음에 설명하는 도 3 및 도 4에 도시한 바와 같은 반도체장치(10)이 여러개 탑재되고 메모리카드MC의 본체를 구성한다.

상기 메모리카드(전자장치)는 도 3(평면도)에 도시한 바와 같이 여러개의 반도체장치(10)을 실장기판(11)의 실장면상에 방향을 일치시킨 상태에서 행렬형상으로 실장하고 있다. 각 반도체장치(10)의 실장방향을 알 수 있도록 봉지체(7)의 표면에는 마크(22)가 형성되어 있다. 또한, (21)은 전자기기PC와 접속하기 위한 커넥터단자이다. 이 여러개의 반도체장치(10) 중 봉지체(7)의 한측면(7A)와 직교하는방향(도면 중 Y방향)으로 실장된 여러개의 반도체장치(10)의 각각은 도 4(도 3의 주요부 확대평면도)에 도시한 바와 같이 인접하는 반도체장치(10) 사이에 있어서, 한쪽의 반도체장치(10)의 봉지체(7)의 한측면(7A)에 배열된 외부리이드(3A)와 다른 쪽 반도체장치(10)의 봉지체(7)의 다른 측면(7B)에 배열된 외부리이드(3B)가 대향하는 상태로 되지만, 한쪽의 반도체장치(10)의 외부리이드(3A)는 그의 반도체칩(1)의 외부단자BP와 전기적으로 접속되고, 다른 쪽의 반도체장치(10)의 외부리이드(3B)는 그의 반도체칩(1)의 외부단자BP와 전기적으로 접속되어 있지 않으므로, 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3A)끼리가 대향하는 일은 없다. 따라서, 한쪽의 반도체장치(10)의 외부리이드(3A)와 다른 쪽의 반도체장치(10)의 외부리이드(3B) 사이의 격리영역을 축소 또는 폐지하고, 실장시에 반도체장치(10)의 위치어긋남이나 땜납의 돌출 등이 발생해도, 봉지체(7)의 한측면(7A)와 직교하는 방향으로 실장된 여러개의 반도체장치(10)에 있어서 인접하는 반도체장치(10)사이에서의 단락은 발생하지 않는다.

즉, 인접하는 반도체장치(10) 사이의 인접하는 리이드(3A), (3B)를 전기적으로 분리하기 위해, 통상 실장기판(11)에 형성되는 랜드(푸트프린트(foot print))(13)은 소정의 간격(리이드의 위치맞춤 정밀도 여유, 땜납의 돌출폭)을 고려해서 배치되지만, 본 실시예의 경우 도 10a 및 도 10b에 도시한 바와 같이, 인접하는 배선(12)의 랜드(13)은 상기 소정의 간격 이하로 설정 또는 간격을 없애서 일체로 형성하는 것이 가능하다 또한, 배선(12)를 봉지체(7)의 하부에 있어서 거의 직선적으로 레이아웃할 수 있으므로, 실장효율을 향상시키는 것이 가능하다.

또, 봉지체(7)의 한측면(7A)와 직교하는 방향(도면 중 Y방향)으로 실장된 여러개의 반도체장치(10)의 각각은 인접하는 반도체장치(10) 사이에 있어서, 한쪽의 반도체장치(10)의 봉지체(7)의 한측면(7A)에 배열된 외부리이드(3A)와 다른 쪽의 반도체장치(10)의 봉지체(7)의 한측면(7A)에 배열된 외부리이드(3A) 사이에 한쪽의 반도체장치(10)의 봉지체(7)의 다른 측면(7B)에 배열된 외부리이드(3B)가 존재하지만, 이 한쪽의 반도체장치(10)의 봉지체(7)의 다른 측면(7B)에 배열된 외부리이드(3B)는 그의 반도체칩(1)의 외부단자BP와 전기적으로 접속되어 있지 않으므로, 한쪽의 반도체장치(10)의 외부리이드(3A)와 다른 쪽의 반도체장치(10)의 외부리이드(3A) 사이에 이들과 다른 기능을 갖는 외부리이드가 존재하는 일은 없다. 따라서. 칩선택 리이드(3A)(CS) 등의 전기적으로 독립시키지 않으면 안되는 리이드는 배열(둘러치는) 배선(12A)가 필요하게 되지만, 그 이외의 공통신호 리이드, 전원 리이드에 관해서는 실장기판(11)상으로 연장하는 배선(12)를 배열하지 않고 봉지체(7)의 한측면(7B)와 직교하는 방향으로 실장된 각 반도체장치(10)의 동일 기능의 외부리이드(3A)를 대략 직선의 배선(12)에 의해 전기적으로 접속할 수 있다.

이와 같이 본 실시형태에 의하면 이하의 효과가 얻어진다.

[1] 실장기판(11)의 실장면상에 여러개 실장되는 반도체장치(10)에 있어서, 평면이 직사각형 형상인 봉지체(7)에 의해 반도체칩(1)을 봉지하고, 상기 봉지체(7)의 한측면(7A)에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3A)를 여러개 배열하고, 상기 봉지체(7)의 한측면(7A)와 대향하는 다른 측면(7B)에 그의 측면을 따라서 상기 반도체칩(1)의외부단자BP와 전기적으로 접속되지 않는 외부리이드(3B)를 여러개 배열한 구조로 구성하는 것에 의해, 이 반도체장치(10)을 실장기판(11)의 실장면상에 방향을 일치시킨 상태에서 봉지체(7)의 한측면(7A)와 직교하는 방향으로 여러개 실장한 경우, 이 방향과 인접하는 반도체장치(10) 사이에 있어서 한쪽의 반도체장치(10)의 봉지체(7)의 한측면(7A)에 배열된 외부리이드(3A)와 다른쪽의 반도체장치(10)의 봉지체(7)의 다른 측면(7B)에 배열된 외부리이드(3B)가 대향하는 상태로 되지만, 한쪽의 반도체장치(10)의 외부리이드(3A)는 그의 반도체칩(1)의 외부단자BP와 전기적으로 접속되고, 다른 쪽의 반도체장치(10)의 외부리이드(3B)는 그의 반도체칩(1)의 외부단자BP와 전기적으로 접속되어 있지 않으므로, 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3A)끼리가 대향하는 일은 없다. 따라서, 한쪽의 반도체장치(10)의 외부리이드(3A)와 다른 쪽의 반도체장치(10)의 외부리이드(3B)사이의 격리영역을 축소 또는 폐지하고 실장시에 반도체장치(10)의 위치어긋남이나 땜납의 돌출 등이 발생해도, 봉지체(7)의 한측면(7A)와 직교하는 방향으로 실장된 여러개의 반도체장치(10)에 있어서 인접하는 반도체장치(10) 사이에서의 단락은 발생하지 않는다. 이 결과, 한쪽의 반도체장치(10)의 외부리이드(3A)와 다른 쪽의 반도체장치(10)의 외부리이드(3B) 사이의 격리영역을 축소 또는 폐지할 수 있으므로, 이것에 상당하는 분만큼 실장기판(11)상에서의 반도체장치(10)의 고밀도 실장이 가능하게 된다.

또, 반도체장치(10)을 실장기판(11)의 실장면상에 방향을 일치시킨 상태에서 봉지체(7)의 한측면(7A)와 직교하는 방향으로 여러개 실장한 경우, 이 방향과 인접하는 반도체장치(10) 사이에 있어서 한쪽의 반도체장치(10)의 봉지체(7)의 한측면(7A)에 배열된 외부리이드(3A)와 다른 쪽의 반도체장치(10)의 봉지체(7)의 한측면(7A)에 배열된 외부리이드(3A) 사이에 한쪽의 반도체장치(10)의 봉지체(7)의 다른 측면(7B)에 배열된 외부리이드(3B)가 존재하지만, 이 한쪽의 반도체장치(10)의 봉지체(7)의 다른 측면(7B)에 배열된 외부리이드(3B)는 그의 반도체칩(1)의 외부단자BP와 전기적으로 접속되어 있지 않으므로, 한쪽의 반도체장치(10)의 외부리이드(3A)와 다른 쪽의 반도체장치(10)의 외부리이드(3A) 사이에 이들과 다른 기능을 갖는 외부리이드가 존재하는 일은 없다. 따라서, 실장기판(11)상을 Y방향으로 연장하는 배선(12)를 배열하지 않고, 봉지체(7)의 한측면(7A)와 직교하는 방향으로 실장된 각 반도체장치(10)의 동일 기능의 외부리이드(3A)를 전기적으로 접속할 수 있다. 이 결과, 배선(12)의 배열 영역을 축소 또는 폐지할 수 있으므로, 이것에 상당하는 분만큼 실장기판(11)상에서의 반도체장치(10)의 고밀도 실장이 가능하게 된다.

또, 봉지체(7)의 한측면(7A)에 배열된 외부리이드(3A)와 봉지체(7)의 다른 측면(7B)에 배열된 외부리이드(3B)에 의해 실장기판(11)상에 반도체장치(10)을 안정한 상태로 고정시킬 수 있으므로, 반도체장치(10)의 내충격성을 높일 수 있다.

[2] 메모리카드(전자장치)에 있어서, 평면이 직사각형 형상인 봉지체(7)에 의해 반도체칩(1)을 봉지하고, 상기 봉지체(7)의 한측면(7A)에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3A)를 여러개 배열하고, 상기 봉지체(7)의 한측면(7A)와 대향하는 다른 측면(7B)에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속되지 않는 외부리이드(3B)를 여러개 배열한 구조의 반도체장치(1())을 실장기판(11)의 실장면상에 방향을 일치시킨 상태에서 봉지체(7)의 한측면(7A)와 직교하는 방향으로 여러개 실장하는 것에 의해, 인접하는 반도체장치(10) 사이에 있어서 한쪽의 반도체장치(10)의 외부리이드(3A)와 다른쪽의 반도체장치(10)의 외부리이드(3B) 사이의 격리영역을 축소 또는 폐지할 수 있으므로, 이것에 상당하는 분만큼 메모리카드의 평면사이즈를 축소할 수 있다. 또, 실장기판(11)상으로 연장하는 배선(12)를 배열하지 않고 봉지체(7)의 한측면(7A)와 직교하는 방향으로 실장된 각 반도체장치(10)의 동일 기능의 외부리이드(3A)를 전기적으로 접속할 수 있으므로, 배선(12)의 배열 영역을 축소 또는 폐지할 수 있어 이것에 상당하는 분만큼 메모리카드의 평면사이즈를 축소할 수 있다.

실시형태2

도 5는 본 발명의 실시형태2인 반도체장치의 봉지체의 상부를 제거한 상태의 평면도이다.

도 5에 도시한 바와 같이, 본 실시형태의 반도체장치(10)은 TSOP구조로 구성되어 있다. 이 TSOP구조의 반도체장치(10)은 4개의 탭지지용 리이드(5)의 각각에 의해 지지된 탭(4)의 한 표면상에 반도체칩(1)을 탑재하고 있다.

상기 반도체칩(1)의 한변의 외측에는 그의 한번을 따라서 여러개의 내부리이드(2A)가 배열되어 있다. 이 여러개의 내부리이드(2A)의 각각은 반도체칩(1)의 주면의 한변측에 배열된 여러개의 외부단자BP의 각각과 본딩와이어(6)을 거쳐서 전기적으로 접속되어 있다.

상기 반도체칩(1)의 한변과 대향하는 다른 변(다른 쪽의 긴 변)의 외측에는 그의 다른 변을 따라서 여러개의 내부리이드(2B)가 배열되어 있다. 이 여러개의 내부리이드(2B)의 각각은 반도체칩(1)의 외부단자BP와 전기적으로 접속되어 있지 않다.

상기 반도체칩(1)의 한변과 직교하는 2개의 변 중 한쪽변의 외측에는 그의 변을 따라서 여러개의 내부리이드(2C)가 배열되어 있다. 이 여러개의 내부리이드(2C)의 각각은 반도체칩(1)의 주면의 한변과 직교하는 2개의 변 중 한쪽 변에 배열된 여러개의 외부단자BP의 각각과 본딩와이어(6)을 거쳐서 전기적으로 접속되어 있다.

상기 반도체칩(1), 내부리이드(2A), 내부리이드(2B), 내부리이드(2C), 탭(4), 탭지지용 리이드(5) 및 본딩와이어(6) 등은 평면이 직사각형 형상으로 형성된 봉지체(7)에 의해 봉지되어 있다.

상기 봉지체(7)의 한측면(7A)에는 그의 측면을 따라서 여러개의 외부리이드(3A)가 배열되어 있다. 또, 봉지체(7)의 한측면(7A)와 대향하는 다른 측면(7B)에는 그의 측면을 따라서 여러개의 외부리이드(3B)가 배열되어 있다. 또, 봉지체(7)의 한측면과 직교하는 2개의 측면 중 한쪽의 측면(7C)에는 그의 측면을 따라서 여러개의 외부리이드(3C)가 배열되어 있다. 이 외부리이드(3A), (3B), (3C)의 각각은 갈매기날개형상으로 성형되어 있다.

상기 여러개의 외부리이드(3A)의 각각은 반도체칩(1)의 한변의 외측에 배열된 여러개의 내부리이드(2A)의 각각과 일체화되어 있다. 또, 여러개의 외부리이드(3B)의 각각은 반도체칩(1)의 다른 변의 외측에 배열된 여러개의 내부리이드(2B)의 각각과 일체화되어 있다. 또, 여러개의 외부리이드(3C)의 각각은 반도체칩(1)의 한변과 직교하는 2개의 변 중 한쪽변의 외측에 배열된 여러개의 내부리이드(2C)의 각각과 일체화되어 있다. 즉, 본 실시형태의 반도체장치(10)은 봉지체(7)의 한측면(7A)에 그의 한측면을 따라서 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3A)를 여러개 배열하고, 봉지체(7)의 한측면(7A)와 대향하는 다른 측면(7B)에 그의 측면을 따라서 반도체칩(1)의 외부단자BP와 전기적으로 접속되지 않는 외부리이드(3B)를 여러개 배열하고, 봉지체(7)의 한측면(7A)와 직교하는 2개의 측면 중 한쪽의 측면(7C)에 그의 측면을 따라서 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3C)를 여러개 배열한 3방향 리이드 배열구조로 구성되어 있다.

이와 같이 구성된 반도체장치(10)은 1개의 메모리시스템으로서 예를 들면 퍼스널컴퓨터, 오피스컴퓨터 등의 전자기기에 증설 접속되는 메모리카드(전자장치)의 실장기판상에 여러개 규칙적으로 실장된다.

상기 메모리카드(전자장치)는 도 6(평면도)에 도시한 바와 같이, 여러개의 반도체장치(10)을 실장기판(11)의 실장면상에 방향을 일치시킨 상태에서 행렬형상으로 실장하고 있다. 이 여러개의 반도체장치(10) 중 봉지체(7)의 한측면(7A)와 동일의 방향(도면 중 X방향)으로 실장된 여러개의 반도체장치(10)의 각각은 도 7(도 6의 주요부 확대평면도)에 도시한 바와 같이, 인접하는 반도체장치(10) 사이에 있어서 한쪽의 반도체장치(10)의 봉지체(7)의 측면(7C)에 배열된 외부리이드(3C)와 다른 쪽의 반도체장치(10)의 봉지체(7)의 측면(7C)에 배열된 외부리이드(3C)가 대향하는 일은 없다. 따라서, 한쪽의 반도체장치(10)과 다른 쪽의 반도체장치(10) 사이를 채운 상태로 실장하고, 실장시에 반도체장치(10)의 위치어긋남이나 땜납이 삐져나오는 것 등이 발생해도 봉지체(7)의 한측면(7A)와 동일한 방향으로 실장된 여러개의 반도체장치(10)의 각각에 있어서는 인접하는 반도체장치(10) 사이에서의 단락은 발생하지 않는다. 이 결과, 봉지체(7)의 한측면(7A)와 동일한 방향으로 여러개의 반도체장치(10)의 각각을 채운 상태로 실장할 수 있으므로, 이것에 상당하는 분만큼 반도체장치(10)의 고밀도 실장이 가능하게 된다.

또, 봉지체(7)의 한측면(7A)와 동일한 방향(도면 중 X방향)으로 실장된 여러개의 반도체장치(10)의 각각은 인접하는 반도체장치(10) 사이에 있어서, 한쪽의 반도체장치(10)의 봉지체(7)의 측면(7C)에 배열된 외부리이드(3C)와 다른 쪽의 반도체장치(10)의 봉지체(7)의 측면(7C)에 배열된 외부리이드(3C) 사이에 이것과 다른 기능의 다른 외부리이드가 존재하는 일은 없다. 따라서 실장기판의 내부에서 X방향으로 연장하는 배선(도시하지 않음)을 배열하지 않고 봉지체(7)의 한측면(7A)와 동일한 방향으로 실장된 각 반도체장치(10)의 동일 기능의 외부리이드(3C)를 전기적으로 접속할 수 있다. 이 결과, X방향으로 연장하는 배선의 배열영역을 축소 또는 폐지할 수 있으므로, 이것에 상당하는 분만큼 반도체장치(10)의 고밀도 실장이 가능하게 된다. 즉, Y방향에 있어서 인접하는 반도체장치(10)의 외부리이드(3A)끼리를 실장기판의 표면배선층(12)에 의해 직선적으로 접속하고, X방향에 있어서 인접하는 반도체장치(10)의 외부리이드(3C)끼리를 실장기판의 내부배선의 특정된 한층만으로 직선적으로 접속하는 것에 의해, 배선의 배열영역을 극력 저감할 수 있다.

실시형태3

도 8은 본 발명의 실시형태3인 반도체장치의 봉지체의 상부를 제거한 상태의 평면도이다.

도 8에 도시한 바와 같이 본 실시형태의 반도체장치(10)은 평면이 직사각형상인 봉지체(7)에 의해 반도체칩(1)을 봉지하고, 상기 봉지체(7)의 한측면(7A)의 일부 영역에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3A)를 여러개 배열하고, 상기 봉지체(7)의 한측면(7A)의 다른 부 영역에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속되지 않는 외부리이드(3B)를 여러개 배열하고, 상기 봉지체(7)의 한측면(7A)의 일부 영역과 대향하는 다른 측면(7B)의 일부 영역에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속되지 않는 외부리이드(3B)를 여러개 배열하고, 상기 봉지체(7)의 한측면(7A)의 다른부 영역과 대향하는 다른 측면(7B)의 다른부 영역에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3A)를 여러개 배열한 2방향 리이드 배열구조로 구성되어 있다.

이와 같이 구성된 반도체장치(10)을 실장기판의 실장면상에 방향을 일치시킨 상태에서 행렬형상으로 여러개 실장한 경우, 봉지체(7)의 한측면(7A)와 직교하는 방향으로 실장된 여러개의 반도체장치(10)의 각각은 인접하는 반도체장치(10) 사이에 있어서 상술한 실시형태1과 마찬가지로, 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3A)끼리가 대향하는 일은 없다. 또, 봉지체(7)의 한측면(7A)와 직교하는 방향으로 실장된 여러개의 반도체장치(10)의 각각은 인접하는 반도체장치(10) 사이에 있어서, 한쪽의 반도체장치(10)의 외부리이드(3A)와 다른 쪽의 반도체장치의 외부리이드(3A) 사이에 이들과 다른 기능을 갖는 외부리이드가 존재하는 일은 없다. 따라서, 상술한 실시형태1과 마찬가지로, 반도체장치(10)의 고밀도 실장이 가능하게 된다.

실시형태4

도 9는 본 발명의 실시형태4인 반도체장치의 봉지체의 상부를 제거한 상태의 평면도이다.

도 9에 도시한 바와 같이 본 실시형태의 반도체장치는 평면이 직사각형 형상인 봉지체(7)에 의해 반도체칩(1)을 봉지하고, 상기 봉지체(7)의 한측면(7A)의 일부 영역에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3A)를 여러개 배열하고, 상기 봉지체(7)의 한측면(7A)의 다른 부 영역에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속되지 않는 외부리이드(3B)를 여러개 배열하고, 상기 봉지체(7)의 한측면(7A)의 일부 영역과 대향하는 다른 측면(7B)의 일부 영역에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속되지 않는 외부리이드(3B)를 여러개 배열하고, 상기 봉지체(7)의 한측면(7A)의 다른부 영역과 대향하는 다른 측면(7B)의 다른부 영역에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3A)를 여러개 배열하고, 상기 봉지체(7)의 한측면(7A)와 직교하는 2개의측면 중 한쪽의 측면(7C)에 그의 측면을 따라서 상기 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3C)를 여러개 배열한 3방향 리이드 배열구조로 구성되어 있다.

이와 같이 구성된 반도체장치(10)을 실장기판의 실장면상에 방향을 일치시킨 상태에서 행렬형상으로 여러개 실장한 경우, 봉지체(7)의 한측면(7A)와 동일한 방향으로 실장된 여러개의 반도체장치(10)의 각각은 인접하는 반도체장치(10) 사이에 있어서 상술한 실시형태2와 마찬가지로, 반도체칩(1)의 외부단자BP와 전기적으로 접속된 외부리이드(3C)끼리가 대향하는 일은 없다. 따라서, 상술한 실시형태2와 마찬가지로, 반도체장치(10)의 고밀도 실장이 가능하게 된다.

실시형태5

도 15는 본 실시형태5인 반도체장치(패키지)의 평면도이다.

반도체장치(100)은 실시형태1과 마찬가지로 TSOP구조로 구성되어 있고, 그의 봉지체(7)에는 도 17에 도시한 플래시메모리(EEPROM)을 탑재하는 반도체칩(23)이 봉지되어 있다. 반도체칩(23)의 주면에는 매트릭스형상으로 배치된 여러개의 메모리셀을 갖는 4개의 메모리어레이MA, 각 메모리어레이MA에서 소정의 메모리셀을 선택하기 위한 워드디코더WD 및 컬럼디코더CD와 센스회로SA, 전원전압 발생회로와 승압회로 등을 포함하는 전원회로VC, 입출력회로 등의 외부장치와의 인터페이스로 되는 제어회로CC가 각각 형성되어 있다. 또, 본딩패드BP는 반도체칩(23)의 1개의 긴 변만을 따라서 배치되고 그 근방에 상기 전원회로VC, 제어회로CC 등의 주변회로를 적극적으로 배치하는 것에 의해, 칩내의 신호배선의 길이를 동일하게 하는 것 및칩사이즈의 축소화를 도모하고 있다. 각 본딩패드BP는 도 15 및 16에 도시하는 Vcc, Vss, I/O 등의 전원핀 및 신호핀과 대응하고 있고, 각 본딩패드BP는 대응하는 전원핀 및 신호핀의 내부리이드(2A)와 와이어(6)에 의해 접속되어 있다. 각 핀기능에 대해서는 도 16에 기재되어 있는 바와 같고, NC핀(3B)은 패키지내에 있어서 전기적으로 플로팅상태로 되어 있다.

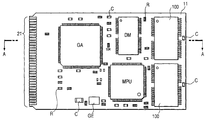

상기 반도체장치(100)은 도 18 및 도 19에 도시한 바와 같이 실장기판(11)상에 여러개 실장되고 메모리카드의 본체를 구성한다. 도 18은 실장기판(11)의 표면측의 평면도이고, 도 19는 실장기판(11)의 상기 표면측과 반대의 이면측의 평면도이다. 또, 도 20은 도 18 및 도 19에 있어서의 A-A선을 따라 자른 단면도를 도시한 것이다.

상기 실장기판(11)의 이면측에는 또한 게이트어레이칩을 탑재한 QFP형 패키지GA, 마이크로 컴퓨터를 탑재한 QFP형 패키지MPU 및 DRAM칩을 탑재한 TSOP형 패키지DM이 실장되어 있다. 또한, 실장기판(11)상에는 임피던스정합 등을 실행하기 위한 칩콘덴서C 및 칩저항R 및 클럭을 공급하는 클럭발생기GE 등이 실장되어 있다.

상기 실장기판(11)상에 탑재된 패키지는 도 21에 도시한 ATA(ATAttachment)카드(24)를 구성한다. 이하, ATA카드(24)의 시스템구성을 간단히 설명한다.

도 21의 ATA카드(24)는 AT호환기가 하드디스크로 액세스하는 데 사용하는 인터페이스와 프로토콜을 준거한 카드로서, PCMCIA(Personal Computer Memory Card International Association)의 메모리카드 표준화단체에 의해 규격화되어 있다.

(25)는 ATA카드의 핀커넥터부로서 외부단자(21)에 대응한다. 이외부단자(21)을 통해서 PC(Personal Computer)나 PDA(Personal Digital Assistant) 등과 신호의 수수를 실행한다. 이 외부단자는 PCMCIA에 의해, 외부단자수, 단자명, 단자번호가 결정되고 있다.

외부로부터의 데이타나 어드레스는 신호선(26)을 거쳐서 우선 게이트어레이GA로 입력된다. 게이트어레이GA는 PCMCIA인터페이스PCIN의 제어, 마이크로 컴퓨터MPU의 제어, DRAM의 제어, 플래시메모리(100)의 제어 및 플래시메모리(100)과 PCMCIA인터페이스 사이의 데이타 전송제어를 실행한다. 카드내의 각 소자의 데이타나 어드레스의 수수는 (27)의 로컬데이타버스, 로컬어드레스버스를 거쳐서 실행된다.

MPU는 외부로부터의 코맨드를 받아서 데이타의 제어를 실행한다. 외부로부터의 데이타는 라이트나 리드 어느 쪽도 고속데이타처리를 위해, DRAM을 거쳐서 플래시메모리(100)으로 또는 플래시메모리(100)에서 DRAM으로 보내진다. 또, 어느 플래시메모리(100)에 데이타를 라이트할 것인지, 어느 플래시메모리(100)에서 데이타의 리드를 실행할 것인지를 CE(Chip Enable)버스(28)을 거쳐서 제어한다. 또한, MPU는 플래시메모리(100)에 기억되어 있는 데이타의 신뢰성 향상을 위해, ECC(Error Check Correction)연산처리(각 섹터의 리라이트 회수관리, 불량섹터의 액세스관리), 웨어레벨링(ware leveling)(각 섹터의 리라이트 회수의 평균화)의 관리를 실행한다.

이상, 본 발명자에 의해 이루어진 발명을 상기 실시형태에 따라서 구체적으로 설명했지만, 본 발명은 상기 실시형태에 한정되는 것이 아니고 그 요지를 이탈하지 않는 범위에 있어서 여러가지로 변경가능한 것은 물론이다.

예를 들면, 본 발명은 세라믹스로 이루어지는 봉지체에 의해 반도체칩을 봉지하는 반도체장치에 적용할 수 있다.

또, 본 발명은 LOC(Lead On Chip)구조 또는 COL(Chip On Lead)구조의 반도체장치에 적용할 수 있다.

또, 본 발명은 SRAM(Static Random Access Memory), EPROM(Electrically Programmable Read Only Memory), EEPROM(Electrically Erasable Programmable ROM), 플래시메모리(전체 비트 일괄소거형 EEPROM)등으로 이루어지는 기억회로 시스템으로 구성된 반도체칩을 탑재하는 반도체장치에 적용할 수 있다.

Claims (38)

- 그의 주면에 여러개의 본딩패드와 반도체소자를 갖고 또한 대략 장방형상이며, 제1 방향으로 연장하는 한쌍의 긴 변과 상기 제1 방향과 대략 수직방향인 제2 방향으로 연장하는 한쌍의 짧은 변을 갖고, 상기 여러개의 본딩패드가 상기 한쌍의 긴 변의 한쪽을 따라서 배치되는 반도체칩,상기 반도체칩의 외측에 배치되고 상기 한쌍의 긴 변의 한쪽을 따라서 배치되며, 그의 각각이 내부리이드부와 외부리이드를 갖고, 상기 내부리이드부의 선단부가 본딩와이어에 의해 대응하는 본딩패드에 전기적으로 접속되는 여러개의 제1 리이드,상기 반도체칩의 외측에 배치되고 상기 한쌍의 긴 변의 다른 쪽을 따라서 배치되며, 그의 각각이 내부리이드부와 외부리이드를 갖고, 상기 반도체칩과는 전기적으로 접속되지 않는 여러개의 제2 리이드 및상기 반도체칩, 상기 여러개의 제1 리이드의 내부리이드부, 상기 여러개의 제 2 리이드의 내부리이드부 및 상기 본딩와이어를 봉지하고 대략 장방형상이며, 상기 제1방향으로 연장하는 한쌍의 긴 변과 상기 제2 방향으로 연장하는 한쌍의 짧은 변을 갖는 봉지체를 포함하고,상기 여러개의 제1 리이드의 외부리이드는 상기 봉지체의 한쌍의 긴 변의 한쪽에서 돌출하고, 상기 여러개의 제2 리이드의 외부리이드는 상기 봉지체의 한쌍의 긴 변의 다른 쪽에서 돌출하고, 상기 여러개의 제1 리이드의 외부리이드와 대향하는 위치에 배치된 상기 여러개의 제2 리이드의 외부리이드의 각각은 상기 봉지체 외측에 있어서 전기적으로 접속되어 있는 반도체장치.

- 제1항에 있어서,상기 제1 리이드의 외부리이드와 상기 제2 리이드의 외부리이드는 상기 제2 방향과 평행한 방향으로 상기 봉지체에서 돌출하고, 대향하는 상기 제1 및 제2 리이드의 외부리이드는 상기 제2 방향에 있어서 대략 일직선상에 배치되는 반도체장치.

- 제1항에 있어서,상기 대향하는 제1 및 제2 리이드는 봉지체 외측의 배선에 의해 접속되는 반도체장치.

- 제1항에 있어서,상기 반도체칩은 그의 주면에 형성된 메모리어레이 및 상기 메모리어레이와 상기 본딩패드 사이에 배치된 입출력회로를 갖는 반도체장치.

- 그의 주면에 여러개의 배선을 갖는 실장기판과 상기 실장기판의 주면상에 탑재된 여러개의 반도체패키지를 포함하는 반도체장치로서,상기 여러개의 반도체패키지의 각각은그의 주면에 여러개의 본딩패드와 반도체소자를 갖고 또한 대략 장방형이며, 제1 방향으로 연장하는 한쌍의 긴 변과 상기 제1 방향과 대략 수직방향인 제2 방향으로 연장하는 한쌍의 짧은 변을 갖고, 상기 여러개의 본딩패드가 상기 한쌍의 긴 변의 한쪽을 따라서 배치되는 반도체칩,상기 반도체칩의 외측에 배치되고 상기 한쌍의 긴 변의 한쪽을 따라서 배치되며, 그의 각각이 내부리이드부와 외부리이드를 갖고, 상기 내부리이드부의 선단부가 본딩와이어에 의해 대응하는 본딩패드에 전기적으로 접속되는 여러개의 제1 리이드,상기 반도체칩의 외측에 배치되고 상기 한쌍의 긴 변의 다른 쪽을 따라서 배치되며, 그의 각각이 내부리이드부와 외부리이드를 갖고, 상기 반도체칩과는 전기적으로 접속되지 않는 여러개의 제2 리이드 및상기 반도체칩, 상기 여러개의 제1 리이드의 내부리이드부, 상기 여러개의 제 2 리이드의 내부리이드부 및 상기 본딩와이어를 봉지하고 대략 장방형상이며, 상기 제1 방향으로 연장하는 한쌍의 긴 변과 상기 제2 방향으로 연장하는 한쌍의 짧은 변을 갖는 봉지체를 구비하고,상기 여러개의 제1 리이드의 외부리이드는 상기 봉지체의 한쌍의 긴 변의 한쪽에서 돌출하고, 상기 여러개의 제2 리이드의 외부리이드는 상기 봉지체의 한쌍의 긴 변의 다른 쪽에서 돌출하고,상기 여러개의 반도체패키지는 인접하는 반도체패키지의 제1 리이드와 제2 리이드가 대향하도록 상기 제2 방향에 있어서 소정의 간격으로 배치되고,상기 인접하는 반도체패키지의 제1 리이드와 제2 리이드의 외부리이드의 선단은 상기 실장기판의 주면상에 형성된 배선에 의해 접속되어 있는 반도체장치.

- 제5항에 있어서,상기 인접하는 반도체패키지의 제1 리이드의 선단부는 상기 배선의 제1 랜드부상에 배치되고, 상기 인접하는 반도체패키지의 제2 리이드의 선단부는 상기 배선의 제2 랜드부상에 배치되고, 상기 제1 랜드부와 상기 제2 랜드부의 간격은 상기 외부리이드의 간격보다 좁은 반도체장치.

- 제5항에 있어서,상기 인접하는 반도체패키지의 제1 리이드의 선단부는 상기 배선의 제1 랜드부상에 배치되고, 상기 인접하는 반도체패키지의 제2 리이드의 선단부는 상기 배선의 제2 랜드부상에 배치되고, 상기 제1 랜드부와 상기 제2 랜드부는 일체로 형성되어 있는 반도체장치.

- 한쌍의 긴변과 상기 긴변과 수직방향으로 연장하는 한쌍의 짧은변으로 이루어지고, 그의 주면상에 여러개의 배선을 갖고, 상기 배선이 각각 상기 긴변을 따라서 연장하는 장방형상의 실장기판 및상기 실장기판의 주면상에 탑재된 여러개의 반도체메모리장치를 포함하고,상기 반도체메모리장치의 각각은그의 주면상에 여러개의 외부단자를 갖고, 제1 방향으로 연장하는 한쌍의 긴변과 상기 제1 방향과 대략 수직인 제2 방향으로 연장하는 한쌍의 짧은변을 갖고, 상기 외부단자가 상기 반도체칩의 긴변의 한쪽을 따라서 배치되는 장방형상의 반도체칩,상기 반도체칩의 한쌍의 긴변의 한쪽을 따라서 배치되고, 그의 각각이 내부리이드부와 외부리이드부를 갖고, 상기 내부리이드부의 선단부가 대응하는 외부단자에 직접 접속되는 여러개의 제1 리이드,상기 반도체칩의 한쌍의 긴변의 다른쪽을 따라서 배치되고, 그의 각각이 상기 제1 리이드의 한쪽과 각각 대향해서 배치되고, 내부리이드부와 외부리이드부를 갖고, 상기 반도체칩에 직접 접속되지 않는 여러개의 제2 리이드 및상기 반도체칩, 상기 제1 리이드의 내부리이드부 및 상기 제2 리이드의 내부리이드부를 봉지하고, 상기 제1 방향으로 연장하는 한쌍의 긴변과 상기 제2 방향으로 연장하는 한쌍의 짧은변을 갖는 장방형상의 형태로 이루어지는 봉지체를 포함하고,상기 제1 리이드의 외부리이드는 상기 봉지체의 한쌍의 긴변의 한쪽에서 돌출하고, 상기 제2 리이드의 외부리이드는 상기 한쌍의 긴변의 다른쪽에서 돌출하고,상기 제1 리이드의 하나와 상기 제2 리이드의 하나는 각각 상기 배선중의 하나에 의해 접속되는 반도체장치.

- 제8항에 있어서,상기 제2 리이드의 하나는 상기 제1 리이드의 하나와 대향해서 배치되는 반도체장치.

- 제8항에 있어서,상기 제2 리이드의 전부는 각각 상기 제1 리이드와 대향해서 배치되는 반도체장치.

- 제8항에 있어서,상기 여러개의 반도체메모리장치는 상기 실장기판의 긴변의 한쪽을 따라서 배치되는 반도체장치.

- 제11항에 있어서,상기 여러개의 배선은 상기 여러개의 반도체메모리장치의 하부로 연장하는 반도체장치.

- 제12항에 있어서,상기 여러개의 배선은 서로 평행하게 배치되는 반도체장치.

- 제8항에 있어서,상기 반도체메모리장치의 하나와 상기 반도체메모리장치의 다른 하나는 서로 인접해서 배치되고, 상기 반도체메모리장치의 하나의 상기 제2 리이드와 상기 반도체메모리장치의 다른 하나의 상기 제1 리이드는 서로 인접배치되는 반도체장치.

- 제14항에 있어서,상기 반도체메모리장치의 상기 제1 리이드와 상기 제2 리이드는 상기 배선중의 하나에 의해 직접 접속되는 반도체장치.

- 제8항에 있어서,상기 여러개의 제1 리이드와 제2 리이드는 땜납에 의해 상기 실장기판에 접착되는 반도체장치.

- 제8항에 있어서,상기 실장기판의 짧은변의 한쪽을 따라 배치되는 여러개의 커넥터단자를 더 포함하는 반도체장치.

- 제8항에 있어서,상기 실장기판상에 8개의 반도체메모리장치가 탑재되는 반도체장치.

- 제8항에 있어서,상기 배선중의 하나는 상기 여러개의 장치에 공통으로 신호를 입력하는 반도체장치.

- 그의 주면상에 여러개의 배선을 갖는 실장기판 및상기 실장기판의 주면상에 탑재된 여러개의 반도체메모리장치를 포함하고,상기 반도체메모리장치의 각각은그의 주면상에 여러개의 외부단자를 갖고, 제1 방향으로 연장하는 한쌍의 긴변과 상기 제1 방향과 수직인 제2 방향으로 연장하는 한쌍의 짧은변을 갖고, 상기 외부단자가 상기 반도체칩의 한쌍의 긴변의 한쪽을 따라서 배치되는 장방 형상의 반도체칩,상기 반도체칩의 한쌍의 긴변의 한쪽을 따라 배치되고, 그의 각각이 내부리이드부와 외부리이드부를 갖고, 상기 내부리이드부의 선단부가 대응하는 외부단자에 직접 접속되는 여러개의 제1 리이드,상기 반도체칩의 한쌍의 긴변의 다른쪽을 따라 배치되고, 그의 각각이 상기 제1 리이드의 한쪽과 각각 대향해서 배치되고, 내부리이드부와 외부리이드부를 갖고, 상기 반도체칩에 직접 접속되지 않는 여러개의 제2 리이드 및상기 반도체칩, 상기 제1 리이드의 내부리이드부 및 상기 제2 리이드의 내부리이드부를 봉지하고, 상기 제1 방향으로 연장하는 한쌍의 긴변과 상기 제2 방향으로 연장하는 한쌍의 짧은변을 갖는 장방형상의 형태로 이루어지는 봉지체를 포함하고,상기 제1 리이드의 외부리이드부는 상기 봉지체의 한쌍의 긴변의 한쪽에서 돌출하고, 상기 제2 리이드의 외부리이드부는 상기 봉지체의 상기 한쌍의 긴변의 다른쪽에서 돌출하고,상기 제1 리이드의 하나 및 상기 제1 리이드의 하나와 대향하는 상기 제2 리이드의 하나는 상기 여러개의 배선중에서 동일 배선에 의해 서로 접속되는 반도체장치.

- 제20항에 있어서,상기 제2 리이드의 전부는 각각 상기 제1 리이드의 관계와는 반대로 배치되는 반도체장치.

- 제20항에 있어서,상기 여러개의 배선은 상기 여러개의 반도체메모리장치의 하부로 연장하고, 상기 제2 방향을 따라서 배치되는 반도체장치.

- 제22항에 있어서,상기 여러개의 배선은 서로 평행하게 배치되는 반도체장치.

- 제22항에 있어서,상기 반도체메모리장치의 하나와 상기 반도체메모리장치의 다른 하나는 서로인접해서 배치되고 상기 실장기판상에 탑재되고, 상기 반도체메모리장치의 하나의 상기 제2 리이드와 상기 반도체메모리장치의 다른 하나의 상기 제1 리이드는 서로 인접 배치되는 반도체장치.

- 제24항에 있어서,상기 반도체메모리장치의 제1 리이드와 제2 리이드는 상기 동일 배선에 의해 접속되는 반도체장치.

- 제20항에 있어서,상기 여러개의 제1 리이드와 상기 제2 리이드는 땜납에 의해 상기 실장기판상에 접착되는 반도체장치.

- 제20항에 있어서,상기 실장기판상에 8개의 반도체메모리장치가 탑재되는 반도체장치.

- 제20항에 있어서,상기 동일 배선은 상기 여러개의 반도체메모리장치에 공통으로 신호를 입력하는 반도체장치.

- 한쌍의 긴변과 그의 주면상에 여러개의 배선을 갖는 실장기판 및상기 실장기판의 주면상에 탑재된 제1 및 제2 반도체메모리장치를 포함하고,상기 제1 및 제2 반도체메모리장치의 각각은제1 방향으로 연장하는 한쌍의 긴변과 상기 제1 방향과 수직인 제2 방향으로 연장하는 한쌍의 짧은 변을 갖는 장방형상의 반도체칩,상기 반도체칩의 주면상에 배치되고 상기 반도체칩의 한쌍의 긴변의 한쪽을 따라서 배치되는 여러개의 외부단자,상기 반도체칩의 한쌍의 긴변의 한쪽을 따라서 배치되고 그의 각각이 내부리이드부와 외부리이드부를 갖고, 상기 내부리이드부의 선단부가 상기 외부단자의 대응하는 하나에 직접 접속되는 여러개의 제1 리이드,상기 반도체칩의 한쌍의 긴변의 다른쪽을 따라서 배치되고 그의 각각이 상기 제1 리이드의 하나와 각각 대향해서 배치되고 내부리이드부와 외부리이드부를 갖고 상기 반도체칩에 직접 접속되지 않는 여러개의 제2 리이드,상기 반도체칩, 상기 제1 리이드의 내부리이드부 및 상기 제2 리이드의 내부리이드부를 봉지하고, 상기 제1 방향으로 연장하는 한쌍의 긴변과 상기 제2 방향으로 연장하는 한쌍의 짧은변을 갖는 장방형상의 형태로 이루어지는 봉지체를 포함하고,상기 제1 리이드의 외부리이드부는 상기 봉지체의 상기 한쌍의 긴변의 한쪽에서 돌출하고, 상기 제2 리이드의 외부리이드부는 상기 봉지체의 한쌍의 긴변의 다른쪽에서 돌출하고,상기 제1 반도체메모리장치의 제1 리이드의 하나, 상기 제2 반도체메모리장치의 상기 제1 리이드의 하나 및 상기 제1 반도체메모리장치의 제2 리이드의 하나는 모두 상기 여러개의 배선중에서 공통배선에 접속되는 반도체장치.

- 제29항에 있어서,상기 공통배선은 상기 제1 반도체메모리장치와 상기 제2 반도체메모리장치가 배치되는 방향을 따라서 연장하는 반도체장치.

- 제30항에 있어서,상기 공통배선은 상기 반도체칩의 긴변을 따라서 일직선으로 연장하는 반도체장치.

- 제29항에 있어서,상기 제1 및 제2 반도체메모리장치의 제2 리이드는 각각 상기 제1 및 제2 반도체장치의 상기 제1 리이드와 대향해서 배치되는 반도체장치.

- 제29항에 있어서,상기 배선은 상기 제1 및 제2 반도체메모리장치의 하부로 연장하는 반도체장치.

- 제33항에 있어서,상기 여러개의 배선은 서로 평행하게 배치되는 반도체장치.

- 제29항에 있어서,상기 제1 및 제2 반도체메모리장치는 서로 인접해서 배치되고, 상기 제1 반도체메모리장치의 제2 리이드와 상기 제2 반도체메모리장치의 제1 리이드는 서로 인접 배치되는 반도체장치.

- 제29항에 있어서,상기 제1 및 제2 리이드의 여러개의 외부리이드부는 땜납에 의해 상기 실장기판에 접착되는 반도체장치.

- 제29항에 있어서,상기 실장기판의 짧은변의 한쪽을 따라서 배치되는 여러개의 커넥터단자를 더 포함하는 반도체장치.

- 제29항에 있어서,상기 배선은 상기 제1 및 제2 반도체메모리장치에 신호를 공통으로 입력하는 반도체장치.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP96-118899 | 1996-05-14 | ||

| JP8118899A JPH09307058A (ja) | 1996-05-14 | 1996-05-14 | 半導体装置及びそれを用いた電子装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR970077398A KR970077398A (ko) | 1997-12-12 |

| KR100435978B1 true KR100435978B1 (ko) | 2004-08-25 |

Family

ID=14747932

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019970018462A KR100435978B1 (ko) | 1996-05-14 | 1997-05-13 | 반도체장치 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US6121681A (ko) |

| JP (1) | JPH09307058A (ko) |

| KR (1) | KR100435978B1 (ko) |

| SG (1) | SG54501A1 (ko) |

| TW (1) | TW321791B (ko) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000315776A (ja) | 1999-05-06 | 2000-11-14 | Hitachi Ltd | 半導体装置 |

| US6634561B1 (en) * | 1999-06-24 | 2003-10-21 | Sandisk Corporation | Memory card electrical contact structure |

| KR100309161B1 (ko) | 1999-10-11 | 2001-11-02 | 윤종용 | 메모리 카드 및 그 제조방법 |

| JP3645172B2 (ja) * | 2000-10-27 | 2005-05-11 | シャープ株式会社 | 半導体集積回路装置搭載用基板 |

| DE10109344C1 (de) * | 2001-02-27 | 2002-10-10 | Siemens Ag | Schaltungsanordnung mit Halbbrücken |

| JP3839267B2 (ja) * | 2001-03-08 | 2006-11-01 | 株式会社ルネサステクノロジ | 半導体装置及びそれを用いた通信端末装置 |

| US7092256B1 (en) | 2002-04-26 | 2006-08-15 | Sandisk Corporation | Retractable card adapter |

| KR100475740B1 (ko) * | 2003-02-25 | 2005-03-10 | 삼성전자주식회사 | 신호 완결성 개선 및 칩 사이즈 감소를 위한 패드배치구조를 갖는 반도체 집적 회로장치 |

| US7152801B2 (en) * | 2004-04-16 | 2006-12-26 | Sandisk Corporation | Memory cards having two standard sets of contacts |

| US7487265B2 (en) * | 2004-04-16 | 2009-02-03 | Sandisk Corporation | Memory card with two standard sets of contacts and a hinged contact covering mechanism |

| ITMI20050139A1 (it) * | 2005-01-31 | 2006-08-01 | St Microelectronics Srl | Dispositivo di memorizzazione dati rimovibile e relativo metodo di assemblaggio |

| US7710736B2 (en) * | 2005-08-02 | 2010-05-04 | Sandisk Corporation | Memory card with latching mechanism for hinged cover |

| JP2008091722A (ja) * | 2006-10-03 | 2008-04-17 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| US8395246B2 (en) * | 2007-06-28 | 2013-03-12 | Sandisk Technologies Inc. | Two-sided die in a four-sided leadframe based package |

| US8058099B2 (en) * | 2007-06-28 | 2011-11-15 | Sandisk Technologies Inc. | Method of fabricating a two-sided die in a four-sided leadframe based package |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FR489643A (fr) * | 1917-12-03 | 1919-02-25 | Felice Gilardini | Courroie pour transmissions, et procédé pour sa fabrication |

| JPH04259365A (ja) * | 1991-02-12 | 1992-09-14 | Mitsubishi Heavy Ind Ltd | 加振溶射方法 |

| US5469333A (en) * | 1993-05-05 | 1995-11-21 | International Business Machines Corporation | Electronic package assembly with protective encapsulant material on opposing sides not having conductive leads |

| US5484959A (en) * | 1992-12-11 | 1996-01-16 | Staktek Corporation | High density lead-on-package fabrication method and apparatus |

-

1996

- 1996-05-14 JP JP8118899A patent/JPH09307058A/ja active Pending

-

1997

- 1997-04-22 TW TW086105233A patent/TW321791B/zh not_active IP Right Cessation

- 1997-05-02 SG SG1997001363A patent/SG54501A1/en unknown

- 1997-05-13 KR KR1019970018462A patent/KR100435978B1/ko not_active IP Right Cessation

- 1997-05-14 US US08/856,145 patent/US6121681A/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| KR970077398A (ko) | 1997-12-12 |

| TW321791B (ko) | 1997-12-01 |

| JPH09307058A (ja) | 1997-11-28 |

| US6121681A (en) | 2000-09-19 |

| SG54501A1 (en) | 1998-11-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5780925A (en) | Lead frame package for electronic devices | |

| KR0147259B1 (ko) | 적층형 패키지 및 그 제조방법 | |

| KR100435978B1 (ko) | 반도체장치 | |

| TWI584445B (zh) | 半導體裝置 | |

| US5018051A (en) | IC card having circuit modules for mounting electronic components | |

| US6452266B1 (en) | Semiconductor device | |

| JP3718008B2 (ja) | メモリモジュールおよびその製造方法 | |

| US5726492A (en) | Semiconductor module including vertically mounted semiconductor chips | |

| KR970006529B1 (ko) | 반도체 장치 | |

| EP0461639B1 (en) | Plastic-molded-type semiconductor device | |

| KR0120921B1 (ko) | 반도체 장치 | |

| KR960002990B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| KR20040065176A (ko) | 반도체장치 | |

| KR19990063110A (ko) | 반도체 장치 | |

| US11594522B2 (en) | Semiconductor devices with duplicated die bond pads and associated device packages and methods of manufacture | |

| JP2006351664A (ja) | 半導体装置 | |

| US20030015803A1 (en) | High-density multichip module and method for manufacturing the same | |

| JPH11168150A (ja) | 半導体集積回路装置 | |

| KR101252305B1 (ko) | 멀티칩 모듈 | |

| JP3718015B2 (ja) | メモリモジュールおよびプリント基板 | |

| KR200319437Y1 (ko) | 핀 접속부를 구비하는 패키지 적층형 반도체 장치 | |

| JP2796119B2 (ja) | 半導体デバイスおよびメモリモジュールデバイス | |

| KR200283835Y1 (ko) | 핀 접속부를 구비하는 패키지 적층형 반도체 소자 | |

| KR950013050B1 (ko) | 엘오씨(Lead On Chip)용 리드 프레임 | |

| KR0145696B1 (ko) | 반도체장치 및 그들을 적층한 모듈과 그것을 실장한 전자장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20130524 Year of fee payment: 10 |

|

| FPAY | Annual fee payment |

Payment date: 20140530 Year of fee payment: 11 |

|

| LAPS | Lapse due to unpaid annual fee |