JP7612472B2 - 半導体装置及び半導体記憶装置 - Google Patents

半導体装置及び半導体記憶装置 Download PDFInfo

- Publication number

- JP7612472B2 JP7612472B2 JP2021047614A JP2021047614A JP7612472B2 JP 7612472 B2 JP7612472 B2 JP 7612472B2 JP 2021047614 A JP2021047614 A JP 2021047614A JP 2021047614 A JP2021047614 A JP 2021047614A JP 7612472 B2 JP7612472 B2 JP 7612472B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- oxide semiconductor

- electrode

- conductive layer

- metal element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/481—Internal lead connections, e.g. via connections, feedthrough structures

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/05—Making the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/33—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells the capacitor extending under the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

- H10D30/6713—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6728—Vertical TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

- Thin Film Transistor (AREA)

- Electrodes Of Semiconductors (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

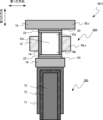

第1の実施形態の半導体装置は、第1の領域と、第2の領域と、第1の領域と第2の領域との間の第3の領域と、を含む酸化物半導体層と、ゲート電極と、第3の領域とゲート電極との間に設けられたゲート絶縁層と、第1の領域に電気的に接続された第1の電極と、第2の領域に電気的に接続された第2の電極と、第1の領域と第1の電極との間、及び、第2の領域と第2の電極との間の少なくとも一方の位置に設けられ、酸素(O)及び窒素(N)の少なくともいずれか一方の元素と、第1の金属元素と、を含む第1の導電層と、酸化物半導体層と第1の導電層との間に設けられ、インジウム(In)、亜鉛(Zn)、スズ(Sn)、及びカドミウム(Cd)から成る群から選ばれる少なくとも一つの元素と、を含み、厚さが第1の導電層の厚さよりも厚い第2の導電層と、酸素(O)と、を備える。

第2の実施形態の半導体装置は、ゲート電極が、酸化物半導体層を囲む点で、第1の実施形態の半導体装置と異なっている。以下、第1の実施形態と重複する内容については、一部記述を省略する場合がある。

第1の方向に延びる第1の配線と、第1の方向と交差する第2の方向に延びる第2の配線と、メモリセルと、を備え、メモリセルは、第1の領域と、第2の領域と、第1の領域と第2の領域との間の第3の領域と、を含み、第1の領域が第1の配線に電気的に接続され、第3の領域が第2の配線の一部に囲まれた酸化物半導体層と、第3の領域と第2の配線の一部との間に設けられたゲート絶縁層と、第2の領域に電気的に接続された第1の電極と、第2の電極と、第1の電極と第2の電極との間の絶縁層と、を含むキャパシタと、第1の領域と第1の配線との間、及び、第2の領域と第1の電極との間の少なくとも一方の位置に設けられ、酸素(O)及び窒素(N)の少なくともいずれか一方の元素と、第1の金属元素と、を含む第1の導電層と、酸化物半導体層と第1の導電層との間に設けられ、インジウム(In)、亜鉛(Zn)、スズ(Sn)、及びカドミウム(Cd)から成る群から選ばれる少なくとも一つの元素と、酸素(O)と、を含む第2の導電層と、を備える。以下、第1又は第2の実施形態と重複する内容については、一部記述を省略する場合がある。

第4の実施形態の半導体装置は、酸化物半導体層と、電極と、酸化物半導体層と電極との間に設けられ、第1の金属元素と、を含む第1の導電層と、酸素(O)及び窒素(N)の少なくともいずれか一方の元素と、酸化物半導体層と第1の導電層との間に設けられ、インジウム(In)、亜鉛(Zn)、スズ(Sn)、及びカドミウム(Cd)から成る群から選ばれる少なくとも一つの元素と、酸素(O)と、を含む第2の導電層と、を備える。以下、第1の実施形態と重複する内容については、一部記述を省略する場合がある。

10a 第1の領域

10b 第2の領域

10c 第3の領域

12 ゲート電極

14 ゲート絶縁層

16 ソース電極(第1の電極)

18 ドレイン電極(第2の電極)

20 バリア層(第1の導電層)

22 コンタクト層(第2の導電層)

71 セル電極(第1の電極)

72 プレート電極(第2の電極)

73 キャパシタ絶縁膜(絶縁層)

100 トランジスタ(半導体装置)

200 トランジスタ(半導体装置)

201 キャパシタ

300 半導体メモリ(半導体記憶装置)

BLx ビット線(第1の配線)

MC1 第1のメモリセル(メモリセル)

WLx ワード線(第2の配線)

Claims (19)

- 第1の領域と、第2の領域と、前記第1の領域と前記第2の領域との間の第3の領域と、を含む酸化物半導体層と、

ゲート電極と、

前記第3の領域と前記ゲート電極との間に設けられたゲート絶縁層と、

前記第1の領域に電気的に接続された第1の電極と、

前記第2の領域に電気的に接続された第2の電極と、

前記第1の領域と前記第1の電極との間、及び、前記第2の領域と前記第2の電極との間の少なくとも一方の位置に設けられ、酸素(O)と、窒素(N)と、第1の金属元素と、を含む第1の導電層と、

前記酸化物半導体層と前記第1の導電層との間に設けられ、インジウム(In)、亜鉛(Zn)、スズ(Sn)、及びカドミウム(Cd)から成る群から選ばれる少なくとも一つの元素と、酸素(O)と、を含み、厚さが前記第1の導電層の厚さよりも厚い第2の導電層と、

を備え、

前記第1の金属元素はチタン(Ti)である半導体装置。 - 前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の電極の厚さ、又は、前記酸化物半導体層との間に前記第1の導電層が設けられた前記第2の電極の厚さは、前記第2の導電層よりも厚い請求項1記載の半導体装置。

- 前記第1の導電層の厚さは、1nm以上10nm以下である請求項1又は請求項2記載の半導体装置。

- 前記第1の導電層の中に含まれる酸素(O)及び窒素(N)以外の元素の原子濃度の中で、前記第1の金属元素の原子濃度が最も高い請求項1ないし請求項3いずれか一項記載の半導体装置。

- 前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の電極、又は、前記酸化物半導体層との間に前記第1の導電層が設けられた前記第2の電極、の少なくともいずれか一方の電極は、第2の金属元素を含み、

前記少なくともいずれか一方の電極に含まれる金属元素の原子濃度の中で、前記第2の金属元素の原子濃度が最も高く、

前記第2の金属元素は前記第1の金属元素と同一である請求項1ないし請求項4いずれか一項記載の半導体装置。 - 前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の電極、又は、前記酸化物半導体層との間に前記第1の導電層が設けられた前記第2の電極、の少なくともいずれか一方の電極は、第2の金属元素を含み、

前記少なくともいずれか一方の電極に含まれる金属元素の原子濃度の中で、前記第2の金属元素の原子濃度が最も高く、

前記第2の金属元素は前記第1の金属元素と異なる請求項1ないし請求項4いずれか一項記載の半導体装置。 - 第1の領域と、第2の領域と、前記第1の領域と前記第2の領域との間の第3の領域と、を含む酸化物半導体層と、

ゲート電極と、

前記第3の領域と前記ゲート電極との間に設けられたゲート絶縁層と、

前記第1の領域に電気的に接続された第1の電極と、

前記第2の領域に電気的に接続された第2の電極と、

前記第1の領域と前記第1の電極との間、及び、前記第2の領域と前記第2の電極との間の少なくとも一方の位置に設けられた第1の導電層であって、チタン(Ti)、タングステン(W)、銅(Cu)、アルミニウム(Al)、タンタル(Ta)、及びモリブデン(Mo)から成る群から選ばれる少なくとも一つの第1の金属元素と、酸素(O)と、窒素(N)と、を含み、前記第1の導電層の中に含まれる酸素(O)及び窒素(N)以外の元素の原子濃度の中で、前記第1の金属元素の原子濃度が最も高い第1の導電層と、

前記酸化物半導体層と前記第1の導電層との間に設けられ、インジウム(In)、亜鉛(Zn)、スズ(Sn)、及びカドミウム(Cd)から成る群から選ばれる少なくとも一つの元素と、酸素(O)と、を含む第2の導電層と、

を備え、

前記第1の金属元素はチタン(Ti)である半導体装置。 - 第1の領域と、第2の領域と、前記第1の領域と前記第2の領域との間の第3の領域と、を含む酸化物半導体層と、

ゲート電極と、

前記第3の領域と前記ゲート電極との間に設けられたゲート絶縁層と、

前記第1の領域に電気的に接続された第1の電極と、

前記第2の領域に電気的に接続された第2の電極と、

前記第1の領域と前記第1の電極との間、及び、前記第2の領域と前記第2の電極との間の少なくとも一方の位置に設けられ、酸素(O)と、窒素(N)と、第1の金属元素と、を含む第1の導電層と、

前記酸化物半導体層と前記第1の導電層との間に設けられ、インジウム(In)、亜鉛(Zn)、スズ(Sn)、及びカドミウム(Cd)から成る群から選ばれる少なくとも一つの元素と、酸素(O)と、を含む第2の導電層と、を備え、

前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の電極、又は、前記酸化物半導体層との間に前記第1の導電層が設けられた前記第2の電極、の少なくともいずれか一方の電極は、第2の金属元素を含み、

前記少なくともいずれか一方の電極に含まれる金属元素の原子濃度の中で、前記第2の金属元素の原子濃度が最も高く、

前記第2の金属元素は前記第1の金属元素と同一であり、

前記第1の金属元素はチタン(Ti)である半導体装置。 - 前記酸化物半導体層は、ガリウム(Ga)及びアルミニウム(Al)の少なくともいずれか一方の元素と、インジウム(In)と、亜鉛(Zn)とを含む請求項1ないし請求項8いずれか一項記載の半導体装置。

- 前記ゲート電極は、前記酸化物半導体層を囲む請求項1ないし請求項9いずれか一項記載の半導体装置。

- 第1の方向に延びる第1の配線と、

前記第1の方向と交差する第2の方向に延びる第2の配線と、

メモリセルと、を備え、

前記メモリセルは、

第1の領域と、第2の領域と、前記第1の領域と前記第2の領域との間の第3の領域と、を含み、前記第1の領域が前記第1の配線に電気的に接続され、前記第3の領域が前記第2の配線の一部に囲まれた酸化物半導体層と、

前記第3の領域と前記第2の配線の一部との間に設けられたゲート絶縁層と、

前記第2の領域に電気的に接続された第1の電極と、第2の電極と、前記第1の電極と前記第2の電極との間の絶縁層と、を含むキャパシタと、

前記第1の領域と前記第1の配線との間、及び、前記第2の領域と前記第1の電極との間の少なくとも一方の位置に設けられ、酸素(O)と、窒素(N)と、第1の金属元素と、を含む第1の導電層と、

前記酸化物半導体層と前記第1の導電層との間に設けられ、インジウム(In)、亜鉛(Zn)、スズ(Sn)、及びカドミウム(Cd)から成る群から選ばれる少なくとも一つの元素と、酸素(O)と、を含み、厚さが前記第1の導電層の厚さよりも厚い第2の導電層と、

を備え、

前記第1の金属元素はチタン(Ti)である半導体記憶装置。 - 前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の配線の厚さ、又は、前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の電極の厚さは、前記第2の導電層よりも厚い請求項11記載の半導体記憶装置。

- 前記第1の導電層の厚さは、1nm以上10nm以下である請求項11又は請求項12記載の半導体記憶装置。

- 前記第1の導電層の中に含まれる酸素(O)及び窒素(N)以外の元素の原子濃度の中で、前記第1の金属元素の原子濃度が最も高い請求項11ないし請求項13いずれか一項記載の半導体記憶装置。

- 前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の配線、又は、前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の電極、の少なくともいずれか一方は、第2の金属元素を含み、

前記少なくともいずれか一方に含まれる金属元素の原子濃度の中で、前記第2の金属元素の原子濃度が最も高く、

前記第2の金属元素は前記第1の金属元素と同一である請求項11ないし請求項14いずれか一項記載の半導体記憶装置。 - 前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の配線、又は、前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の電極、の少なくともいずれか一方は、第2の金属元素を含み、

前記少なくともいずれか一方に含まれる金属元素の原子濃度の中で、前記第2の金属元素の原子濃度が最も高く、

前記第2の金属元素は前記第1の金属元素と異なる請求項11ないし請求項14いずれか一項記載の半導体記憶装置。 - 第1の方向に延びる第1の配線と、

前記第1の方向と交差する第2の方向に延びる第2の配線と、

メモリセルと、を備え、

前記メモリセルは、

第1の領域と、第2の領域と、前記第1の領域と前記第2の領域との間の第3の領域と、を含み、前記第1の領域が前記第1の配線に電気的に接続され、前記第3の領域が前記第2の配線の一部に囲まれた酸化物半導体層と、

前記第3の領域と前記第2の配線の一部との間に設けられたゲート絶縁層と、

前記第2の領域に電気的に接続されたキャパシタと、

前記第1の領域と前記第1の配線との間、及び、前記第2の領域と前記キャパシタとの間の少なくとも一方の位置に設けられた第1の導電層であって、チタン(Ti)、タングステン(W)、銅(Cu)、アルミニウム(Al)、タンタル(Ta)、及びモリブデン(Mo)から成る群から選ばれる少なくとも一つの第1の金属元素と、酸素(O)と、窒素(N)と、を含み、前記第1の導電層の中に含まれる酸素(O)及び窒素(N)以外の元素の原子濃度の中で、前記第1の金属元素の原子濃度が最も高い第1の導電層と、

前記酸化物半導体層と前記第1の導電層との間に設けられ、インジウム(In)、亜鉛(Zn)、スズ(Sn)、及びカドミウム(Cd)から成る群から選ばれる少なくとも一つの元素と、酸素(O)と、を含む第2の導電層と、

を備え、

前記第1の金属元素はチタン(Ti)である半導体記憶装置。 - 第1の方向に延びる第1の配線と、

前記第1の方向と交差する第2の方向に延びる第2の配線と、

メモリセルと、を備え、

前記メモリセルは、

第1の領域と、第2の領域と、前記第1の領域と前記第2の領域との間の第3の領域と、を含み、前記第1の領域が前記第1の配線に電気的に接続され、前記第3の領域が前記第2の配線の一部に囲まれた酸化物半導体層と、

前記第3の領域と前記第2の配線の一部との間に設けられたゲート絶縁層と、

前記第2の領域に電気的に接続された第1の電極と、第2の電極と、前記第1の電極と前記第2の電極との間の絶縁層と、を含むキャパシタと、

前記第1の領域と前記第1の配線との間、及び、前記第2の領域と前記第1の電極との間の少なくとも一方の位置に設けられた第1の導電層であって、酸素(O)と、窒素(N)と、第1の金属元素と、を含む第1の導電層と、

前記酸化物半導体層と前記第1の導電層との間に設けられ、インジウム(In)、亜鉛(Zn)、スズ(Sn)、及びカドミウム(Cd)から成る群から選ばれる少なくとも一つの元素と、酸素(O)と、を含む第2の導電層と、を備え、

前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の配線、又は、前記酸化物半導体層との間に前記第1の導電層が設けられた前記第1の電極、の少なくともいずれか一方は、第2の金属元素を含み、

前記少なくともいずれか一方に含まれる金属元素の原子濃度の中で、前記第2の金属元素の原子濃度が最も高く、

前記第2の金属元素は前記第1の金属元素と同一であり、

前記第1の金属元素はチタン(Ti)である半導体記憶装置。 - 前記酸化物半導体層は、ガリウム(Ga)及びアルミニウム(Al)の少なくともいずれか一方の元素と、インジウム(In)と、亜鉛(Zn)とを含む請求項11ないし請求項18いずれか一項記載の半導体記憶装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021047614A JP7612472B2 (ja) | 2021-03-22 | 2021-03-22 | 半導体装置及び半導体記憶装置 |

| TW110120640A TWI797636B (zh) | 2021-03-22 | 2021-06-07 | 半導體裝置與半導體記憶裝置 |

| CN202110702228.5A CN115117062A (zh) | 2021-03-22 | 2021-06-24 | 半导体装置与半导体存储装置 |

| US17/470,871 US12089395B2 (en) | 2021-03-22 | 2021-09-09 | Semiconductor device and semiconductor memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2021047614A JP7612472B2 (ja) | 2021-03-22 | 2021-03-22 | 半導体装置及び半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2022146576A JP2022146576A (ja) | 2022-10-05 |

| JP7612472B2 true JP7612472B2 (ja) | 2025-01-14 |

Family

ID=83284238

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2021047614A Active JP7612472B2 (ja) | 2021-03-22 | 2021-03-22 | 半導体装置及び半導体記憶装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US12089395B2 (ja) |

| JP (1) | JP7612472B2 (ja) |

| CN (1) | CN115117062A (ja) |

| TW (1) | TWI797636B (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7612472B2 (ja) * | 2021-03-22 | 2025-01-14 | キオクシア株式会社 | 半導体装置及び半導体記憶装置 |

| KR102710108B1 (ko) * | 2021-09-24 | 2024-09-25 | 한국전자통신연구원 | 산화물 반도체를 포함하는 sram 소자 |

| JP2024000648A (ja) | 2022-06-21 | 2024-01-09 | キオクシア株式会社 | 半導体装置及び半導体記憶装置 |

| JP2024137422A (ja) * | 2023-03-24 | 2024-10-07 | キオクシア株式会社 | 半導体装置及び半導体記憶装置 |

| WO2025032477A1 (ja) * | 2023-08-10 | 2025-02-13 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| KR20250113219A (ko) * | 2024-01-18 | 2025-07-25 | 삼성전자주식회사 | 반도체 소자 및 그 제조 방법 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007173796A (ja) | 2005-12-19 | 2007-07-05 | Internatl Business Mach Corp <Ibm> | pFET材料としての金属酸窒化物を用いた半導体構造およびその製造方法 |

| JP2010056539A (ja) | 2008-07-31 | 2010-03-11 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| WO2012002574A1 (ja) | 2010-07-02 | 2012-01-05 | 合同会社先端配線材料研究所 | 薄膜トランジスタ |

| WO2012002573A1 (ja) | 2010-07-02 | 2012-01-05 | 合同会社先端配線材料研究所 | 半導体装置 |

| JP2020003798A (ja) | 2009-09-04 | 2020-01-09 | 株式会社半導体エネルギー研究所 | 表示装置 |

| JP2020198343A (ja) | 2019-05-31 | 2020-12-10 | キオクシア株式会社 | 半導体装置及び半導体記憶装置 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100861236B1 (ko) * | 2007-04-10 | 2008-10-02 | 경북대학교 산학협력단 | 낮은 누설전류를 갖는 기둥형 전계효과트랜지스터 |

| JP5579848B2 (ja) | 2010-06-21 | 2014-08-27 | 株式会社アルバック | 半導体装置、半導体装置を有する液晶表示装置、半導体装置の製造方法 |

| JP5731369B2 (ja) * | 2010-12-28 | 2015-06-10 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| KR20130048703A (ko) | 2011-11-02 | 2013-05-10 | 히타치 덴센 가부시키가이샤 | 박막 트랜지스터 및 그 제조 방법과, 박막 트랜지스터를 구비한 표시 장치, 스퍼터링 타깃재 |

| KR101925012B1 (ko) * | 2012-07-17 | 2018-12-05 | 에스케이하이닉스 주식회사 | 반도체 장치 및 그의 제조 방법 |

| CN102931091A (zh) * | 2012-10-25 | 2013-02-13 | 深圳市华星光电技术有限公司 | 一种主动矩阵式平面显示装置、薄膜晶体管及其制作方法 |

| JP2014143410A (ja) | 2012-12-28 | 2014-08-07 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| KR102290801B1 (ko) | 2013-06-21 | 2021-08-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| US9859439B2 (en) * | 2013-09-18 | 2018-01-02 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing the same |

| US9177875B2 (en) * | 2013-11-15 | 2015-11-03 | Taiwan Seminconductor Manufacturing Co., Ltd. | Advanced process control method for controlling width of spacer and dummy sidewall in semiconductor device |

| TWI532192B (zh) * | 2014-02-20 | 2016-05-01 | 友達光電股份有限公司 | 薄膜電晶體及畫素結構 |

| KR20170080320A (ko) | 2015-12-31 | 2017-07-10 | 엘지디스플레이 주식회사 | 박막트랜지스터, 그를 갖는 표시장치, 및 박막트랜지스터의 제조방법 |

| JP6538598B2 (ja) * | 2016-03-16 | 2019-07-03 | 株式会社東芝 | トランジスタ及び半導体記憶装置 |

| CN109219883B (zh) * | 2016-08-31 | 2023-03-21 | 美光科技公司 | 存储器胞元和存储器阵列 |

| US10644123B2 (en) * | 2016-09-30 | 2020-05-05 | Intel Corporation | Systems, methods, and apparatuses for implementing a high mobility low contact resistance semiconducting oxide in metal contact vias for thin film transistors |

| US10818799B2 (en) * | 2016-12-24 | 2020-10-27 | Intel Corporation | Vertical transistor devices and techniques |

| EP3559997A4 (en) * | 2016-12-24 | 2020-11-04 | INTEL Corporation | VERTICAL TRANSISTOR DEVICES AND TECHNIQUES |

| WO2019005090A1 (en) * | 2017-06-30 | 2019-01-03 | Intel Corporation | SOURCE AND DRAIN CONTACTS OF SEMICONDUCTOR OXIDE DEVICE COMPRISING GRADUATED INDIUM LAYERS |

| JP7124059B2 (ja) * | 2017-08-31 | 2022-08-23 | マイクロン テクノロジー,インク. | 半導体デバイス、トランジスタ、および金属酸化物半導体デバイスを接触させるための関連する方法 |

| JP7109928B2 (ja) | 2018-01-31 | 2022-08-01 | キオクシア株式会社 | トランジスタ及び半導体記憶装置並びにトランジスタの製造方法 |

| US20200006570A1 (en) * | 2018-06-29 | 2020-01-02 | Intel Corporation | Contact structures for thin film transistor devices |

| JP2021108331A (ja) * | 2019-12-27 | 2021-07-29 | キオクシア株式会社 | 半導体記憶装置 |

| US11488981B2 (en) * | 2020-07-21 | 2022-11-01 | Micron Technology, Inc. | Array of vertical transistors and method used in forming an array of vertical transistors |

| JP2022049605A (ja) * | 2020-09-16 | 2022-03-29 | キオクシア株式会社 | 半導体装置及び半導体記憶装置 |

| JP7612472B2 (ja) * | 2021-03-22 | 2025-01-14 | キオクシア株式会社 | 半導体装置及び半導体記憶装置 |

-

2021

- 2021-03-22 JP JP2021047614A patent/JP7612472B2/ja active Active

- 2021-06-07 TW TW110120640A patent/TWI797636B/zh active

- 2021-06-24 CN CN202110702228.5A patent/CN115117062A/zh active Pending

- 2021-09-09 US US17/470,871 patent/US12089395B2/en active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007173796A (ja) | 2005-12-19 | 2007-07-05 | Internatl Business Mach Corp <Ibm> | pFET材料としての金属酸窒化物を用いた半導体構造およびその製造方法 |

| JP2010056539A (ja) | 2008-07-31 | 2010-03-11 | Semiconductor Energy Lab Co Ltd | 半導体装置及びその作製方法 |

| JP2020003798A (ja) | 2009-09-04 | 2020-01-09 | 株式会社半導体エネルギー研究所 | 表示装置 |

| WO2012002574A1 (ja) | 2010-07-02 | 2012-01-05 | 合同会社先端配線材料研究所 | 薄膜トランジスタ |

| WO2012002573A1 (ja) | 2010-07-02 | 2012-01-05 | 合同会社先端配線材料研究所 | 半導体装置 |

| JP2020198343A (ja) | 2019-05-31 | 2020-12-10 | キオクシア株式会社 | 半導体装置及び半導体記憶装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US12089395B2 (en) | 2024-09-10 |

| US20220302120A1 (en) | 2022-09-22 |

| TW202238855A (zh) | 2022-10-01 |

| JP2022146576A (ja) | 2022-10-05 |

| TWI797636B (zh) | 2023-04-01 |

| CN115117062A (zh) | 2022-09-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI786507B (zh) | 半導體裝置及半導體記憶裝置 | |

| JP7612472B2 (ja) | 半導体装置及び半導体記憶装置 | |

| US11769810B2 (en) | Semiconductor device and semiconductor memory device | |

| US20200381557A1 (en) | Semiconductor device and semiconductor memory device | |

| US11502204B2 (en) | Semiconductor device and semiconductor memory device | |

| US11374130B2 (en) | Semiconductor device and semiconductor memory device | |

| US11978806B2 (en) | Semiconductor device and semiconductor storage device | |

| TWI872299B (zh) | 半導體裝置及半導體記憶裝置 | |

| US12310065B2 (en) | Semiconductor device, semiconductor memory device, and method for manufacturing semiconductor device | |

| JP2023136275A (ja) | 半導体装置及び半導体記憶装置 | |

| US12477718B2 (en) | Semiconductor device and semiconductor memory device each having portions of oxide semiconductor between gate insulating layer and electrodes | |

| TWI852037B (zh) | 半導體裝置、半導體記憶裝置、及半導體裝置之製造方法 | |

| US20230290882A1 (en) | Semiconductor device and semiconductor memory device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230907 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20240516 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240625 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240806 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20241126 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20241225 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7612472 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |