JP6972660B2 - アイドルトーン分散装置および周波数比計測装置 - Google Patents

アイドルトーン分散装置および周波数比計測装置 Download PDFInfo

- Publication number

- JP6972660B2 JP6972660B2 JP2017105463A JP2017105463A JP6972660B2 JP 6972660 B2 JP6972660 B2 JP 6972660B2 JP 2017105463 A JP2017105463 A JP 2017105463A JP 2017105463 A JP2017105463 A JP 2017105463A JP 6972660 B2 JP6972660 B2 JP 6972660B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- output

- frequency

- jitter

- measured

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000006185 dispersion Substances 0.000 claims description 105

- 238000005259 measurement Methods 0.000 claims description 24

- 238000009826 distribution Methods 0.000 claims description 3

- 241000286209 Phasianidae Species 0.000 claims 2

- 238000001228 spectrum Methods 0.000 description 94

- 238000002474 experimental method Methods 0.000 description 46

- 238000010586 diagram Methods 0.000 description 20

- 238000013139 quantization Methods 0.000 description 18

- 230000000630 rising effect Effects 0.000 description 15

- 230000003111 delayed effect Effects 0.000 description 11

- 230000000694 effects Effects 0.000 description 11

- 230000000052 comparative effect Effects 0.000 description 10

- 238000004088 simulation Methods 0.000 description 9

- 238000012360 testing method Methods 0.000 description 7

- 230000000737 periodic effect Effects 0.000 description 6

- 230000001934 delay Effects 0.000 description 4

- 230000001360 synchronised effect Effects 0.000 description 4

- 230000002123 temporal effect Effects 0.000 description 3

- 108010076504 Protein Sorting Signals Proteins 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 238000012935 Averaging Methods 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 238000010187 selection method Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/322—Continuously compensating for, or preventing, undesired influence of physical parameters

- H03M3/368—Continuously compensating for, or preventing, undesired influence of physical parameters of noise other than the quantisation noise already being shaped inherently by delta-sigma modulators

- H03M3/37—Compensation or reduction of delay or phase error

- H03M3/372—Jitter reduction

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R23/00—Arrangements for measuring frequencies; Arrangements for analysing frequency spectra

- G01R23/005—Circuits for comparing several input signals and for indicating the result of this comparison, e.g. equal, different, greater, smaller (comparing phase or frequency of 2 mutually independent oscillations in demodulators)

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/322—Continuously compensating for, or preventing, undesired influence of physical parameters

- H03M3/324—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by means or methods for compensating or preventing more than one type of error at a time, e.g. by synchronisation or using a ratiometric arrangement

- H03M3/326—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by means or methods for compensating or preventing more than one type of error at a time, e.g. by synchronisation or using a ratiometric arrangement by averaging out the errors

- H03M3/328—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by means or methods for compensating or preventing more than one type of error at a time, e.g. by synchronisation or using a ratiometric arrangement by averaging out the errors using dither

- H03M3/3283—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by means or methods for compensating or preventing more than one type of error at a time, e.g. by synchronisation or using a ratiometric arrangement by averaging out the errors using dither the dither being in the time domain

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/322—Continuously compensating for, or preventing, undesired influence of physical parameters

- H03M3/324—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by means or methods for compensating or preventing more than one type of error at a time, e.g. by synchronisation or using a ratiometric arrangement

- H03M3/346—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by means or methods for compensating or preventing more than one type of error at a time, e.g. by synchronisation or using a ratiometric arrangement by suppressing active signals at predetermined times, e.g. muting, using non-overlapping clock phases

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/458—Analogue/digital converters using delta-sigma modulation as an intermediate step

- H03M3/466—Multiplexed conversion systems

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/458—Analogue/digital converters using delta-sigma modulation as an intermediate step

- H03M3/466—Multiplexed conversion systems

- H03M3/472—Shared, i.e. using a single converter for multiple channels

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Measuring Frequencies, Analyzing Spectra (AREA)

- Compression, Expansion, Code Conversion, And Decoders (AREA)

Description

本発明の目的は、周波数デルタシグマ変調で発生するアイドルトーンに起因する量子化雑音を抑制することができるアイドルトーン分散装置および周波数比計測装置を提供することにある。

n(nは2以上の任意の自然数)個の周波数デルタシグマ変調部と、

前記n個の周波数デルタシグマ変調部の出力信号を加算して前記周波数デルタシグマ変調信号を出力する加算部と、を備え、

前記n個の周波数デルタシグマ変調部の各々は、前記基準信号と前記被測定信号とのいずれか一方を用いて他方を周波数デルタシグマ変調し、

前記基準信号と前記被測定信号との少なくとも一方は、前記周波数デルタシグマ変調部の出力信号のアイドルトーンの周波数よりも高い周波数成分を含むジッターを有することを特徴とする。

n(nは2以上の任意の自然数)個の周波数デルタシグマ変調部と、

前記被測定信号と前記基準信号との位相を調整して、n組の出力被測定信号および出力基準信号を生成して、各組の前記出力被測定信号および前記出力基準信号を前記n個の周波数デルタシグマ変調部の各々に供給する位相調整部と、

前記n個の周波数デルタシグマ変調部の出力信号を加算して前記周波数デルタシグマ変調信号を出力する加算部と、を備え、

前記位相調整部は、前記n個の周波数デルタシグマ変調部のうちの少なくとも一部の前記周波数デルタシグマ変調部の出力信号のアイドルトーンの位相が互いに異なるように、前記被測定信号と前記基準信号との位相を調整して、前記n組の出力被測定信号および出力基準信号を生成し、

前記n個の周波数デルタシグマ変調部の各々は、前記位相調整部から供給される前記出力基準信号と前記出力被測定信号とのいずれか一方を用いて他方を周波数デルタシグマ変調し、

前記出力基準信号と前記出力被測定信号とのうちの少なくとも1つは、前記アイドルトーンの周波数よりも高い周波数成分を含むジッターを有することを特徴とする。

前記位相調整部は、D/n=Pi+1−Piとなるように、前記被測定信号と前記基準信号との位相を調整して、前記n組の出力被測定信号および出力基準信号を生成することが好ましい。

これにより、n個の周波数デルタシグマ変調部の出力信号のアイドルトーンの位相が互いに異なるようになるので、アイドルトーンを適確に時間的に分散させることができ、アイドルトーンの影響を抑制することができる。

これにより、アイドルトーンを適確に時間的に分散させることができ、アイドルトーンの影響を抑制することができる。

D/n≠Pi+1−Piであることが好ましい。

D/n≠Pi+1−Piであってもn個の周波数デルタシグマ変調部の出力信号のアイドルトーンの位相が互いに異なるようにすることができる。これによって、アイドルトーンを適確に時間的に分散させることができ、アイドルトーンの影響を抑制することができる。

また、遅延量の設定の自由度が高まり、調整が簡易になり、調整が簡易になることから特別な装置を必要とせず、製造コストを低減することができる。

これにより、アイドルトーンに起因する量子化雑音の影響を大幅に抑制することができる。

これにより、別途、ジッターを生成する装置を用意する必要がなく、ジッターを付加したい信号に対し、容易かつ適確にジッターを付加することができる。

これにより、適確にジッターの周波数帯域を設定することができる。

前記被測定信号と前記基準信号との周波数比を測定することを特徴とする。

このような本発明の周波数比計測装置によれば、アイドルトーンに起因する量子化雑音の影響を抑制することができ、これにより、測定精度を向上させることができる。

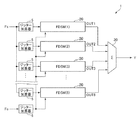

図1は、本発明のアイドルトーン分散装置の第1実施形態を示すブロック図である。図2は、図1に示すアイドルトーン分散装置のジッター加算器の構成例を示すブロック図である。図3は、図2に示すジッター加算器の動作を説明するためのタイミングチャートである。図4は、図1に示すアイドルトーン分散装置のジッター加算器の構成例を示すブロック図である。図10は、周波数デルタシグマ変調部の構成例を示すブロック図である。

また、信号のレベルが「ロー(Low)」の場合を「0」、信号のレベルが「ハイ(High)」の場合を「1」とも言う。これらは、他の実施形態でも同様である。

また、ジッター加算器5の数は、1つでもよく、また、複数でもよいが、本実施形態では、ジッター加算器5は、複数設けられている。なお、ジッター加算器5については、後に詳述する。

ビットストリーム構成のFDSMを用いる場合は、信号処理回路を簡素化することができる。また、データストリーム構成のFDSMを用いる場合は、周波数変動が大きい場合にも容易に対応することができる。

図1に示すように、データストリーム構成のFDSM20は、被測定信号の立ち上がりエッジをカウントしてカウント値を示すカウントデータDcを出力するアップカウンター21と、基準信号の立ち上がりエッジに同期してカウントデータDcをラッチして第1データD1を出力する第1ラッチ22と、基準信号の立ち上がりエッジに同期して第1データD1をラッチして第2データD2を出力する第2ラッチ23と、第1データD1から第2データD2を減算して出力データOUTを生成する減算器24とを備える。なお、第1ラッチ22および第2ラッチ23は、例えばDフリップフロップ回路等で構成される。

図10に示すように、ビットストリーム構成のFDSM20は、基準信号の立ち上がりエッジに同期して被測定信号をラッチして第1データd1を出力する第1ラッチ22と、基準信号の立ち上がりエッジに同期して第1データd1をラッチして第2データd2を出力する第2ラッチ23と、第1データd1と第2データd2の排他的論理和を演算して出力データOUTを生成する排他的論理和回路25とを備える。なお、第1ラッチ22および第2ラッチ23は、例えばDフリップフロップ回路等で構成される。

位相調整部10は、被測定信号を遅延させずに、出力被測定信号Fx1として出力し、被測定信号(出力被測定信号Fx1)を遅延させて、出力被測定信号Fx2として出力し、以下、同様にして、順次、遅延させて出力被測定信号Fxnまで出力する。

また、位相調整部10は、基準信号を遅延させずに、出力基準信号Fc1〜出力基準信号Fcnとして出力する。

位相調整部10は、基準信号を遅延させずに、出力基準信号Fc1として出力し、基準信号(出力基準信号Fc1)を遅延させて、出力基準信号Fc2として出力し、以下、同様にして、順次、遅延させて出力基準信号Fcnまで出力する。

また、位相調整部10は、被測定信号を遅延させずに、出力被測定信号Fx1〜出力被測定信号Fxnとして出力する。

位相調整部10は、被測定信号を遅延させずに、出力被測定信号Fx1として出力し、被測定信号(出力被測定信号Fx1)を遅延させて、出力被測定信号Fx2として出力し、以下、同様にして、順次、遅延させて出力被測定信号Fxnまで出力する。

また、位相調整部10は、基準信号を遅延させずに、出力基準信号Fc1として出力し、基準信号(出力基準信号Fc1)を遅延させて、出力基準信号Fc2として出力し、以下、同様にして、順次、遅延させて出力基準信号Fcnまで出力する。この場合、被測定信号についての遅延時間と、基準信号についての遅延時間とは、異なるように設定する。

この位相調整部10により被測定信号と基準信号との少なくとも一方を遅延させることにより、各FDSM20における周波数デルタシグマ変調で発生する周期的な量子化雑音であるアイドルトーンを時間的に分散させ、アイドルトーンの影響を抑制することができる。

(構成1)

構成1は、n個のFDSM20の出力信号のアイドルトーンの位相がすべて互いに異なるように、位相調整部10が構成されている。具体的には、下記のように位相調整部10を構成する。

例として、10個のFDSM20と基準信号(周波数:200MHz)を用いて、最大遅延量15000p秒の位相を調整する場合を挙げると、Dは15000p秒、Tは1/200MHz=5000p秒、nは10となる。設計値としてmに10を選べば、mD/nTは3となり、mD/nTとmは互いに素となることから上記条件を満たす。この場合、Pi+1−PiをD/n、すなわち1500p秒ずつ位相をずらすよう調整すれば良い。

構成2は、n個のFDSM20の出力信号のアイドルトーンの位相のうちの一部が互いに異なるように、位相調整部10が構成されている。具体的には、下記のように位相調整部10を構成する。

この場合でもジッターを付与することで、n個のFDSM20の出力信号のアイドルトーンの位相が互いに異なるようにすることができる。これによって、アイドルトーンを適確に時間的に分散させることができ、アイドルトーンの影響を抑制することができる。

また、遅延量の設定の自由度が高まり、調整が簡易になり、調整が簡易になることから特別な装置を必要とせず、製造コストを低減することができる。

また、一部がD/n=Pi+1−Piを満足し、他(残り)がD/n≠Pi+1−Piであってもよい。

また、加算器30は、出力データOUT1〜出力データOUTnを加算して、周波数デルタシグマ変調信号Yを生成し、出力する。この周波数デルタシグマ変調信号Yは、基準信号の周波数と被測定信号の周波数との比(周波数比)に対応している。

出力被測定信号Fx1〜出力被側定信号Fxnにジッターを付与する各ジッター加算器5は、各FDSMの入力側に接続されている。

また、基準信号Fcにジッターを付与するジッター加算器5は、位相調整部10の入力側に接続されている。

また、基準信号Fcにジッターを付与するジッター加算器5を設けることにより、n個の出力基準信号Fc1〜出力基準信号Fcnに個別にジッターを付与するn個のジッター加算器5を設ける場合に比べて、回路規模を小さくすることができる。

図2に示すように、ジッター加算器5は、1ビットのリプルカウンター51(バイナリーカウンター)と、複数の遅延素子52と、セレクター53と、マルチプレクサー54と、微分器55とを有している。

また、リプルカウンター51の出力側(後段)に、直列に接続された複数の遅延素子52が接続されている。

また、セレクター53の出力側および各遅延素子52の出力側にマルチプレクサー54が接続され、マルチプレクサー54の出力側に微分器55が接続されている。

まず、対象信号は、ジッター加算器5のリプルカウンター51に入力され、リプルカウンター51で2分周され、出力される。

また、初段の遅延素子52から出力された遅延信号a1は、マルチプレクサー54および2段目(2番目)の遅延素子52に入力され、2段目の遅延素子52で遅延される。

また、2段目の遅延素子52から出力された遅延信号a2は、マルチプレクサー54および3段目(3番目)の遅延素子52に入力され、3段目の遅延素子52で遅延される。

以下、同様にして、3段目から最終段までの各遅延素子52から出力された遅延信号a3、a4・・・anは、マルチプレクサー54に入力される。このようにして、位相(位相差)の異なる複数の遅延信号a1、a2、a3、a4・・・anがマルチプレクサー54に入力される。各遅延素子52における信号の遅延量は、リプルカウンター51に入力される対象信号に対する最終段の遅延素子52から出力される遅延信号anの遅延量(位相差)が対象信号の1周期を超えないように設定されている。

また、ジッターに含まれる周波数成分のうちの最大周波数をA、FDSM20の出力信号のアイドルトーンの周波数をB、測定帯域の上限周波数をCとしたとき、前述したように、Aは、Bよりも大きければ特に限定されず、諸条件に応じて適宜設定されるものであるが、A/Cは、1以上であることが好ましく、2以上であることがより好ましく、8以上であることがさらに好ましい。

また、除去するジッターの周波数成分は、特に限定されず、諸条件に応じて適宜設定されるものであるが、測定帯域の上限周波数を100MHzとする場合であれば、1MHz以下の低周波数成分を除去することが好ましく、2MHz以下の低周波数成分を除去することがより好ましく、5MHz以下の低周波数成分を除去することがさらに好ましく、10MHz以下の低周波数成分を除去することがさらに好ましく、20MHz以下の低周波数成分を除去することがさらに好ましく、50MHz以下の低周波数成分を除去することがさらに好ましく、100MHz以下の低周波数成分を除去することがさらに好ましい。

(構成1)

図4に示すように、構成1では、ジッター加算器5は、エミッターフォロア回路50Aと、加算器51Aとを有している。エミッターフォロア回路50Aは、トランジスター52A(npnトランジスター)と、トランジスター52Aのエミッターに接続された抵抗53Aとを有している。また、加算器51Aは、トランジスター52Aのコレクターに接続されている。

加算器51Aには、電源電圧とノイズとが入力される。また、ジッターを加算する信号は、トランジスター52Aのベースに入力される。

構成2では、アイドルトーン分散装置1の回路を構成する原子の熱運動により対象の回路に電気的なノイズを付与し、これにより、時間的な揺らぎ持つ信号を出力させる。

このようなアイドルトーン分散装置1は、前述した各部に対応する機能を実現するハードウェアで構成することが可能である。また、アイドルトーン分散装置1は、前述した各部に対応する機能を実現するプログラムやモジュール等により、ソフトウェア的に構成することも可能である。また、アイドルトーン分散装置1は、前述した各部に対応する機能を実現するハードウェアとソフトウェアとを組み合わせて構成することも可能である。

なお、本実施形態では、基準信号(各出力基準信号)および各出力被測定信号は、それぞれ、FDSM20の出力信号のアイドルトーンの周波数よりも高い周波数成分を含むジッターを有しているが、これに限定されず、各出力基準信号および各出力被測定信号のうちの少なくとも1つが、FDSM20の出力信号のアイドルトーンの周波数よりも高い周波数成分を含むジッターを有していればよい。

このアイドルトーン分散装置1は、n(nは2以上の任意の自然数)個のFDSM20(周波数デルタシグマ変調部)と、被測定信号Fxと基準信号Fcとの位相を調整して、n組の出力被測定信号Fx1〜出力被測定信号Fxnおよび出力基準信号Fc1〜出力基準信号Fcnを生成して、各組の出力被測定信号Fx1〜出力被測定信号Fxnおよび出力基準信号Fc1〜出力基準信号Fcnをn個のFDSM20(周波数デルタシグマ変調部)の各々に供給する位相調整部10と、n個のFDSM20(周波数デルタシグマ変調部)の出力信号を加算して周波数デルタシグマ変調信号Yを出力する加算器30(加算部)とを備えている。

また、位相調整部10は、n個のFDSM20(周波数デルタシグマ変調部)のうちの少なくとも一部のFDSM20(周波数デルタシグマ変調部)の出力信号のアイドルトーンの位相が互いに異なるように、被測定信号Fxと基準信号Fcとの位相を調整して、n組の出力被測定信号Fx1〜出力被測定信号Fxnおよび出力基準信号Fc1〜出力基準信号Fcnを生成する。

また、n個のFDSM20(周波数デルタシグマ変調部)の各々は、位相調整部10から供給される出力基準信号Fc1〜出力基準信号Fcnと、出力被測定信号Fx1〜出力被測定信号Fxnとのいずれか一方を用いて他方を周波数デルタシグマ変調する。

また、出力基準信号Fc1〜出力基準信号Fcnと、出力被測定信号Fx1〜出力被測定信号Fxnとのうちの少なくとも1つは、アイドルトーンの周波数よりも高い周波数成分を含むジッターを有する。

図5は、本発明のアイドルトーン分散装置の第2実施形態を示すブロック図である。

以下、第2実施形態について説明するが、前述した実施形態との相違点を中心に説明し、同様の事項はその説明を省略する。

被測定信号Fxにジッターを付与するジッター加算器5は、位相調整部10の入力側に接続されている。

また、出力基準信号Fc1〜出力基準信号Fcnにジッターを付与する各ジッター加算器5は、各FDSMの入力側に接続されている。

また、n個の出力基準信号Fc1〜出力基準信号Fcnに個別にジッターを付与するn個のジッター加算器5を設けることにより、基準信号Fcにジッターを付与するジッター加算器5を設ける場合に比べて、周波数デルタシグマ変調信号に含まれるノイズ成分を低下させることができる。

以上のような第2実施形態によっても、前述した実施形態と同様の効果を発揮することができる。

図6は、本発明のアイドルトーン分散装置の第3実施形態を示すブロック図である。

以下、第3実施形態について説明するが、前述した実施形態との相違点を中心に説明し、同様の事項はその説明を省略する。

被測定信号Fx1〜出力被測定信号Fxnにジッターを付与する各ジッター加算器5は、位相調整部10の入力側に接続されている。

また、出力基準信号Fc1〜出力基準信号Fcnにジッターを付与する各ジッター加算器5は、各FDSMの入力側に接続されている。

同様に、n個の出力基準信号Fc1〜出力基準信号Fcnに個別にジッターを付与するn個のジッター加算器5を設けることにより、基準信号Fcにジッターを付与するジッター加算器5を設ける場合に比べて、周波数デルタシグマ変調信号に含まれるノイズ成分を低下させることができる。

以上のような第3実施形態によっても、前述した実施形態と同様の効果を発揮することができる。

図7は、本発明のアイドルトーン分散装置の第4実施形態を示すブロック図である。

以下、第4実施形態について説明するが、前述した実施形態との相違点を中心に説明し、同様の事項はその説明を省略する。

同様に、基準信号Fcにジッターを付与するジッター加算器5を設けることにより、n個の出力基準信号Fc1〜出力基準信号Fcnに個別にジッターを付与するn個のジッター加算器5を設ける場合に比べて、回路規模を小さくすることができる。

以上のような第4実施形態によっても、前述した実施形態と同様の効果を発揮することができる。

図8は、本発明のアイドルトーン分散装置の第5実施形態を示すブロック図である。

以下、第5実施形態について説明するが、前述した実施形態との相違点を中心に説明し、同様の事項はその説明を省略する。

以上のような第5実施形態によっても、前述した実施形態と同様の効果を発揮することができる。

また、第5実施形態は、第2〜第4実施形態にも適用することができる。

このアイドルトーン分散装置1は、n(nは2以上の任意の自然数)個のFDSM20(周波数デルタシグマ変調部)と、n個のFDSM20(周波数デルタシグマ変調部)の出力信号を加算して周波数デルタシグマ変調信号Yを出力する加算器30(加算部)とを備えている。

また、n個のFDSM20(周波数デルタシグマ変調部)の各々は、基準信号Fcと被測定信号Fxとのいずれか一方を用いて他方を周波数デルタシグマ変調する。

また、基準信号Fcと被測定信号Fxとの少なくとも一方は、FDSM20(周波数デルタシグマ変調部)の出力信号のアイドルトーンの周波数よりも高い周波数成分を含むジッターを有する。

また、被測定信号として、周波数を変動させた矩形波を用いた。この場合、搬送周波数を261.24MHzとし、1秒間に2M回(変調周波数:2MHz)、±500kHzの範囲で搬送周波数を変更し、これを矩形波に変換したものを被測定信号とした。すなわち、各実験では、2MHzの周波数成分を検出対象(測定対象)の周波数とした。

アイドルトーン分散装置として、下記の装置a、装置b、装置c、装置dおよび装置eを用意した。

(装置a)

図1に示す第1実施形態のアイドルトーン分散装置1を用いた。また、FDSM20の並列数は、8個とした。また、8個のFDSM20にすべて位相の異なる被測定信号を入力した。また、8個のFDSM20に入力する被測定信号は、1/260M×1/8[秒]ずつ遅延させた。この装置aを用いる場合、グラフの説明には、「等分8並列」と記載する。

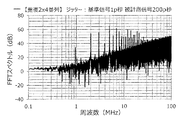

図1に示す第1実施形態のアイドルトーン分散装置1を用いた。また、FDSM20の並列数は、8個とした。また、2個のFDSM20に同相の被測定信号を入力し、その2個のFDSM20を1組とし、4組のFDSM20にすべて位相の異なる被測定信号を入力した。また、4組のFDSM20に入力する被測定信号は、1/260M×1/4[秒]ずつ遅延させた。この装置bを用いる場合、グラフの説明には、「重複2×4並列」と記載する。

図8に示す位相調整部10を有していない第5実施形態のアイドルトーン分散装置1を用いた。また、FDSM20の並列数は、8個とした。すなわち、8個のFDSM20にすべて同一の位相の被測定信号を入力した。この装置cを用いる場合、グラフの説明には、「同相8並列」と記載する。

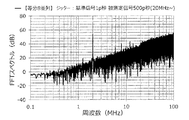

図9に示すアイドルトーン分散装置200(比較例)を用いた。このアイドルトーン分散装置200は、1個のFDSM20を有している。また、アイドルトーン分散装置200は、被測定にジッターを付与するジッター加算器5と、基準信号Fcにジッターを付与するジッター加算器5とを備えている。この装置dを用いる場合、グラフの説明には、「シングル」と記載する。

図7に示す第4実施形態のアイドルトーン分散装置1を用いた。また、FDSM20の並列数は、8個とした。また、8個のFDSM20にすべて位相の異なる被測定信号を入力した。また、8個のFDSM20に入力する被測定信号は、1/260M×1/8[秒]ずつ遅延させた。この装置eを用いる場合、グラフの説明には、「等分8並列」および「共通」と記載する。

装置aを用い、基準信号には、共通のジッターを付与し、被測定信号には、FDSM20毎に独立してジッターを付与した。

また、基準信号に付与するジッターの大きさを「10p秒」とし、被測定信号に付与するジッターの大きさを「10p秒」とした(実施例)。

また、基準信号に付与するジッターおよび被測定信号に付与するジッターは、それぞれ、最大の周波数成分が130MHzで、130MHz以下の周波数成分を含んでいる。

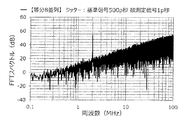

アイドルトーン分散装置から出力される周波数デルタシグマ変調信号について、含まれる周波数成分の強度を求め、アイドルトーン分散装置の出力スペクトルのグラフを作成した。この結果を図12に示す。

各グラフの横軸は、高速フーリエ変換(FFT)を行って求めた周波数成分(周波数)であり、縦軸は、強度(FFTスペクトル)である(図20〜図78も同様)。

本実験の結果から、基準信号および被測定信号がジッターを含む場合は、基準信号および被測定信号がジッターを含まない場合に比べて、アイドルトーンの影響が抑制されることが判る。また、ジッターの大きさに応じて、アイドルトーンの影響を抑制する効果(アイドルトーン抑制効果)が異なることも判る。

実験1の実施例において、被測定信号に付与するジッターの大きさを「1p秒」に固定し、基準信号に付与するジッターの大きさを「10p秒」、「20p秒」、「50p秒」、「100p秒」、「200p秒」、「500p秒」、「1000p秒」、「2000p秒」(実施例)とし、アイドルトーン分散装置の出力スペクトルのグラフを作成した。この結果を図20〜図27に示す。

なお、被測定信号がジッターを含まず(ジッターの大きさが0p秒)、基準信号に付与するジッターの大きさを「10p秒」、「20p秒」、「50p秒」、「100p秒」、「200p秒」、「500p秒」、「1000p秒」、「2000p秒」(実施例)とし、シミュレーションを行って、アイドルトーン分散装置の出力スペクトルのグラフを作成したところ、被測定信号のジッターの大きさが1p秒の場合と、ほぼ同様の結果が得られた。これにより、基準信号のみがジッターを含む場合でもアイドルトーンは抑制されることが判る。

実験1の実施例において、基準信号に付与するジッターの大きさを「1p秒」に固定し、被測定信号に付与するジッターの大きさを「10p秒」、「20p秒」、「50p秒」、「100p秒」、「200p秒」、「500p秒」、「1000p秒」、「2000p秒」(実施例)とし、アイドルトーン分散装置の出力スペクトルのグラフを作成した。この結果を図28〜図35に示す。

なお、基準信号がジッターを含まず(ジッターの大きさが0p秒)、被測定信号に付与するジッターの大きさを「10p秒」、「20p秒」、「50p秒」、「100p秒」、「200p秒」、「500p秒」、「1000p秒」、「2000p秒」(実施例)とし、シミュレーションを行って、アイドルトーン分散装置の出力スペクトルのグラフを作成したところ、基準信号のジッターの大きさが1p秒の場合と、ほぼ同様の結果が得られた。これにより、被測定信号のみがジッターを含む場合でもアイドルトーンは抑制されることが判る。

また、実験3の図28〜図35に示すグラフと、実験1の図12〜図19に示すグラフとの対応するグラフ同士を比べると、実験1の実施例の方がベース部分の強度は高いことが判る。同様に、実験2についても実験1の実施例の方がベース部分の強度は高いことが判る。

これは、ジッターの大きさが同じ場合、基準信号と被測定信号とのいずれか一方のみにジッターを付与する場合に比べ、両方にジッターを付与する方が系に投入されるノイズのエネルギーが大きくなることに対応している。

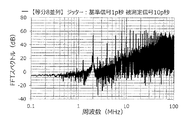

装置bを用い、基準信号には、共通のジッターを付与し、被測定信号には、FDSM20毎に独立してジッターを付与した。

また、基準信号に付与するジッターの大きさを「1p秒」とし、被測定信号に付与するジッターの大きさを「10p秒」とした(実施例)。

アイドルトーン分散装置から出力される周波数デルタシグマ変調信号について、含まれる周波数成分の強度を求め、アイドルトーン分散装置の出力スペクトルのグラフを作成した。この結果を図37に示す。

また、比較例として、装置bにおいて、基準信号および被測定信号にそれぞれジッターが含まれていない場合(ジッターの大きさが0p秒)について、シミュレーションを行って、アイドルトーン分散装置の出力スペクトルのグラフを作成した。この結果を図36に示す。

なお、基準信号がジッターを含まず(ジッターの大きさが0p秒)、被測定信号に付与するジッターの大きさを「10p秒」、「20p秒」、「50p秒」、「100p秒」、「200p秒」、「500p秒」、「1000p秒」、「2000p秒」(実施例)とし、シミュレーションを行って、アイドルトーン分散装置の出力スペクトルのグラフを作成したところ、基準信号のジッターの大きさが1p秒の場合と、ほぼ同様の結果が得られた。これにより、被測定信号のみがジッターを含む場合でもアイドルトーンは抑制されることが判る。

また、測定帯域の上限値を10MHzに設定する場合、実験1の実施例では、前述したように、ジッターの大きさの最適値は、500p秒程度であるが、実験4の実施例では、図43に示すように、ジッターの大きさの最適値は、1000p秒程度であり、実験1の実施例の2倍程度となっている。

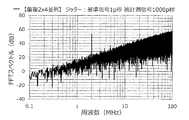

装置cを用い、基準信号には、共通のジッターを付与し、被測定信号には、FDSM20毎に独立してジッターを付与した。

また、基準信号に付与するジッターの大きさを「1p秒」とし、被測定信号に付与するジッターの大きさを「10p秒」とした(実施例)。

アイドルトーン分散装置から出力される周波数デルタシグマ変調信号について、含まれる周波数成分の強度を求め、アイドルトーン分散装置の出力スペクトルのグラフを作成した。この結果を図46に示す。

また、比較例として、装置cにおいて、基準信号および被測定信号にそれぞれジッターが含まれていない場合(ジッターの大きさが0p秒)について、シミュレーションを行って、アイドルトーン分散装置の出力スペクトルのグラフを作成した。この結果を図45に示す。

なお、基準信号がジッターを含まず(ジッターの大きさが0p秒)、被測定信号に付与するジッターの大きさを「10p秒」、「20p秒」、「50p秒」、「100p秒」、「200p秒」、「500p秒」、「1000p秒」、「2000p秒」、「3600p秒」(実施例)とし、シミュレーションを行って、アイドルトーン分散装置の出力スペクトルのグラフを作成したところ、基準信号のジッターの大きさが1p秒の場合と、ほぼ同様の結果が得られた。これにより、被測定信号のみがジッターを含む場合でもアイドルトーンは抑制されることが判る。

また、本実験では、図53に示すように、ジッターの大きさを「2000p秒」にした場合でも、2MHz未満の周波数のアイドルトーンを示すピーク(強度)が、検出対象の周波数である2MHzのピーク(強度)を上回った。

なお、被検出信号の周波数は、261.24MHz±0.5MHzであることから、ジッターの大きさの理論限界は、その周波数の逆数である約3820秒である。

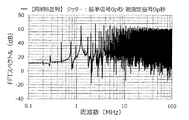

装置dを用い、基準信号および被測定信号に、独立してジッターを付与した。

また、基準信号に付与するジッターの大きさを「1p秒」とし、被測定信号に付与するジッターの大きさを「10p秒」とした(比較例)。

また、実験1の実施例と同様に、基準信号に付与するジッターおよび被測定信号に付与するジッターは、それぞれ、最大の周波数成分が130MHzで、130MHz以下の周波数成分を含んでいる、すなわち、アイドルトーンの周波数よりも高い周波数成分を含んでいる。

アイドルトーン分散装置から出力される周波数デルタシグマ変調信号について、含まれる周波数成分の強度を求め、アイドルトーン分散装置の出力スペクトルのグラフを作成した。この結果を図56に示す。

また、他の比較例として、基準信号に付与するジッターの大きさを「1p秒」に固定し、被測定信号に付与するジッターの大きさを「20p秒」、「50p秒」、「100p秒」、「200p秒」、「500p秒」、「1000p秒」、「2000p秒」、「3600p秒」とし、アイドルトーン分散装置の出力スペクトルのグラフを作成した。この結果を図57〜図64に示す。

そこで、図64に示すように、ジッターの大きさを「3600p秒」まで増やしたところ、2MHzのピークが、2MHz未満の周波数のアイドルトーンを示すピークを上回った。

また、実験6の図56〜図64に示すグラフと、実験5の図46〜図54に示すグラフとの対応するグラフ同士を比べると、実験6の比較例と実験5の実施例とでは、ジッターの大きさに対応するアイドルトーン抑制効果についてはほぼ同じであるが、実験5の実施例では、ベース部分の強度が低下する効果が得られ、ジッターの大きさが増大するほどその効果は顕著となる。

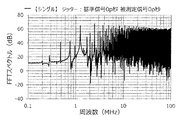

装置eを用い、基準信号に共通のジッターを付与し、また、被測定信号に共通のジッターを付与した。

また、基準信号に付与するジッターの大きさを「1p秒」とし、被測定信号に付与するジッターの大きさを「10p秒」とした(実施例)。

また、実験1の実施例と同様に、基準信号に付与するジッターおよび被測定信号に付与するジッターは、それぞれ、最大の周波数成分が130MHzで、130MHz以下の周波数成分を含んでいる、すなわち、アイドルトーンの周波数よりも高い周波数成分を含んでいる。

また、他の実施例として、基準信号に付与するジッターの大きさを「1p秒」に固定し、被測定信号に付与するジッターの大きさを「20p秒」、「50p秒」、「100p秒」、「200p秒」、「500p秒」、「1000p秒」、「2000p秒」とし、アイドルトーン分散装置の出力スペクトルのグラフを作成した。この結果を図66〜図72に示す。

なお、基準信号がジッターを含まず(ジッターの大きさが0p秒)、被測定信号に付与するジッターの大きさを「10p秒」、「20p秒」、「50p秒」、「100p秒」、「200p秒」、「500p秒」、「1000p秒」、「2000p秒」(実施例)とし、シミュレーションを行って、アイドルトーン分散装置の出力スペクトルのグラフを作成したところ、基準信号のジッターの大きさが1p秒の場合と、ほぼ同様の結果が得られた。これにより、被測定信号のみがジッターを含む場合でもアイドルトーンは抑制されることが判る。

また、実験7の図65〜図72に示すグラフと、実験3の図28〜図35に示すグラフとの対応するグラフ同士を比べると、実験7の実施例と実験3の実施例とでは、実験7の実施例の方がベース部分の強度は高いことが判る。これは、被検出信号に付与されるジッターが独立している場合には、合算したジッターの分布を表す分散はそれぞれの分散の和に近づくのに対し、被検出信号に付与されるジッターが共通である場合には、合算したジッターの分布を表す分散はそれぞれの分散の和よりも大きくなることに対応している。

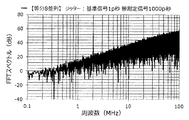

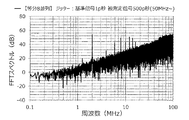

装置aを用い、基準信号には、共通のジッターを付与し、被測定信号には、FDSM20毎に独立してジッターを付与した。

また、基準信号に付与するジッターの大きさを「1p秒」とし、被測定信号に付与するジッターの大きさを「500p秒」とした(実施例)。

また、実験1の実施例と同様に、基準信号に付与するジッターおよび被測定信号に付与するジッターは、それぞれ、最大の周波数成分が130MHzで、130MHz以下の周波数成分を含んでいる、すなわち、アイドルトーンの周波数よりも高い周波数成分を含んでいる。また、ジッターに含まれる1MHz以下の周波数成分を除去するために、セレクター53において、1MHz以下の変動成分を除去した選択パターンを用いた。

また、ジッターに含まれる低周波数成分を除去することで、除去した周波数帯域において、ベース部分の強度が低下することが判る。

図80は、本発明の周波数比計測装置の実施形態を示すブロック図である。

以下、周波数比計測装置の実施形態について、前述した実施形態との相違点を中心に説明し、同様の事項については、その説明を省略する。

周波数比計測装置100は、アイドルトーン分散装置1と、アイドルトーン分散装置1から出力された周波数デルタシグマ変調信号Yに基づいて被測定信号Fxの周波数を示す周波数データDfを生成する周波数データ生成部40とを備えている。また、周波数データ生成部40は、アイドルトーン分散装置1の出力側(後段)に接続されている。また、周波数データ生成部40は、ローパスフィルター41と、ローパスフィルター41の出力側に接続されたスケーリング部42とを備えている。

また、周波数デルタシグマ変調信号Yが、ビットストリーム構成のアイドルトーン分散装置1からの出力であって、2fx<fcである場合、周波数デルタシグマ変調信号Yは、被測定信号Fxの2倍の周波数2fxと基準信号Fcの周波数fcとの比(2fx/fc)を、量子化誤差を含んだ形で時間経過と共にデジタル信号列として出力されるものである。

また、スケーリング部42は、ローパスフィルター41の出力データ41aに補正係数を乗算して周波数データDfを生成する。例えば、周波数データ生成部40の入力側(前段)にビットストリーム構成のアイドルトーン分散装置1が設けられており、例えば、被測定信号Fxの周波数fxが0.1MHz、基準信号Fcの周波数fcが2MHzとすると、2fx/fc=0.1となる。また、周波数デルタシグマ変調信号Yは、被測定信号Fxの周波数fxに比例するので、補正係数は1Mとすればよい。

なお、周波数比計測装置100は、例えば、スケーリング部42が省略され、被測定信号Fxと基準信号Fcとの周波数比を示す周波数比データを生成するようになっていてもよく、また、ローパスフィルター41が省略されていてもよい。

Claims (9)

- 基準信号と被測定信号とのいずれか一方を用いて他方を周波数デルタシグマ変調してアイドルトーンを分散させた周波数デルタシグマ変調信号を出力するアイドルトーン分散装置であって、

n(nは2以上の任意の自然数)個の周波数デルタシグマ変調部と、

前記n個の周波数デルタシグマ変調部の出力信号を加算して前記周波数デルタシグマ変調信号を出力する加算部と、

前記周波数デルタシグマ変調部の出力信号のアイドルトーンの周波数よりも高い周波数成分を含むジッターを生成するハードウェアと、を備え、

前記n個の周波数デルタシグマ変調部の各々は、前記基準信号と前記被測定信号とのいずれか一方を用いて他方を周波数デルタシグマ変調し、

前記基準信号と前記被測定信号との少なくとも一方は、前記ジッターを有することを特徴とするアイドルトーン分散装置。 - 基準信号と被測定信号とのいずれか一方を用いて他方を周波数デルタシグマ変調してアイドルトーンを分散させた周波数デルタシグマ変調信号を出力するアイドルトーン分散装置であって、

n(nは2以上の任意の自然数)個の周波数デルタシグマ変調部と、

前記被測定信号と前記基準信号との位相を調整して、n組の出力被測定信号および出力基準信号を生成して、各組の前記出力被測定信号および前記出力基準信号を前記n個の周波数デルタシグマ変調部の各々に供給する位相調整部と、

前記n個の周波数デルタシグマ変調部の出力信号を加算して前記周波数デルタシグマ変調信号を出力する加算部と、

前記周波数デルタシグマ変調部の出力信号のアイドルトーンの周波数よりも高い周波数成分を含むジッターを生成するハードウェアと、を備え、

前記位相調整部は、前記n個の周波数デルタシグマ変調部のうちの少なくとも一部の前記周波数デルタシグマ変調部の出力信号のアイドルトーンの位相が互いに異なるように、前記被測定信号と前記基準信号との位相を調整して、前記n組の出力被測定信号および出力基準信号を生成し、

前記n個の周波数デルタシグマ変調部の各々は、前記位相調整部から供給される前記出力基準信号と前記出力被測定信号とのいずれか一方を用いて他方を周波数デルタシグマ変調し、

前記出力基準信号と前記出力被測定信号とのうちの少なくとも1つは、前記ジッターを有することを特徴とするアイドルトーン分散装置。 - 所定時間をD、前記被測定信号の1周期または前記基準信号の1周期をT、mをn以下の任意の自然数、mD/nTを整数、mD/nTとmとが互いに素、i(iはn−1以下の任意の自然数)番目の周波数デルタシグマ変調部に供給する出力被測定信号と出力基準信号との位相差をPiとしたとき、

前記位相調整部は、D/n=Pi+1−Piとなるように、前記被測定信号と前記基準信号との位相を調整して、前記n組の出力被測定信号および出力基準信号を生成する請求項2に記載のアイドルトーン分散装置。 - 前記位相調整部は、前記n個の周波数デルタシグマ変調部のうちの一部の前記周波数デルタシグマ変調部の出力信号のアイドルトーンの位相が互いに異なるように、前記被測定信号と前記基準信号との位相を調整して、前記n組の出力被測定信号および出力基準信号を生成する請求項2に記載のアイドルトーン分散装置。

- 所定時間をD、前記被測定信号の1周期または前記基準信号の1周期をT、mをn以下の任意の自然数、mD/nTを整数、mD/nTとmとが互いに素、i(iはn−1以下の任意の自然数)番目の周波数デルタシグマ変調部に供給する出力被測定信号と出力基準信号との位相差をPiとしたとき、

D/n≠Pi+1−Piである請求項2に記載のアイドルトーン分散装置。 - 前記ジッターは、前記アイドルトーンが有する周波数成分のうち、強度の最も大きい成分の周波数よりも高い周波数成分を含む請求項1ないし5のいずれか1項に記載のアイドルトーン分散装置。

- 前記ハードウェアは、ジッター生成部である請求項1ないし6のいずれか1項に記載のアイドルトーン分散装置。

- 前記ジッターの大きさは、前記基準信号の周波数、前記被測定信号の周波数、前記被測定信号の測定帯域および前記周波数デルタシグマ変調部の個数のうちの少なくとも1つに基づいて決定される請求項1ないし7のいずれか1項に記載のアイドルトーン分散装置。

- 請求項1ないし8のいずれか1項に記載のアイドルトーン分散装置を備え、

前記被測定信号と前記基準信号との周波数比を測定することを特徴とする周波数比計測装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017105463A JP6972660B2 (ja) | 2017-05-29 | 2017-05-29 | アイドルトーン分散装置および周波数比計測装置 |

| US15/987,099 US10355708B2 (en) | 2017-05-29 | 2018-05-23 | Idle tone dispersion device and frequency ratio measuring device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017105463A JP6972660B2 (ja) | 2017-05-29 | 2017-05-29 | アイドルトーン分散装置および周波数比計測装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018201142A JP2018201142A (ja) | 2018-12-20 |

| JP6972660B2 true JP6972660B2 (ja) | 2021-11-24 |

Family

ID=64401522

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017105463A Active JP6972660B2 (ja) | 2017-05-29 | 2017-05-29 | アイドルトーン分散装置および周波数比計測装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US10355708B2 (ja) |

| JP (1) | JP6972660B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2531532B (en) * | 2014-10-20 | 2020-12-30 | Cambridge Consultants | Radio frequency amplifier |

| JP2021036656A (ja) | 2019-08-30 | 2021-03-04 | セイコーエプソン株式会社 | 周波数比計測装置 |

| US11630161B1 (en) * | 2021-11-08 | 2023-04-18 | Advanced Micro Devices, Inc. | Flexible circuit for droop detection |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4458165A (en) | 1983-03-23 | 1984-07-03 | Tektronix, Inc. | Programmable delay circuit |

| JPH06104751A (ja) * | 1992-09-17 | 1994-04-15 | Fujitsu Ltd | Δς変調型a/d変換器 |

| JP3433655B2 (ja) * | 1997-10-14 | 2003-08-04 | ヤマハ株式会社 | 波形整形装置およびσδ型d/a変換装置 |

| JP3625400B2 (ja) | 1999-09-22 | 2005-03-02 | 株式会社東芝 | 可変遅延素子のテスト回路 |

| DE102005026899B4 (de) * | 2005-06-10 | 2007-02-22 | Infineon Technologies Ag | Kompensationsschaltung zur Takt-Jitter-Kompensation |

| US7792232B2 (en) * | 2005-06-30 | 2010-09-07 | Intel Corporation | Method and system for link jitter compensation including a fast data recovery circuit |

| US7295642B2 (en) * | 2005-06-30 | 2007-11-13 | Teradyne, Inc. | Jitter compensation and generation in testing communication devices |

| US8045670B2 (en) * | 2007-06-22 | 2011-10-25 | Texas Instruments Incorporated | Interpolative all-digital phase locked loop |

| JP5158764B2 (ja) | 2007-09-27 | 2013-03-06 | 川崎マイクロエレクトロニクス株式会社 | 位相シフト方法および回路 |

| US8594253B2 (en) * | 2007-11-16 | 2013-11-26 | St-Ericsson Sa | Jitter compensation |

| JP2012052913A (ja) * | 2010-09-01 | 2012-03-15 | Advantest Corp | 試験装置および信号発生装置 |

| JP6387676B2 (ja) | 2014-05-15 | 2018-09-12 | セイコーエプソン株式会社 | アイドルトーン分散装置及び周波数計測装置 |

| JP6519776B2 (ja) * | 2015-02-24 | 2019-05-29 | 横河電機株式会社 | 周波数カウンタおよび周波数カウンタを内蔵したフィールド機器 |

| US10175130B2 (en) * | 2015-04-20 | 2019-01-08 | Infineon Technologies Ag | System and method for a MEMS sensor |

-

2017

- 2017-05-29 JP JP2017105463A patent/JP6972660B2/ja active Active

-

2018

- 2018-05-23 US US15/987,099 patent/US10355708B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20180343014A1 (en) | 2018-11-29 |

| JP2018201142A (ja) | 2018-12-20 |

| US10355708B2 (en) | 2019-07-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101108132B1 (ko) | 시험 장치 및 시험 방법 | |

| US9231613B2 (en) | Idle tone dispersion device and frequency measurement device | |

| US10491201B2 (en) | Delay circuit, count value generation circuit, and physical quantity sensor | |

| KR100865662B1 (ko) | 노이즈 형성 디지털 주파수 합성 | |

| Balestrieri et al. | Review on jitter terminology and definitions | |

| JP6972660B2 (ja) | アイドルトーン分散装置および周波数比計測装置 | |

| JP5337157B2 (ja) | 試験装置、及び試験方法 | |

| US7977996B1 (en) | Pulse generator with precision edge placement | |

| CN114070271A (zh) | 基于相位插值的时钟抖动产生装置及其方法 | |

| US7664166B2 (en) | Pleisiochronous repeater system and components thereof | |

| JP5208211B2 (ja) | 試験装置、及び試験方法 | |

| JP5432352B1 (ja) | パルスパターン発生装置及びパルスパターン発生方法 | |

| JP6733237B2 (ja) | 周波数デルタシグマ変調信号出力装置 | |

| JP5410454B2 (ja) | パルスパターン発生装置及び該装置を用いた誤り率測定システム並びにパルスパターン発生方法 | |

| JP2010057174A (ja) | パルスエッジシフトの復調方法および復調器 | |

| JP6761630B2 (ja) | 周波数シンセサイザー | |

| JP3081593B2 (ja) | サンプリング周波数制御を有する通信信号レシーバ | |

| EP2528230B1 (en) | Signal processing | |

| JP5176545B2 (ja) | 信号測定装置 | |

| JP2008118338A (ja) | ジッタ発生装置 | |

| Kim et al. | Analysis and simulation of jitter for high speed channels in VLSI systems | |

| JP2017163378A (ja) | 周波数デルタシグマ変調信号出力装置 | |

| KR20240149298A (ko) | 클럭 생성 장치 및 이를 이용한 클럭 생성 방법 | |

| JP2757090B2 (ja) | 分周逓倍回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200423 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210524 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210727 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210916 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20211005 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20211018 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6972660 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |