JP6926982B2 - 電源制御回路および環境発電装置 - Google Patents

電源制御回路および環境発電装置 Download PDFInfo

- Publication number

- JP6926982B2 JP6926982B2 JP2017222253A JP2017222253A JP6926982B2 JP 6926982 B2 JP6926982 B2 JP 6926982B2 JP 2017222253 A JP2017222253 A JP 2017222253A JP 2017222253 A JP2017222253 A JP 2017222253A JP 6926982 B2 JP6926982 B2 JP 6926982B2

- Authority

- JP

- Japan

- Prior art keywords

- switch

- circuit

- control signal

- energy harvesting

- resistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000003306 harvesting Methods 0.000 title claims description 110

- 239000003990 capacitor Substances 0.000 claims description 52

- 230000008094 contradictory effect Effects 0.000 claims 2

- 238000001514 detection method Methods 0.000 description 31

- 238000010248 power generation Methods 0.000 description 25

- 238000010586 diagram Methods 0.000 description 18

- 230000007423 decrease Effects 0.000 description 11

- 238000000034 method Methods 0.000 description 7

- 230000007613 environmental effect Effects 0.000 description 3

- 238000012544 monitoring process Methods 0.000 description 3

- 230000000087 stabilizing effect Effects 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/04—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices

- H01L31/053—Energy storage means directly associated or integrated with the PV cell, e.g. a capacitor integrated with a PV cell

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02J—CIRCUIT ARRANGEMENTS OR SYSTEMS FOR SUPPLYING OR DISTRIBUTING ELECTRIC POWER; SYSTEMS FOR STORING ELECTRIC ENERGY

- H02J50/00—Circuit arrangements or systems for wireless supply or distribution of electric power

- H02J50/05—Circuit arrangements or systems for wireless supply or distribution of electric power using capacitive coupling

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02J—CIRCUIT ARRANGEMENTS OR SYSTEMS FOR SUPPLYING OR DISTRIBUTING ELECTRIC POWER; SYSTEMS FOR STORING ELECTRIC ENERGY

- H02J7/00—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries

- H02J7/34—Parallel operation in networks using both storage and other dc sources, e.g. providing buffering

- H02J7/345—Parallel operation in networks using both storage and other dc sources, e.g. providing buffering using capacitors as storage or buffering devices

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02J—CIRCUIT ARRANGEMENTS OR SYSTEMS FOR SUPPLYING OR DISTRIBUTING ELECTRIC POWER; SYSTEMS FOR STORING ELECTRIC ENERGY

- H02J7/00—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries

- H02J7/34—Parallel operation in networks using both storage and other dc sources, e.g. providing buffering

- H02J7/35—Parallel operation in networks using both storage and other dc sources, e.g. providing buffering with light sensitive cells

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02N—ELECTRIC MACHINES NOT OTHERWISE PROVIDED FOR

- H02N11/00—Generators or motors not provided for elsewhere; Alleged perpetua mobilia obtained by electric or magnetic means

- H02N11/002—Generators

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

Description

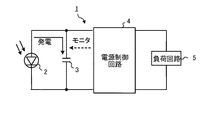

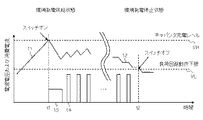

図1は、第1の実施形態における、環境発電装置の一例を示す機能ブロック図である。図1において環境発電装置1は、環境発電素子2、キャパシタ3、電源制御回路4、負荷回路5を有する。端子VDDおよび端子VSSは、環境発電素子2と他の回路とを電気的に接続する共有端子である。

図3は、第2の実施形態における、環境発電装置の一例を示す回路図である。図3において環境発電装置1dは、太陽光発電素子2a、キャパシタ3a、電源制御回路4d、および負荷回路5aを有する。

図4は、第3の実施形態における、環境発電装置の一例を示す回路図である。図4において環境発電装置1aは、太陽光発電素子2a、キャパシタ3a、電源制御回路4a、および負荷回路5aを有する。ここで、他の環境発電装置と同一の構成要素には同一の参照符号を付与し、その説明を省略する。

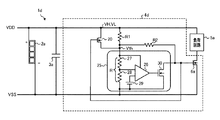

図5は、第4の実施形態における、環境発電装置の一例を示す回路図である。図4において環境発電装置1bは、太陽光発電素子2a、キャパシタ3a、電源制御回路4b、および負荷回路5aを有する。図5の環境発電装置1bは、図4の環境発電装置1aに対し、論理反転回路21の具体例である論理反転回路21aを有する。電流I1は、抵抗R1、R2、およびスイッチ30を通って、端子VDDから端子VSSまで流れる電流である。電流I2は、抵抗R3およびスイッチ32を通って、端子VDDから端子VSSまで流れる電流である。電流I3は、抵抗R1とスイッチ22の並列回路および抵抗27、抵抗28を通って、端子VDDから端子VSSまで流れる電流である。

図7は、第5の実施形態における、環境発電装置の一例を示す回路図である。図7において環境発電装置1cは、太陽光発電素子2a、キャパシタ3a、電源制御回路4c、および負荷回路5aを有する。図7の環境発電装置1cは、図3の環境発電装置1aに対し、論理反転回路21の他の具体例である論理反転回路21bを有する。

図9は、第6の実施形態における、環境発電装置の一例を示す回路図である。図9において環境発電装置1dは、太陽光発電素子2a、キャパシタ3a、電源制御回路4d、および負荷回路5aを有する。ここで、他の環境発電装置と同一の構成要素には同一の参照符号を付与し、その説明を省略する。

図12は、第7の実施形態における、環境発電装置の一例を示す回路図である。図12において環境発電装置1fは、太陽光発電素子2a、キャパシタ3a、電源制御回路4f、および負荷回路5aを有する。ここで、他の環境発電装置と同一の構成要素には同一の参照符号を付与し、その説明を省略する。

2:環境発電素子

3:キャパシタ

4:電源制御回路

5:負荷回路

6a:スイッチ

20:スイッチ

30:スイッチ

21:論理反転回路

25:電圧検出回路

26:比較器

Claims (4)

- 第1基準ノードと第2基準ノードとの間に並列接続された電源およびキャパシタと、前記キャパシタから供給される電荷により動作する負荷回路との接続を制御する電源制御回路であって、

前記第1基準ノードと前記第2基準ノードの電位差に応じて第1制御信号を出力する第1制御回路と、

前記第1制御信号の論理を反転させた第2制御信号を出力する第2制御回路と、

前記第2制御信号に応じて、前記キャパシタと前記負荷回路との電気的接続をオンオフする第1スイッチと、

前記第1基準ノードと前記第1制御回路との間に接続された第1抵抗と、

前記第1抵抗と前記第1制御回路との間のノードと前記第1制御信号を出力する第1出力ノードとの間に接続された第2抵抗と、

前記第1抵抗に並列接続され、前記第2制御信号に応じてオンオフする第2スイッチとを有し、

前記第1スイッチおよび前記第2スイッチは、前記第2制御信号の電圧値に基づいてオンオフする、電源制御回路。 - 第1基準ノードと第2基準ノードとの間に並列接続された電源およびキャパシタと、前記キャパシタから供給される電荷により動作する負荷回路との接続を制御する電源制御回路であって、

前記第1基準ノードと前記第2基準ノードの電位差に応じて第1制御信号を出力する第1制御回路と、

前記第1制御信号の論理を反転させた第2制御信号を出力する第2制御回路と、

前記第2制御信号に応じて、前記キャパシタと前記負荷回路との電気的接続をオンオフする第1スイッチと、

前記第1基準ノードと前記第1制御回路との間に接続された第1抵抗と、

前記第1抵抗と前記第1制御回路との間のノードと前記第1制御信号を出力する第1出力ノードとの間に接続された第2抵抗と、

前記第1抵抗に並列接続され、前記第1制御信号に応じてオンオフする第2スイッチとを有し、

前記第1スイッチと前記第2スイッチは相反する論理でオンオフし、

前記第1スイッチは前記第2制御信号の電圧値に基づいてオンオフし、

前記第2スイッチは前記第1制御信号の電圧値に基づいてオンオフする、電源制御回路。 - 第1基準ノードと第2基準ノードに接続された環境発電素子と、

前記環境発電素子に並列接続されたキャパシタと、

前記キャパシタから供給される電荷により動作する負荷回路と、

前記第1基準ノードと前記第2基準ノードの電位差に応じて第1制御信号を出力する第1制御回路と、

前記第1制御信号の論理を反転させた第2制御信号を出力する第2制御回路と、

前記第2制御信号に応じて、前記キャパシタと前記負荷回路との電気的接続をオンオフする第1スイッチと、

前記第1基準ノードと前記第1制御回路との間に接続された第1抵抗と、

前記第1抵抗と前記第1制御回路との間のノードと前記第1制御信号を出力する第1出力ノードとの間に接続された第2抵抗と、

前記第1抵抗に並列接続され、前記第2制御信号に応じてオンオフする第2スイッチと、

を有し、

前記第1スイッチおよび前記第2スイッチは、前記第2制御信号の電圧値に基づいてオンオフする、環境発電装置。 - 第1基準ノードと第2基準ノードに接続された環境発電素子と、

前記環境発電素子に並列接続されたキャパシタと、

前記キャパシタから供給される電荷により動作する負荷回路と、

前記第1基準ノードと前記第2基準ノードの電位差に応じて第1制御信号を出力する第1制御回路と、

前記第1制御信号の論理を反転させた第2制御信号を出力する第2制御回路と、

前記第2制御信号に応じて、前記キャパシタと前記負荷回路との電気的接続をオンオフする第1スイッチと、

前記第1基準ノードと前記第1制御回路との間に接続された第1抵抗と、

前記第1抵抗と前記第1制御回路との間のノードと前記第1制御信号を出力する第1出力ノードとの間に接続された第2抵抗と、

前記第1抵抗に並列接続され、前記第1制御信号に応じてオンオフする第2スイッチと、

を有し、

前記第1スイッチと前記第2スイッチは相反する論理でオンオフし、

前記第1スイッチは前記第2制御信号の電圧値に基づいてオンオフし、

前記第2スイッチは前記第1制御信号の電圧値に基づいてオンオフする、環境発電装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016227303 | 2016-11-22 | ||

| JP2016227303 | 2016-11-22 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018088249A JP2018088249A (ja) | 2018-06-07 |

| JP6926982B2 true JP6926982B2 (ja) | 2021-08-25 |

Family

ID=62146951

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017222253A Active JP6926982B2 (ja) | 2016-11-22 | 2017-11-17 | 電源制御回路および環境発電装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US10488904B2 (ja) |

| JP (1) | JP6926982B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10756563B2 (en) * | 2017-12-15 | 2020-08-25 | Datamax-O'neil Corporation | Powering devices using low-current power sources |

| IT201900004149A1 (it) * | 2019-03-21 | 2020-09-21 | St Microelectronics Srl | Sensore, sistema e procedimento di funzionamento corrispondenti |

| WO2023118850A1 (en) * | 2021-12-22 | 2023-06-29 | Lightricity Limited | Energy harvesting electronic devices with ultra-low power consumption |

| US11881849B2 (en) * | 2022-05-03 | 2024-01-23 | Littelfuse, Inc. | Solid state relay harvesting power from load by measuring stored energy |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0749721A (ja) * | 1993-08-09 | 1995-02-21 | Sanyo Electric Co Ltd | 太陽電池を電源とする電気機器の保護装置 |

| JPH0818010A (ja) | 1994-06-28 | 1996-01-19 | Hitachi Ltd | 半導体集積回路 |

| JP4384272B2 (ja) * | 1998-01-27 | 2009-12-16 | パナソニック電工株式会社 | 電子式自動点滅器 |

| JP2000357948A (ja) * | 1999-06-15 | 2000-12-26 | Oki Electric Ind Co Ltd | 電圧検出回路 |

| JP2001209111A (ja) * | 2000-01-27 | 2001-08-03 | Olympus Optical Co Ltd | カメラ |

| US8228194B2 (en) * | 2004-10-28 | 2012-07-24 | University Of Pittsburgh - Of The Commonwealth System Of Higher Education | Recharging apparatus |

| JP5554108B2 (ja) * | 2010-03-26 | 2014-07-23 | パナソニック株式会社 | 過電流防止式電源装置及びそれを用いた照明器具 |

| JP5646943B2 (ja) * | 2010-10-12 | 2014-12-24 | ラピスセミコンダクタ株式会社 | 充電制御システム及び充電制御装置 |

| US8953350B2 (en) * | 2011-04-08 | 2015-02-10 | Sunedison, Inc. | Photovoltaic power converters |

| JP6500639B2 (ja) | 2015-01-29 | 2019-04-17 | 富士通株式会社 | 電源制御回路、環境発電装置および環境発電装置の制御方法 |

-

2017

- 2017-11-15 US US15/813,241 patent/US10488904B2/en active Active

- 2017-11-17 JP JP2017222253A patent/JP6926982B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2018088249A (ja) | 2018-06-07 |

| US20180143675A1 (en) | 2018-05-24 |

| US10488904B2 (en) | 2019-11-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6926982B2 (ja) | 電源制御回路および環境発電装置 | |

| KR100618518B1 (ko) | 리셋 회로 | |

| JP6118599B2 (ja) | パワーオンリセット回路、電源回路および電源システム | |

| US20220294426A1 (en) | Ultra-low energy per cycle oscillator topology | |

| JP2011223829A (ja) | 負電圧チャージポンプ回路の制御回路および負電圧チャージポンプ回路、ならびにそれらを用いた電子機器およびオーディオシステム | |

| JP2011221982A (ja) | 基準電圧回路 | |

| US9454165B2 (en) | Semiconductor device and current control method that controls amount of current used for voltage generation based on connection state of external capacitor | |

| US20140084983A1 (en) | Semiconductor device | |

| JP4439974B2 (ja) | 電源電圧監視回路 | |

| JP2016146156A (ja) | 電源制御回路、環境発電装置および環境発電装置の制御方法 | |

| JP2006115594A (ja) | 誤動作防止回路 | |

| JP2009277122A (ja) | 電源電圧監視回路 | |

| JP2008203098A (ja) | タイマー回路 | |

| JP2007151322A (ja) | 電源回路およびdc−dcコンバータ | |

| JP7431632B2 (ja) | アナログスイッチ回路 | |

| KR20060053977A (ko) | 반도체 집적회로 및 승압방법 | |

| US10644694B2 (en) | Power-on reset circuit with hysteresis | |

| JP5889700B2 (ja) | パワーオン・リセット回路及び半導体装置 | |

| CN102621368A (zh) | 振荡停止检测电路、半导体装置、钟表以及电子设备 | |

| JP2006074210A (ja) | 半導体集積回路装置のリセット回路 | |

| JP2008017101A (ja) | パワーオンリセット回路 | |

| JP5687091B2 (ja) | 電源電圧検出回路 | |

| CN104137416B (zh) | 电压检测电路和电子电路 | |

| JP2006108778A (ja) | 出力回路 | |

| JP5629188B2 (ja) | 減電圧リセット回路及びこれを用いた電源装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20180528 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200807 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20210421 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210427 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210622 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210706 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210719 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6926982 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |