JP6798942B2 - トランジスタおよび半導体装置 - Google Patents

トランジスタおよび半導体装置 Download PDFInfo

- Publication number

- JP6798942B2 JP6798942B2 JP2017124719A JP2017124719A JP6798942B2 JP 6798942 B2 JP6798942 B2 JP 6798942B2 JP 2017124719 A JP2017124719 A JP 2017124719A JP 2017124719 A JP2017124719 A JP 2017124719A JP 6798942 B2 JP6798942 B2 JP 6798942B2

- Authority

- JP

- Japan

- Prior art keywords

- oxide

- insulator

- metal oxide

- oxide layer

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title description 99

- 239000012212 insulator Substances 0.000 claims description 533

- 229910044991 metal oxide Inorganic materials 0.000 claims description 150

- 150000004706 metal oxides Chemical class 0.000 claims description 144

- 229910052738 indium Inorganic materials 0.000 claims description 37

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims description 37

- 229910052733 gallium Inorganic materials 0.000 claims description 31

- 229910052710 silicon Inorganic materials 0.000 claims description 29

- 229910052721 tungsten Inorganic materials 0.000 claims description 28

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical group [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 claims description 27

- 239000011701 zinc Substances 0.000 claims description 27

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical group [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 25

- 239000010703 silicon Chemical group 0.000 claims description 25

- 239000010937 tungsten Substances 0.000 claims description 24

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 23

- 229910052782 aluminium Inorganic materials 0.000 claims description 23

- 239000010936 titanium Substances 0.000 claims description 23

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 claims description 22

- -1 lantern Chemical compound 0.000 claims description 22

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 22

- 229910052725 zinc Inorganic materials 0.000 claims description 22

- 229910052735 hafnium Inorganic materials 0.000 claims description 21

- 229910052719 titanium Inorganic materials 0.000 claims description 21

- 239000010949 copper Chemical group 0.000 claims description 20

- 229910052715 tantalum Inorganic materials 0.000 claims description 20

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 claims description 19

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical group [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 19

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 17

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 claims description 16

- 229910052796 boron Inorganic materials 0.000 claims description 15

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 claims description 15

- 229910052726 zirconium Inorganic materials 0.000 claims description 15

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical group [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 14

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 claims description 14

- 229910052779 Neodymium Inorganic materials 0.000 claims description 14

- 229910052802 copper Inorganic materials 0.000 claims description 14

- 229910052750 molybdenum Inorganic materials 0.000 claims description 14

- 239000011733 molybdenum Substances 0.000 claims description 14

- 229910052720 vanadium Inorganic materials 0.000 claims description 14

- 239000000969 carrier Substances 0.000 claims description 13

- 229910052727 yttrium Inorganic materials 0.000 claims description 12

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical group [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 claims description 11

- 229910052684 Cerium Inorganic materials 0.000 claims description 11

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 claims description 11

- 229910052732 germanium Inorganic materials 0.000 claims description 11

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 claims description 11

- 229910052742 iron Inorganic materials 0.000 claims description 11

- 229910052759 nickel Inorganic materials 0.000 claims description 11

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 claims description 10

- 229910052790 beryllium Inorganic materials 0.000 claims description 8

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical group [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 claims description 8

- 229910052746 lanthanum Inorganic materials 0.000 claims description 6

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 claims description 6

- ATBAMAFKBVZNFJ-UHFFFAOYSA-N beryllium atom Chemical group [Be] ATBAMAFKBVZNFJ-UHFFFAOYSA-N 0.000 claims description 4

- GWXLDORMOJMVQZ-UHFFFAOYSA-N cerium Chemical compound [Ce] GWXLDORMOJMVQZ-UHFFFAOYSA-N 0.000 claims 6

- LEONUFNNVUYDNQ-UHFFFAOYSA-N vanadium atom Chemical group [V] LEONUFNNVUYDNQ-UHFFFAOYSA-N 0.000 claims 6

- 239000004020 conductor Substances 0.000 description 413

- 239000010408 film Substances 0.000 description 169

- 230000006870 function Effects 0.000 description 136

- 238000000034 method Methods 0.000 description 120

- 229910052760 oxygen Inorganic materials 0.000 description 100

- 239000001301 oxygen Substances 0.000 description 100

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 98

- 239000000758 substrate Substances 0.000 description 90

- 239000010410 layer Substances 0.000 description 68

- 229910052739 hydrogen Inorganic materials 0.000 description 67

- 239000001257 hydrogen Substances 0.000 description 66

- 230000004888 barrier function Effects 0.000 description 65

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 57

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 55

- 239000000463 material Substances 0.000 description 48

- 229910052814 silicon oxide Inorganic materials 0.000 description 39

- 238000003860 storage Methods 0.000 description 34

- 238000004544 sputter deposition Methods 0.000 description 33

- 238000005229 chemical vapour deposition Methods 0.000 description 32

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 31

- 230000015572 biosynthetic process Effects 0.000 description 29

- 239000012535 impurity Substances 0.000 description 29

- 239000007789 gas Substances 0.000 description 28

- 238000010438 heat treatment Methods 0.000 description 28

- 229910052581 Si3N4 Inorganic materials 0.000 description 27

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 26

- 238000000231 atomic layer deposition Methods 0.000 description 26

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 24

- 229910052757 nitrogen Inorganic materials 0.000 description 23

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 22

- 229910001868 water Inorganic materials 0.000 description 22

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 21

- 238000005477 sputtering target Methods 0.000 description 20

- 229910052751 metal Inorganic materials 0.000 description 19

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 18

- 239000002184 metal Substances 0.000 description 18

- 238000004549 pulsed laser deposition Methods 0.000 description 18

- 238000001451 molecular beam epitaxy Methods 0.000 description 15

- 239000011787 zinc oxide Substances 0.000 description 13

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 12

- 229910001195 gallium oxide Inorganic materials 0.000 description 12

- 238000004519 manufacturing process Methods 0.000 description 12

- 230000003647 oxidation Effects 0.000 description 12

- 238000007254 oxidation reaction Methods 0.000 description 12

- 239000012298 atmosphere Substances 0.000 description 11

- 238000009792 diffusion process Methods 0.000 description 11

- 238000001312 dry etching Methods 0.000 description 11

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 11

- 230000005684 electric field Effects 0.000 description 10

- 238000005530 etching Methods 0.000 description 10

- 229910000449 hafnium oxide Inorganic materials 0.000 description 10

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 10

- 230000001965 increasing effect Effects 0.000 description 10

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 10

- 239000000203 mixture Substances 0.000 description 10

- 150000004767 nitrides Chemical class 0.000 description 10

- 230000008569 process Effects 0.000 description 10

- 206010021143 Hypoxia Diseases 0.000 description 9

- 229910052786 argon Inorganic materials 0.000 description 9

- 150000002431 hydrogen Chemical class 0.000 description 9

- 229910052749 magnesium Inorganic materials 0.000 description 9

- 239000011777 magnesium Substances 0.000 description 9

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 9

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 8

- 238000010586 diagram Methods 0.000 description 8

- 229910003437 indium oxide Inorganic materials 0.000 description 8

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 8

- 239000011347 resin Substances 0.000 description 8

- 229920005989 resin Polymers 0.000 description 8

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 7

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 7

- 239000000956 alloy Substances 0.000 description 7

- 229910001882 dioxygen Inorganic materials 0.000 description 7

- 230000003071 parasitic effect Effects 0.000 description 7

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 6

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 6

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 6

- 229910052799 carbon Inorganic materials 0.000 description 6

- 239000012528 membrane Substances 0.000 description 6

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 6

- 229910052698 phosphorus Inorganic materials 0.000 description 6

- 239000011574 phosphorus Substances 0.000 description 6

- 238000009832 plasma treatment Methods 0.000 description 6

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 6

- 239000010409 thin film Substances 0.000 description 6

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 6

- 229910001930 tungsten oxide Inorganic materials 0.000 description 6

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 5

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 5

- 238000006243 chemical reaction Methods 0.000 description 5

- 239000011651 chromium Substances 0.000 description 5

- 239000002131 composite material Substances 0.000 description 5

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 5

- 239000013078 crystal Substances 0.000 description 5

- 230000006378 damage Effects 0.000 description 5

- 230000007547 defect Effects 0.000 description 5

- 229910001873 dinitrogen Inorganic materials 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 229910052731 fluorine Inorganic materials 0.000 description 5

- 239000011737 fluorine Substances 0.000 description 5

- 239000011810 insulating material Substances 0.000 description 5

- 238000001459 lithography Methods 0.000 description 5

- 239000007769 metal material Substances 0.000 description 5

- 239000002245 particle Substances 0.000 description 5

- 239000002994 raw material Substances 0.000 description 5

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 4

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 4

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 4

- 239000010931 gold Substances 0.000 description 4

- 239000011261 inert gas Substances 0.000 description 4

- 238000009413 insulation Methods 0.000 description 4

- 230000010354 integration Effects 0.000 description 4

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 4

- 239000012299 nitrogen atmosphere Substances 0.000 description 4

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 4

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 4

- 238000001039 wet etching Methods 0.000 description 4

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 3

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 3

- 230000009471 action Effects 0.000 description 3

- 239000004760 aramid Substances 0.000 description 3

- 229920003235 aromatic polyamide Polymers 0.000 description 3

- 229910052810 boron oxide Inorganic materials 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- JKWMSGQKBLHBQQ-UHFFFAOYSA-N diboron trioxide Chemical compound O=BOB=O JKWMSGQKBLHBQQ-UHFFFAOYSA-N 0.000 description 3

- 238000007667 floating Methods 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- NJWNEWQMQCGRDO-UHFFFAOYSA-N indium zinc Chemical compound [Zn].[In] NJWNEWQMQCGRDO-UHFFFAOYSA-N 0.000 description 3

- 239000011156 metal matrix composite Substances 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 239000004332 silver Substances 0.000 description 3

- 239000002356 single layer Substances 0.000 description 3

- 239000000243 solution Substances 0.000 description 3

- 229910052718 tin Inorganic materials 0.000 description 3

- GPPXJZIENCGNKB-UHFFFAOYSA-N vanadium Chemical group [V]#[V] GPPXJZIENCGNKB-UHFFFAOYSA-N 0.000 description 3

- 238000004435 EPR spectroscopy Methods 0.000 description 2

- 239000004677 Nylon Substances 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 125000004429 atom Chemical group 0.000 description 2

- 238000005452 bending Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 238000010894 electron beam technology Methods 0.000 description 2

- 239000000835 fiber Substances 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 2

- 230000001939 inductive effect Effects 0.000 description 2

- 238000010884 ion-beam technique Methods 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 2

- 239000000395 magnesium oxide Substances 0.000 description 2

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229910052758 niobium Inorganic materials 0.000 description 2

- 239000010955 niobium Substances 0.000 description 2

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 2

- MWUXSHHQAYIFBG-UHFFFAOYSA-N nitrogen oxide Inorganic materials O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 2

- 229920001778 nylon Polymers 0.000 description 2

- 230000001590 oxidative effect Effects 0.000 description 2

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 2

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 2

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 229920000515 polycarbonate Polymers 0.000 description 2

- 239000004417 polycarbonate Substances 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920000728 polyester Polymers 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 229920000098 polyolefin Polymers 0.000 description 2

- 239000011148 porous material Substances 0.000 description 2

- 239000000047 product Substances 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 239000011819 refractory material Substances 0.000 description 2

- 230000000717 retained effect Effects 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 239000013589 supplement Substances 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- 238000012360 testing method Methods 0.000 description 2

- 238000004402 ultra-violet photoelectron spectroscopy Methods 0.000 description 2

- 229910001928 zirconium oxide Inorganic materials 0.000 description 2

- FIPWRIJSWJWJAI-UHFFFAOYSA-N Butyl carbitol 6-propylpiperonyl ether Chemical compound C1=C(CCC)C(COCCOCCOCCCC)=CC2=C1OCO2 FIPWRIJSWJWJAI-UHFFFAOYSA-N 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- 229910008813 Sn—Si Inorganic materials 0.000 description 1

- 229910010967 Ti—Sn Inorganic materials 0.000 description 1

- 229910001080 W alloy Inorganic materials 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- MDPILPRLPQYEEN-UHFFFAOYSA-N aluminium arsenide Chemical compound [As]#[Al] MDPILPRLPQYEEN-UHFFFAOYSA-N 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 1

- 230000000903 blocking effect Effects 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- ZMIGMASIKSOYAM-UHFFFAOYSA-N cerium Chemical compound [Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce][Ce] ZMIGMASIKSOYAM-UHFFFAOYSA-N 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000007865 diluting Methods 0.000 description 1

- 230000005685 electric field effect Effects 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 238000007654 immersion Methods 0.000 description 1

- 238000009616 inductively coupled plasma Methods 0.000 description 1

- 230000008595 infiltration Effects 0.000 description 1

- 238000001764 infiltration Methods 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- DNNSSWSSYDEUBZ-UHFFFAOYSA-N krypton atom Chemical compound [Kr] DNNSSWSSYDEUBZ-UHFFFAOYSA-N 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- MGRWKWACZDFZJT-UHFFFAOYSA-N molybdenum tungsten Chemical compound [Mo].[W] MGRWKWACZDFZJT-UHFFFAOYSA-N 0.000 description 1

- 239000002105 nanoparticle Substances 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 238000007645 offset printing Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 125000002524 organometallic group Chemical group 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 239000012466 permeate Substances 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 238000010248 power generation Methods 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 229910021332 silicide Inorganic materials 0.000 description 1

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 229910002076 stabilized zirconia Inorganic materials 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- 229910001233 yttria-stabilized zirconia Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1222—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer

- H01L27/1225—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or crystalline structure of the active layer with semiconductor materials not belonging to the group IV of the periodic table, e.g. InGaZnO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/24—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only semiconductor materials not provided for in groups H01L29/16, H01L29/18, H01L29/20, H01L29/22

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/417—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions carrying the current to be rectified, amplified or switched

- H01L29/41725—Source or drain electrodes for field effect devices

- H01L29/41733—Source or drain electrodes for field effect devices for thin film transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78645—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate

- H01L29/78648—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with multiple gate arranged on opposing sides of the channel

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78696—Thin film transistors, i.e. transistors with a channel being at least partly a thin film characterised by the structure of the channel, e.g. multichannel, transverse or longitudinal shape, length or width, doping structure, or the overlap or alignment between the channel and the gate, the source or the drain, or the contacting structure of the channel

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Ceramic Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Thin Film Transistor (AREA)

- Semiconductor Memories (AREA)

Description

<トランジスタの構成1>

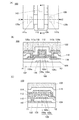

図1(A)は、本発明の一態様であるトランジスタの上面図である。また、図1(B)は、図1(A)にA3−A4の一点鎖線で示す部位の断面図である。つまりトランジスタのチャネル形成領域におけるチャネル幅方向の断面図を示す。図1(C)は、図1(A)にA1−A2の一点鎖線で示す部位の断面図である。つまりトランジスタのチャネル長方向の断面図を示す。図1(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

基板400としては、例えば、絶縁体基板、半導体基板または導電体基板を用いればよい。絶縁体基板としては、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板(イットリア安定化ジルコニア基板など)、樹脂基板などがある。また、半導体基板としては、例えば、シリコン、ゲルマニウムなどの単体半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムからなる化合物半導体基板などがある。さらには、前述の半導体基板内部に絶縁体領域を有する半導体基板、例えばSOI(Silicon On Insulator)基板などがある。導電体基板としては、黒鉛基板、金属基板、合金基板、導電性樹脂基板などがある。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。さらには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などがある。または、これらの基板に素子が設けられたものを用いてもよい。基板に設けられる素子としては、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などがある。

なお、トランジスタを、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体で囲うことによって、トランジスタの電気特性を安定にすることができる。例えば絶縁体401a、絶縁体401b、絶縁体408aおよび絶縁体408bとして、水素などの不純物および酸素の透過を抑制する機能を有する絶縁体を用いればよい。

導電体404、導電体310、導電体416a1、導電体416a2としては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タングステン、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニウム、ベリリウム、インジウムなどから選ばれた金属元素を1種以上含む材料を用いることができる。また、リン等の不純物元素を含有させた多結晶シリコンに代表される、電気伝導度が高い半導体、ニッケルシリサイドなどのシリサイドを用いてもよい。

図1に示すトランジスタと異なる構成のトランジスタを図2に示す。図2(A)は、本発明の一態様であるトランジスタの上面図である。また、図2(B)は、図2(A)にA3−A4の一点鎖線で示す部位の断面図である。つまりトランジスタのチャネル形成領域におけるチャネル幅方向の断面図を示す。図2(C)は、図2(A)にA1−A2の一点鎖線で示す部位の断面図である。つまりトランジスタのチャネル長方向の断面図を示す。図2(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

図1に示すトランジスタと異なる構成のトランジスタを図6に示す。図6(A)はトランジスタの上面図である。また、図6(B)は、図6(A)にA3−A4の一点鎖線で示す部位の断面図である。つまりトランジスタのチャネル形成領域におけるチャネル幅方向の断面図を示す。図6(C)は、図6(A)にA1−A2の一点鎖線で示す部位の断面図である。つまりトランジスタのチャネル長方向の断面図を示す。図6(A)の上面図では、図の明瞭化のために一部の要素を省いて図示している。

図17(A)は、本発明の一態様の半導体装置であるトランジスタ100の上面図であり、図17(B)は、図17(A)に示す一点鎖線X1−X2間における切断面の断面図に相当し、図17(C)は、図17(A)に示す一点鎖線Y1−Y2間における切断面の断面図に相当する。なお、図17(A)において、煩雑になることを避けるため、トランジスタ100の構成要素の一部(ゲート絶縁体として機能する絶縁体等)を省略して図示している。また、一点鎖線X1−X2方向をチャネル長方向、一点鎖線Y1−Y2方向をチャネル幅方向と呼称する場合がある。なお、トランジスタの上面図においては、以降の図面においても図17(A)と同様に、構成要素の一部を省略して図示する場合がある。

図18(A)は、トランジスタ500の上面図であり、図18(B)は、図18(A)に示す一点鎖線X1−X2間における切断面の断面図に相当し、図18(C)は、図18(A)に示す一点鎖線Y1−Y2間における切断面の断面図に相当する。

<トランジスタの作製方法>

以下では、本発明に係る図1に示すトランジスタの作製方法を図1および図7乃至図10を用いて説明する。図1および図7乃至図10において、各図の(A)は上面図であり、各図の(B)は、(A)に示す一点鎖線A3−A4に対応する断面図である。各図の(C)は、(A)に示す一点鎖線A1−A2に対応する断面図である。

本実施の形態では、半導体装置の一形態を、図19および図20を用いて説明する。

本発明の一態様である半導体装置を使用した、記憶装置の一例を図19および図20に示す。

図19、および図20に示す記憶装置は、トランジスタ800のゲートの電位が保持可能という特性を有することで、以下に示すように、情報の書き込み、保持、読み出しが可能である。

図19、および図20に示す記憶装置は、トランジスタ800を有さない構成としてもよい。トランジスタ800を有さない場合も、先に述べた記憶装置と同様の動作により情報の書き込みおよび保持動作が可能である。

本発明の一態様の記憶装置の一例を、図19に示す。記憶装置は、トランジスタ900、トランジスタ800、トランジスタ700、容量素子600を有する。トランジスタ700はトランジスタ800の上方に設けられ、容量素子600はトランジスタ800、およびトランジスタ700の上方に設けられている。

記憶装置の変形例の一例を、図20に示す。図20は、図19と、トランジスタ800の構成が異なる。

12 スパッタリングターゲット

50a バッキングプレート

50c バッキングプレート

66 シャッタ

67 部

100 トランジスタ

100a 部分

100b 部分

102 基板

104 絶縁体

106 導電体

108 酸化物

108a 酸化物

108b 酸化物

108c 酸化物

108n 領域

110 絶縁体

112 導電体

116 絶縁体

118 絶縁体

120a 導電体

120b 導電体

141a 開口部

141b 開口部

143 開口部

301 絶縁体

302 絶縁体

303 絶縁体

310 導電体

310a 導電体

310b 導電体

310c 導電体

400 基板

401a 絶縁体

401b 絶縁体

402 絶縁体

404 導電体

404a 導電体

406a 酸化物

406a1 酸化物

406b 酸化物

406b1 酸化物

406b1n 酸化物

406b1w 酸化物

406bn 酸化物

406bn_n 酸化物

406bn_1 酸化物

406bn_2 酸化物

406bw 酸化物

406bw_n 酸化物

406bw_1 酸化物

406bw_2 酸化物

406c 酸化物

406d 酸化物

408a 絶縁体

408b 絶縁体

410 絶縁体

412 絶縁体

412a 絶縁体

416a1 導電体

416a2 導電体

417a1 バリア膜

417a2 バリア膜

500 トランジスタ

502 基板

504 導電体

506 絶縁体

507 絶縁体

508 酸化物

508a 酸化物

508b 酸化物

508c 酸化物

508n 領域

512a 導電体

512b 導電体

514 絶縁体

516 絶縁体

518 絶縁体

520a 導電体

520b 導電体

542a 開口部

542b 開口部

542c 開口部

600 容量素子

610 絶縁体

612 導電体

616 導電体

630 絶縁体

632 絶縁体

634 絶縁体

650 絶縁体

700 トランジスタ

710 絶縁体

712 絶縁体

714 絶縁体

716 絶縁体

718 導電体

720 絶縁体

722 絶縁体

724 絶縁体

772 絶縁体

774 絶縁体

780 絶縁体

782 絶縁体

784 絶縁体

785 導電体

787 導電体

800 トランジスタ

811 基板

812 半導体領域

814 絶縁体

816 導電体

818a 低抵抗領域

818b 低抵抗領域

820 絶縁体

822 絶縁体

824 絶縁体

826 絶縁体

828 導電体

830 導電体

850 絶縁体

852 絶縁体

854 絶縁体

856 導電体

858 絶縁体

900 トランジスタ

3001 配線

3002 配線

3003 配線

3004 配線

3005 配線

3006 配線

3007 配線

3008 配線

3009 配線

3010 配線

Claims (15)

- ゲート電極と、ソース電極と、ドレイン電極と、ゲート絶縁体と、金属酸化物を有し、

前記ゲート絶縁体は、前記ゲート電極と前記金属酸化物との間に位置し、

前記ゲート電極は、前記ゲート絶縁体を介して、前記金属酸化物と重なる領域を有し、

前記ソース電極および前記ドレイン電極は、前記金属酸化物の上面と接する領域を有し、

前記金属酸化物は、第1の酸化物層と、前記第1の酸化物層に接する第2の酸化物層と、を有し、

前記第1の酸化物層は、第1のバンドギャップを有し、

前記第2の酸化物層は、前記第1のバンドギャップよりも大きい第2のバンドギャップを有し、

前記第1の酸化物層は、インジウムおよび亜鉛の一方または双方を有し、

前記第2の酸化物層は、インジウム、亜鉛、および元素M(元素Mは、アルミニウム、ガリウム、シリコン、ホウ素、イットリウム、銅、バナジウム、ベリリウム、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムから選ばれた一、または複数)を有し、

前記金属酸化物は、0.5nm以上3nm以下のサイズの第1の領域と、0.5nm以上3nm以下のサイズの第2の領域とを有し、

前記第1の領域は、キャリアとなる電子又はホールを流す機能を有し、前記第2の領域は、前記キャリアを流さない機能を有し、

前記ゲート電極の電圧を0Vに保持した状態において、前記第2の酸化物層の伝導帯下端とフェルミレベルとの差は、前記第1の酸化物層の伝導帯下端とフェルミレベルとの差より大きいトランジスタ。 - ゲート電極と、ソース電極と、ドレイン電極と、ゲート絶縁体と、金属酸化物を有し、

前記ゲート絶縁体は、前記ゲート電極と前記金属酸化物との間に位置し、

前記ゲート電極は、前記ゲート絶縁体を介して、前記金属酸化物と重なる領域を有し、

前記ソース電極および前記ドレイン電極は、前記金属酸化物の上面と接する領域を有し、

前記金属酸化物は、第1の酸化物層と、前記第1の酸化物層に接する第2の酸化物層と、有し、

前記第1の酸化物層は、第1のバンドギャップを有し、

前記第2の酸化物層は、前記第1のバンドギャップよりも大きい第2のバンドギャップを有し、

前記金属酸化物は、前記第1の酸化物層を2層以上有し、

前記第1の酸化物層は、インジウムおよび亜鉛の一方または双方を有し、

前記第2の酸化物層は、インジウム、亜鉛、および元素M(元素Mは、アルミニウム、ガリウム、シリコン、ホウ素、イットリウム、銅、バナジウム、ベリリウム、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムから選ばれた一、または複数)を有し、

前記金属酸化物は、0.5nm以上3nm以下のサイズの第1の領域と、0.5nm以上3nm以下のサイズの第2の領域とを有し、

前記第1の領域は、キャリアとなる電子又はホールを流す機能を有し、前記第2の領域は、前記キャリアを流さない機能を有し、

前記ゲート電極の電圧を0Vに保持した状態において、前記第2の酸化物層の伝導帯下端とフェルミレベルとの差は、前記第1の酸化物層の伝導帯下端とフェルミレベルとの差より大きいトランジスタ。 - ゲート電極と、ソース電極と、ドレイン電極と、ゲート絶縁体と、金属酸化物を有し、

前記ゲート絶縁体は、前記ゲート電極と前記金属酸化物との間に位置し、

前記ゲート電極は、前記ゲート絶縁体を介して、前記金属酸化物と重なる領域を有し、

前記ソース電極および前記ドレイン電極は、前記金属酸化物の上面と接する領域を有し、

前記金属酸化物は、第1の酸化物層と、前記第1の酸化物層に接する第2の酸化物層と、有し、

前記第1の酸化物層は、第1のバンドギャップを有し、

前記第2の酸化物層は、前記第1のバンドギャップよりも大きい第2のバンドギャップを有し、

前記金属酸化物は、前記第1の酸化物層を2層以上有し、

前記第1の酸化物層は、インジウムおよび亜鉛の一方または双方を有し、

前記第2の酸化物層は、インジウム、亜鉛、および元素M(元素Mは、アルミニウム、ガリウム、シリコン、ホウ素、イットリウム、銅、バナジウム、ベリリウム、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムから選ばれた一、または複数)を有し、

前記金属酸化物は、0.5nm以上3nm以下のサイズの第1の領域と、0.5nm以上3nm以下のサイズの第2の領域とを有し、

前記第1の領域は、キャリアとなる電子又はホールを流す機能を有し、前記第2の領域は、前記キャリアを流さない機能を有し、

前記ゲート電極に正の電圧が印加された状態において、前記第2の酸化物層の伝導帯下端は、前記第1の酸化物層の伝導帯下端よりエネルギーが低く、

前記ゲート電極に負の電圧が印加された状態において、前記第2の酸化物層の伝導帯下端は、前記第1の酸化物層の伝導帯下端よりエネルギーが高いトランジスタ。 - 請求項2または請求項3において、

前記金属酸化物は、前記第1の酸化物層を、3層以上10層以下を有するトランジスタ。 - ゲート電極と、ソース電極と、ドレイン電極と、ゲート絶縁体と、第1の金属酸化物と、第2の金属酸化物と、第3の金属酸化物を有し、

前記ゲート絶縁体は、前記ゲート電極と前記第1の金属酸化物との間に位置し、

前記ゲート電極は、前記ゲート絶縁体および前記第1の金属酸化物を介して、前記第2の金属酸化物と重なる領域を有し、

前記ソース電極および前記ドレイン電極は、前記第2の金属酸化物の上面と接する領域を有し、

前記第3の金属酸化物は、前記第2の金属酸化物の上面と接する領域を有し、

前記第2の金属酸化物は、第1の酸化物層と、前記第1の酸化物層に接する第2の酸化物層と、有し、

前記第1の酸化物層は、第1のバンドギャップを有し、

前記第2の酸化物層は、前記第1のバンドギャップよりも大きい第2のバンドギャップを有し、

前記第1の酸化物層は、インジウムおよび亜鉛の一方または双方を有し、

前記第2の酸化物層は、インジウム、亜鉛、および元素M(元素Mは、アルミニウム、ガリウム、シリコン、ホウ素、イットリウム、銅、バナジウム、ベリリウム、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムから選ばれた一、または複数)を有し、

前記第2の金属酸化物は、0.5nm以上3nm以下のサイズの第1の領域と、0.5nm以上3nm以下のサイズの第2の領域とを有し、

前記第1の領域は、キャリアとなる電子又はホールを流す機能を有し、前記第2の領域は、前記キャリアを流さない機能を有し、

前記ゲート電極の電圧を0Vに保持した状態において、前記第2の酸化物層の伝導帯下端とフェルミレベルとの差は、前記第1の酸化物層の伝導帯下端とフェルミレベルとの差より大きいトランジスタ。 - ゲート電極と、ソース電極と、ドレイン電極と、ゲート絶縁体と、第1の金属酸化物と、第2の金属酸化物と、第3の金属酸化物を有し、

前記ゲート絶縁体は、前記ゲート電極と前記第1の金属酸化物との間に位置し、

前記ゲート電極は、前記ゲート絶縁体および前記第1の金属酸化物を介して、前記第2の金属酸化物と重なる領域を有し、

前記ソース電極および前記ドレイン電極は、前記第2の金属酸化物の上面と接する領域を有し、

前記第3の金属酸化物は、前記第2の金属酸化物の上面と接する領域を有し、

前記第2の金属酸化物は、第1の酸化物層と、前記第1の酸化物層に接する第2の酸化物層と、有し、

前記第1の酸化物層は、第1のバンドギャップを有し、

前記第2の酸化物層は、前記第1のバンドギャップよりも大きい第2のバンドギャップを有し、

前記第2の金属酸化物は、前記第1の酸化物層を、2層以上を有し、

前記第1の酸化物層は、インジウムおよび亜鉛の一方または双方を有し、

前記第2のバンドギャップを有する酸化物層は、インジウム、亜鉛、および元素M(元素Mは、アルミニウム、ガリウム、シリコン、ホウ素、イットリウム、銅、バナジウム、ベリリウム、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムから選ばれた一、または複数)を有し、

前記第2の金属酸化物は、0.5nm以上3nm以下のサイズの第1の領域と、0.5nm以上3nm以下のサイズの第2の領域とを有し、

前記第1の領域は、キャリアとなる電子又はホールを流す機能を有し、前記第2の領域は、前記キャリアを流さない機能を有し、

前記ゲート電極の電圧を0Vに保持した状態において、前記第2の酸化物層の伝導帯下端とフェルミレベルとの差は、前記第1の酸化物層の伝導帯下端とフェルミレベルとの差より大きいトランジスタ。 - ゲート電極と、ソース電極と、ドレイン電極と、ゲート絶縁体と、第1の金属酸化物と、第2の金属酸化物と、第3の金属酸化物を有し、

前記ゲート絶縁体は、前記ゲート電極と前記第1の金属酸化物との間に位置し、

前記ゲート電極は、前記ゲート絶縁体および前記第1の金属酸化物を介して、前記第2の金属酸化物と重なる領域を有し、

前記ソース電極および前記ドレイン電極は、前記第2の金属酸化物の上面と接する領域を有し、

前記第3の金属酸化物は、前記第2の金属酸化物の上面と接する領域を有し、

前記第2の金属酸化物は、第1の酸化物層と、前記第1の酸化物層に接する第2の酸化物層と、有し、

前記第1の酸化物層は、第1のバンドギャップを有し、

前記第2の酸化物層は、前記第1のバンドギャップよりも大きい第2のバンドギャップを有し、

前記第2の金属酸化物は、前記第1の酸化物層を2層以上有し、

前記第1の酸化物層は、インジウムおよび亜鉛の一方または双方を有し、

前記第2の酸化物層は、インジウム、亜鉛、および元素M(元素Mは、アルミニウム、ガリウム、シリコン、ホウ素、イットリウム、銅、バナジウム、ベリリウム、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムから選ばれた一、または複数)を有し、

前記第2の金属酸化物は、0.5nm以上3nm以下のサイズの第1の領域と、0.5nm以上3nm以下のサイズの第2の領域とを有し、

前記第1の領域は、キャリアとなる電子又はホールを流す機能を有し、前記第2の領域は、前記キャリアを流さない機能を有し、

前記第1の金属酸化物は、前記第1の酸化物層よりバンドギャップが大きいトランジスタ。 - 請求項6または請求項7において、

前記第2の金属酸化物は、前記第1の酸化物層を、3層以上10層以下を有するトランジスタ。 - 請求項5乃至請求項8のいずれか一において、

前記第2の金属酸化物は、チャネル形成領域を有し、

前記チャネル形成領域のチャネル幅方向において、前記第3の金属酸化物は、前記第2の金属酸化物を覆う様に配されるトランジスタ。 - 請求項5乃至請求項9のいずれか一において、

前記第1の金属酸化物のバンドギャップおよび前記第3の金属酸化物のバンドギャップは、前記第2の金属酸化物のバンドギャップより大きいトランジスタ。 - 請求項1乃至請求項10のいずれか一において、

前記第1の酸化物層は、膜厚が0.5nm以上10nm以下の領域を有するトランジスタ。 - 請求項1乃至請求項11のいずれか一において、

前記第1の酸化物層は、膜厚が0.5nm以上2.0nm以下の領域を有するトランジスタ。 - 請求項1乃至請求項12のいずれか一において、

前記第2の酸化物層は、膜厚が0.1nm以上10nm以下の領域を有するトランジスタ。 - 請求項1乃至請求項13のいずれか一において、

前記第2の酸化物層は、膜厚が0.1nm以上3.0nm以下の領域を有するトランジスタ。 - 請求項1乃至請求項14のいずれか一において、

前記第1の酸化物層のキャリア密度は、6×1018cm−3以上5×1020cm−3以下であるトランジスタ。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016127106 | 2016-06-27 | ||

| JP2016127106 | 2016-06-27 | ||

| JP2016140981 | 2016-07-18 | ||

| JP2016140981 | 2016-07-18 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020192553A Division JP2021036615A (ja) | 2016-06-27 | 2020-11-19 | トランジスタ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2018019074A JP2018019074A (ja) | 2018-02-01 |

| JP2018019074A5 JP2018019074A5 (ja) | 2019-06-20 |

| JP6798942B2 true JP6798942B2 (ja) | 2020-12-09 |

Family

ID=60677919

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017124719A Expired - Fee Related JP6798942B2 (ja) | 2016-06-27 | 2017-06-27 | トランジスタおよび半導体装置 |

| JP2020192553A Withdrawn JP2021036615A (ja) | 2016-06-27 | 2020-11-19 | トランジスタ |

| JP2022137406A Withdrawn JP2022169759A (ja) | 2016-06-27 | 2022-08-31 | トランジスタ及び半導体装置 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020192553A Withdrawn JP2021036615A (ja) | 2016-06-27 | 2020-11-19 | トランジスタ |

| JP2022137406A Withdrawn JP2022169759A (ja) | 2016-06-27 | 2022-08-31 | トランジスタ及び半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20170373195A1 (ja) |

| JP (3) | JP6798942B2 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102583770B1 (ko) * | 2016-09-12 | 2023-10-06 | 삼성디스플레이 주식회사 | 메모리 트랜지스터 및 이를 갖는 표시장치 |

| WO2019145807A1 (ja) * | 2018-01-25 | 2019-08-01 | 株式会社半導体エネルギー研究所 | 半導体装置、および半導体装置の作製方法 |

| WO2019175698A1 (ja) | 2018-03-12 | 2019-09-19 | 株式会社半導体エネルギー研究所 | 金属酸化物、及び金属酸化物を有するトランジスタ |

| CN108878512B (zh) * | 2018-06-29 | 2020-08-25 | 云南大学 | 一种金属氧化物叠层场效应材料及其应用 |

| JP2020009960A (ja) * | 2018-07-11 | 2020-01-16 | 株式会社半導体エネルギー研究所 | 半導体装置、および半導体装置の作製方法 |

| US11031506B2 (en) * | 2018-08-31 | 2021-06-08 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device including transistor using oxide semiconductor |

| WO2020059026A1 (ja) * | 2018-09-18 | 2020-03-26 | シャープ株式会社 | 表示装置、および表示装置の製造方法 |

| US11211461B2 (en) * | 2018-12-28 | 2021-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and memory device |

| CN118696615A (zh) * | 2022-02-25 | 2024-09-24 | 株式会社半导体能源研究所 | 存储装置 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7982216B2 (en) * | 2007-11-15 | 2011-07-19 | Fujifilm Corporation | Thin film field effect transistor with amorphous oxide active layer and display using the same |

| JP5382763B2 (ja) * | 2008-04-09 | 2014-01-08 | 独立行政法人産業技術総合研究所 | 半導体素子及びその製造方法と、該半導体素子を備えた電子デバイス |

| JP2010165922A (ja) * | 2009-01-16 | 2010-07-29 | Idemitsu Kosan Co Ltd | 電界効果型トランジスタ、電界効果型トランジスタの製造方法及び半導体素子の製造方法 |

| KR102450889B1 (ko) * | 2009-12-04 | 2022-10-06 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| JP5497417B2 (ja) * | 2009-12-10 | 2014-05-21 | 富士フイルム株式会社 | 薄膜トランジスタおよびその製造方法、並びにその薄膜トランジスタを備えた装置 |

| WO2011070928A1 (en) * | 2009-12-11 | 2011-06-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| KR101778224B1 (ko) * | 2010-10-12 | 2017-09-15 | 삼성전자주식회사 | 트랜지스터와 그 제조방법 및 트랜지스터를 포함하는 전자소자 |

| KR101457833B1 (ko) * | 2010-12-03 | 2014-11-05 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| US8878174B2 (en) * | 2011-04-15 | 2014-11-04 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor element, memory circuit, integrated circuit, and driving method of the integrated circuit |

| US8952377B2 (en) * | 2011-07-08 | 2015-02-10 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US9059219B2 (en) * | 2012-06-27 | 2015-06-16 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

| KR102171650B1 (ko) * | 2012-08-10 | 2020-10-29 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| US9614258B2 (en) * | 2012-12-28 | 2017-04-04 | Semiconductor Energy Laboratory Co., Ltd. | Power storage device and power storage system |

| JP6199581B2 (ja) * | 2013-03-08 | 2017-09-20 | 株式会社半導体エネルギー研究所 | 金属酸化物膜、及び半導体装置 |

| JP2016058708A (ja) * | 2014-09-11 | 2016-04-21 | 株式会社半導体エネルギー研究所 | 半導体装置、及び半導体装置の評価方法 |

| WO2016055894A1 (en) * | 2014-10-06 | 2016-04-14 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and electronic device |

-

2017

- 2017-06-19 US US15/626,565 patent/US20170373195A1/en not_active Abandoned

- 2017-06-27 JP JP2017124719A patent/JP6798942B2/ja not_active Expired - Fee Related

-

2020

- 2020-11-19 JP JP2020192553A patent/JP2021036615A/ja not_active Withdrawn

-

2022

- 2022-08-31 JP JP2022137406A patent/JP2022169759A/ja not_active Withdrawn

Also Published As

| Publication number | Publication date |

|---|---|

| JP2021036615A (ja) | 2021-03-04 |

| US20170373195A1 (en) | 2017-12-28 |

| JP2022169759A (ja) | 2022-11-09 |

| JP2018019074A (ja) | 2018-02-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6798942B2 (ja) | トランジスタおよび半導体装置 | |

| JP7052110B2 (ja) | 表示装置 | |

| JP7025488B2 (ja) | トランジスタ | |

| CN105849875B (zh) | 半导体装置及其制造方法 | |

| US10964787B2 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| US10504925B2 (en) | Semiconductor device and method for manufacturing semiconductor device | |

| JP2015128153A (ja) | 半導体装置及びその作製方法 | |

| US10475931B2 (en) | Semiconductor device and manufacturing method thereof | |

| US10615187B2 (en) | Transistor, semiconductor device, and electronic device | |

| US12119353B2 (en) | Semiconductor device, electronic component, and electronic device | |

| JP6873840B2 (ja) | トランジスタ | |

| WO2018002757A1 (ja) | トランジスタ | |

| WO2018002764A1 (ja) | スパッタリング装置を用いた金属酸化物の作製方法 | |

| WO2017216682A1 (ja) | スパッタリング装置およびトランジスタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190517 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190517 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20200326 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200331 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200601 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20201020 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20201119 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6798942 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |