JP6764234B2 - 固体撮像装置及びカメラ - Google Patents

固体撮像装置及びカメラ Download PDFInfo

- Publication number

- JP6764234B2 JP6764234B2 JP2016032425A JP2016032425A JP6764234B2 JP 6764234 B2 JP6764234 B2 JP 6764234B2 JP 2016032425 A JP2016032425 A JP 2016032425A JP 2016032425 A JP2016032425 A JP 2016032425A JP 6764234 B2 JP6764234 B2 JP 6764234B2

- Authority

- JP

- Japan

- Prior art keywords

- impurity region

- impurity

- solid

- region

- conductive type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Solid State Image Pick-Up Elements (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

Description

図2(a)〜(d)は、第1実施形態に係る画素PXの構造の例を示している。ここでは、理解を容易にするため、X方向(第1方向)で互いに隣り合う2つの画素PX(それぞれ、「画素PX1」、「画素PX2」とする。)を用いて述べる。

上述のとおり、本実施形態では、電荷蓄積領域(不純物領域R1及びR2)は埋め込み型で構成されてもよい。以下、埋め込み型の構成を採用した場合について説明する。

図8(a)及び(b)を参照しながら第2実施形態を述べる。図8(a)は、平面視においてX方向で互いに隣り合う2つの画素PX(それぞれ「画素PX3」、「画素PX4」とする。)のレイアウト図を示している。図8(b)は、図8(a)のカットラインD1−D2での断面構造を示している。

図10(a1)〜(a4)及び(b1)〜(b4)は、第3実施形態に係る固体撮像装置の製造方法のうち、不純物領域R5を形成する工程の一例を示している。図10(a1)〜(a4)のそれぞれは、各工程における単位画素PXのレイアウト図を示している。図10(b1)〜(b4)は、図10(a1)〜(a4)のカットラインE1−E2での断面構造をそれぞれ示している。

以上、いくつかの好適な実施形態を例示したが、本発明はこれらに限られるものではなく、本発明の趣旨を逸脱しない範囲で、その一部が変更されてもよいし、各実施形態の各特徴が組み合わされてもよい。

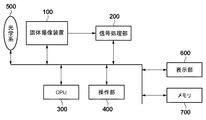

図11は、以上の各実施形態で例示された画素PXを備える固体撮像装置100が適用されたカメラの構成例を説明するための図である。カメラは、固体撮像装置100の他、例えば、処理部200、CPU300(又はプロセッサ)、操作部400、光学系500を具備する。また、カメラは、静止画や動画をユーザに表示するための表示部600、それらのデータを記憶するためのメモリ700をさらに具備しうる。固体撮像装置100は、光学系500を通過した光に基づいて画像データを生成する。該画像データは、処理部200により所定の補正処理が為され、表示部600やメモリ700に出力される。また、ユーザにより操作部400を介して入力された撮影条件に応じて、CPU300によって、各ユニットの設定情報が変更され、又は、各ユニットの制御方法が変更されうる。なお、カメラの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置(例えば、パーソナルコンピュータ、携帯端末)も含まれる。

Claims (12)

- 半導体基板上に配された複数の画素を備える固体撮像装置であって、

各画素は、前記半導体基板の上面に対する平面視において、

光電変換により生じた電荷を蓄積するための第1導電型の第1不純物領域と、

前記第1不純物領域から第1方向にずれた位置に形成され、光電変換により生じた電荷を蓄積するための前記第1導電型の第2不純物領域と、

前記第1不純物領域と前記第2不純物領域との間に形成された第2導電型の第3不純物領域と、

前記第3不純物領域から前記第1方向と交差する第2方向にずれた位置に形成された前記第1導電型の第4不純物領域と、

前記第1不純物領域と前記第4不純物領域との間に配され、前記第1不純物領域から前記第4不純物領域に電荷を転送するためのトランジスタの第1ゲート電極と、

前記第2不純物領域と前記第4不純物領域との間に配され、前記第2不純物領域から前記第4不純物領域に電荷を転送するためのトランジスタの第2ゲート電極と、

前記第1ゲート電極と前記第2ゲート電極との間かつ前記第3不純物領域と前記第4不純物領域との間に形成された前記第2導電型の第5不純物領域と、

を含み、

前記第5不純物領域の前記第2導電型の不純物の濃度は、前記第3不純物領域の前記第2導電型の不純物の濃度よりも高く、

平面視で、前記第5不純物領域の一部は、前記第1不純物領域の前記第4不純物領域側の端および前記第2不純物領域の前記第4不純物領域側の端よりも前記第4不純物領域側に位置している

ことを特徴とする固体撮像装置。 - 前記第4不純物領域は、前記第2方向において、前記第1不純物領域および前記第2不純物領域の双方と重なるように形成されている

ことを特徴とする請求項1に記載の固体撮像装置。 - 各画素は、前記平面視において、前記第1不純物領域の前記第2不純物領域に対して反対側に形成された第1部分と前記第2不純物領域の前記第1不純物領域に対して反対側に形成された第2部分とを含む第6不純物領域をさらに含み、

前記第3不純物領域の前記第2導電型の不純物の濃度は、前記第6不純物領域の前記第2導電型の不純物の濃度よりも低い

ことを特徴とする請求項1または請求項2に記載の固体撮像装置。 - 各画素は、前記平面視において、

前記第1不純物領域、前記第2不純物領域および前記第3不純物領域のそれぞれの前記第4不純物領域に対して反対側に形成された絶縁性の素子分離部と、

前記素子分離部と、前記第1不純物領域、前記第2不純物領域および前記第3不純物領域のそれぞれとの間に形成された前記第2導電型の第7不純物領域と、

をさらに含む

ことを特徴とする請求項1から請求項3のいずれか1項に記載の固体撮像装置。 - 前記半導体基板の表面からの深さ方向における前記第5不純物領域の不純物濃度プロファイルと、前記深さ方向における前記第7不純物領域の不純物濃度プロファイルとは、互いに等しい

ことを特徴とする請求項4に記載の固体撮像装置。 - 前記第5不純物領域は、その底面が、前記第4不純物領域の底面よりも深く且つ前記第1不純物領域および前記第2不純物領域の双方の底面よりも浅くなるように形成されている

ことを特徴とする請求項1から請求項5のいずれか1項に記載の固体撮像装置。 - 前記半導体基板の表面からの深さ方向において、前記第5不純物領域の不純物濃度のピーク位置は、前記第1不純物領域の不純物濃度のピーク位置および前記第2不純物領域の不純物濃度のピーク位置の少なくとも一方と、前記第4不純物領域の不純物濃度のピーク位置との間に位置している

ことを特徴とする請求項6に記載の固体撮像装置。 - 前記第5不純物領域は、その底面が、前記第1不純物領域および前記第2不純物領域の双方の底面と同じ深さ又はそれよりも深くなるように形成されている

ことを特徴とする請求項1から請求項5のいずれか1項に記載の固体撮像装置。 - 前記第5不純物領域は、前記半導体基板の表面からの深さ方向において、少なくとも前記第4不純物領域と同じ深さには設けられている

ことを特徴とする請求項1から請求項5のいずれか1項に記載の固体撮像装置。 - 前記第1不純物領域、前記第2不純物領域および前記第3不純物領域と、前記半導体基板の表面との間には、前記第2導電型の第8不純物領域が設けられており、

前記第8不純物領域の前記第2導電型の不純物の濃度は、前記第5不純物領域の前記第2導電型の不純物の濃度よりも高い

ことを特徴とする請求項1から請求項9のいずれか1項に記載の固体撮像装置。 - 半導体基板上に配された複数の画素を備える固体撮像装置であって、

各画素は、前記半導体基板の上面に対する平面視において、

光電変換により生じた電荷を蓄積するための第1導電型の第1不純物領域と、

前記第1不純物領域から第1方向にずれた位置に形成され、光電変換により生じた電荷を蓄積するための前記第1導電型の第2不純物領域と、

前記第1不純物領域と前記第2不純物領域との間に形成された第2導電型の第3不純物領域と、

前記第3不純物領域から前記第1方向と交差する第2方向にずれた位置に形成された前記第1導電型の第4不純物領域と、

前記第1不純物領域と前記第4不純物領域との間に配され、前記第1不純物領域から前記第4不純物領域に電荷を転送するためのトランジスタの第1ゲート電極と、

前記第2不純物領域と前記第4不純物領域との間に配され、前記第2不純物領域から前記第4不純物領域に電荷を転送するためのトランジスタの第2ゲート電極と、

前記第1ゲート電極と前記第2ゲート電極との間かつ前記第3不純物領域と前記第4不純物領域との間に形成された前記第2導電型の第5不純物領域と、

を含み、

前記第1不純物領域および前記第2不純物領域の双方に蓄積された電荷に対する前記第5不純物領域のポテンシャル障壁は、該電荷に対する前記第3不純物領域のポテンシャル障壁よりも高く、

平面視で、前記第5不純物領域の一部は、前記第1不純物領域の前記第4不純物領域側の端および前記第2不純物領域の前記第4不純物領域側の端よりも前記第4不純物領域側に位置している

ことを特徴とする固体撮像装置。 - 請求項1から請求項11のいずれか1項に記載の固体撮像装置と、

前記固体撮像装置から出力される信号を処理する処理部と、を備える

ことを特徴とするカメラ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US15/163,986 US9768213B2 (en) | 2015-06-03 | 2016-05-25 | Solid-state image sensor and camera |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015113350 | 2015-06-03 | ||

| JP2015113350 | 2015-06-03 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016225597A JP2016225597A (ja) | 2016-12-28 |

| JP2016225597A5 JP2016225597A5 (ja) | 2019-03-28 |

| JP6764234B2 true JP6764234B2 (ja) | 2020-09-30 |

Family

ID=57748582

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016032425A Active JP6764234B2 (ja) | 2015-06-03 | 2016-02-23 | 固体撮像装置及びカメラ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6764234B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6776079B2 (ja) * | 2016-09-27 | 2020-10-28 | 東芝情報システム株式会社 | 固体撮像素子及びその製造方法 |

| JP2021068788A (ja) | 2019-10-21 | 2021-04-30 | キヤノン株式会社 | 光電変換装置、光電変換装置の製造方法、および撮像システム |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4282049B2 (ja) * | 2002-02-28 | 2009-06-17 | キヤノン株式会社 | 半導体装置、光電変換装置及びカメラ |

| JP2003324191A (ja) * | 2002-05-02 | 2003-11-14 | Canon Inc | 光電変換装置及び撮像装置 |

| JP3840203B2 (ja) * | 2002-06-27 | 2006-11-01 | キヤノン株式会社 | 固体撮像装置及び固体撮像装置を用いたカメラシステム |

| JP2010118538A (ja) * | 2008-11-13 | 2010-05-27 | Toshiba Corp | 固体撮像装置 |

| JP5743837B2 (ja) * | 2011-10-07 | 2015-07-01 | キヤノン株式会社 | 光電変換装置、撮像装置および撮像システム |

| JP5967944B2 (ja) * | 2012-01-18 | 2016-08-10 | キヤノン株式会社 | 固体撮像装置およびカメラ |

| JP5936364B2 (ja) * | 2012-01-18 | 2016-06-22 | キヤノン株式会社 | 撮像装置、及び撮像装置を含む撮像システム |

| JP6164951B2 (ja) * | 2013-06-28 | 2017-07-19 | キヤノン株式会社 | 光電変換装置の製造方法、光電変換装置、及び撮像システム |

| JP6175970B2 (ja) * | 2013-08-12 | 2017-08-09 | 株式会社ニコン | 固体撮像素子および撮像装置 |

-

2016

- 2016-02-23 JP JP2016032425A patent/JP6764234B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016225597A (ja) | 2016-12-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9768213B2 (en) | Solid-state image sensor and camera | |

| JP7013119B2 (ja) | 固体撮像素子、固体撮像素子の製造方法、及び撮像システム | |

| US9124833B2 (en) | Solid-state imaging apparatus | |

| JP5864990B2 (ja) | 固体撮像装置およびカメラ | |

| US8648944B2 (en) | Solid-state image sensor and camera having impurity diffusion region | |

| JP5539104B2 (ja) | 光電変換装置およびそれを用いた撮像システム | |

| US7709869B2 (en) | Photoelectric conversion device, method of manufacturing the same, and image sensing system | |

| US20170324916A1 (en) | Optical sensor, signal reading method therefor, solid-state imaging device, and signal reading method therefor | |

| JP6406585B2 (ja) | 撮像装置 | |

| US8053272B2 (en) | Semiconductor device fabrication method | |

| KR20140099848A (ko) | 고체촬상장치 및 그 제조 방법 | |

| JP2010161236A (ja) | 光電変換装置の製造方法 | |

| JP6254048B2 (ja) | 半導体装置 | |

| US20200091212A1 (en) | Image sensor having p-type isolation structure | |

| JP2017195215A (ja) | 撮像素子及びその製造方法 | |

| JP2004342836A (ja) | 固体撮像素子及び固体撮像素子の製造方法 | |

| JP6764234B2 (ja) | 固体撮像装置及びカメラ | |

| US9640570B2 (en) | Method of manufacturing solid-state image sensor | |

| US20190297282A1 (en) | Solid-state image sensor | |

| JP5644433B2 (ja) | 固体撮像素子、および、固体撮像素子の製造方法 | |

| JP2017220603A (ja) | 固体撮像素子および固体撮像素子の製造方法 | |

| JP6029698B2 (ja) | 光電変換装置及びそれを用いた撮像システム | |

| JP7316046B2 (ja) | 光電変換装置およびカメラ | |

| JP6420450B2 (ja) | 半導体装置 | |

| JP2006351729A (ja) | 接合形電界効果トランジスタ及びその製造方法並びに固体撮像装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190213 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190213 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20191122 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200106 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200305 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200814 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200911 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6764234 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |