JP6487195B2 - 半導体光集積素子、半導体光集積素子の製造方法及び光モジュール - Google Patents

半導体光集積素子、半導体光集積素子の製造方法及び光モジュール Download PDFInfo

- Publication number

- JP6487195B2 JP6487195B2 JP2014248981A JP2014248981A JP6487195B2 JP 6487195 B2 JP6487195 B2 JP 6487195B2 JP 2014248981 A JP2014248981 A JP 2014248981A JP 2014248981 A JP2014248981 A JP 2014248981A JP 6487195 B2 JP6487195 B2 JP 6487195B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- semiconductor optical

- semiconductor

- integrated device

- optical integrated

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000003287 optical effect Effects 0.000 title claims description 220

- 239000004065 semiconductor Substances 0.000 title claims description 189

- 238000004519 manufacturing process Methods 0.000 title claims description 36

- 238000005530 etching Methods 0.000 claims description 88

- 239000000758 substrate Substances 0.000 claims description 60

- 238000005253 cladding Methods 0.000 claims description 38

- 238000000034 method Methods 0.000 claims description 38

- 125000006850 spacer group Chemical group 0.000 claims description 16

- 239000000463 material Substances 0.000 claims description 14

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 claims description 10

- 229910052698 phosphorus Inorganic materials 0.000 claims description 10

- 239000011574 phosphorus Substances 0.000 claims description 10

- 230000008569 process Effects 0.000 claims description 9

- 229910052782 aluminium Inorganic materials 0.000 claims description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 4

- 239000010410 layer Substances 0.000 description 417

- 230000010355 oscillation Effects 0.000 description 23

- 229910004298 SiO 2 Inorganic materials 0.000 description 18

- 230000010354 integration Effects 0.000 description 14

- 229910000530 Gallium indium arsenide Inorganic materials 0.000 description 13

- 230000005540 biological transmission Effects 0.000 description 11

- 238000000059 patterning Methods 0.000 description 11

- 239000012071 phase Substances 0.000 description 8

- 230000000052 comparative effect Effects 0.000 description 7

- 239000000243 solution Substances 0.000 description 7

- 238000003776 cleavage reaction Methods 0.000 description 6

- 230000006866 deterioration Effects 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 230000001681 protective effect Effects 0.000 description 6

- 230000007017 scission Effects 0.000 description 6

- 238000001228 spectrum Methods 0.000 description 6

- 238000010521 absorption reaction Methods 0.000 description 5

- 230000008878 coupling Effects 0.000 description 5

- 238000010168 coupling process Methods 0.000 description 5

- 238000005859 coupling reaction Methods 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 230000007547 defect Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 230000001629 suppression Effects 0.000 description 4

- 238000001039 wet etching Methods 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 238000002347 injection Methods 0.000 description 3

- 239000007924 injection Substances 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 230000010363 phase shift Effects 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 230000002159 abnormal effect Effects 0.000 description 2

- 125000004429 atom Chemical group 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 238000006731 degradation reaction Methods 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 239000000835 fiber Substances 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 238000010884 ion-beam technique Methods 0.000 description 2

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 239000011241 protective layer Substances 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- KZBUYRJDOAKODT-UHFFFAOYSA-N Chlorine Chemical compound ClCl KZBUYRJDOAKODT-UHFFFAOYSA-N 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000000460 chlorine Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 239000012792 core layer Substances 0.000 description 1

- 238000003795 desorption Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 235000012489 doughnuts Nutrition 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 125000005842 heteroatom Chemical group 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 125000004437 phosphorous atom Chemical group 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 230000008719 thickening Effects 0.000 description 1

- 238000000927 vapour-phase epitaxy Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/10—Construction or shape of the optical resonator, e.g. extended or external cavity, coupled cavities, bent-guide, varying width, thickness or composition of the active region

- H01S5/12—Construction or shape of the optical resonator, e.g. extended or external cavity, coupled cavities, bent-guide, varying width, thickness or composition of the active region the resonator having a periodic structure, e.g. in distributed feedback [DFB] lasers

- H01S5/1231—Grating growth or overgrowth details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/20—Structure or shape of the semiconductor body to guide the optical wave ; Confining structures perpendicular to the optical axis, e.g. index or gain guiding, stripe geometry, broad area lasers, gain tailoring, transverse or lateral reflectors, special cladding structures, MQW barrier reflection layers

- H01S5/2054—Methods of obtaining the confinement

- H01S5/2081—Methods of obtaining the confinement using special etching techniques

- H01S5/209—Methods of obtaining the confinement using special etching techniques special etch stop layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/02—Structural details or components not essential to laser action

- H01S5/026—Monolithically integrated components, e.g. waveguides, monitoring photo-detectors, drivers

- H01S5/0267—Integrated focusing lens

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/02—Structural details or components not essential to laser action

- H01S5/028—Coatings ; Treatment of the laser facets, e.g. etching, passivation layers or reflecting layers

- H01S5/0287—Facet reflectivity

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/10—Construction or shape of the optical resonator, e.g. extended or external cavity, coupled cavities, bent-guide, varying width, thickness or composition of the active region

- H01S5/12—Construction or shape of the optical resonator, e.g. extended or external cavity, coupled cavities, bent-guide, varying width, thickness or composition of the active region the resonator having a periodic structure, e.g. in distributed feedback [DFB] lasers

- H01S5/125—Distributed Bragg reflector [DBR] lasers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/20—Structure or shape of the semiconductor body to guide the optical wave ; Confining structures perpendicular to the optical axis, e.g. index or gain guiding, stripe geometry, broad area lasers, gain tailoring, transverse or lateral reflectors, special cladding structures, MQW barrier reflection layers

- H01S5/22—Structure or shape of the semiconductor body to guide the optical wave ; Confining structures perpendicular to the optical axis, e.g. index or gain guiding, stripe geometry, broad area lasers, gain tailoring, transverse or lateral reflectors, special cladding structures, MQW barrier reflection layers having a ridge or stripe structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/20—Structure or shape of the semiconductor body to guide the optical wave ; Confining structures perpendicular to the optical axis, e.g. index or gain guiding, stripe geometry, broad area lasers, gain tailoring, transverse or lateral reflectors, special cladding structures, MQW barrier reflection layers

- H01S5/22—Structure or shape of the semiconductor body to guide the optical wave ; Confining structures perpendicular to the optical axis, e.g. index or gain guiding, stripe geometry, broad area lasers, gain tailoring, transverse or lateral reflectors, special cladding structures, MQW barrier reflection layers having a ridge or stripe structure

- H01S5/227—Buried mesa structure ; Striped active layer

- H01S5/2275—Buried mesa structure ; Striped active layer mesa created by etching

Landscapes

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- Optics & Photonics (AREA)

- Geometry (AREA)

- Semiconductor Lasers (AREA)

Description

本発明の実施形態を説明する前に、まず本発明の比較例に係る上方回折格子型DRレーザの一構成例について説明する。

第1の実施形態は本発明を、DFBレーザ領域とDBRミラー領域が側壁形状制御層を介してBJ集積された、リッジ導波路型の上方回折格子型DRレーザ(半導体光集積素子の一例)に適用したものである。

次に、本発明の第2の実施形態について説明する。第2の実施形態は、本発明を、DFBレーザ領域とDBRミラー領域が側壁形状制御層を介してBJ集積された、リッジ導波路型の上方回折格子型DRレーザに適用したものである。

次に、本発明の第3の実施形態について説明する。第3の実施形態は、本発明を水平共振器型面出射の機構を有するDRレーザに適用した例である。図4Aは、本実施形態のDRレーザ400の光軸方向断面図であり、図4Bは上面図である。

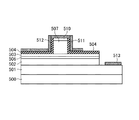

次に、本発明の第4の実施形態について説明する。第4の実施形態は本発明を、半絶縁性InP基板上に形成した上方回折格子型DRレーザに適用した例である。図5Aは、本実施形態のDRレーザ500の光軸方向断面図であり、図5Bは、図5AのL3位置における光軸垂直方向の断面図である。本実施形態のDRレーザ500は基板を除く多層構造は第1の実施形態に記載のDRレーザ200と同一である。従って、側壁形状制御層形成やBJ集積を含むエピタキシャル成長工程は第1の実施形態と同じである。

次に、本発明の第5の実施形態について説明する。第5の実施形態は、本発明を埋め込みヘテロ(BH:Beried Hetero)型の上方回折格子型DRレーザに適用した例である。図6Aは、本実施形態のDRレーザ600の光共振器部分の光軸方向断面図であり、図6B、図6Cはそれぞれ、図6AのL4、L5位置における光軸垂直方向の断面図である。

次に、図7に基づき、本発明の実施形態に係るDRレーザを搭載した光送受信モジュール(光モジュール)の構成例について説明する。なお、光送受信モジュールに搭載されるDRレーザは、本発明を適用した半導体光集積素子であれば、上述した第1〜第5の実施形態に限られるものではない。

550 半絶縁性InP基板、

501 n型InPバッファ層、

202、302、402、502、602 InGaAlAs系活性層、

106、203、303、403、503、130 p型InGaAsPエッチング停止層、

107、204、206、304、306、404、406、504、506、603、604 p型InPスペーサ層、

108、205、305、405、505、605 p型InGaAsP回折格子層、

113、207、308、408、507、606 p型InPクラッド層、

110、208、309、409、508、607 アンドープInGaAsP光導波路層、

109、209、310、410、509、608 n型InP側壁形状制御層、

114、210、311、411、510、609 p型InGaAsコンタクト層、

115、119、211、312、511、610 SiO2保護膜、

116、212、313、413、512、611 p型電極、

117、213、314、414、513、612 n型電極、

118、214、315、415、418、514、613 誘電体無反射膜、

416 集積ミラー、

417 集積レンズ、

419 p型電極パッド、

420 n型電極コンタクト部、

421 リッジ型ストライプ、

307、407 p型InPバッファ層、

102 n型InGaAlAs光ガイド層、

103 InGaAlAs多重量子井戸、

104 p型InGaAlAs光ガイド層、

105 p型InAlAs電子ストップ層、

111 アンドープInPクラッド層、

112 アンドープInGaAsP回折格子層、

614 半絶縁性InP埋め込み層、

215 SiO2パターニングマスク。

Claims (15)

- 半導体基板上に、第1半導体光素子及び第2半導体光素子が、光軸を揃え突き合わせ接続される半導体光集積素子であって、

前記第1半導体光素子は、光を発生する活性層を含み、

前記第2半導体光素子は、前記活性層で発生する光を導波する導波路層を含み、

前記半導体光集積素子は、

前記活性層と前記導波路層の上部の全面に渡って、一回のエピタキシャル成長で形成される回折格子層及びエッチング停止層を含む半導体再成長層と、

前記半導体再成長層の上部に形成されるクラッド層と、を含み、

前記回折格子層は第1導電型にドーピングされ、

前記回折格子層は前記エッチング停止層の上に配置される、

ことを特徴とする半導体光集積素子。 - 請求項1に記載の半導体光集積素子において、

前記半導体再成長層が、前記クラッド層を所定のエッチング溶液を用いて化学エッチングする際のエッチング停止層を含む

ことを特徴とする半導体光集積素子。 - 請求項1に記載の半導体光集積素子において、

前記半導体再成長層は、

前記エッチング停止層の上に前記スペーサ層が形成され、

前記スペーサ層の上に前記回折格子層が形成される

ことを特徴とする半導体光集積素子。 - 請求項1乃至3のいずれかに記載の半導体光集積素子において、

前記半導体再成長層は、前記クラッド層と同一の半導体材料からなり、前記クラッド層とはドーピングイオン濃度が異なる半導体材料からなるバッファ層を更に含み、

前記バッファ層は、前記活性層および前記導波路層の上に形成される

ことを特徴とする半導体光集積素子。 - 請求項1乃至4のいずれかに記載の半導体光集積素子において、

光軸を揃え突き合わせ接続される前記活性層と前記導波路層との接続界面に形成される側壁形状制御層を含む

ことを特徴とする半導体光集積素子。 - 請求項5に記載の半導体光集積素子において、

前記活性層は、アルミを含み、

前記活性層の上に、リンを含むリン系スペーサ層を含み、

前記リン系スペーサ層は、前記活性層を覆い、且つ、前記半導体光集積素子における前記接続界面とは反対の端部から前記側壁形状制御層の上にまで達する庇状に形成される

ことを特徴とする半導体光集積素子。 - 請求項1乃至6のいずれかに記載の半導体光集積素子において、

前記第1半導体光素子は、分布帰還型半導体レーザであり、

前記第2半導体光素子は、分布ブラッグ反射ミラーである

ことを特徴とする半導体光集積素子。 - 請求項1乃至7のいずれかに記載の半導体光集積素子において、

前記第2半導体光素子と反対側において、前記第1半導体光素子と光軸を揃え突き合わせ接続される第3半導体光素子を更に含み、

前記第3半導体光素子は、

前記活性層で発生する光を導波する導波路層を含み、

前記半導体再成長層は、前記活性層、前記第2半導体光素子の前記導波路層及び前記第3半導体光素子の前記導波路層の上部の全面に渡って、一回のエピタキシャル成長で形成される回折格子層及びエッチング停止層を含み、

前記回折格子層は前記第1導電型にドーピングされ、

前記回折格子層は前記エッチング停止層の上に配置される、

ことを特徴とする半導体光集積素子。 - 請求項8に記載の半導体光集積素子において、

前記第3半導体光素子は、分布ブラッグ反射ミラーである

ことを特徴とする半導体光集積素子。 - 請求項1乃至9のいずれかに記載の半導体光集積素子において、

光出射端に前記活性層から発生した光を前記半導体基板面に向かって反射させる反射鏡と、

前記半導体基板面上であって、前記反射鏡によって反射された光が出射する位置に設けられた、当該光を集光するためのレンズと、を更に含む

ことを特徴とする半導体光集積素子。 - 半導体基板上に、第1半導体光素子及び第2半導体光素子が、光軸を揃え突き合わせ接続される半導体光集積素子の製造方法であって、

前記第1半導体光素子に、光を発生する活性層を形成する工程と、

前記第2半導体光素子に、前記活性層で発生する光を導波する導波路層を形成する工程と、

前記活性層と前記導波路層の上部の全面に渡って、エッチング停止層及び回折格子層をこの順に一回のエピタキシャル成長で形成する工程と、

前記回折格子層に第1導電型にドーピングをする工程と、

前記エッチング停止層及び回折格子層を含む半導体再成長層の上部にクラッド層を形成する工程と、を含む、

半導体光集積素子の製造方法。 - 請求項11に記載の半導体光集積素子の製造方法において、

前記クラッド層を所定のエッチング溶液を用いて化学エッチングする際のエッチング停止層と、前記クラッド層と同一の半導体材料であり、前記クラッド層とはドーピングイオン濃度が異なる半導体材料からなるスペーサ層と、回折格子層を順に積層して形成する工程と、

前記回折格子層に光軸方向に沿って所定のピッチを有する回折格子を形成する工程と

を含む

ことを特徴とする半導体光集積素子の製造方法。 - 請求項11又は12に記載の半導体光集積素子の製造方法において、

前記活性層で発生する光を導波する導波路層を含む、前記第1半導体光素子と光軸を揃え突き合わせ接続される第3半導体光素子を、前記第2半導体光素子と反対側に形成する工程を更に含み、

前記一回のエピタキシャル成長で形成する工程では、前記活性層、前記第2半導体光素子の前記導波路層及び前記第3半導体光素子の前記導波路層の上部の全面に渡って、前記エッチング停止層及び回折格子層がこの順に一回のエピタキシャル成長で形成される

ことを特徴とする半導体光集積素子の製造方法。 - 請求項11乃至13に記載のいずれかひとつの半導体光集積素子の製造方法において、

マストランスポート現象によって、前記半導体基板の形状を変化させて、前記活性層と前記導波路層との接続界面において、前記活性層と前記導波路層のそれぞれの側壁に接する側壁形状制御層を形成する工程と、

前記活性層の直上にリンを含むリン系スペーサ層を形成する工程と、を更に含み、

前記活性層は、アルミを含み、

前記リン系スペーサ層は、前記活性層を覆い、且つ、前記半導体光集積素子における前記接続界面とは反対の端部から前記側壁形状制御層の上にまで達する庇状に形成される

ことを特徴とする半導体光集積素子の製造方法。 - 請求項1乃至10のいずれかに記載の半導体光集積素子と、

前記半導体光集積素子を駆動する駆動回路と、

前記半導体光集積素子及び前記駆動回路を収容する筺体と、を備えることを特徴とする光モジュール。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014248981A JP6487195B2 (ja) | 2014-12-09 | 2014-12-09 | 半導体光集積素子、半導体光集積素子の製造方法及び光モジュール |

| US14/961,984 US9780530B2 (en) | 2014-12-09 | 2015-12-08 | Semiconductor integrated optical device, manufacturing method thereof and optical module |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014248981A JP6487195B2 (ja) | 2014-12-09 | 2014-12-09 | 半導体光集積素子、半導体光集積素子の製造方法及び光モジュール |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016111263A JP2016111263A (ja) | 2016-06-20 |

| JP2016111263A5 JP2016111263A5 (ja) | 2017-09-21 |

| JP6487195B2 true JP6487195B2 (ja) | 2019-03-20 |

Family

ID=56095185

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014248981A Active JP6487195B2 (ja) | 2014-12-09 | 2014-12-09 | 半導体光集積素子、半導体光集積素子の製造方法及び光モジュール |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9780530B2 (ja) |

| JP (1) | JP6487195B2 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10063032B2 (en) | 2016-03-06 | 2018-08-28 | Finisar Corporation | Distributed reflector laser |

| DE102016106495A1 (de) * | 2016-04-08 | 2017-10-12 | Osram Opto Semiconductors Gmbh | Halbleiterlaser |

| JP6388007B2 (ja) * | 2016-08-08 | 2018-09-12 | 三菱電機株式会社 | 光デバイスの製造方法 |

| JP7046484B2 (ja) * | 2016-11-30 | 2022-04-04 | 日本ルメンタム株式会社 | アレイ半導体光素子、光送信モジュール、及び光モジュール、並びに、それらの製造方法 |

| DE102017100997A1 (de) * | 2017-01-19 | 2018-07-19 | Osram Opto Semiconductors Gmbh | Halbleiterlaser und Verfahren zur Herstellung eines solchen Halbleiterlasers |

| CN107863686B (zh) * | 2017-10-25 | 2023-05-09 | 中国科学院福建物质结构研究所 | 一种激光二极管与背光探测器集成的制备方法及集成芯片 |

| JP2020174140A (ja) * | 2019-04-11 | 2020-10-22 | 住友電気工業株式会社 | 半導体集積光デバイス、半導体集積光デバイスを作製する方法 |

| FR3095903B1 (fr) * | 2019-05-09 | 2022-12-09 | Commissariat Energie Atomique | Laser monomode hybride III-V sur silicium de fabrication simplifiée |

| CN110824721B (zh) * | 2019-09-24 | 2021-11-23 | 杭州驭光光电科技有限公司 | 衍射光学组件的设计方法及衍射光学组件 |

| US11251585B2 (en) | 2019-10-01 | 2022-02-15 | Ii-Vi Delaware, Inc. | DFB with weak optical feedback |

| US11233375B2 (en) | 2019-10-01 | 2022-01-25 | Ii-Vi Delaware, Inc. | Two-kappa DBR laser |

| US11784464B2 (en) | 2020-09-30 | 2023-10-10 | Ii-Vi Delaware, Inc. | Directly modulated laser |

| JP2024113981A (ja) | 2023-02-10 | 2024-08-23 | 富士通オプティカルコンポーネンツ株式会社 | 光デバイス、光モジュール及び光トランシーバ |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008277445A (ja) | 2007-04-26 | 2008-11-13 | Opnext Japan Inc | 半導体レーザおよび光モジュール |

| JP5047704B2 (ja) | 2007-06-20 | 2012-10-10 | 日本オクラロ株式会社 | 光集積素子 |

| JP5163355B2 (ja) | 2008-08-08 | 2013-03-13 | 富士通株式会社 | 半導体レーザ装置 |

| WO2010111689A2 (en) * | 2009-03-26 | 2010-09-30 | Kaiam Corp. | A semiconductor laser device and circuit for and method of driving same |

| JP5691216B2 (ja) * | 2010-03-29 | 2015-04-01 | 富士通株式会社 | 光半導体集積素子及びその製造方法 |

| JP6084428B2 (ja) * | 2012-10-18 | 2017-02-22 | 日本オクラロ株式会社 | 半導体光集積素子及びその製造方法 |

| US9048618B2 (en) * | 2013-03-12 | 2015-06-02 | Finisar Corporation | Short gain cavity distributed bragg reflector laser |

-

2014

- 2014-12-09 JP JP2014248981A patent/JP6487195B2/ja active Active

-

2015

- 2015-12-08 US US14/961,984 patent/US9780530B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20160164257A1 (en) | 2016-06-09 |

| JP2016111263A (ja) | 2016-06-20 |

| US9780530B2 (en) | 2017-10-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6487195B2 (ja) | 半導体光集積素子、半導体光集積素子の製造方法及び光モジュール | |

| US8472494B2 (en) | Semiconductor laser silicon waveguide substrate, and integrated device | |

| WO2011096040A1 (ja) | 半導体レーザ素子、半導体レーザ素子の製造方法および光モジュール | |

| US9088132B2 (en) | Semiconductor optical element, integrated semiconductor optical element, and semiconductor optical element module | |

| JP2013251394A (ja) | 半導体レーザ装置 | |

| US6850550B2 (en) | Complex coupling MQW semiconductor laser | |

| US9601903B2 (en) | Horizontal cavity surface emitting laser device | |

| US20150357792A1 (en) | Semiconductor laser element, integrated semiconductor laser element, and method for producing semiconductor laser element | |

| JP2017204601A (ja) | 半導体レーザ | |

| US7949020B2 (en) | Semiconductor laser and optical integrated semiconductor device | |

| JP2015164148A (ja) | 集積型半導体光素子、及び集積型半導体光素子の製造方法 | |

| JP7376837B2 (ja) | 半導体チップおよび光モジュール | |

| CN107623250A (zh) | 一种短腔长面发射激光器及其制造方法 | |

| US12027818B2 (en) | Semiconductor laser | |

| JP5206976B2 (ja) | 半導体レーザ及びその製造方法 | |

| US20170194766A1 (en) | Optical device and optical module | |

| CN115051239A (zh) | 可调谐电吸收调制激光器及其制备方法 | |

| JP5163355B2 (ja) | 半導体レーザ装置 | |

| JP2002057405A (ja) | 半導体レーザ装置及びその製造方法 | |

| JP4457000B2 (ja) | 光増幅装置 | |

| JP2009016878A (ja) | 半導体レーザ及びそれを用いた光モジュール | |

| JP2000183443A (ja) | スポットサイズ変換器付き半導体レーザ装置、及びその製造方法 | |

| JP2009244648A (ja) | 光変調器、その製造方法、光集積素子およびその製造方法 | |

| US20130129278A1 (en) | Integrated semiconductor device | |

| JP5310187B2 (ja) | 半導体レーザ、その製造方法、及び光送信器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170807 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170807 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20180629 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180807 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181009 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190205 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190221 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6487195 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |