JP6177155B2 - 発振回路および周波数シンセサイザ - Google Patents

発振回路および周波数シンセサイザ Download PDFInfo

- Publication number

- JP6177155B2 JP6177155B2 JP2014023064A JP2014023064A JP6177155B2 JP 6177155 B2 JP6177155 B2 JP 6177155B2 JP 2014023064 A JP2014023064 A JP 2014023064A JP 2014023064 A JP2014023064 A JP 2014023064A JP 6177155 B2 JP6177155 B2 JP 6177155B2

- Authority

- JP

- Japan

- Prior art keywords

- value

- code value

- frequency

- frequency control

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000010355 oscillation Effects 0.000 claims description 138

- 230000035945 sensitivity Effects 0.000 claims description 41

- 239000003990 capacitor Substances 0.000 claims description 40

- 230000001186 cumulative effect Effects 0.000 claims description 37

- 230000008859 change Effects 0.000 claims description 30

- 238000001514 detection method Methods 0.000 claims description 20

- 230000003247 decreasing effect Effects 0.000 claims description 2

- 101001020552 Rattus norvegicus LIM/homeobox protein Lhx1 Proteins 0.000 description 18

- 238000010586 diagram Methods 0.000 description 18

- 238000004364 calculation method Methods 0.000 description 12

- 230000000694 effects Effects 0.000 description 6

- 238000006243 chemical reaction Methods 0.000 description 5

- 230000007423 decrease Effects 0.000 description 5

- 230000004048 modification Effects 0.000 description 4

- 238000012986 modification Methods 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 3

- 230000007704 transition Effects 0.000 description 3

- 230000009471 action Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 229920006395 saturated elastomer Polymers 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 1

- 230000000052 comparative effect Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/083—Details of the phase-locked loop the reference signal being additionally directly applied to the generator

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03B—GENERATION OF OSCILLATIONS, DIRECTLY OR BY FREQUENCY-CHANGING, BY CIRCUITS EMPLOYING ACTIVE ELEMENTS WHICH OPERATE IN A NON-SWITCHING MANNER; GENERATION OF NOISE BY SUCH CIRCUITS

- H03B5/00—Generation of oscillations using amplifier with regenerative feedback from output to input

- H03B5/08—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance

- H03B5/12—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance active element in amplifier being semiconductor device

- H03B5/1206—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance active element in amplifier being semiconductor device using multiple transistors for amplification

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03B—GENERATION OF OSCILLATIONS, DIRECTLY OR BY FREQUENCY-CHANGING, BY CIRCUITS EMPLOYING ACTIVE ELEMENTS WHICH OPERATE IN A NON-SWITCHING MANNER; GENERATION OF NOISE BY SUCH CIRCUITS

- H03B5/00—Generation of oscillations using amplifier with regenerative feedback from output to input

- H03B5/08—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance

- H03B5/12—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance active element in amplifier being semiconductor device

- H03B5/1237—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance active element in amplifier being semiconductor device comprising means for varying the frequency of the generator

- H03B5/124—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance active element in amplifier being semiconductor device comprising means for varying the frequency of the generator the means comprising a voltage dependent capacitance

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03B—GENERATION OF OSCILLATIONS, DIRECTLY OR BY FREQUENCY-CHANGING, BY CIRCUITS EMPLOYING ACTIVE ELEMENTS WHICH OPERATE IN A NON-SWITCHING MANNER; GENERATION OF NOISE BY SUCH CIRCUITS

- H03B5/00—Generation of oscillations using amplifier with regenerative feedback from output to input

- H03B5/08—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance

- H03B5/12—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance active element in amplifier being semiconductor device

- H03B5/1237—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance active element in amplifier being semiconductor device comprising means for varying the frequency of the generator

- H03B5/1262—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance active element in amplifier being semiconductor device comprising means for varying the frequency of the generator the means comprising switched elements

- H03B5/1265—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element comprising lumped inductance and capacitance active element in amplifier being semiconductor device comprising means for varying the frequency of the generator the means comprising switched elements switched capacitors

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/093—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using special filtering or amplification characteristics in the loop

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03B—GENERATION OF OSCILLATIONS, DIRECTLY OR BY FREQUENCY-CHANGING, BY CIRCUITS EMPLOYING ACTIVE ELEMENTS WHICH OPERATE IN A NON-SWITCHING MANNER; GENERATION OF NOISE BY SUCH CIRCUITS

- H03B2201/00—Aspects of oscillators relating to varying the frequency of the oscillations

- H03B2201/02—Varying the frequency of the oscillations by electronic means

- H03B2201/0275—Varying the frequency of the oscillations by electronic means the means delivering several selected voltages or currents

- H03B2201/0283—Varying the frequency of the oscillations by electronic means the means delivering several selected voltages or currents the means functioning digitally

- H03B2201/0291—Varying the frequency of the oscillations by electronic means the means delivering several selected voltages or currents the means functioning digitally and being controlled by a processing device, e.g. a microprocessor

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03J—TUNING RESONANT CIRCUITS; SELECTING RESONANT CIRCUITS

- H03J2200/00—Indexing scheme relating to tuning resonant circuits and selecting resonant circuits

- H03J2200/10—Tuning of a resonator by means of digitally controlled capacitor bank

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Stabilization Of Oscillater, Synchronisation, Frequency Synthesizers (AREA)

Description

(全体構成例)

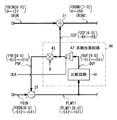

図1は、第1の実施の形態に係る周波数シンセサイザの一構成例を表すものである。図1では、太線で示した配線は、複数のビットからなるワードを伝えるいわゆるバス配線を示し、細線で示した配線は、1つの信号または差動信号を伝える配線を示す。周波数シンセサイザ1は、デジタル制御発振回路(DCO)を有するデジタルPLLである。なお、本開示の実施の形態に係る発振回路は、本実施の形態により具現化されるので、併せて説明する。

図3は、発振回路15の一構成例を表すものである。発振回路15は、制御部20と、発振部30とを有している。

続いて、本実施の形態の周波数シンセサイザ1の動作および作用について説明する。

まず、図1,3,4などを参照して、周波数シンセサイザ1の全体動作概要を説明する。基準位相生成回路11は、分周比ワードFCWおよびクロック信号CLKに基づいて、基準位相ワードPW1を生成する。位相比較回路12は、基準位相ワードPW1および位相ワードPW2に基づいて、位相誤差ワードPEWを生成する。ループフィルタ13は、位相誤差ワードPEWおよびクロック信号CLKに基づいて、位相誤差ワードPEW2を生成する。利得調整回路14は、位相誤差ワードPEW2に基づいて、周波数制御ワードCBIN,FBINを生成する。発振回路15は、周波数制御ワードCBIN,FBINおよびクロック信号CLKに基づいて、クロック信号DCOCLK,DCOCLKBを生成する。具体的には、発振回路15では、制御部20が、周波数制御ワードCBIN,FBINおよびクロック信号CLKに基づいて、周波数制御ワードCBIN,FBINを周波数制御ワードCTM,FTMに変換し、発振部30が、周波数制御ワードCTM,FTMに基づいて、周波数制御ワードCTM,FTMに応じた周波数foのクロック信号DCOCLK,DCOCLKBを生成する。位相検出回路16は、クロック信号DCOCLK,DCOCLKB、基準クロック信号REFCLK、およびクロック信号CLKに基づいて、位相ワードPW2を生成する。リタイミング回路17は、基準クロック信号REFCLKをクロック信号DCOCLK,DCOCLKBに基づくタイミングでリタイミングして、クロック信号CLKとして出力する。

次に、周波数シンセサイザ1の詳細動作について説明する。周波数シンセサイザ1は、例えば、電源投入直後などの初期状態では、微調整用の周波数制御ワードFBINを所定の値(例えば“0”)に固定し、粗調整用の周波数制御ワードCBINを変化させることにより負帰還動作を行う。その際、補正ワードCCF,FCFが示す値は“0”を維持するため、制御部20は、粗調整用の周波数制御ワードCBINが示す値をサーモメータコードに変換することにより周波数制御ワードCTMを生成する。そして、周波数シンセサイザ1は、この負帰還動作により、周波数foを目標周波数ftargetに近付ける(動作P1)。

以上のように本実施の形態では、周波数制御ワードFLMT1の値がしきい値TH1よりも大きくなった場合やしきい値TL1よりも小さくなった場合に、粗調整用の可変容量バンクの設定を切り替えるようにしたので、粗調整用の可変容量バンクの設定を切り替える頻度を少なくすることができ、位相雑音を低減することができる。

周波数シンセサイザの構成は、図1の構成に限定されるものではない。以下に、他の構成について詳細に説明する。

前記第1のコード値に基づいて第1の感度で発振信号の周波数が変化し、前記第2のコード値に基づいて前記第1の感度よりも高い第2の感度で前記発振信号の周波数が変化する発振部と

を備えた発振回路。

前記(1)に記載の発振回路。

前記(1)または(2)に記載の発振回路。

前記第1のコード値と、前記第1の所定の範囲よりも狭い第2の所定の範囲の上限値および下限値とを比較して比較結果値を生成する比較部と、

前記比較結果値を累積加算して累積値を求める累積加算部と、

前記累積値に基づいて前記第1の入力コード値を補正するとともに前記第2の入力コード値を補正する補正部と

を有する

前記(1)から(3)のいずれかに記載の発振回路。

前記(4)に記載の発振回路。

前記補正部は、前記第2の入力コード値を前記累積値の分だけ増やすことにより前記第2の入力コードを補正し、前記第1の入力コード値を、前記第1の感度を前記第2の感度で除算した値と前記累積値との積の分だけ減らすことにより前記第1の入力コード値を補正する

前記(4)または(5)に記載の発振回路。

インダクタと

前記インダクタと並列接続され、前記第1のコード値に基づいて容量値が変化する第1の可変容量バンクと、

前記インダクタと並列接続され、前記第2のコード値に基づいて容量値が変化する第2の可変容量バンクと

を有する

前記(1)から(6)のいずれかに記載の発振回路。

前記第2の可変容量バンクは、前記第2の感度に対応する変化率で容量値が変化する第2の可変容量素子を複数有する

前記(7)に記載の発振回路。

前記基準位相信号と帰還位相信号との位相差を検出する位相比較回路と、

前記位相比較回路における検出結果に基づいて第1の入力コード値および第2の入力コード値を生成する周波数制御回路と、

前記第1の入力コード値および前記第2の入力コード値に基づいて発振信号を生成する発振回路と、

前記発振信号の位相を求めて前記帰還位相信号として出力する位相検出回路と

を備え、

前記発振回路は、

前記第1の入力コード値を補正することにより、前記第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、前記第1の入力コード値の補正量に応じて前記第2の入力コード値を補正して第2のコード値を生成する演算部と、

前記第1のコード値に応じて第1の感度で発振信号の周波数が変化し、前記第2のコード値に応じて前記第1の感度よりも高い第2の感度で前記発振信号の周波数が変化する発振部と

を有する

周波数シンセサイザ。

前記位相比較回路における検出結果に基づいて第1の入力コード値および第2の入力コード値を生成する周波数制御回路と、

前記第1の入力コード値および前記第2の入力コード値に基づいて発振信号を生成する発振回路と、

前記発振信号を分周して前記帰還クロック信号を生成する分周回路と

を備え、

前記発振回路は、

前記第1の入力コード値を補正することにより、前記第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、前記第1の入力コード値の補正量に応じて前記第2の入力コード値を補正して第2のコード値を生成する演算部と、

前記第1のコード値に応じて第1の感度で発振信号の周波数が変化し、前記第2のコード値に応じて前記第1の感度よりも高い第2の感度で前記発振信号の周波数が変化する発振部と

を有する

周波数シンセサイザ。

Claims (9)

- 第1の入力コード値を補正することにより、前記第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、前記第1の入力コード値の補正量に応じて第2の入力コード値を補正して第2のコード値を生成する演算部と、

前記第1のコード値に基づいて第1の感度で発振信号の周波数が変化し、前記第2のコード値に基づいて前記第1の感度よりも高い第2の感度で前記発振信号の周波数が変化する発振部と

を備え、

前記演算部は、

前記第1のコード値と、前記第1の所定の範囲よりも狭い第2の所定の範囲の上限値および下限値とを比較して比較結果値を生成する比較部と、

前記比較結果値を累積加算して累積値を求める累積加算部と、

前記累積値に基づいて前記第1の入力コード値を補正するとともに前記第2の入力コード値を補正する補正部と

を有する

発振回路。 - 前記第1の入力コード値の補正による前記発振信号の周波数の変化方向と、前記第2の入力コード値の補正による前記発振信号の周波数の変化方向とは、互いに反対方向である

請求項1に記載の発振回路。 - 前記第2の入力コード値の補正量は、前記第1の感度と前記第2の感度との感度比、および前記第1の入力コード値の補正量に応じた量である

請求項1または請求項2に記載の発振回路。 - 前記比較部は、さらに、前記第1のコード値と、前記第1の所定の範囲の上限値および下限値とを比較して、前記比較結果値を生成する

請求項1から請求項3のいずれか一項に記載の発振回路。 - 前記比較結果値は、前記第1のコード値が前記第2の所定の範囲の上限値よりも大きい場合には正の値であり、前記第1のコード値が前記第2の所定の範囲の下限値よりも小さい場合には負の値であり、

前記補正部は、前記第2の入力コード値を前記累積値の分だけ増やすことにより前記第2の入力コード値を補正し、前記第1の入力コード値を、前記第2の感度を前記第1の感度で除算した値と前記累積値との積の分だけ減らすことにより前記第1の入力コード値を補正する

請求項1から請求項4のいずれか一項に記載の発振回路。 - 前記発振部は、

インダクタと

前記インダクタと並列接続され、前記第1のコード値に基づいて容量値が変化する第1の可変容量バンクと、

前記インダクタと並列接続され、前記第2のコード値に基づいて容量値が変化する第2の可変容量バンクと

を有する

請求項1から請求項5のいずれか一項に記載の発振回路。 - 前記第1の可変容量バンクは、前記第1の感度に対応する変化率で容量値が変化する第1の可変容量素子を複数有し、

前記第2の可変容量バンクは、前記第2の感度に対応する変化率で容量値が変化する第2の可変容量素子を複数有する

請求項6に記載の発振回路。 - 基準位相信号を生成する基準位相生成回路と、

前記基準位相信号と帰還位相信号との位相差を検出する位相比較回路と、

前記位相比較回路における検出結果に基づいて第1の入力コード値および第2の入力コード値を生成する周波数制御回路と、

前記第1の入力コード値および前記第2の入力コード値に基づいて発振信号を生成する発振回路と、

前記発振信号の位相を求めて前記帰還位相信号として出力する位相検出回路と

を備え、

前記発振回路は、

前記第1の入力コード値を補正することにより、前記第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、前記第1の入力コード値の補正量に応じて前記第2の入力コード値を補正して第2のコード値を生成する演算部と、

前記第1のコード値に応じて第1の感度で発振信号の周波数が変化し、前記第2のコード値に応じて前記第1の感度よりも高い第2の感度で前記発振信号の周波数が変化する発振部と

を有し、

前記演算部は、

前記第1のコード値と、前記第1の所定の範囲よりも狭い第2の所定の範囲の上限値および下限値とを比較して比較結果値を生成する比較部と、

前記比較結果値を累積加算して累積値を求める累積加算部と、

前記累積値に基づいて前記第1の入力コード値を補正するとともに前記第2の入力コード値を補正する補正部と

を有する

周波数シンセサイザ。 - 入力クロック信号と帰還クロック信号との間の位相差を検出する位相比較回路と、

前記位相比較回路における検出結果に基づいて第1の入力コード値および第2の入力コード値を生成する周波数制御回路と、

前記第1の入力コード値および前記第2の入力コード値に基づいて発振信号を生成する発振回路と、

前記発振信号を分周して前記帰還クロック信号を生成する分周回路と

を備え、

前記発振回路は、

前記第1の入力コード値を補正することにより、前記第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、前記第1の入力コード値の補正量に応じて前記第2の入力コード値を補正して第2のコード値を生成する演算部と、

前記第1のコード値に応じて第1の感度で発振信号の周波数が変化し、前記第2のコード値に応じて前記第1の感度よりも高い第2の感度で前記発振信号の周波数が変化する発振部と

を有し、

前記演算部は、

前記第1のコード値と、前記第1の所定の範囲よりも狭い第2の所定の範囲の上限値および下限値とを比較して比較結果値を生成する比較部と、

前記比較結果値を累積加算して累積値を求める累積加算部と、

前記累積値に基づいて前記第1の入力コード値を補正するとともに前記第2の入力コード値を補正する補正部と

を有する

周波数シンセサイザ。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014023064A JP6177155B2 (ja) | 2014-02-10 | 2014-02-10 | 発振回路および周波数シンセサイザ |

| US14/608,264 US9391622B2 (en) | 2014-02-10 | 2015-01-29 | Oscillator circuit and frequency synthesizer |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2014023064A JP6177155B2 (ja) | 2014-02-10 | 2014-02-10 | 発振回路および周波数シンセサイザ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2015149694A JP2015149694A (ja) | 2015-08-20 |

| JP2015149694A5 JP2015149694A5 (ja) | 2016-03-03 |

| JP6177155B2 true JP6177155B2 (ja) | 2017-08-09 |

Family

ID=53775865

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014023064A Active JP6177155B2 (ja) | 2014-02-10 | 2014-02-10 | 発振回路および周波数シンセサイザ |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9391622B2 (ja) |

| JP (1) | JP6177155B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10503122B2 (en) | 2017-04-14 | 2019-12-10 | Innophase, Inc. | Time to digital converter with increased range and sensitivity |

| US10840921B2 (en) * | 2018-09-07 | 2020-11-17 | Innophase Inc. | Frequency control word linearization for an oscillator |

| US10622959B2 (en) | 2018-09-07 | 2020-04-14 | Innophase Inc. | Multi-stage LNA with reduced mutual coupling |

| US11095296B2 (en) | 2018-09-07 | 2021-08-17 | Innophase, Inc. | Phase modulator having fractional sample interval timing skew for frequency control input |

| US10728851B1 (en) | 2019-01-07 | 2020-07-28 | Innophase Inc. | System and method for low-power wireless beacon monitor |

| US11070196B2 (en) | 2019-01-07 | 2021-07-20 | Innophase Inc. | Using a multi-tone signal to tune a multi-stage low-noise amplifier |

| JP7341933B2 (ja) | 2020-03-23 | 2023-09-11 | 株式会社東芝 | 半導体装置、デジタル制御発振器、周波数シンセサイザ、及び半導体装置の制御方法 |

| JP2021149996A (ja) | 2020-03-23 | 2021-09-27 | 株式会社東芝 | 半導体記憶装置、及び半導体記憶装置の制御方法 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| IL96351A (en) * | 1990-11-14 | 1994-01-25 | Zuta Marc | Frequency synthesizer having microcomputer supplying analog and digital control signals to vco |

| US7330079B2 (en) * | 2005-10-31 | 2008-02-12 | Texas Instruments Incorporated | Method and apparatus for rapid local oscillator frequency calibration |

| JP2009010599A (ja) * | 2007-06-27 | 2009-01-15 | Panasonic Corp | デジタル制御発振回路、周波数シンセサイザ、それを用いた無線通信機器及びその制御方法 |

| JP5457813B2 (ja) * | 2009-12-16 | 2014-04-02 | ルネサスエレクトロニクス株式会社 | Adpll回路、半導体装置及び携帯情報機器 |

| JP5515921B2 (ja) * | 2010-03-24 | 2014-06-11 | セイコーエプソン株式会社 | 恒温型圧電発振器の製造方法 |

| WO2011161860A1 (ja) * | 2010-06-21 | 2011-12-29 | パナソニック株式会社 | 周波数シンセサイザ |

-

2014

- 2014-02-10 JP JP2014023064A patent/JP6177155B2/ja active Active

-

2015

- 2015-01-29 US US14/608,264 patent/US9391622B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20150229318A1 (en) | 2015-08-13 |

| US9391622B2 (en) | 2016-07-12 |

| JP2015149694A (ja) | 2015-08-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6177155B2 (ja) | 発振回路および周波数シンセサイザ | |

| JP2010252289A (ja) | 電圧制御発振器のための補償回路 | |

| JPWO2011001652A1 (ja) | Pll回路、およびそれを搭載した無線通信装置 | |

| JP2015149694A5 (ja) | ||

| JP5205427B2 (ja) | 局部発振器 | |

| JP4625849B2 (ja) | 発振器制御装置 | |

| US9197227B2 (en) | Semiconductor device | |

| JP5010705B2 (ja) | デジタル制御発振器 | |

| JP4593669B2 (ja) | バラツキ補正方法、pll回路及び半導体集積回路 | |

| JP5097235B2 (ja) | 半導体装置 | |

| JP2006135892A (ja) | 電圧制御発振器及び発振周波数調整方法 | |

| US9654119B2 (en) | Phase locked loop and operating method thereof | |

| US7741889B2 (en) | Phase locked loop with phase rotation for spreading spectrum | |

| US20120139654A1 (en) | Frequency synthesizer | |

| JP2015154444A (ja) | タイムデジタルコンバータ及びこれに用いられるキャリブレーション方法 | |

| JPWO2010134287A1 (ja) | Pll周波数シンセサイザ | |

| JP2016063374A (ja) | 信号処理装置およびその制御方法 | |

| JP2017157921A (ja) | 位相同期回路 | |

| JP2011188323A (ja) | Pll回路 | |

| TWI424305B (zh) | 時脈產生器、時脈產生方法、與行動通訊裝置 | |

| JP2009077308A (ja) | 位相ロックループ回路 | |

| JP2009200703A (ja) | チャージポンプ回路およびpll回路 | |

| US20250112594A1 (en) | Spread spectrum clock generation circuit | |

| KR101680935B1 (ko) | 다중 적분 경로를 이용하는 디지털 위상 고정 루프 및 이의 동작 방법 | |

| CN101093996B (zh) | 数字控制振荡器的频率搜寻方法及使用该方法的解码器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160114 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160114 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20160720 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20160721 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161006 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161129 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170111 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170613 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170711 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6177155 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |