JP6096523B2 - 半導体装置とその製造方法 - Google Patents

半導体装置とその製造方法 Download PDFInfo

- Publication number

- JP6096523B2 JP6096523B2 JP2013018260A JP2013018260A JP6096523B2 JP 6096523 B2 JP6096523 B2 JP 6096523B2 JP 2013018260 A JP2013018260 A JP 2013018260A JP 2013018260 A JP2013018260 A JP 2013018260A JP 6096523 B2 JP6096523 B2 JP 6096523B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- gate electrode

- surface layer

- semiconductor device

- gan

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

本発明の目的は、このトレードオフの関係を打破することにある。即ち、安定的なノーマリオフ動作を保証することができ、しかもオン抵抗を低減することができる半導体装置を提供することを目的とする。

第1層は、p型又は真性の窒化ガリウムで構成されている。第2層は、n型の窒化アルミニウムガリウムで構成されている。表面層は、p型のGaN系化合物半導体で構成されている。表面層は、p型の窒化アルミニウムガリウムで構成されているのが好ましい。この半導体装置では、ゲート電極に電圧が印加されていない場合、第2層及び表面層が空乏化され、第2層の伝導体の下限がフェルミ準位よりも上側に存在し、ゲート電極に正電圧が印加されると第1層と第2層との接合界面近傍にポテンシャル井戸が発生するとともに、その電位レベルがフェルミ準位よりも下側に存在して、ポテンシャル井戸に2DEG(2 Dimensional Electron Gas:2次元電子ガス)が発生することで、ノーマリオフで動作する。

ここで、表面層の表面側に形成されているゲート電極は、表面層の表面側に直接的(典型的にはショットキー接続)、又は間接的(典型的には絶縁材を介在させて対向させる)に形成することができる。

上記の製造方法を採用すると、表面層から第2層に空乏層が伸びることでノーマリオフが実現され易い半導体装置を得ることができる。

III-V族化合物半導体は、窒化ガリウム(GaN)系化合物であるのが好ましい。窒化ガリウム系化合物は、そのバンドギャップが大きいために、高温動作可能な高周波デバイスを実現し得る。窒化ガリウム系化合物は、III-V族化合物半導体であることから、大出力で高耐圧である特性を備えている。

(第1実施例) 図1に第1実施例の半導体装置の要部断面図を模式的に示す。

サファイア(Al2O3)からなる基板22上に、窒化ガリウム(GaN)からなるバッファ層24が形成されている。基板22には、サファイアに代えて炭化シリコン(SiC)や窒化ガリウム(GaN)を利用してもよい。バッファ層24上に、p−GaN層32(第1層の一例)と、SI(Semi Insulated)−GaN層62(中間層の一例)と、AlGaN層34(第2層の一例)が積層されている。

SI(Semi Insulated)−GaN層62は、p−GaN層32とAlGaN層34との間に介在している。p−GaN層32には、マグネシウム(Mg)がドーピングされている。AlGaN層34は、その半導体結晶にアルミニウム(Al)を含有しており、p−GaN層32やSI−GaN層62よりもバンドギャップが大きい。

ニッケル(Ni)と金(Au)の積層構造からなるゲート電極44が、AlGaN層34の表面側の紙面中央に直接的にショットキー接触して形成されている。ゲート電極44を挟んだ紙面左右の位置関係に、チタン(Ti)とアルミニウム(Al)の積層構造からなるドレイン電極42とソース電極46が、AlGaN層34に対してオーミック接触して形成されている。SI−GaN層62は実質的に真性半導体の層で形成されている。

図2(a)は、ゲート電極44に電圧が印加されていない状態であり、図2(b)は、ゲート電極44に正電圧が印加されている状態である。

図2(a)に示すように、AlGaN層34のバンドギャップがp−GaN層32やSI−GaN層62よりも大きいことから、そのバンドギャップ差に基づいて、AlGaN層34とSI−GaN層62の接合界面のうちのSI−GaN層62側に、ポテンシャル井戸52が形成されている。このポテンシャル井戸52の電位レベルは、ゲート電極44が0Vのときはフェルミ準位(EF)よりも上側に存在しており、2DEGが発生していない。したがって、ゲート電極44が0Vのときは、この半導体装置のドレイン電極42とソース電極46間に電流が流れない。即ち、ノーマリオフとして作動する。

このとき、2DEGの電子は、不純物濃度が少ないSI−GaN層62に沿って移動する。したがって、電子が不純物によって散乱される確率は小さく、電子の移動度の大きい状態が実現される。

AlGaN層34には、n型不純物としてシリコン(Si)をドーピングしておくことが好ましい。AlGaN層34がn型であると、電子供給層として機能することから、オン抵抗をさらに低減させることができる。もっとも、AlGaN層34はp型でなければよく、SI(Semi Insulated)であってもよい。

まずサファイア基板22を準備する。このサファイア基板22上に、低温下で有機金属気相エピタキシャル(MOCVD)法を用いて、バッファ層24を約50nmの膜厚で形成する。このとき、ガリウム原料としてトリメチルガリウム(TMGa)、窒素原料としてアンモニアガス(NH3)を好適に利用することができる。

次に、このバッファ層24上に有機金属気相エピタキシャル法を用いて、p−GaN層32を約0.5μmの膜厚で形成する。このとき、ガリウム原料としてトリメチルガリウム(TMGa)、窒素原料としてアンモニアガス(NH3)、ドーパント材料としてシクロペンタジエニルマグネシウム(CP2Mg)を好適に利用することができる。

次に、p−GaN層32上に有機金属気相エピタキシャル法を用いて、SI−GaN層62を約10nm(好ましくは5〜15nm)の膜厚で形成する。このとき、ガリウム原料としてトリメチルガリウム(TMGa)、窒素原料としてアンモニアガス(NH3)を好適に利用することができる。また、このSI−GaN層62の不純物濃度が1×1017cm-3以下となるように形成するのが好ましい。このSI−GaN層62の膜厚は、形成されるポテンシャル井戸の範囲を充足していれば十分である。ポテンシャル井戸の幅は、利用される材料などによって変動するが、SI−GaN層62の膜厚は5〜15nmの範囲内であるのが好ましい。

次に、このSI−GaN層62上に有機金属気相エピタキシャル法を用いて、AlGaN層34を約25nmの膜厚で形成する。このとき、アルミニウム原料としてトリメチルアルミニウム(TMAl)、ガリウム原料としてトリメチルガリウム(TMGa)、窒素原料としてアンモニアガス(NH3)を好適に利用することができる。なお、このAlGaN層34の成膜過程で、n型不純物としてモノシラン(SiH4)を同時に利用し、AlGaN層34にn型不純物をドーピングしてもよい。

まず、AlGaN層34上にチタン(Ti)とアルミニウム(Al)を順に蒸着する。その後に、フォト工程とエッチング技術を利用してドレイン電極42とソース電極46をパターニングする。パターニングした後に、RTA(Rapid Thermal Anneal)法によって550℃で30秒の熱処理を実施する。これにより、AlGaN層34に対するドレイン電極42とソース電極46の接触抵抗が低減され、オーミック接触が実現される。

次に、リフトオフ法を利用してゲート電極44を形成する。即ち、ゲート電極44を形成したい場所以外にレジスト膜を成膜した後に、ニッケル(Ni)と金(Au)を順に蒸着する。その後に、レジスト膜とともにそのレジスト膜上に形成されているニッケル(Ni)と金(Au)を剥離する。これにより、所望の位置関係にゲート電極44が形成される。

上記の工程を経て、第1実施例の半導体装置を形成することができる。

サファイア(Al2O3)の基板122上に、窒化ガリウム(GaN)からなるバッファ層124が形成されている。基板122には、サファイアに代えて炭化シリコン(SiC)や窒化ガリウム(GaN)を利用してもよい。バッファ層124上に、p−GaN層132(第1層の一例)と、n−AlGaN層34(第2層の一例)が積層されている。

n−AlGaN層134にはシリコン(Si)がドーピングされている。なお、このn−AlGaN層134は、その半導体結晶にアルミニウム(Al)を含有しており、p−GaN層132よりもバンドギャップが大きい。

ニッケル(Ni)と金(Au)の積層構造からなるゲート電極144が、n−AlGaN層34の表面側の紙面中央に直接的にショットキー接触して形成されている。このゲート電極144を挟んだ紙面左右の位置関係に、チタン(Ti)とアルミニウム(Al)の積層構造からなるドレイン電極142とソース電極146が、オーミック接触して形成されている。

一方、よく知られているように、n−AlGaN層134は、GaN層132よりも小さな格子定数であることから、格子不整合によりn−AlGaN層134には引張り歪みが生じている。この引張り歪みに基づいて、n−AlGaN層134内には成長方向と逆方向にピエゾ分極電界が発生している。即ち、n−AlGaN層134のピエゾ分極電界は、GaN層132との接合界面に向かう方向(この例では紙面下方向)に発生している。第2実施例では、ピエゾ分極電界と自発分極電界の向きが逆向きで構成されている。

したがって、本実施例のように、自発分極電界がピエゾ分極電界と逆方向となるように構成されている場合、この両者を重畳した分極電界の方向は自発分極電界の方向と一致する。即ち、n−AlGaN層134内の分極電界の方向は、GaN層132との接合界面から離れる方向(この例では紙面上方向)に発生している。

まず第1に、従来のこの種の半導体装置では、GaN層132を形成する場合に有機金属気相エピタキシャル(MOCVD)法を用いて形成していた。有機金属気相エピタキシャル(MOCVD)法を用いてGaN層132を形成すると、その成長は必ずGa面で終了する。したがって、その上方に形成されるn−AlGaN層134は、N面から成長が始まるので、必然的に自発分極電界はGaN層132との接合界面の方向に向かって発生していた。

第2に従来の技術思想では、自発分極電界とピエゾ分極電界の方向を揃え、ともにGaN層132との接合界面の方向に向かって発生させることで、その界面近傍に形成されるポテンシャル井戸を深くし、2DEGの密度を向上させようとする傾向にあった。これらの理由から、従来のこの種の半導体装置では、自発分極電界がGaN層132との接合界面の方向に向かって発生していたのである。

しかしながら、この構成を採用すると、半導体装置をノーマリオフとして機能させる場合にその動作が不安定になるという問題がある。本実施例では、従来採用していた自発分極電界とピエゾ分極電界の配置関係とは異なる配置関係を敢えて採用することによって、安定的なノーマリオフ動作をする半導体装置の実現に成功している。

図4(a)は、ゲート電極144に電圧が印加されていない状態であり、図4(b)は、ゲート電極144に正電圧が印加されている状態である。

図4(a)に示すように、n−AlGaN層134のバンドギャップがp−GaN層132よりも大きいことから、この両層間の接合界面では、フェルミ準位を合わせるようにエネルギーバンドが曲げられる。本実施例では、n−AlGaN層134内のエネルギーバンドが、ゲート電極144側からGaN層132との接合界面に向かって上方向に傾斜して形成されていることが分かる。これは、n−AlGaN層134内の分極電界の方向がGaN層132との接合界面から離れる方向に発生していることに起因している。これにより、n−AlGaN層134内からGaN層132との接合界面近傍に向けて電子キャリアが供給される現象の発生が抑制される。したがって、この接合界面近傍に2DEGが発生することができないために、ゲート電極144が0Vのときは、ドレイン電極142とソース電極146間に電流が流れない。即ち、ノーマリオフとして作動する。

同様に、p−GaN層132が実質的に不純物を含有していない真性半導体の層で形成されていてもよい。オン抵抗の小さい半導体装置を実現することができる。

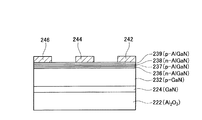

サファイア(Al2O3)の基板222上に、窒化ガリウム(GaN)からなるバッファ層224が形成されている。基板222には、サファイアに代えて炭化シリコン(SiC)や窒化ガリウム(GaN)を利用してもよい。バッファ層24上に、p−GaN層32(第1層の一例)と、n−AlGaN層34(第2層の一例)と、p−AlGaN層235(表面層の一例)が積層されている。

p−GaN層232とp−AlGaN層235には、マグネシウム(Mg)がドーピングされている。p−AlGaN層235とn−AlGaN層233は、その半導体結晶にアルミニウム(Al)を含有しており、p−GaN層232よりもバンドギャップが大きい。

ニッケル(Ni)と金(Au)の積層構造からなるゲート電極244が、p−AlGaN層235の表面側の紙面中央に直接的にショットキー接触して形成されている。このゲート電極244を挟んだ紙面左右の位置関係に、チタン(Ti)とアルミニウム(Al)の積層構造からなるドレイン電極242とソース電極246が、オーミック接触して形成されている。

なお、p−GaN層232は、実質的に不純物を含有していない真性半導体の層で形成されていてもよい。この場合、この層に沿って移動する2DEGに対する不純物散乱が抑制されることから、2DEGの移動度を大きくすることができる。

図6(a)は、ゲート電極244に電圧が印加されていない状態であり、図5(b)は、ゲート電極244に正電圧が印加されている状態である。

図6(a)に示すように、ゲート電極244に電圧が印加されていない場合、n−AlGaN層233内に対して、p−GaN層232とp−AlGaN層235の両方から空乏層が伸びて形成される。そのため、図6(a)中のn−AlGaN層233内のエネルギーバンドに示されるように、そのエネルギーバンドは傾斜するとともに、伝導体の下限はフェルミ準位よりも上側に存在することになる。したがって、p−GaN層232との接合界面近傍に2DEGが発生することができないために、ゲート電極244が0Vのときは、この半導体装置のドレイン電極242とソース電極246間に電流が流れない。即ち、ノーマリオフとして作動する。

なお、このn−AlGaN層233が実質的に完全空乏化されるためには、次の関係式を満たすようにn−AlGaN層233とp−AlGaN層235が設定されているのが好ましい。

Xd<(2εNdVd/(qNa(Na+Nd)))1/2 ・・・・(1)

Xa<(2εNaVd/(qNd(Na+Nd)))1/2 ・・・・(2)

ここで、Xdはn−AlGaN層233の膜厚であり、Ndはn−AlGaN層233のドナー密度であり、Xaはp−AlGaN層235の膜厚であり、Naはp−AlGaN層235のアクセプタ密度であり、Vdはn−AlGaN層233とp−AlGaN層235で形成される拡散電位であり、εはGaN半導体結晶の誘電率であり、qは電子電荷の絶対値である。

図5の半導体装置と対比すると、本変形例の特徴が明瞭に理解できる。本変形例では、第3実施例のn−AlGaN層233(第2層の一例)とp−AlGaN層235(表面層)に相当するn−AlGaN層236、238(第2層の一例)とp−AlGaN層237、239(上部層)の繰返しが積層して形成されている。具体的には、第1のn−AlGaN層236上に第1のp−AlGaN層237が形成され、さらにその上に第2のn−AlGaN層238と第2のp−AlGaN層239が積層して形成されている。

また、ノーマリオフを実現する範囲内で、積層構造内の第2層の不純物濃度を比較的高く構成することが可能となるので、電子供給能力が増大し、オン抵抗を低減し得る。

また、積層構造を採用することで、ゲート電極244に正電圧を印加した場合でも、積層構造内のpn接合が逆バイアスされて、ゲート電極244からの電流の流入を防止することができる。半導体装置の安定的な動作を実現し易い。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

24:バッファ層

32:p−GaN層(第1層の一例)

34:AlGaN層(第2層の一例)

42:ドレイン電極

44:ゲート電極

46:ソース電極

62:SI−GaN層(中間層の一例)

Claims (4)

- 第1層と第2層と表面層がこの順に積層され、表面層の表面側にゲート電極が形成されているノーマリオフで動作する半導体装置であり、

第1層は、p型又は真性の窒化ガリウムで構成されており、

第2層は、n型の窒化アルミニウムガリウムで構成されており、

表面層は、p型のGaN系化合物半導体で構成されており、

ゲート電極に電圧が印加されていない場合、第2層及び表面層が空乏化され、第2層の伝導体の下限がフェルミ準位よりも上側に存在し、ゲート電極に正電圧が印加されると第1層と第2層との接合界面近傍にポテンシャル井戸が発生するとともに、その電位レベルがフェルミ準位よりも下側に存在して、ポテンシャル井戸に2DEG(2 Dimensional Electron Gas:2次元電子ガス)が発生することで、ノーマリオフで動作するようにしたことを特徴とする半導体装置。 - 表面層は、p型の窒化アルミニウムガリウムで構成されている請求項1に記載の半導体装置。

- 第1層と第2層と表面層がこの順に積層され、表面層の表面側にゲート電極が形成されているとともに、ゲート電極に電圧が印加されていない場合、第2層及び表面層が空乏化され、第2層の伝導体の下限がフェルミ準位よりも上側に存在し、ゲート電極に正電圧が印加されると第1層と第2層との接合界面近傍にポテンシャル井戸が発生するとともに、その電位レベルがフェルミ準位よりも下側に存在して、ポテンシャル井戸に2DEG(2 Dimensional Electron Gas:2次元電子ガス)が発生することで、ノーマリオフで動作するようにした半導体装置の製造方法であり、

p型又は真性の窒化ガリウムからなる第1層上に、n型の窒化アルミニウムガリウムからなる第2層をエピタキシャル成長させる第2層成長工程と、

その第2層上に、p型のGaN系化合物半導体からなる表面層をエピタキシャル成長させる表面層成長工程と、

その表面層の表面側にゲート電極を形成するゲート電極形成工程を有することを特徴とする製造方法。 - 表面層成長工程では、p型の窒化アルミニウムガリウムからなる表面層をエピタキシャル成長させる請求項3に記載の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013018260A JP6096523B2 (ja) | 2013-02-01 | 2013-02-01 | 半導体装置とその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013018260A JP6096523B2 (ja) | 2013-02-01 | 2013-02-01 | 半導体装置とその製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010050058A Division JP5221577B2 (ja) | 2010-03-08 | 2010-03-08 | 半導体装置とその製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015092719A Division JP6185508B2 (ja) | 2015-04-30 | 2015-04-30 | 半導体装置とその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013123074A JP2013123074A (ja) | 2013-06-20 |

| JP2013123074A5 JP2013123074A5 (ja) | 2013-12-05 |

| JP6096523B2 true JP6096523B2 (ja) | 2017-03-15 |

Family

ID=48774840

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013018260A Active JP6096523B2 (ja) | 2013-02-01 | 2013-02-01 | 半導体装置とその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6096523B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2017126610A (ja) | 2016-01-12 | 2017-07-20 | トヨタ自動車株式会社 | スイッチング素子 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0624208B2 (ja) * | 1982-07-29 | 1994-03-30 | 日本電気株式会社 | 半導体装置 |

| JPH0415929A (ja) * | 1990-05-10 | 1992-01-21 | Fujitsu Ltd | 高電子移動度トランジスタ |

| JP2000068498A (ja) * | 1998-08-21 | 2000-03-03 | Nippon Telegr & Teleph Corp <Ntt> | 絶縁性窒化物膜およびそれを用いた半導体装置 |

| JP4906023B2 (ja) * | 2001-08-14 | 2012-03-28 | 古河電気工業株式会社 | GaN系半導体装置 |

| JP2004273486A (ja) * | 2003-03-05 | 2004-09-30 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP4041075B2 (ja) * | 2004-02-27 | 2008-01-30 | 株式会社東芝 | 半導体装置 |

-

2013

- 2013-02-01 JP JP2013018260A patent/JP6096523B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013123074A (ja) | 2013-06-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4744109B2 (ja) | 半導体装置とその製造方法 | |

| JP6174874B2 (ja) | 半導体装置 | |

| JP6371986B2 (ja) | 窒化物半導体構造物 | |

| TWI462293B (zh) | 增強型電晶體及其形成方法 | |

| US8410525B2 (en) | Compound semiconductor substrate and device therewith | |

| US20140110759A1 (en) | Semiconductor device | |

| JP6035721B2 (ja) | 半導体装置の製造方法 | |

| JP2007220895A (ja) | 窒化物半導体装置およびその製造方法 | |

| JP2010135640A (ja) | 電界効果トランジスタ | |

| JP5997234B2 (ja) | 半導体装置、電界効果トランジスタおよび電子装置 | |

| JP4474292B2 (ja) | 半導体装置 | |

| CN110875387A (zh) | 半导体器件和用于形成半导体器件的方法 | |

| JP2011210785A (ja) | 電界効果トランジスタ、およびその製造方法 | |

| KR100860070B1 (ko) | 트랜지스터 | |

| JP6096523B2 (ja) | 半導体装置とその製造方法 | |

| JP2015056413A (ja) | 窒化物半導体装置 | |

| JP7074282B2 (ja) | 高電子移動度トランジスタ | |

| JP5221577B2 (ja) | 半導体装置とその製造方法 | |

| JP6185508B2 (ja) | 半導体装置とその製造方法 | |

| JP7069486B2 (ja) | 高電子移動度トランジスタ | |

| JP5285252B2 (ja) | 窒化物半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131023 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140418 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140422 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140623 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20140623 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20150203 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150430 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20150512 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20150731 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161121 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170216 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6096523 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |