JP6077786B2 - 撮像装置 - Google Patents

撮像装置 Download PDFInfo

- Publication number

- JP6077786B2 JP6077786B2 JP2012183583A JP2012183583A JP6077786B2 JP 6077786 B2 JP6077786 B2 JP 6077786B2 JP 2012183583 A JP2012183583 A JP 2012183583A JP 2012183583 A JP2012183583 A JP 2012183583A JP 6077786 B2 JP6077786 B2 JP 6077786B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- node

- potential

- charge

- pixel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000003384 imaging method Methods 0.000 title claims description 52

- 239000003990 capacitor Substances 0.000 claims description 50

- 238000009825 accumulation Methods 0.000 claims description 29

- 229920006395 saturated elastomer Polymers 0.000 claims description 12

- 238000006243 chemical reaction Methods 0.000 claims description 8

- 239000004065 semiconductor Substances 0.000 description 58

- 238000000034 method Methods 0.000 description 23

- 238000010586 diagram Methods 0.000 description 14

- 239000012535 impurity Substances 0.000 description 9

- 230000006870 function Effects 0.000 description 7

- 230000035945 sensitivity Effects 0.000 description 7

- 239000000758 substrate Substances 0.000 description 5

- 230000007423 decrease Effects 0.000 description 4

- 239000000470 constituent Substances 0.000 description 3

- 230000000694 effects Effects 0.000 description 2

- 238000002474 experimental method Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14636—Interconnect structures

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/57—Control of the dynamic range

- H04N25/59—Control of the dynamic range by controlling the amount of charge storable in the pixel, e.g. modification of the charge conversion ratio of the floating node capacitance

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

- H04N25/771—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components comprising storage means other than floating diffusion

Description

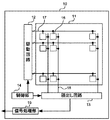

図1は本発明の第1実施形態に係る撮像装置10の構成例を説明する。撮像装置10は、画素アレイ11、駆動回路12、読出し回路13、制御部14及び信号処理部15を備えうる。画素アレイ11には、入射光に応じた信号を出力する画素16がアレイ状に配置される。駆動回路12は制御部14からの指示に従って、駆動線17を介して行ごとに画素16に制御信号を供給する。読出し回路13は制御部14からの指示に従って、画素16から信号線18に出力された信号を列ごとに読み出し、信号処理部15に出力する。信号処理部15はそれぞれの画素16から出力された信号に基づいて各画素16の画素値を決定する。

Vres−Vcur=Q/Cf

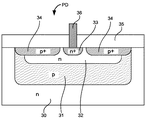

このように、半導体領域33が飽和するまでの間、ノードNDの電位変化量(すなわち、Vres−Vcur)は蓄積された電荷量Qに対して比例して変化する。

Vres−Vcur=Q/(Cf+Cs)

このようにノードNDにコンデンサ23の容量を付加することによって、図4(c)に示されるように、入射光の照度が高く、高ゲイン状態において線形関係を満たさないような電荷量Qであっても、低ゲイン状態で測定した場合には線形関係を満たしうる。

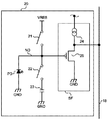

続いて、図7を参照して本発明の第2実施形態について説明する。図7(a)は本実施形態の画素70の構成を説明する回路図であり、図7(b)はこの画素70を含む撮像装置10の制御方法の一例を説明するタイミングチャートである。本実施形態では、図1の撮像装置10の画素16として、図7(a)に示される画素70を用いる。図2の画素20と図7の画素70とで共通する構成要素には同一の参照符号を付して重複する説明を省略する。

続いて、図8を参照して本発明の第3実施形態について説明する。図8(a)は本実施形態の画素80の構成を説明する回路図であり、図8(b)はこの画素80を含む撮像装置10の制御方法の一例を説明するタイミングチャートである。本実施形態では、図1の撮像装置10の画素16として、図8(a)に示される画素80を用いる。図7の画素70と図8の画素80とで共通する構成要素には同一の参照符号を付して重複する説明を省略する。

続いて、図9、図10を参照して本発明の第4実施形態について説明する。上述の第1実施形態において、蓄積された電荷量Qが多い場合に、低ゲイン状態においてもノードNDの電位が飽和電圧Vsatを超えてしまい、低ゲイン信号の線形性を維持できないことがある。このような場合に、コンデンサ23の容量を大きくして線形性を維持しようとすると、高ゲイン状態において飽和電圧Vsatを若干上回るような電荷量Qを十分な感度で測定できなくなる。そこで、本実施形態では、2段階に分けてノードNDに容量値を付加する。図9は本実施形態の画素90の構成を説明する回路図である。本実施形態では、図1の撮像装置10の画素16として、図9に示される画素90を用いる。図8の画素80と図9の画素90とで共通する構成要素には同一の参照符号を付して重複する説明を省略する。

続いて、図11を参照して本発明の第5実施形態について説明する。図11(a)は本実施形態の画素110の構成を説明する回路図であり、図11(b)はこの画素110を含む撮像装置10の制御方法の一例を説明するタイミングチャートである。本実施形態では、図1の撮像装置10の画素16として、図11(a)に示される画素110を用いる。図2の画素20と図11の画素110とで共通する構成要素には同一の参照符号を付して重複する説明を省略する。画素110は、スイッチ21、22及びコンデンサ23の代わりに、MOSトランジスタ(MOSFET)TR、TCを備える点で画素20とは異なる。MOSトランジスタTR、TCは電圧源VRESとノードNDとの間に直列に接続される。

続いて、図12を参照して本発明の第6実施形態について説明する。図12(a)は本実施形態の画素120の構成を説明する回路図であり、図12(b)はこの画素120を含む撮像装置10の制御方法の一例を説明するタイミングチャートである。本実施形態では、図1の撮像装置10の画素16として、図12(a)に示される画素120を用いる。図9の画素90と図12の画素120とで共通する構成要素には同一の参照符号を付して重複する説明を省略する。本実施形態においても、上述の第4実施形態と同様に、2段階に分けてノードNDに容量値を付加する。画素120は、スイッチ21、22a、22b及びコンデンサ23a、23bの代わりに、MOSトランジスタTR、TCa、TCbを備える点で画素90とは異なる。MOSトランジスタTR、TCa、TCbは電圧源VRESとノードNDとの間に直列に接続される。

Claims (7)

- 複数の画素を有する撮像装置であって、

前記複数の画素のそれぞれは、

電荷蓄積領域を有する光電変換部と、

前記電荷蓄積領域に接続されたコンタクトプラグを含むノードの電位に基づいて信号を出力する出力部と、

前記ノードに容量を電気的に接続する接続部とを含み、

前記電荷蓄積領域は第1部分及び第2部分を含み、光電変換により発生した電荷は前記第1部分に先に蓄積され、前記第1部分が飽和した後に前記第2部分に蓄積され、

前記ノードに前記容量が電気的に接続された状態で前記第1部分と前記容量とに所定量の電荷が分散して蓄積されたことによる前記ノードの電位変化の量は、前記ノードに前記容量が電気的に接続されていない状態で前記第1部分に前記所定量の電荷が蓄積されたことによる前記ノードの電位変化の量よりも小さく、前記ノードに前記容量が電気的に接続されていない状態で前記第2部分に前記所定量の電荷が蓄積されたことによる前記ノードの電位変化の量よりも大きく、

前記出力部は、前記ノードに前記容量が電気的に接続されていない状態で前記電荷蓄積領域への信号電荷の蓄積が開始された後に、前記容量が電気的に接続される前の前記ノードの前記信号電荷に応じた電位に基づいて第1信号を出力し、その後に前記容量が電気的に接続された後の前記ノードの前記信号電荷に応じた電位に基づいて第2信号を出力することを特徴とする撮像装置。 - 前記コンタクトプラグは、前記第1部分に接続され、

前記第1部分は、前記第2部分に取り囲まれることを特徴とする請求項1に記載の撮像装置。 - 前記撮像装置は、前記出力部から出力された信号を用いて画素値を決定する処理部を更に有し、

前記処理部は、前記第1信号の値が所定の値よりも小さい場合に、前記第1信号に基づいて前記画素値を決定し、前記第1信号の値が前記所定の値よりも大きい場合に、前記第2信号に基づいて前記画素値を決定することを特徴とする請求項1又は2に記載の撮像装置。 - 前記所定の値は、前記第1部分が飽和した時点の前記ノードの電位に基づくことを特徴とする請求項3に記載の撮像装置。

- 前記複数の画素は、前記出力部から出力された前記第1信号を保持する第1保持部と、前記出力部から出力された前記第2信号を保持する第2保持部とを更に含むことを特徴とする請求項1乃至4の何れか1項に記載の撮像装置。

- 前記複数の画素のそれぞれは、

前記ノードの電位をリセット電圧に設定するリセット部と、

前記ノードの電位が前記リセット電圧に設定された状態で前記出力部が前記ノードの電位に基づいて出力する第3信号を保持する第3保持部とを更に含むことを特徴とする請求項5に記載の撮像装置。 - 前記容量が電気的に接続された状態の前記ノードの電位に基づいて前記第2信号を出力することを特徴とする請求項1乃至6の何れか1項に記載の撮像装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012183583A JP6077786B2 (ja) | 2012-08-22 | 2012-08-22 | 撮像装置 |

| US13/957,737 US9257460B2 (en) | 2012-08-22 | 2013-08-02 | Image capturing apparatus and control method therefor |

| US14/946,911 US9362326B2 (en) | 2012-08-22 | 2015-11-20 | Image capturing apparatus and control method therefor |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012183583A JP6077786B2 (ja) | 2012-08-22 | 2012-08-22 | 撮像装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014042167A JP2014042167A (ja) | 2014-03-06 |

| JP2014042167A5 JP2014042167A5 (ja) | 2015-06-25 |

| JP6077786B2 true JP6077786B2 (ja) | 2017-02-08 |

Family

ID=50147149

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012183583A Active JP6077786B2 (ja) | 2012-08-22 | 2012-08-22 | 撮像装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US9257460B2 (ja) |

| JP (1) | JP6077786B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6376785B2 (ja) * | 2014-03-14 | 2018-08-22 | キヤノン株式会社 | 撮像装置、および、撮像システム |

| JP6385192B2 (ja) | 2014-08-14 | 2018-09-05 | キヤノン株式会社 | 撮像装置、撮像システム及び撮像システムの駆動方法 |

| JP6579741B2 (ja) * | 2014-10-09 | 2019-09-25 | キヤノン株式会社 | 撮像装置及び放射線撮像システム |

| JP2016139660A (ja) * | 2015-01-26 | 2016-08-04 | 株式会社東芝 | 固体撮像装置 |

| US10136868B2 (en) * | 2015-09-03 | 2018-11-27 | General Electric Company | Fast dual energy for general radiography |

| JP7129199B2 (ja) * | 2018-04-11 | 2022-09-01 | キヤノン株式会社 | 光検出装置、光検出システム及び移動体 |

| US11658201B2 (en) * | 2021-08-25 | 2023-05-23 | Silead Inc. | Dual conversion gain image sensor pixels |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5903021A (en) | 1997-01-17 | 1999-05-11 | Eastman Kodak Company | Partially pinned photodiode for solid state image sensors |

| US6246436B1 (en) * | 1997-11-03 | 2001-06-12 | Agilent Technologies, Inc | Adjustable gain active pixel sensor |

| JP3592106B2 (ja) * | 1998-11-27 | 2004-11-24 | キヤノン株式会社 | 固体撮像装置およびカメラ |

| US6850278B1 (en) | 1998-11-27 | 2005-02-01 | Canon Kabushiki Kaisha | Solid-state image pickup apparatus |

| JP3584196B2 (ja) * | 1999-02-25 | 2004-11-04 | キヤノン株式会社 | 受光素子及びそれを有する光電変換装置 |

| TW484235B (en) | 1999-02-25 | 2002-04-21 | Canon Kk | Light-receiving element and photoelectric conversion device |

| US6204524B1 (en) * | 1999-07-14 | 2001-03-20 | Micron Technology, Inc. | CMOS imager with storage capacitor |

| JP3558589B2 (ja) | 2000-06-14 | 2004-08-25 | Necエレクトロニクス株式会社 | Mos型イメージセンサ及びその駆動方法 |

| US6855937B2 (en) | 2001-05-18 | 2005-02-15 | Canon Kabushiki Kaisha | Image pickup apparatus |

| JP4724313B2 (ja) * | 2001-05-18 | 2011-07-13 | キヤノン株式会社 | 撮像装置、放射線撮像装置及びそれを用いた放射線撮像システム |

| US7385166B2 (en) * | 2003-10-30 | 2008-06-10 | Micron Technology, Inc. | In-pixel kTC noise suppression using circuit techniques |

| JP5066704B2 (ja) * | 2005-02-04 | 2012-11-07 | 国立大学法人東北大学 | 固体撮像装置、および固体撮像装置の動作方法 |

| US7701493B2 (en) * | 2005-02-28 | 2010-04-20 | Micron Technology, Inc. | Imager row-wise noise correction |

| JP2006262387A (ja) * | 2005-03-18 | 2006-09-28 | Canon Inc | 固体撮像装置及びカメラ |

| EP2037667B1 (en) | 2007-09-14 | 2017-08-23 | Canon Kabushiki Kaisha | Image sensing apparatus and imaging system |

| JP2009177797A (ja) * | 2007-12-26 | 2009-08-06 | Panasonic Corp | 固体撮像装置及びその駆動方法 |

| DE112011100842T5 (de) * | 2010-03-08 | 2013-01-17 | Semiconductor Energy Laboratory Co., Ltd. | Halbleiterbauelement und Verfahren zu dessen Herstellung |

| US9200956B2 (en) * | 2010-06-27 | 2015-12-01 | Sri International | Readout transistor circuits for CMOS imagers |

| JP5576754B2 (ja) * | 2010-09-29 | 2014-08-20 | キヤノン株式会社 | 放射線撮像装置 |

| JP2015109503A (ja) * | 2013-12-03 | 2015-06-11 | ソニー株式会社 | イメージセンサおよびイメージセンサの動作方法、撮像装置、電子機器、並びにプログラム |

-

2012

- 2012-08-22 JP JP2012183583A patent/JP6077786B2/ja active Active

-

2013

- 2013-08-02 US US13/957,737 patent/US9257460B2/en active Active

-

2015

- 2015-11-20 US US14/946,911 patent/US9362326B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US9362326B2 (en) | 2016-06-07 |

| US20140054445A1 (en) | 2014-02-27 |

| US20160079298A1 (en) | 2016-03-17 |

| US9257460B2 (en) | 2016-02-09 |

| JP2014042167A (ja) | 2014-03-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6077786B2 (ja) | 撮像装置 | |

| JP6598791B2 (ja) | 暗電流低減および低電力消費を伴う撮像のための方法 | |

| US10332928B2 (en) | Solid-state imaging device, method for manufacturing solid-state imaging device, and electronic apparatus | |

| JP2009506575A (ja) | 4方向共有のピクセル上に2方向共有の蓄積ゲートを設ける方法及び装置 | |

| US10720467B2 (en) | Optical sensor and signal readout method therefor, and solid-state image pickup device and signal readout method therefor | |

| JP5995457B2 (ja) | 撮像装置、撮像システム、および撮像装置の駆動方法。 | |

| JP6406912B2 (ja) | 撮像装置並びにその駆動方法 | |

| JP2009506725A (ja) | 4方向共有のピクセル上に2方向共有の蓄積ゲートを設ける方法及び装置 | |

| JP6004665B2 (ja) | 撮像装置、および撮像システム。 | |

| US9425225B2 (en) | Solid-state imaging device | |

| CN110164888B (zh) | 像素电路 | |

| JP3793205B2 (ja) | 電荷検出装置および固体撮像装置 | |

| JP5814818B2 (ja) | 固体撮像装置 | |

| US20150124135A1 (en) | Sharp pixel with fixed conversion gain | |

| JP6700656B2 (ja) | 撮像装置 | |

| US9893103B2 (en) | Solid-state image sensor | |

| US20130070134A1 (en) | Low Noise CMOS Pixel Array | |

| KR101340839B1 (ko) | 고감도 cmos 영상 센서 장치 | |

| KR101211085B1 (ko) | 공유 포토 다이오드 이미지 센서 | |

| JP2009168613A (ja) | 赤外線固体撮像素子 | |

| JP2006074063A (ja) | 電荷検出装置の製造方法 | |

| de Moraes Cruz et al. | Simple Technique to Reduce FPN in a linear-logarithm APS | |

| JP5570628B2 (ja) | 固体撮像装置 | |

| JP2014154562A (ja) | 固体撮像装置、その製造方法、及び撮像システム | |

| JP2018201046A (ja) | 撮像装置並びにその駆動方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150428 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150428 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160212 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160412 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160801 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160927 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20161216 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170113 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 6077786 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |