JP5945672B2 - 遊技機制御用マイコンチップ - Google Patents

遊技機制御用マイコンチップ Download PDFInfo

- Publication number

- JP5945672B2 JP5945672B2 JP2011120356A JP2011120356A JP5945672B2 JP 5945672 B2 JP5945672 B2 JP 5945672B2 JP 2011120356 A JP2011120356 A JP 2011120356A JP 2011120356 A JP2011120356 A JP 2011120356A JP 5945672 B2 JP5945672 B2 JP 5945672B2

- Authority

- JP

- Japan

- Prior art keywords

- program

- mode

- rom

- built

- fraud

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Description

特許文献1では、遊技機制御用マイコンチップに外部装置から入力される正規の外部入力信号に関するインピーダンス値の許容範囲を設定して該許容範囲を前記マイコンチップの内蔵ROMに格納しておき、不正対策として、外部入力信号の入力ごとにそのインピーダンス値を確認して、インピーダンス値が前記許容範囲外であれば不正行為とみなすことが行われている。

そこで本発明は、不正対策プログラムによって遊技制御用のユーザープログラムが制約されることなく、興趣の豊かな遊技を実現することができる遊技機制御用マイコンチップを提供することを課題としてなされたものである。

遊技機制御用マイコンチップにおいて、

不正対策プログラムおよび該プログラムに関連する情報を記憶する第1の内蔵ROMと、

遊技制御用のユーザープログラムおよび該プログラムに関連する情報を記憶する第2の内蔵ROMと、

前記不正対策プログラムに基づく制御又は前記ユーザープログラムに基づく制御を実行する中央制御装置(CPU)と、を具備し、

前記不正対策プログラムは、前記ユーザープログラムと一連に実行され、不正行為を検出するためのスイッチの検出状況を監視して不正対策を施す構成とし、

かつ、リセット信号が入力されるシステムリセット端子と、

モード設定信号が入力されるモード設定入力端子と、

前記システムリセット端子へのリセット信号の入力に応じてシステムリセットを実行するシステムリセット手段と、

前記システムリセットの実行後、前記第1の内蔵ROMへの前記不正対策プログラムの書込みを実行する第1のプログラムモード、前記第2の内蔵ROMへの前記ユーザープログラムの書込みを実行する第2のプログラムモード、および前記第2の内蔵ROMに書込まれた前記ユーザープログラムの異常の有無をチェックするセキュリティモードのいずれかに移行せしめるモード移行手段と、

前記不正対策プログラムが前記第1の内蔵ROMに書込まれていることを示す第1の書込制限手段と、

前記ユーザープログラムが前記第2の内蔵ROMに書込まれていることを示す第2の書込制限手段と、を具備し、

前記モード移行手段は、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力があり、かつ、前記第1の内蔵ROMに前記不正対策プログラムが書込まれていない状態であることが示されていることを条件に、前記第1のプログラムモードへと移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力があり、前記第1の内蔵ROMに前記不正対策プログラムが書込まれている状態であることが示される一方、前記第2の内蔵ROMに前記ユーザープログラムが書込まれていない状態が示されていることを条件に、前記第2のプログラムモードへと移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力があったにも拘らず、前記第1及び第2の書込制限手段により前記第1及び第2の内蔵ROMに前記各プログラムが書込まれている状態であることが示されていることを条件に、前記セキュリティモードに移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力がないことを条件に、前記セキュリティモードに移行せしめるように構成され、

該セキュリティモードで異常がなければ、前記不正対策プログラムと前記ユーザープログラムに基づく制御を実行するユーザーモードに移行せしめ、前記セキュリティモードで異常があれば、前記中央制御装置の処理を停止せしめる構成とする。

このようにマイコンチップメーカーにて不正対策プログラムを書込むようにすれば、遊技機メーカーにおいては不正対策プログラムを改変することができず、不正対策プログラムを遊技機制御用マイコンチップの機能の一部とすることが可能となる。よってチップの機能の一部となった不正対策プログラムはプログラム記憶用の前記規定の記憶容量から除外することができ、その分、ユーザープログラムの記憶容量を増加することができる。したがって、ユーザープログラムのプログラム内容を増やすことができ、遊技内容が豊富で興趣の豊かな遊技を実現することができる。

尚、遊技機制御用マイコンチップは、専用のROMライタにより不正対策およびユーザープログラムが第1又は第2の内蔵ROMに書込まれる。前記ROMライタにマイコンチップをセットすることで、モード設定入力端子にROMライタよりモード設定信号が入力され、第1又は第2のプログラムモードへ移行させるようにしてある。マイコンチップを遊技機に実装した場合は、モード設定入力端子をプルダウンしてモード設定信号が入力しないようにすることが望ましい。

また、第1および第2のプログラムモードにおいては、不正対策又はユーザープログラムの第1、第2の各内蔵ROMへの書込み後に、正常に書込むことができたか確認するために、各内蔵ROMからプログラムを読出せることは勿論である。

遊技機制御用マイコンチップにおいて、

不正対策プログラムおよび該プログラムに関連する情報を記憶する第1の内蔵ROMと、

遊技制御用のユーザープログラムおよび該プログラムに関連する情報を記憶する第2の内蔵ROMと、

前記不正対策プログラムに基づく制御又は前記ユーザープログラムに基づく制御を実行する中央制御装置(CPU)と、を具備し、

前記不正対策プログラムは、前記ユーザープログラムと一連に実行され、不正行為を検出するためのスイッチの検出状況を監視して不正対策を施す構成とし、

かつ、リセット信号が入力されるシステムリセット端子と、

モード設定信号が入力されるモード設定入力端子と、

前記システムリセット端子へのリセット信号の入力に応じてシステムリセットを実行するシステムリセット手段と、

前記システムリセットの実行後、前記第1の内蔵ROMへの前記不正対策プログラムの書込みを実行する第1のプログラムモード、前記第2の内蔵ROMへの前記ユーザープログラムの書込みを実行する第2のプログラムモード、および前記第2の内蔵ROMに書込まれた前記ユーザープログラムの異常の有無をチェックするセキュリティモードのいずれかに移行せしめるモード移行手段と、

前記不正対策プログラムが前記第1の内蔵ROMに書込まれていることを示す第1の書込制限手段と、

前記ユーザープログラムが前記第2の内蔵ROMに書込まれていることを示す第2の書込制限手段と、を具備し、

前記モード移行手段は、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力があり、かつ、前記第1の内蔵ROMに前記不正対策プログラムが書込まれていない状態が示されていることを条件に、前記第1のプログラムモードへと移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力があり、前記第1の内蔵ROMに前記不正対策プログラムが書込まれている状態が示される一方、前記第2の内蔵ROMに前記ユーザープログラムが書込まれていない状態が示されていることを条件に、前記第2のプログラムモードへと移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力がなく、かつ、前記第2の内蔵ROMに前記ユーザープログラムが書込まれている状態が示されていることを条件に、前記セキュリティモードに移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力がなく、かつ、前記第2の内蔵ROMに前記ユーザープログラムが書込まれている状態が示されていないことを条件に、前記中央制御装置の処理を停止せしめるように構成され、

前記セキュリティモードで異常がなければ、前記不正対策プログラムと前記ユーザープログラムに基づく制御を実行するユーザーモードに移行せしめ、前記セキュリティモードで異常があれば、前記中央制御装置の処理を停止せしめる構成とする。

このようにマイコンチップメーカーにて不正対策プログラムを書込むようにすれば、遊技機メーカーにおいては不正対策プログラムを改変することができず、不正対策プログラムを遊技機制御用マイコンチップの機能の一部とすることが可能となる。よってチップの機能の一部となった不正対策プログラムはプログラム記憶用の前記規定の記憶容量から除外することができ、その分、ユーザープログラムの記憶容量を増加することができる。したがって、ユーザープログラムのプログラム内容を増やすことができ、遊技内容が豊富で興趣の豊かな遊技を実現することができる。

尚、遊技機制御用マイコンチップは、専用のROMライタにより不正対策およびユーザープログラムが第1又は第2の内蔵ROMに書込まれる。前記ROMライタにマイコンチップをセットすることで、モード設定入力端子にROMライタよりモード設定信号が入力され、第1又は第2のプログラムモードへ移行させるようにしてある。マイコンチップを遊技機に実装した場合は、モード設定入力端子をプルダウンしてモード設定信号が入力しないようにすることが望ましい。

また、第1および第2のプログラムモードにおいては、不正対策又はユーザープログラムの第1、第2の各内蔵ROMへの書込み後に、正常に書込むことができたか確認するために、各内蔵ROMからプログラムを読出せることは勿論である。

更に、前記セキュリティモード移行後に、該セキュリティモードで異常があれば、ユーザープログラムが異常のため中央制御装置の処理を停止することが望ましい。

更にまた、マイコンチップが遊技機に実装された状態であって、モード設定信号の入力がないときでもユーザープログラムが書込まれているか確認するので、ユーザープログラムに異常があれば(第2の内蔵ROMにユーザープログラムが書きこまれていない状態であれば)直ちにCPUの処理を停止して遊技を不能とする。よって、遊技者が遊技を開始してから遊技機に不具合が生じ、遊技者が被る損害を未然に防ぐことができる。

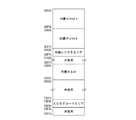

図1は遊技機制御用マイコンチップの概略ブロック図を示す。図1に示すように、遊技機制御用マイコンチップ(以下、マイコンチップという)1は、中央制御装置(CPU)2、第1の内蔵ROM(図には内蔵ROM1と示す)3A、第2の内蔵ROM(図には内蔵ROM2と示す)3B、内蔵RAM4、およびリセットコントローラ5等のデバイスを備え、これらのデバイスは相互に各種バス10にて接続され、プログラムやこれに関係する情報を含むデータの入出力がなされる。

第2の内蔵ROM3Bは、遊技機の制御を行なうユーザープログラムおよび該プログラムに関連する情報が格納された読出し専用の記憶デバイスであり、本ROMに格納するプログラムやこれに関する情報の書込みが一度だけ可能な構成である。

本実施形態では、第1および第2の内蔵ROMの記憶容量はいずれも8Kバイトに設定されている。

リセットコントローラ5には、マイコンチップ外部からのリセット信号が入力されるシステムリセット端子(図にはXSRSTと示す)6Aと、マイコンチップ外部からのモード設定信号が入力されるモード設定入力端子(図にはPRGと示す)6Bが接続されている。

またリセットコントローラ5には、CPU2が第1および第2の内蔵ROM3A,3B以外からのプログラムを実行することを禁止する指定エリア外走行禁止回路(IAT)5aや、CPU2の異常動作を監視するウォッチドグタイマ(WDT)5b等が設けられている。尚、リセットコントローラ5は特許請求の範囲に記載の「システムリセット手段」に相当する。

また7E00h番地から7FFFh番地は内蔵RAMに割当てられ、内蔵RAMは、不正対策プログラムにおけるワークエリアとして、更にユーザープログラムにおけるにワークエリアとして共通して使用される。

4000h番地から40FFh番地は内蔵レジスタエリアに、FDD0h番地からFDFBh番地はXCSデコードエリアに割当てられている。尚、4100h番地から7DFFh番地、FDFCh番地からFFFFh番地は未使用である。

マイコンチップ1は、電源が投入されると、「モード設定処理1」(図4)が実行され、専用のROMライタにより第1の内蔵ROMへ不正対策プログラムの書込みを行う第1のプログラムモード(図にはプログラムモード1と示す)、前記ROMライタにより第2の内蔵ROMへユーザープログラムの書込みを行う第2のプログラムモード(図にはプログラムモード2と示す)、ユーザープログラムに異常がないかチェックするセキュリティモード、不正対策プログラムおよびユーザープログラムを実行するユーザーモードのいずれかのモードへの設定がなされる。尚、モード設定処理1は特許請求の範囲に記載の「モード移行手段」に相当する。

モード設定端子にHレベルのモード設定信号の入力があれば(S20:yes)、第1の書込制限フラグ(図には書込制限フラグ1又は書込制限F1と示す)を確認する(S25)。第1の書込制限フラグは第1の内蔵ROMに不正対策プログラムが書込まれていると「1」がセットされるもので、この処理では第1の内蔵ROMに不正対策プログラムが書込まれていないことを確認し、第1の内蔵ROMへの不正対策プログラムの書込みを許可する。ここで、第1の書込制限フラグは第1の内蔵ROMに不正対策プログラムが書込まれていると「1」がセットされるものに限定されるものではなく、不正対策プログラムが書込まれていることを判断可能な何らかの情報であれば問題ない。また、第1のプログラムモードへ移行した直後にセットされても、第1のプログラムモードでの書込処理後にセットされる構成としても差し支えない。尚、第1の書込制限フラグは特許請求の範囲に記載の「第1の書込制限手段」に相当する。

第1の書込規制フラグが「0」であれば(S25:yes)、書込みが許可されたことを示す不正対策プログラム書込みフラグに「1」をセットし(S30)、S35の処理で第1のプログラムモード(図にはプログラムモード1と示す)へ移行する。該第1のプログラムモードにおいて第1の内蔵ROMに不正対策プログラムが書込まれる。

第2の書込規制フラグが「0」であれば(S40:yes)、書込みが許可されたことを示すユーザープログラム書込みフラグに「1」をセットし(S45)、S50の処理で第2のプログラムモード(図にはプログラムモード2と示す)へ移行する。該第2のプログラムモードにおいて第2の内蔵ROMにユーザープログラムが書込まれる。

セキュリティモードで異常がなければ(S60:yes)、S65の処理でユーザーモードが設定され、不正対策プログラムおよびユーザープログラムが所定のINT割込みに応じて実行される。

尚、セキュリティモードにおいて、不正対策プログラムおよびユーザープログラムに異常があれば(S60:no)、マイコンチップは不正対策プログラムおよびユーザープログラムの実行を行わず、CPUの処理を停止する。

このようにマイコンチップメーカーにて不正対策プログラムを第1の内蔵ROM3Aに書込むようにすれば、遊技機メーカーにおいては不正対策プログラムを改変することができず、不正対策プログラムをマイコンチップ1の機能の一部とすることが可能となる。

よってマイコンチップ1の機能の一部となった不正対策プログラムが格納された第1の内蔵ROM3Aはプログラム記憶用の前記規定の記憶容量から除外することができ、その分、ユーザープログラムの記憶容量の制約が緩和され記憶容量を増加することができる。したがって、ユーザープログラムのプログラム内容を増やせる分、遊技内容が豊富で興趣の豊かな遊技を実現することができる。

またマイコンチップ1は、セキュリティモードでユーザープログラムの異常があれば、CPU2を停止して確実に不正行為を防ぐことができる。

第2の書込フラグが「1」であれば(S70:yes)、セキュリティモードを実行し(S55)、かつ不正対策およびユーザープログラムが正常であれば(S60:yes)ユーザーモードを実行する(S65)。

S70の処理で第2の書込フラグが「1」でなければ(S70:no)、マイコンチップはCPUの処理を停止する。

これによれば、マイコンチップが遊技機に実装された状態であって、モード設定信号がLレベルのときでもユーザープログラムが書込まれているか確認するので、ユーザープログラムに異常があれば直ちにCPUの処理を停止して遊技を不能とする。よって、遊技者が遊技機を開始してから遊技機に不具合が生じ、遊技者が被る損害を未然に防ぐことができる。

2 CPU(中央制御装置)

3A 第1の内蔵ROM

3B 第2の内蔵ROM

4 内蔵RAM

6A システムリセット端子

6B モード設定入力端子

Claims (2)

- 遊技機制御用マイコンチップにおいて、

不正対策プログラムおよび該プログラムに関連する情報を記憶する第1の内蔵ROMと、

遊技制御用のユーザープログラムおよび該プログラムに関連する情報を記憶する第2の内蔵ROMと、

前記不正対策プログラムに基づく制御又は前記ユーザープログラムに基づく制御を実行する中央制御装置(CPU)と、を具備し、

前記不正対策プログラムは、前記ユーザープログラムと一連に実行され、不正行為を検出するためのスイッチの検出状況を監視して不正対策を施す構成とし、

かつ、リセット信号が入力されるシステムリセット端子と、

モード設定信号が入力されるモード設定入力端子と、

前記システムリセット端子へのリセット信号の入力に応じてシステムリセットを実行するシステムリセット手段と、

前記システムリセットの実行後、前記第1の内蔵ROMへの前記不正対策プログラムの書込みを実行する第1のプログラムモード、前記第2の内蔵ROMへの前記ユーザープログラムの書込みを実行する第2のプログラムモード、および前記第2の内蔵ROMに書込まれた前記ユーザープログラムの異常の有無をチェックするセキュリティモードのいずれかに移行せしめるモード移行手段と、

前記不正対策プログラムが前記第1の内蔵ROMに書込まれていることを示す第1の書込制限手段と、

前記ユーザープログラムが前記第2の内蔵ROMに書込まれていることを示す第2の書込制限手段と、を具備し、

前記モード移行手段は、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力があり、かつ、前記第1の内蔵ROMに前記不正対策プログラムが書込まれていない状態であることが示されていることを条件に、前記第1のプログラムモードへと移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力があり、前記第1の内蔵ROMに前記不正対策プログラムが書込まれている状態であることが示される一方、前記第2の内蔵ROMに前記ユーザープログラムが書込まれていない状態が示されていることを条件に、前記第2のプログラムモードへと移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力があったにも拘らず、前記第1及び第2の書込制限手段により前記第1及び第2の内蔵ROMに前記各プログラムが書込まれている状態であることが示されていることを条件に、前記セキュリティモードに移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力がないことを条件に、前記セキュリティモードに移行せしめるように構成され、

該セキュリティモードで異常がなければ、前記不正対策プログラムと前記ユーザープログラムに基づく制御を実行するユーザーモードに移行せしめ、前記セキュリティモードで異常があれば、前記中央制御装置の処理を停止せしめることを特徴とする遊技機制御用マイコンチップ。 - 遊技機制御用マイコンチップにおいて、

不正対策プログラムおよび該プログラムに関連する情報を記憶する第1の内蔵ROMと、

遊技制御用のユーザープログラムおよび該プログラムに関連する情報を記憶する第2の内蔵ROMと、

前記不正対策プログラムに基づく制御又は前記ユーザープログラムに基づく制御を実行する中央制御装置(CPU)と、を具備し、

前記不正対策プログラムは、前記ユーザープログラムと一連に実行され、不正行為を検出するためのスイッチの検出状況を監視して不正対策を施す構成とし、

かつ、リセット信号が入力されるシステムリセット端子と、

モード設定信号が入力されるモード設定入力端子と、

前記システムリセット端子へのリセット信号の入力に応じてシステムリセットを実行するシステムリセット手段と、

前記システムリセットの実行後、前記第1の内蔵ROMへの前記不正対策プログラムの書込みを実行する第1のプログラムモード、前記第2の内蔵ROMへの前記ユーザープログラムの書込みを実行する第2のプログラムモード、および前記第2の内蔵ROMに書込まれた前記ユーザープログラムの異常の有無をチェックするセキュリティモードのいずれかに移行せしめるモード移行手段と、

前記不正対策プログラムが前記第1の内蔵ROMに書込まれていることを示す第1の書込制限手段と、

前記ユーザープログラムが前記第2の内蔵ROMに書込まれていることを示す第2の書込制限手段と、を具備し、

前記モード移行手段は、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力があり、かつ、前記第1の内蔵ROMに前記不正対策プログラムが書込まれていない状態が示されていることを条件に、前記第1のプログラムモードへと移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力があり、前記第1の内蔵ROMに前記不正対策プログラムが書込まれている状態が示される一方、前記第2の内蔵ROMに前記ユーザープログラムが書込まれていない状態が示されていることを条件に、前記第2のプログラムモードへと移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力がなく、かつ、前記第2の内蔵ROMに前記ユーザープログラムが書込まれている状態が示されていることを条件に、前記セキュリティモードに移行せしめ、

前記システムリセットの実行後に、前記モード設定入力端子へのモード設定信号の入力がなく、かつ、前記第2の内蔵ROMに前記ユーザープログラムが書込まれている状態が示されていないことを条件に、前記中央制御装置の処理を停止せしめるように構成され、

前記セキュリティモードで異常がなければ、前記不正対策プログラムと前記ユーザープログラムに基づく制御を実行するユーザーモードに移行せしめ、前記セキュリティモードで異常があれば、前記中央制御装置の処理を停止せしめることを特徴とする遊技機制御用マイコンチップ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011120356A JP5945672B2 (ja) | 2010-06-15 | 2011-05-30 | 遊技機制御用マイコンチップ |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010135683 | 2010-06-15 | ||

| JP2010135683 | 2010-06-15 | ||

| JP2011120356A JP5945672B2 (ja) | 2010-06-15 | 2011-05-30 | 遊技機制御用マイコンチップ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012020113A JP2012020113A (ja) | 2012-02-02 |

| JP2012020113A5 JP2012020113A5 (ja) | 2014-07-10 |

| JP5945672B2 true JP5945672B2 (ja) | 2016-07-05 |

Family

ID=45774885

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011120356A Active JP5945672B2 (ja) | 2010-06-15 | 2011-05-30 | 遊技機制御用マイコンチップ |

| JP2011120355A Active JP5514982B2 (ja) | 2010-06-15 | 2011-05-30 | 遊技機制御用マイコンチップ |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011120355A Active JP5514982B2 (ja) | 2010-06-15 | 2011-05-30 | 遊技機制御用マイコンチップ |

Country Status (1)

| Country | Link |

|---|---|

| JP (2) | JP5945672B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6503704B2 (ja) * | 2014-11-27 | 2019-04-24 | サミー株式会社 | 遊技機 |

| JP6578652B2 (ja) * | 2014-11-27 | 2019-09-25 | サミー株式会社 | 遊技機 |

| JP6503705B2 (ja) * | 2014-11-27 | 2019-04-24 | サミー株式会社 | 遊技機 |

| JP6503706B2 (ja) * | 2014-11-27 | 2019-04-24 | サミー株式会社 | 遊技機 |

| JP6578653B2 (ja) * | 2014-11-27 | 2019-09-25 | サミー株式会社 | 遊技機 |

| JP2018027136A (ja) * | 2016-08-15 | 2018-02-22 | 株式会社ユニバーサルエンターテインメント | 遊技機 |

| JP6495977B2 (ja) * | 2017-07-21 | 2019-04-03 | 株式会社藤商事 | 遊技機 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0847566A (ja) * | 1994-08-08 | 1996-02-20 | Sophia Co Ltd | 遊技機用マイクロコンピュータ及びその検査装置 |

| JPH09239131A (ja) * | 1996-03-07 | 1997-09-16 | Sankyo Kk | 遊技機 |

| JPH11300016A (ja) * | 1998-04-16 | 1999-11-02 | Le Tec:Kk | 遊技機制御用マイクロコンピュータチップ |

| JP2004129874A (ja) * | 2002-10-10 | 2004-04-30 | Shinko Electric Co Ltd | 遊技機用制御装置 |

| JP2004129955A (ja) * | 2002-10-11 | 2004-04-30 | Shinko Electric Co Ltd | 遊技機用制御装置 |

| JP2009034317A (ja) * | 2007-08-01 | 2009-02-19 | Daito Giken:Kk | 遊技台 |

| JP5552609B2 (ja) * | 2008-03-03 | 2014-07-16 | 株式会社高尾 | 遊技機 |

| JP4364292B2 (ja) * | 2008-10-02 | 2009-11-11 | 株式会社エルイーテック | 遊技機制御用チップ及び遊技機制御方法 |

-

2011

- 2011-05-30 JP JP2011120356A patent/JP5945672B2/ja active Active

- 2011-05-30 JP JP2011120355A patent/JP5514982B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP5514982B2 (ja) | 2014-06-04 |

| JP2012020113A (ja) | 2012-02-02 |

| JP2012020112A (ja) | 2012-02-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5945672B2 (ja) | 遊技機制御用マイコンチップ | |

| US5396609A (en) | Method of protecting programs and data in a computer against unauthorized access and modification by monitoring address regions | |

| JP5120931B2 (ja) | 遊技機 | |

| JP5250804B2 (ja) | 遊技機 | |

| JP5120932B2 (ja) | 遊技機 | |

| US10509568B2 (en) | Efficient secure boot carried out in information processing apparatus | |

| JP2012250131A (ja) | 遊技機 | |

| JP5578943B2 (ja) | スロットマシン | |

| JP5578942B2 (ja) | スロットマシン | |

| RU2008133310A (ru) | Дезагрегированная защищенная среда выполнения | |

| JPH01219982A (ja) | Icカード | |

| JP2012020113A5 (ja) | ||

| JP2009000241A (ja) | 遊技機 | |

| JP3653474B2 (ja) | 遊技機 | |

| JP2016168106A (ja) | 遊技機制御用チップ | |

| JP5443956B2 (ja) | インサーキットエミュレータ用アダプタおよびインサーキットエミュレータ | |

| KR20140034346A (ko) | 반도체 소자의 유효 사용기간 제어 시스템과 그 방법 | |

| JP3501129B2 (ja) | 制御装置 | |

| JP2007190099A5 (ja) | ||

| JP2018027230A (ja) | 遊技機用プロセッサ装置、チップ、基板及び遊技機 | |

| JP3922731B2 (ja) | 遊技機制御用ワンチップマイクロコンピュータ | |

| JP2007064762A (ja) | 半導体装置、テストモード制御回路 | |

| JP6379852B2 (ja) | 電子情報記録媒体、プロセッサモジュールの処理方法、及びプロセッサモジュールの処理プログラム | |

| JP5892344B2 (ja) | スロットマシン | |

| JP5892345B2 (ja) | スロットマシン |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140522 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140523 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150721 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150724 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150917 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160322 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160325 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5945672 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |