JP5838692B2 - Cmos半導体装置の製造方法 - Google Patents

Cmos半導体装置の製造方法 Download PDFInfo

- Publication number

- JP5838692B2 JP5838692B2 JP2011211062A JP2011211062A JP5838692B2 JP 5838692 B2 JP5838692 B2 JP 5838692B2 JP 2011211062 A JP2011211062 A JP 2011211062A JP 2011211062 A JP2011211062 A JP 2011211062A JP 5838692 B2 JP5838692 B2 JP 5838692B2

- Authority

- JP

- Japan

- Prior art keywords

- type semiconductor

- semiconductor device

- cmos

- ink

- recess

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

Description

印刷法のなかでも、微細な画線パターンを形成可能な印刷法として、マイクロコンタクト印刷が挙げられる(非特許文献1)。これらの印刷法はポリジメチルシロキサン(PDMS)などの比較的柔らかく、表面エネルギーの低い版を用いて、インクの泣き別れ(凝集破壊)無しに乾燥(半乾燥)したインクを版から基板へと全転写をさせる事で高詳細なパターンを得る事ができる。

さらに、請求項3に記載のCMOS半導体装置の製造方法は、請求項1または2の構成に対して、前記Pチャネル領域を形成するためのP型半導体インクと前記Nチャネル領域を形成するためのN型半導体インクとは、1[mPa・s]以上30[mPa・s]以下の粘度を有することを特徴としている。

さらに、請求項5に記載のCMOS半導体装置の製造方法は、請求項1乃至4のいずれか1の構成に対して、前記凹版は、シリコーン樹脂もしくはフッ素樹脂で構成された表面にモールディング法で形成された、前記第1凹部及び前記第2凹部を含む凹部としての溝構造部と該溝構造部以外の部分を平坦化した平坦部とを備え、前記溝構造部の幅が1[μm]以上50[μm]以下であり、前記シリコーン樹脂もしくは前記フッ素樹脂で構成された表面のショアA硬度が30以上80以下であることを特徴としている。

(構成)

図1は、本発明の実施の形態にかかるCMOS半導体装置の断面図である。図2は、ゲート絶縁膜401を除く、図1のCMOS半導体装置の平面図である。

図1に示すように、本実施の形態にかかるCMOS半導体装置501は、基板000上にゲート電極301、ゲート絶縁膜401、第1のソース電極201、ドレイン電極203、第2のソース電極202が設けられ、チャネル部として、Pチャネル領域101とNチャネル領域102とが形成されている。なお、図1において、CMOS半導体装置501から、チャネル部を除いたものが、被印刷基板001となる。

本実施の形態では、図2に示すように、チャネル部を構成する、Pチャネル領域101のチャネル長Lp及びチャネル幅Zpと、Nチャネル領域102のチャネル長Ln及びチャネル幅Znとが、「Lp=Ln」、「Zp=Zn」の関係となるように形成されている。

次に、図3に基づき、上記構成のCMOS半導体装置501の製造方法を以下に説明する。図3は、CMOS半導体装置501の製造方法の一例を示す模式図である。

なお、被印刷基板001の製造工程については、公知の製造工程と同様となるため説明を省略する。以下、本発明の特徴部分である凹版を用いたマイクロコンタクト印刷による被印刷基板001へのチャネル部の形成工程について具体的に説明する。

先ず、図3中の(1)に示すように、P型半導体インクジェットヘッド701によってP型半導体インク111を凹版601に形成された溝構造部の1つである第1凹部602に供給する。また、N型半導体インクジェットヘッド702によってN型半導体インク112を凹版601に形成された溝構造部の1つである第2凹部603に供給する。

また、インク供給時において、インクの液滴径制御や着弾制御、溝構造部と平坦部604との境界のエッジによりインクがはじきやすくなる効果を利用して、所定の位置のみのインキングを行う。

図3中の(2)に示すように、半導体インクをインキングした後に、凹版601を被印刷基板001のデバイス形成面に接触させる。その後、加熱処理等を経て、図3中の(3)に示すように、インクを被印刷基板001に一括して転写する。インクは所定の位置だけに付着しているために、所望のパターンを精度よく基板に転写させる事ができる。

このようにして、P型半導体インク111とN型半導体インク112を凹版601にインキングして一括で被印刷基板001へ転写する事によって、工程の短縮やコンパクトな製造ラインの構築も見込めるようになる。また、温度や湿度の変動によるプラスチックフィルム基板の収縮や膨張の問題が指摘されているが、複数色を一括で行う事は各色間の寸法変動を最小限に抑える事ができるために、大面積の高精度アライメントにも寄与する事が可能である。更には、各工程を連続に行うため、表面汚染などを抑制し、プロセス安定性やデバイスパフォーマンス・信頼性の向上も期待できる。

N型半導体の材料には、Siナノ粒子やSi前駆体 、金属酸化物、低分子有機半導体、高分子有機半導体を用いる事ができる。

金属酸化物を主成分とする酸化物半導体材料としては、Cu2O、NiO、CuAlO2、CuGaO2、ZnRh2O4、SnO、LaCuOSeなどの材料が挙げられ、これらの材料のインクは金属酸化物のナノ粒子分散体や、金属酸化物前駆体の何れであっても構わない。

有機半導体材料としては、チオフェン及びその誘導体を骨格にもつオリゴマーやポリマー、フェニレン−ビニレン及びその誘導体を骨格にもつオリゴマーやポリマー、フルオレン及びその誘導体を骨格にもつオリゴマーやポリマー、ベンゾフラン及びその誘導体を骨格にもつオリゴマーやポリマー、チエニレン−ビニレン及びその誘導体を骨格にもつオリゴマーやポリマー、トリフェニルアミンなどの芳香族第3級アミン及びその誘導体を骨格にもつオリゴマーやポリマー、カルバゾール及びその誘導体を骨格にもつオリゴマーやポリマー、ビニルカルバゾール及びその誘導体を骨格にもつオリゴマーやポリマー、ピロール及びその誘導体を骨格にもつオリゴマーやポリマー、アセチレン及びその誘導体を骨格にもつオリゴマーやポリマー、イソチアナフェン及びその誘導体を骨格にもつオリゴマーやポリマー、ヘプタジエン及びその誘導体を骨格にもつオリゴマーやポリマーなどの高分子、無金属フタロシアニン、金属フタロシアニン類及びそれらの誘導体、ジアミン類、フェニルジアミン類及びそれらの誘導体、ルブレン、ペンタセンなどのアセン類及びその誘導体、ポルフィリン、テトラメチルポルフィリン、テトラフェニルポルフィリン、テトラベンズポルフィリン、モノアゾテトラベンズポルフィリン、ジアゾテトラベンズポルフィン、トリアゾテトラベンズポルフィリン、オクタエチルポルフィリン、オクタアルキルチオポルフィラジン、オクタアルキルアミノポルフィラジン、ヘミポルフィラジン、クロロフィル等の無金属ポルフィリンや金属ポルフィリン及びそれらの誘導体が利用できる。金属フタロシアニンや金属ポルフィリンの中心金属としては、マグネシウム、亜鉛、銅、銀、アルミニウム、ケイ素、チタン、バナジウム、クロム、マンガン、鉄、コバルト、ニッケル、スズ、白金、鉛などの金属、金属酸化物、金属ハロゲン化物などを用いる事ができる。

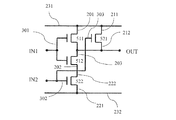

図4は、本実施の形態にかかるCMOS半導体装置501の回路構成の一例を示す図である。

第1の電源線231と、第2の電源線232との間には、Pチャネル型電界効果トランジスタ511と、Nチャネル型電界効果トランジスタ512とが設けられている。Pチャネル型電界効果トランジスタ511の第1のソース電極201は、第1の電源線231に接続されている。また、Nチャネル型電界効果トランジスタ512の第2のソース電極202は、第2の電源線232に接続されている。Pチャネル型電界効果トランジスタ511とNチャネル型電界効果トランジスタ512とはドレイン電極203が共通しており、共通のドレイン電極203が出力端子OUTに接続されている。Pチャネル型電界効果トランジスタ511とNチャネル型電界効果トランジスタ512とはゲート電極301が共通しており、共通のゲート電極301が入力端子INに接続されている。このような構成によって、入力端子INから入力された信号は、反転して出力端子OUTから出力される。

上記凹版601を用いたマイクロコンタクト印刷によるチャネル部の形成方法を用いて製造された半導体装置501(図4に示すCMOS回路)を用いて、下記の回路構成を有するCMOS半導体装置を製造することが可能である。

図5は、本実施の形態に係るNAND回路の回路構成の一例を示す図である。また、図6は、本実施の形態に係るNOR回路の回路構成の一例を示す図である。

図5に示すNAND回路は、第1のPチャネル型電界効果トランジスタ511と、第1のNチャネル型電界効果トランジスタ512と、第2のPチャネル型電界効果トランジスタ521と、第2のNチャネル型電界効果トランジスタ522とを備えている。

更に、NAND回路は、第1の電源線231と、入力端子IN1と、入力端子IN2と、出力端子OUTとを備えている。

更に、第2のPチャネル型電界効果トランジスタ521のゲート電極303は第2のNチャネル型電界効果トランジスタ522のゲート電極302に接続されていると共に、NAND回路の入力端子IN2に接続されている。更に、CMOS回路の共通のゲート電極301はNAND回路の入力端子IN1に接続されている。

そして、第1のPチャネル型電界効果トランジスタ511と第1のNチャネル型電界効果トランジスタ512とを組み合わせてCMOS回路が形成されている。このCMOS回路は、上記チャネル部の形成方法を用いて製造されたものとなる。

更に、第2のNチャネル型電界効果トランジスタ522のソース電極211は第2の電源線232に接続され、第2のNチャネル型電界効果トランジスタ522のドレイン電極212はCMOS回路のドレイン電極203に接続されていると共に、NOR回路の出力端子OUTに接続されている。

次に、図7に基づき、上記実施の形態のCMOS半導体装置の製造方法及びCMOS半導体装置の変形例を説明する。

図7は、本変形例にかかるCMOS半導体装置501の一例を示す平面図である。

本変形例において、凹版601の第1凹部602と第2凹部603とは、Pチャネル領域101のチャネル長LpがNチャネル領域102のチャネル長Lnと比較して狭くなり、かつPチャネル領域101のチャネル幅ZpがNチャネル領域102のチャネル幅Znと比較して広くなるように長さおよび幅が形成されている。このこと以外は、上記の実施の形態と同様にしてCMOS半導体装置501を製造している。

このようにして、Pチャネル型電界効果トランジスタとNチャネル型電界効果トランジスタのチャネル長Lp,Lnとチャネル幅Zp,Znとを調整する事で、P型半導体とN型半導体の電界効果移動度が異なる場合においても、トランジスタの電流値の大きさを同程度にする事ができる。

また、本発明は上記実施の形態に限定されるものではなく、本発明の目的を達成できる範囲での変形、改良等は本発明に含まれるものである。

印刷パターンとして、4インチのCMOSアレイ、各層の周囲にアライメントマークを配置したものを使用した。本実施例では基板上にゲート電極とキャパシタ、バスラインで構成されるゲート層が形成され、ゲート層上に絶縁膜が形成され、絶縁膜上にソース・ドレイン電極が形成された被印刷基板上にP型半導体とN型半導体で構成される半導体層をパターニングする。

2)インキ塗工膜を乾燥させて凹版上にP型半導体とN型半導体のインクパターンを得た。

印刷パターンが形成された被印刷基板を加熱装置でアニールし、CMOSアレイのP型半導体層(Pチャネル領域)とN型半導体層(Nチャネル領域)とを形成した。本発明の印刷方法を用いる事で、高精細なTFTアレイを効率よく得られた。

001 被印刷基板

101 P型半導体

102 N型半導体

111 P型半導体インク

112 N型半導体インク

201 第1のソース電極

202 第2のソース電極

203 ドレイン電極

211、221 ソース電極

212、222 ドレイン電極

231 第1の電源線

232 第2の電源線

301、302、303、304、305 ゲート電極

401 ゲート絶縁膜

501 CMOS半導体装置

511 第1のPチャネル型電界効果トランジスタ

512 第1のNチャネル型電界効果トランジスタ

521 第2のPチャネル型電界効果トランジスタ

522 第2のNチャネル型電界効果トランジスタ

601 凹版

602 第1凹部

603 第2凹部

604 平坦部

701 P型半導体インクジェットヘッド

702 N型半導体インクジェットヘッド

Claims (8)

- Pチャネル型電界効果トランジスタとNチャンネル型電界効果トランジスタとを組み合わせて構成されるCMOS回路を含むCMOS半導体装置の製造方法であって、

凹版を用いた印刷方法によって、前記Pチャネル型電界効果トランジスタを構成するPチャネル領域と、前記Nチャンネル型電界効果トランジスタを構成するNチャネル領域とを形成し、

前記凹版は、前記Pチャネル領域を形成するための第1凹部と、前記Nチャネル領域を形成するための第2凹部とを備え、

前記凹版を用いた印刷方法は、

非接触式インキング法で、前記第1凹部にP型半導体インクを供給すると共に、前記第2凹部にN型半導体インクを供給する工程と、

前記P型半導体インク及び前記N型半導体インクを供給後に、凹版を被印刷基板に押しつけて、前記第1凹部に供給したP型半導体インクと前記第2凹部に供給したN型半導体インクとを一括して前記被印刷基板に転写する工程と、を含むことを特徴とするCMOS半導体装置の製造方法。 - 前記非接触式インキング法は、ディスペンサ法もしくはインクジェット法の何れか一方であることを特徴とする請求項1に記載のCMOS半導体装置の製造方法。

- 前記Pチャネル領域を形成するためのP型半導体インクと前記Nチャネル領域を形成するためのN型半導体インクとは、1[mPa・s]以上30[mPa・s]以下の粘度を有することを特徴とする請求項1又は2に記載のCMOS半導体装置の製造方法。

- 前記P型半導体インクと前記N型半導体インクとは、1[atm]における沸点が130[℃]以上の薬液を含有していることを特徴とする請求項1乃至3のいずれか1項に記載のCMOS半導体装置の製造方法。

- 前記凹版は、シリコーン樹脂もしくはフッ素樹脂で構成された表面にモールディング法で形成された、前記第1凹部及び前記第2凹部を含む凹部としての溝構造部と該溝構造部以外の部分を平坦化した平坦部とを備え、

前記溝構造部の幅が1[μm]以上50[μm]以下であり、

前記シリコーン樹脂もしくは前記フッ素樹脂で構成された表面のショアA硬度が30以上80以下であることを特徴とする請求項1乃至4のいずれか1項に記載のCMOS半導体装置の製造方法。 - 前記凹版は、前記P型半導体インクの含有するP型半導体と前記N型半導体インクの含有するN型半導体との電界効果移動度の差異に応じて、前記Pチャネル領域及び前記Nチャネル領域のチャネル長及びチャネル幅の少なくとも一方が相互で異なるように前記第1凹部及び前記第2凹部が形成されていることを特徴とする請求項1乃至5のいずれか1項に記載のCMOS半導体装置の製造方法。

- 前記CMOS半導体装置は、前記CMOS回路を含むNAND回路を備えることを特徴とする請求項1乃至6のいずれか1項に記載のCMOS半導体装置の製造方法。

- 前記CMOS半導体装置は、前記CMOS回路を含むNOR回路を備えることを特徴とする請求項1乃至7のいずれか1項に記載のCMOS半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011211062A JP5838692B2 (ja) | 2011-09-27 | 2011-09-27 | Cmos半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011211062A JP5838692B2 (ja) | 2011-09-27 | 2011-09-27 | Cmos半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013074041A JP2013074041A (ja) | 2013-04-22 |

| JP2013074041A5 JP2013074041A5 (ja) | 2014-07-17 |

| JP5838692B2 true JP5838692B2 (ja) | 2016-01-06 |

Family

ID=48478303

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011211062A Expired - Fee Related JP5838692B2 (ja) | 2011-09-27 | 2011-09-27 | Cmos半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5838692B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6334216B2 (ja) * | 2014-03-14 | 2018-05-30 | 京セラ株式会社 | 半導体粒子ペースト |

| JP6530591B2 (ja) * | 2014-07-25 | 2019-06-12 | 旭化成株式会社 | フレキシブル回路デバイス及びそれを備える筋電位測定装置 |

| JP6492523B2 (ja) * | 2014-10-21 | 2019-04-03 | 凸版印刷株式会社 | 有機半導体薄膜トランジスタ素子 |

| CN107104188A (zh) * | 2017-04-20 | 2017-08-29 | 上海幂方电子科技有限公司 | 有机互补型非门器件的制备方法 |

| JPWO2022050353A1 (ja) * | 2020-09-07 | 2022-03-10 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7244626B2 (en) * | 2004-06-30 | 2007-07-17 | Motorola, Inc. | Semiconductor devices shared element(s) apparatus and method |

| KR100634327B1 (ko) * | 2005-04-13 | 2006-10-13 | 한국기계연구원 | 롤-투-롤 윤전인쇄방식을 이용한 전자소자의 제조방법 및그 제조장치 |

| JP4729963B2 (ja) * | 2005-04-15 | 2011-07-20 | パナソニック株式会社 | 電子部品接続用突起電極とそれを用いた電子部品実装体およびそれらの製造方法 |

| JP2008159812A (ja) * | 2006-12-22 | 2008-07-10 | Sharp Corp | 半導体層形成装置および半導体層形成方法 |

| JP2008166016A (ja) * | 2006-12-27 | 2008-07-17 | Toppan Printing Co Ltd | 有機機能性素子の製造方法 |

| JP2009130165A (ja) * | 2007-11-26 | 2009-06-11 | Sanyo Electric Co Ltd | Cmos半導体装置 |

| JP2010212587A (ja) * | 2009-03-12 | 2010-09-24 | Ricoh Co Ltd | 有機薄膜トランジスタ、有機薄膜トランジスタの製造方法、有機薄膜トランジスタアレイ及び表示装置 |

| JP5587636B2 (ja) * | 2010-03-01 | 2014-09-10 | 富士紡ホールディングス株式会社 | 研磨パッド |

| JP2011187750A (ja) * | 2010-03-09 | 2011-09-22 | Ricoh Co Ltd | 有機薄膜トランジスタの製造方法、有機薄膜トランジスタレイの製造方法及び表示装置の製造方法 |

-

2011

- 2011-09-27 JP JP2011211062A patent/JP5838692B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2013074041A (ja) | 2013-04-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| Fukuda et al. | Recent progress in the development of printed thin‐film transistors and circuits with high‐resolution printing technology | |

| Buga et al. | A review on materials and technologies for organic large‐area electronics | |

| TWI470697B (zh) | 薄膜電晶體及其製造方法 | |

| JP4888043B2 (ja) | 有機半導体用組成物、トランジスタの製造方法、アクティブマトリクス装置の製造方法、電気光学装置の製造方法および電子機器の製造方法 | |

| JP5838692B2 (ja) | Cmos半導体装置の製造方法 | |

| JP4730623B2 (ja) | 薄膜トランジスタ、薄膜トランジスタの製造方法、および電子機器 | |

| JP2006352083A (ja) | 有機薄膜トランジスタ及びアクティブマトリックス表示装置 | |

| US20090134387A1 (en) | Cmos semiconductor device | |

| JP6229658B2 (ja) | 薄膜トランジスタ及びその製造方法、画像表示装置 | |

| JP2008244362A (ja) | 半導体装置の製造方法、半導体装置、半導体回路、電気光学装置および電子機器 | |

| Zheng et al. | Smart Electronic Systems: Heterogeneous Integration of Silicon and Printed Electronics | |

| JP2010212587A (ja) | 有機薄膜トランジスタ、有機薄膜トランジスタの製造方法、有機薄膜トランジスタアレイ及び表示装置 | |

| JP6393936B2 (ja) | 薄膜トランジスタ、トランジスタアレイ、薄膜トランジスタの製造方法及びトランジスタアレイの製造方法 | |

| KR101487443B1 (ko) | 유전막 표면 개질용 트랜지스터 및 이의 제조 방법 | |

| JP5261744B2 (ja) | 有機tftの製造方法、及び有機tft | |

| JP6050400B2 (ja) | 有機電子デバイスを製造する方法および有機電子デバイス | |

| KR101288622B1 (ko) | 유기 박막 트랜지스터의 유기 반도체층 형성 방법, 이에 의해 형성된 유기 박막 트랜지스터, 이를 포함하는 표시 소자 및 그 표시 소자로 형성된 표시용 전자기기 | |

| JP5790075B2 (ja) | 電界効果トランジスタの製造方法及びそれに用いる製造装置 | |

| JP5779933B2 (ja) | 薄膜トランジスタ装置およびその製造方法 | |

| Tseng | Scaling of inkjet-printed transistors using novel printing techniques | |

| JP5057423B2 (ja) | 有機半導体装置の製造方法 | |

| JP5103735B2 (ja) | 有機半導体層用組成物、薄膜トランジスタの製造方法、アクティブマトリクス装置の製造方法、電気光学装置の製造方法および電子機器の製造方法 | |

| KR101499075B1 (ko) | 유전막 표면 개질용 저전압 트랜지스터 및 이의 제조 방법 | |

| JP2006261528A (ja) | 有機薄膜トランジスタ、それを備えた表示装置および有機薄膜トランジスタの製造方法。 | |

| JP2008192669A (ja) | 有機半導体用組成物、及びトランジスタの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140603 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140821 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150721 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150728 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150917 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20151013 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20151026 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5838692 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |