JP5784299B2 - データ処理装置および画像処理装置 - Google Patents

データ処理装置および画像処理装置 Download PDFInfo

- Publication number

- JP5784299B2 JP5784299B2 JP2010245478A JP2010245478A JP5784299B2 JP 5784299 B2 JP5784299 B2 JP 5784299B2 JP 2010245478 A JP2010245478 A JP 2010245478A JP 2010245478 A JP2010245478 A JP 2010245478A JP 5784299 B2 JP5784299 B2 JP 5784299B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- unit

- output

- image processing

- buffer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F5/00—Methods or arrangements for data conversion without changing the order or content of the data handled

- G06F5/06—Methods or arrangements for data conversion without changing the order or content of the data handled for changing the speed of data flow, i.e. speed regularising or timing, e.g. delay lines, FIFO buffers; over- or underrun control therefor

Description

次に、画像処理モジュールA50を実際の画像処理に適用した場合の動作例について説明する。以下の説明においては、画像処理モジュールA50が、出力部53に備えたフィルタ処理部531によって歪補正処理を行う場合の例について説明する。図4は、本実施形態の画像処理モジュールA50において行う歪補正処理を説明する図である。

ここで、画像処理モジュールA50による歪補正処理の動作の説明に先立って、画像処理モジュールA50における歪補正処理の処理方法および各構成要素の構成について説明する。まず、画像処理モジュールA50における歪補正処理の方法について説明する。図5は、本実施形態の画像処理モジュールA50における歪補正処理方法の一例を説明する図である。歪補正処理に画像処理モジュールA50を適用した場合の本適用例においては、画像処理モジュールA50内のフィルタ処理部531は、図5(a)に示したような、1フレームの静止画像のデータを水平方向に複数のブロック(以下、「ブロックライン」という)に分割したブロック画像データ毎に歪補正処理を行う。そして、フィルタ処理部531は、静止画像の上(ブロックライン1)から順次歪補正処理を行うものとする。

続いて、本適用例におけるデータバッファ52の構成について説明する。図6および図7は、本実施形態の画像処理モジュールA50に備えたデータバッファ52の構成例および動作例を説明する図である。本適用例の画像処理モジュールA50に備えたデータバッファ52は、図6(a)に示したように、ブロックラインの垂直方向の幅を1ラインとし、ブロックラインの水平方向に16ライン分の記憶領域(領域1〜領域16)で構成されているものとする。

続いて、本適用例においてブロック画像データをデータバッファ52に書き込む動作について説明する。図8は、本実施形態の画像処理モジュールA50に備えたデータバッファ52にブロック画像データを書き込む動作例を説明する図である。

続いて、本適用例においてデータバッファ52に記憶されているブロック画像データを読み出す動作について説明する。図9は、本実施形態の画像処理モジュールA50に備えたデータバッファ52からブロック画像データを読み出す動作例を説明する図である。

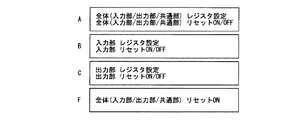

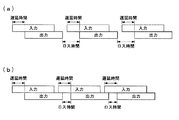

続いて、本適用例の画像処理モジュールA50における歪み補正処理の動作について説明する。図10および図11は、本実施形態の画像処理モジュールA50におけるパイプライン処理のタイミングおよび制御内容の一例を説明する図である。図10および図11においては、説明を容易にするため、図4〜図9を用いて説明した本適用例の画像処理モジュールA50の構成を簡略化した場合の例を示している。図10および図11の説明を行うための変更点は以下である。まず、1フレームの静止画像のデータを、2つのブロックラインに分割する。また、データバッファ52は8ライン分の記憶領域(領域1〜領域8)とする。また、入力部51には、12ラインのブロック画像データが入力され、出力部53からは、11ラインの画像処理データが出力されるものとする。なお、ブロック画像データおよび画像処理データには、ブロックライン、およびブロックライン内のライン数を区別するための符号を、上記と同様に付与して説明する。なお、画像処理モジュールA50のパイプライン処理のタイミングに関しては図10を参照し、このときのシーケンサ30による画像処理モジュールA50の制御内容に関しては図11を参照して説明を行う。

なお、図10に示したパイプライン処理のタイミングにおいては、出力部53の処理が待たされている期間(タイミングt5〜タイミングt6)、および入力部51によるデータバッファ52へのブロック画像データの書き込みが待たされている期間(タイミングt10〜タイミングt11)が存在している。このように、処理が待たされる時間も処理モジュールの入出力の遅延時間に影響し、パイプライン処理におけるロス時間となってしまう。このような処理モジュール内の処理が待たされることによるロス時間は、データバッファ52のバッファサイズを最適化することによって、低減することもできる。

10・・・DMAバス

20・・・DRAM

30・・・シーケンサ(画像処理装置)

40・・・入力DMAモジュール

50・・・画像処理モジュールA(データ処理装置)

51・・・入力部(データ書き込み制御部)

52・・・データバッファ(バッファ部)

53・・・出力部(データ読み出し制御部)

531・・・フィルタ処理部(データ読み出し制御部、フィルタ処理部)

54・・・調停部(バッファ領域決定部)

55・・・データバッファ領域決定部(バッファ領域決定部)

60・・・画像処理モジュールB(データ処理装置)

70・・・出力DMAモジュール

Claims (5)

- パイプライン接続された複数の画像処理モジュールを用いて、画像データを処理するデータ処理装置であって、

前記画像処理モジュールは、

前記画像データの領域を複数行から成る複数の重複ブロックに分割し、第1のブロックにおける最後の行の画像処理を行う際に必要とするデータ数と、該第1のブロックの次に処理を行う第2のブロックにおける最初の行の画像処理を行う際に必要とするデータ数とを合わせた数のデータを記憶する記憶容量のバッファ部と、

入力データを、前記バッファ部に書き込むデータ書き込み制御部と、

前記バッファ部に記憶されているデータを読み出し、該読み出したデータに基づいて生成した出力データを出力するデータ読み出し制御部と、

前記データ書き込み制御部がデータを書き込む前記バッファ部内の記憶領域、および前記データ読み出し制御部がデータを読み出す前記バッファ部内の記憶領域を決定するバッファ領域決定部と、

を備え、

前記データ書き込み制御部は、

前記バッファ領域決定部によって決定された前記記憶領域に前記入力データを書き込み、前記入力データの書き込みが完了したときに、データの書き込みが完了したことを表すデータ書き込み完了信号を出力し、

前記データ読み出し制御部は、

前記バッファ領域決定部によって決定された前記記憶領域に記憶されているデータを読み出し、該読み出したデータに基づいて生成した出力データの出力が完了したときに、データの読み出しが完了したことを表すデータ読み出し完了信号を出力する、

ことを特徴とするデータ処理装置。 - 前記データ書き込み制御部は、

前記バッファ領域決定部によって決定された前記バッファ部内の書き込み可能領域に前記入力データを書き込み、予め定められた数の前記入力データの前記バッファ部への書き込みが完了したときに、データの書き込みが完了したと判定し、

前記データ読み出し制御部は、

前記バッファ領域決定部によって決定された前記バッファ部内の読み出し可能領域からデータを読み出し、予め定められた数の前記バッファ部からの読み出しが完了し、該読み出したデータに基づいて生成した出力データの出力が完了したときに、データの読み出しが完了したと判定し、

前記バッファ領域決定部は、

前記データ書き込み制御部による前記入力データの書き込み状態、および前記データ読み出し制御部によるデータの読み出し状態に応じて、前記バッファ部内の前記書き込み可能領域および前記読み出し可能領域を変更する、

ことを特徴とする請求項1に記載のデータ処理装置。 - 前記バッファ領域決定部は、

前記データ書き込み制御部によってデータが書き込まれた前記バッファ部内の前記記憶領域を、有効なデータが記憶され、該記憶されたデータを読み出すことができる前記読み出し可能領域に決定し、

前記データ読み出し制御部によってデータが読み出された前記バッファ部内の前記記憶領域を、空き領域であり、前記入力データを書き込むことができる前記書き込み可能領域に決定する、

ことを特徴とする請求項2に記載のデータ処理装置。 - 前記データ読み出し制御部は、

前記読み出したデータに基づいてフィルタ処理した出力データを生成するフィルタ処理部、

を備え、

前記記憶容量は、

前記フィルタ処理部がフィルタ処理を行う際に必要とするデータ数に基づいて決定する、

ことを特徴とする請求項3に記載のデータ処理装置。 - パイプライン接続された複数の画像処理モジュールを用いて、画像データを処理するデータ処理装置であって、前記画像処理モジュールは、前記画像データの領域を複数行から成る複数の重複ブロックに分割し、第1のブロックにおける最後の行の画像処理を行う際に必要とするデータ数と、該第1のブロックの次に処理を行う第2のブロックにおける最初の行の画像処理を行う際に必要とするデータ数とを合わせた数のデータを記憶する記憶容量のバッファ部と、入力データを、前記バッファ部に書き込むデータ書き込み制御部と、前記バッファ部に記憶されているデータを読み出し、該読み出したデータに基づいて生成した出力データを出力するデータ読み出し制御部と、前記データ書き込み制御部がデータを書き込む前記バッファ部内の記憶領域、および前記データ読み出し制御部がデータを読み出す前記バッファ部内の記憶領域を決定するバッファ領域決定部と、を有し、前記データ書き込み制御部が前記バッファ領域決定部によって決定された前記記憶領域に前記入力データを書き込み、前記入力データの書き込みが完了したときに、データの書き込みが完了したことを表すデータ書き込み完了信号と、前記データ読み出し制御部が前記バッファ領域決定部によって決定された前記記憶領域に記憶されているデータを読み出し、該読み出したデータに基づいて生成した出力データの出力が完了したときに、データの読み出しが完了したことを表すデータ読み出し完了信号と、をそれぞれ出力するデータ処理装置、

を備え、

前記データ書き込み完了信号が出力された後に、前記データ書き込み制御部による画像データの書き込みに係る設定を行い、

前記データ読み出し完了信号が出力された後に、前記データ読み出し制御部による画像データの読み出しに係る設定を行う、

ことを特徴とする画像処理装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010245478A JP5784299B2 (ja) | 2010-11-01 | 2010-11-01 | データ処理装置および画像処理装置 |

| US13/284,571 US8904069B2 (en) | 2010-11-01 | 2011-10-28 | Data processing apparatus and image processing apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010245478A JP5784299B2 (ja) | 2010-11-01 | 2010-11-01 | データ処理装置および画像処理装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012098883A JP2012098883A (ja) | 2012-05-24 |

| JP2012098883A5 JP2012098883A5 (ja) | 2013-11-28 |

| JP5784299B2 true JP5784299B2 (ja) | 2015-09-24 |

Family

ID=45997932

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010245478A Active JP5784299B2 (ja) | 2010-11-01 | 2010-11-01 | データ処理装置および画像処理装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8904069B2 (ja) |

| JP (1) | JP5784299B2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9465572B2 (en) | 2011-11-09 | 2016-10-11 | Microsoft Technology Licensing, Llc | Dynamic server-side image sizing for fidelity improvements |

| JP6238510B2 (ja) | 2012-07-27 | 2017-11-29 | キヤノン株式会社 | バッファ、バッファの制御方法、同期制御装置、同期制御方法、画像処理装置および画像処理方法 |

| JP6242064B2 (ja) * | 2013-03-28 | 2017-12-06 | オリンパス株式会社 | 画像処理装置 |

| JP6284332B2 (ja) * | 2013-10-02 | 2018-02-28 | オリンパス株式会社 | 画像処理装置、画像処理方法、および撮像装置 |

| JP2015130632A (ja) | 2014-01-08 | 2015-07-16 | 株式会社リコー | 画像処理装置、送受信システム、画像処理方法、およびプログラム |

| EP3136719A4 (en) * | 2014-04-24 | 2017-09-13 | Sony Corporation | Image processing apparatus and method and surgical operation system |

| JP6119682B2 (ja) * | 2014-06-27 | 2017-04-26 | 株式会社デンソー | 電子制御装置 |

| JP6580381B2 (ja) * | 2015-06-12 | 2019-09-25 | オリンパス株式会社 | 画像処理装置および画像処理方法 |

| JP6580380B2 (ja) * | 2015-06-12 | 2019-09-25 | オリンパス株式会社 | 画像処理装置および画像処理方法 |

| JP2017169186A (ja) * | 2016-03-14 | 2017-09-21 | 株式会社リコー | 画像処理装置、情報処理装置、画像処理システム及び画像処理方法 |

| WO2017179099A1 (ja) | 2016-04-11 | 2017-10-19 | オリンパス株式会社 | 画像処理装置 |

| JP6674309B2 (ja) * | 2016-04-18 | 2020-04-01 | キヤノン株式会社 | メモリ制御装置及びメモリ制御方法 |

| US10523864B2 (en) * | 2018-04-10 | 2019-12-31 | Facebook, Inc. | Automated cinematic decisions based on descriptive models |

| JP7176355B2 (ja) | 2018-10-31 | 2022-11-22 | 株式会社リコー | 画像処理装置、画像処理装置の制御方法およびプログラム |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR0121800B1 (ko) | 1992-05-08 | 1997-11-22 | 사또오 후미오 | 메모리 카드장치 |

| US5388074A (en) * | 1992-12-17 | 1995-02-07 | Vlsi Technology, Inc. | FIFO memory using single output register |

| JPH06275098A (ja) * | 1993-03-24 | 1994-09-30 | Mitsubishi Electric Corp | 半導体記憶装置 |

| US6112268A (en) | 1997-06-16 | 2000-08-29 | Matsushita Electric Industrial Co., Ltd. | System for indicating status of a buffer based on a write address of the buffer and generating an abort signal before buffer overflows |

| JP3917734B2 (ja) * | 1997-11-07 | 2007-05-23 | 富士通株式会社 | 半導体記憶装置 |

| US6330630B1 (en) * | 1999-03-12 | 2001-12-11 | Intel Corporation | Computer system having improved data transfer across a bus bridge |

| JP4179701B2 (ja) | 1999-04-28 | 2008-11-12 | オリンパス株式会社 | 画像処理装置 |

| JP3988340B2 (ja) * | 1999-11-29 | 2007-10-10 | セイコーエプソン株式会社 | 画像処理装置およびそれを備えた複写装置 |

| US6732223B1 (en) | 2000-04-03 | 2004-05-04 | Micron Technology, Inc. | Method and apparatus for address FIFO for high-bandwidth command/address busses in digital storage system |

| JP2001312373A (ja) * | 2000-04-21 | 2001-11-09 | Internatl Business Mach Corp <Ibm> | データの書き込み方法およびディスクドライブ装置 |

| JP2002099504A (ja) | 2000-09-26 | 2002-04-05 | Ricoh Co Ltd | データ転送装置、及び、データ転送方法 |

| JP4084922B2 (ja) * | 2000-12-22 | 2008-04-30 | 株式会社ルネサステクノロジ | 不揮発性記憶装置の書込み方法 |

| US7598983B2 (en) | 2001-10-23 | 2009-10-06 | Seiko Epson Corporation | Control of image output using image processing control data |

| JP4024649B2 (ja) | 2001-11-14 | 2007-12-19 | オリンパス株式会社 | 画像処理装置及び画像処理方法 |

| JP4164371B2 (ja) * | 2003-01-16 | 2008-10-15 | キヤノン株式会社 | データ処理装置、データ処理方法、プログラム及び記憶媒体 |

| KR100449807B1 (ko) | 2002-12-20 | 2004-09-22 | 한국전자통신연구원 | 호스트 버스 인터페이스를 갖는 데이터 전송 프로토콜제어 시스템 |

| JP2004206487A (ja) | 2002-12-26 | 2004-07-22 | Kyocera Mita Corp | Fifoメモリ回路 |

| WO2005008214A2 (en) * | 2003-07-07 | 2005-01-27 | Zetetic Institute | Apparatus and method for ellipsometric measurements with high spatial resolution |

| JP4286192B2 (ja) | 2003-08-25 | 2009-06-24 | オリンパス株式会社 | 画像処理装置及び画像処理方法 |

| US7895390B1 (en) | 2004-05-25 | 2011-02-22 | Qlogic, Corporation | Ensuring buffer availability |

| JP4810090B2 (ja) * | 2004-12-20 | 2011-11-09 | キヤノン株式会社 | データ処理装置 |

| US7444491B1 (en) | 2005-12-06 | 2008-10-28 | Nvidia Corporation | Automatic resource sharing between FIFOs |

| US7334061B2 (en) | 2005-12-20 | 2008-02-19 | Fujitsu Limited | Burst-capable interface buses for device-to-device communications |

| JP5449791B2 (ja) | 2009-02-02 | 2014-03-19 | オリンパス株式会社 | データ処理装置および画像処理装置 |

| US8732357B2 (en) * | 2010-10-28 | 2014-05-20 | International Business Machines Corporation | Apparatus and method for dynamically enabling and disabling write XFR—RDY |

-

2010

- 2010-11-01 JP JP2010245478A patent/JP5784299B2/ja active Active

-

2011

- 2011-10-28 US US13/284,571 patent/US8904069B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20120110224A1 (en) | 2012-05-03 |

| JP2012098883A (ja) | 2012-05-24 |

| US8904069B2 (en) | 2014-12-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5784299B2 (ja) | データ処理装置および画像処理装置 | |

| US11699067B2 (en) | Arithmetic processing apparatus and control method therefor | |

| JP5602532B2 (ja) | 画像処理装置および画像処理方法 | |

| JP5738618B2 (ja) | データ処理装置 | |

| JP6442867B2 (ja) | 画像処理装置、撮像装置、及び画像処理方法 | |

| JP5993267B2 (ja) | 画像処理装置 | |

| JP2015158894A (ja) | 画像形成装置、画像形成処理用データ転送制御方法、及び画像形成処理用データ転送制御プログラム | |

| WO2017179099A1 (ja) | 画像処理装置 | |

| US11775809B2 (en) | Image processing apparatus, imaging apparatus, image processing method, non-transitory computer-readable storage medium | |

| JP5675278B2 (ja) | データ処理装置および画像処理装置 | |

| JP6098366B2 (ja) | 画像データ処理装置及び画像データ処理方法 | |

| JP2008072585A (ja) | 演算処理用データ供給方法および画像処理装置 | |

| US10453166B2 (en) | Image processing device and image processing method | |

| JP5583563B2 (ja) | データ処理装置 | |

| JP6295619B2 (ja) | 画像処理装置及び方法、並びに電子機器 | |

| JP5537392B2 (ja) | データ処理装置 | |

| JP4482356B2 (ja) | Simdプロセッサを用いた画像処理方法及び画像処理装置 | |

| JP2007206924A (ja) | 演算処理システム | |

| JP7447519B2 (ja) | 画像処理装置、プログラム、及び画像処理方法 | |

| JP7310536B2 (ja) | 画像処理装置、画像処理方法及びプログラム | |

| JP7159555B2 (ja) | 画像処理装置、画像処理方法及びプログラム | |

| JP2017228849A (ja) | 画像処理装置、撮像装置、制御方法及びプログラム | |

| JP6543517B2 (ja) | 画像処理方法、画像処理装置及びプログラム | |

| JP2016103169A (ja) | 画像処理装置、画像処理方法および電子機器 | |

| JP5535101B2 (ja) | 画像処理装置および画像形成装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131015 Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20131015 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20131015 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140605 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140624 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140723 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20140724 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20141216 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150203 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20150204 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150707 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150722 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5784299 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |