JP6098366B2 - 画像データ処理装置及び画像データ処理方法 - Google Patents

画像データ処理装置及び画像データ処理方法 Download PDFInfo

- Publication number

- JP6098366B2 JP6098366B2 JP2013110560A JP2013110560A JP6098366B2 JP 6098366 B2 JP6098366 B2 JP 6098366B2 JP 2013110560 A JP2013110560 A JP 2013110560A JP 2013110560 A JP2013110560 A JP 2013110560A JP 6098366 B2 JP6098366 B2 JP 6098366B2

- Authority

- JP

- Japan

- Prior art keywords

- pixel data

- writing

- read

- reading

- parallel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N1/00—Scanning, transmission or reproduction of documents or the like, e.g. facsimile transmission; Details thereof

- H04N1/21—Intermediate information storage

- H04N1/2104—Intermediate information storage for one or a few pictures

- H04N1/2112—Intermediate information storage for one or a few pictures using still video cameras

- H04N1/2129—Recording in, or reproducing from, a specific memory area or areas, or recording or reproducing at a specific moment

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N1/00—Scanning, transmission or reproduction of documents or the like, e.g. facsimile transmission; Details thereof

- H04N1/21—Intermediate information storage

- H04N1/2104—Intermediate information storage for one or a few pictures

- H04N1/2112—Intermediate information storage for one or a few pictures using still video cameras

- H04N1/2129—Recording in, or reproducing from, a specific memory area or areas, or recording or reproducing at a specific moment

- H04N1/2133—Recording or reproducing at a specific moment, e.g. time interval or time-lapse

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N1/00—Scanning, transmission or reproduction of documents or the like, e.g. facsimile transmission; Details thereof

- H04N1/21—Intermediate information storage

- H04N1/2104—Intermediate information storage for one or a few pictures

- H04N1/2112—Intermediate information storage for one or a few pictures using still video cameras

- H04N1/2137—Intermediate information storage for one or a few pictures using still video cameras with temporary storage before final recording, e.g. in a frame buffer

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N1/00—Scanning, transmission or reproduction of documents or the like, e.g. facsimile transmission; Details thereof

- H04N1/21—Intermediate information storage

- H04N1/2104—Intermediate information storage for one or a few pictures

- H04N1/2112—Intermediate information storage for one or a few pictures using still video cameras

- H04N1/2137—Intermediate information storage for one or a few pictures using still video cameras with temporary storage before final recording, e.g. in a frame buffer

- H04N1/2141—Intermediate information storage for one or a few pictures using still video cameras with temporary storage before final recording, e.g. in a frame buffer in a multi-frame buffer

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N3/00—Scanning details of television systems; Combination thereof with generation of supply voltages

- H04N3/10—Scanning details of television systems; Combination thereof with generation of supply voltages by means not exclusively optical-mechanical

- H04N3/14—Scanning details of television systems; Combination thereof with generation of supply voltages by means not exclusively optical-mechanical by means of electrically scanned solid-state devices

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Image Input (AREA)

Description

ただ、撮像素子からラスタ走査順に入力される画素データを複数画素ずつ受け取り並列に出力するだけでは、各並列出力のデータの並びは、ラスタ走査順ではなく、飛び飛びのデータとなり、このままでは後段の回路で並列に処理することができない。そのため、ラインバッファなどを用いて、飛び飛びの並列データを後段の回路で並列処理できるように並べ替えることが行われる。

(第1の実施の形態)

図1は、第1の実施の形態の画像データ処理装置と画像データ処理方法の一例を示す図である。

図2は、画像データ処理装置が4画素ずつデータを受け取り4並列で処理を行う例を示す図である。

以上のような制御によれば、4×4個の記憶部12,12a,12bのうち、記憶部12a,12b以外の記憶部12は、ライトアクセスとリードアクセスが異なるタイミングで発生する。そのため、記憶部12には、ライトとリードを共通の端子で行う記憶装置(たとえば、1RWなどの1ポートRAM)が用いられる。一方、4の倍数ライン目の画素データの書き込み中に指定される最初のアドレスがある記憶部12a,12bは、ライトとリードを別々の端子を用いて行う記憶装置(たとえば、1R1Wなどの2ポートRAM)が用いられる。

(比較例)

図3は、並べ替え処理に用いられるRAMの例を示す図である。

図4、図5は、4つのRAMを用いた並べ替え処理の一例の様子を示すタイミングチャートである。

(第2の実施の形態)

図6は、第2の実施の形態の画像データ処理装置が適用される撮像装置の一例を示す図である。

撮像部60は、レンズや反射鏡などの撮像光学系61、CCD(Charge Coupled Device)などである撮像素子62、アンプやフィルタ、ADC(Analog to Digital Converter)などを含むアナログフロントエンド63(図6ではAFEと表記されている)を有する。

(ライン分割処理部72c)

図7は、ライン分割処理部の一例を示す図である。

RAM周辺部90は、記憶領域90a、入力信号制御部90b、出力信号制御部90cを有している。記憶領域90aは、生成する並列データの並列数(N)に対応して、N×N個のRAMを有している。記憶領域90aには、並列化部72bで並列化されたN並列の画素データや、ライトアドレス(WAD)や、リードアドレス(RAD)が入力される。

WADカウント用レジスタ91cは、ライトイネーブル信号WENがアサートされている間、ライトアドレスWADを、画像データ処理装置70の図示しないクロックに同期して、毎サイクルインクリメントする。

タイミング調整用カウンタ92bは、リードイネーブル信号RENがアサートされてから図示しないクロックのNサイクルに1回アサートされ、リードイネーブル信号RENを有効にする信号“1”を送出する。これによって、読み出しのためのRAMアクセスをNサイクルに1回にするタイミングの調整が行われる。

(RAM周辺部90)

図8は、並列数N=4としたときの、RAM周辺部の一例を示す図である。

図9では、入力信号制御部90bへの入力(input)として、STATEカウント用レジスタ91aの3ビットのカウント値STATEが示されている。また、入力信号制御部90bからの出力(output)として、ライト及びリード用の、列選択信号WSEL_C,RSEL_C、行選択信号WSEL_L,RSEL_Lが示されている。

図10では、出力信号制御部90cへの入力として、STATEカウント用レジスタ91aのカウント値STATEの最上位ビットSTATE[2]及びカウント値RCNTが示されている。また、出力信号制御部90cからの出力として、4つの並列データLINE0,LINE1,LINE2,LINE3が示されている。

(記憶領域90a)

図11は、並列数N=4としたときの、記憶領域の例を示す図である。

図12は、1RWの1ポートRAMに用いられるRAMI/Fの一例を示す図である。

AND回路121の2つの入力端子には、ライト用の列選択信号WSEL_Cと行選択信号WSEL_Lが入力される。AND回路122の2つの入力端子には、リード用の列選択信号RSEL_Cと行選択信号RSEL_Lが入力される。OR回路123の2つの入力端子には、AND回路121,122の出力信号が入力され、OR回路123の出力信号は、RAM100のチップイネーブル端子CEに入力される。インバータ回路124には、AND回路121の出力信号が入力され、インバータ回路124の出力信号は、RAM100のライトイネーブル端子WEに入力される。

図13は、1R1Wの2ポートRAMに用いられるRAMI/Fの一例を示す図である。

AND回路131の2つの入力端子には、ライト用の列選択信号WSEL_Cと行選択信号WSEL_Lが入力される。AND回路132の2つの入力端子には、リード用の列選択信号RSEL_Cと行選択信号RSEL_Lが入力される。AND回路131の出力信号は、RAM103のライトイネーブル端子CEIWに入力されるとともに、選択信号として選択回路133に供給される。AND回路132の出力信号は、RAM103のリードイネーブル端子CERAに入力されるとともに、選択信号として選択回路134に供給される。

図12、図13のようなRAMI/F120,130を用いることで、異なるタイプのRAMを同じように扱うことが可能となる。

(ライン分割処理部72cの動作)

図14は、並列データのライト処理の一例の流れを示すフローチャートである。

図15は、並列データのリード処理の一例の流れを示すフローチャートである。

次に、並列数N=4のときの、ライン分割処理部72cによるデータの並べ替え処理の一例を示す。

上から、画像データ処理装置70のクロック、水平同期信号、ライン分割処理部72cに入力される4並列の画素データ(センサ入力IN1〜IN4)、各RAM100〜115のライト及びリードの様子が示されている。

以降も同様のライト及びリードが行われる。

このように、本実施の形態の画像データ処理装置70及び画像データ処理方法によれば、小規模な回路で画素データを適切に並列化できる。

以下にN=3の場合、すなわち画像データ処理装置70が3画素ずつデータを受け取り3並列で処理を行う際の、ライン分割処理部72cにおける画素データのライトとリードの制御例を説明する。

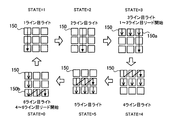

図19には、3×3個のRAMに対してライトまたはリードが行われる6つの状態の例が示されている。状態は、前述したカウント値STATEの値で表されている。

書き込み制御部91は、3×3個のRAM150から、列方向にRAM150を順に選択して、並列化部72bから3画素ずつ並列に入力される画素データを書き込ませる。これにより、まずは撮像素子62の水平方向の読み出しラインの画素データが、1ライン目から順に、列方向に選択されたRAM150にライトされる。

以上のような制御によれば、3×3個のRAM150のうち、カウント値STATE=3,0でライトアクセスとリードアクセスが同じタイミングで行われるRAM150a,150b以外のRAM150は、ライトとリードが異なるタイミングで行われる。そのため、RAM150a,150b以外のRAM150は、1RWなどの1ポートRAMを用いることができるため、回路面積を小さくできる。また、前のラインのリードが完了していないにも関わらず、新たなラインのデータのライトが同じアドレス上で発生することも抑制できるので、前のラインの画素データが上書きされてしまうことを防ぐことができる。

11 並列化部

12,12a,12b 記憶部

13 書き込み制御部

14 読み出し制御部

15 入力信号制御部

16 出力信号制御部

17 回路部

20 ライン分割処理部

30 撮像部

31 撮像素子

Claims (6)

- 撮像素子のN(N≧2)本の読み出しライン分の画素データを保持するN×N個の記憶部と、

前記N×N個の記憶部に含まれる記憶部を列方向または行方向に選択して、N画素ずつ前記画素データを書き込み、Nライン分の前記画素データの書き込みごとに、前記記憶部の選択方向を切り替える書き込み制御部と、

Nの倍数ライン目の前記画素データの書き込み時、当該書き込み時における前記記憶部の選択方向とは異なる方向でN個の前記記憶部を選択し、前記書き込まれた前記Nライン分の画素データの並列読み出しを開始する読み出し制御部と、を有し、

前記N×N個の記憶部のうち、前記Nの倍数ライン目の画素データの書き込みで最初に選択される記憶部は、読み出しと書き込みを異なる端子を用いて行い、他の記憶部は、読み出しと書き込みを共通の端子を用いて行う、

ことを特徴とする画像データ処理装置。 - 前記列方向または前記行方向で選択される前記N個の記憶部への1ライン分の前記画素データの書き込み開始前に、当該N個の記憶部に書き込まれている画素データの読み出しが完了している、ことを特徴とする請求項1に記載の画像データ処理装置。

- 前記読み出し制御部は、前記Nの倍数ラインの画素データのうち、1ワード分の書き込みが完了すると、前記並列読み出しを開始させる、ことを特徴とする請求項1または2に記載の画像データ処理装置。

- 前記撮像素子からの前記画素データの読み出し順で、前記画素データを受け取り、それぞれが、前記読み出し順に対してN画素ずつ飛び飛びのデータ並びとなるN並列の第1の並列データを生成する並列化部を有し、

書き込み時に選択される前記記憶部には、前記並列化部からの前記第1の並列データがN画素ずつ書き込まれ、

読み出し時に選択される前記N個の記憶部から読み出されるN並列の第2の並列データのそれぞれのデータ並びは、前記読み出し順である、

ことを特徴とする請求項1乃至3の何れか一項に記載の画像データ処理装置。 - 前記Nの倍数ラインの前記画素データの書き込みで最初に選択される記憶部と、前記他の記憶部とを、同じ制御信号またはアドレスで動作させる2種類のインターフェースを有することを特徴とする請求項1乃至4の何れか一項に記載の画像データ処理装置。

- 書き込み制御部が、撮像素子のN(N≧2)本の読み出しライン分の画素データを保持するN×N個の記憶部に含まれる記憶部を列方向または行方向に選択して、N画素ずつ前記画素データを書き込み、Nライン分の前記画素データの書き込みごとに、前記記憶部の選択方向を切り替え、

読み出し制御部が、Nの倍数ライン目の前記画素データの書き込み時、当該書き込み時における前記記憶部の選択方向とは異なる方向でN個の前記記憶部を選択し、前記書き込まれた前記Nライン分の画素データの並列読み出しを開始し、

前記N×N個の記憶部のうち、前記Nの倍数ライン目の画素データの書き込みで最初に選択される記憶部は、読み出しと書き込みを異なる端子を用いて行い、他の記憶部は、読み出しと書き込みを共通の端子を用いて行う、

ことを特徴とする画像データ処理方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013110560A JP6098366B2 (ja) | 2013-05-27 | 2013-05-27 | 画像データ処理装置及び画像データ処理方法 |

| US14/270,187 US9723231B2 (en) | 2013-05-27 | 2014-05-05 | Image data processing apparatus and method therefor for pixel data |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013110560A JP6098366B2 (ja) | 2013-05-27 | 2013-05-27 | 画像データ処理装置及び画像データ処理方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014229227A JP2014229227A (ja) | 2014-12-08 |

| JP2014229227A5 JP2014229227A5 (ja) | 2016-03-17 |

| JP6098366B2 true JP6098366B2 (ja) | 2017-03-22 |

Family

ID=51935153

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013110560A Expired - Fee Related JP6098366B2 (ja) | 2013-05-27 | 2013-05-27 | 画像データ処理装置及び画像データ処理方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9723231B2 (ja) |

| JP (1) | JP6098366B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6579744B2 (ja) * | 2014-11-28 | 2019-09-25 | キヤノン株式会社 | 撮像装置、撮像システム、撮像装置の駆動方法、及び撮像装置の検査方法 |

| US10102892B1 (en) * | 2017-06-01 | 2018-10-16 | Intel Corporation | RAM-based shift register with embedded addressing |

| JP7380267B2 (ja) * | 2020-01-31 | 2023-11-15 | セイコーエプソン株式会社 | 印刷制御装置、印刷方法および印刷制御プログラム |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0369090A (ja) * | 1989-08-07 | 1991-03-25 | Oki Electric Ind Co Ltd | 画像用デュアルポートram |

| US5293236A (en) * | 1991-01-11 | 1994-03-08 | Fuji Photo Film Co., Ltd. | Electronic still camera including an EEPROM memory card and having a continuous shoot mode |

| JP3374988B2 (ja) * | 1992-12-22 | 2003-02-10 | 富士ゼロックス株式会社 | 画像データ読取り方法 |

| JP3618826B2 (ja) | 1994-07-25 | 2005-02-09 | キヤノン株式会社 | 画像信号処理装置及び方法 |

| US5650862A (en) * | 1994-07-25 | 1997-07-22 | Canon Kabushiki Kaisha | Image signal processing apparatus with improved pixel parallel/line parallel conversion |

| JP3105168B2 (ja) * | 1996-06-19 | 2000-10-30 | 株式会社東芝 | 画像形成装置および画像処理方法 |

| JPH11145851A (ja) * | 1997-11-07 | 1999-05-28 | Nec Corp | インタリーブ回路 |

| JP4097852B2 (ja) | 1999-08-26 | 2008-06-11 | 株式会社フィリップスエレクトロニクスジャパン | データ書込読出方法、デインターリーブ方法、データ処理方法、メモリ、及びメモリ駆動装置 |

| US6801674B1 (en) * | 2001-08-30 | 2004-10-05 | Xilinx, Inc. | Real-time image resizing and rotation with line buffers |

| US7379609B2 (en) * | 2002-07-19 | 2008-05-27 | Samsung Electronics Co., Ltd. | Image processing apparatus and method for conversion between raster and block formats |

| JP4818854B2 (ja) * | 2006-09-06 | 2011-11-16 | 京セラ株式会社 | 画像表示装置、電子機器、表示制御装置、及び表示制御方法 |

| US7920191B2 (en) | 2006-12-08 | 2011-04-05 | Casio Computer Co., Ltd. | Image capturing apparatus in which pixel charge signals are divided and output in a different order than an arrangement of pixels on an image capturing element and then rearranged and stored in a same order as the arrangement of the pixels on the image capturing element, and method thereof |

| JP4983359B2 (ja) | 2006-12-08 | 2012-07-25 | カシオ計算機株式会社 | 撮像装置及び撮像方法 |

| TWI328390B (en) * | 2006-12-22 | 2010-08-01 | Sunplus Technology Co Ltd | Method for accessing image data and method for accessing yuv420 image data thereof |

| CN101996550A (zh) * | 2009-08-06 | 2011-03-30 | 株式会社东芝 | 用于显示图像的半导体集成电路 |

| US20120182442A1 (en) * | 2011-01-14 | 2012-07-19 | Graham Kirsch | Hardware generation of image descriptors |

| US8953070B2 (en) * | 2011-12-16 | 2015-02-10 | University Of Saskatchewan | Apparatus, methods and systems for randomly accessing pixel data from streaming image sensor data |

| US9232139B2 (en) * | 2012-07-24 | 2016-01-05 | Apple Inc. | Image stabilization using striped output transformation unit |

-

2013

- 2013-05-27 JP JP2013110560A patent/JP6098366B2/ja not_active Expired - Fee Related

-

2014

- 2014-05-05 US US14/270,187 patent/US9723231B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US9723231B2 (en) | 2017-08-01 |

| JP2014229227A (ja) | 2014-12-08 |

| US20140347518A1 (en) | 2014-11-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8904069B2 (en) | Data processing apparatus and image processing apparatus | |

| JP3761061B2 (ja) | データ処理システムおよびデータ処理方法 | |

| US11775809B2 (en) | Image processing apparatus, imaging apparatus, image processing method, non-transitory computer-readable storage medium | |

| JP6098366B2 (ja) | 画像データ処理装置及び画像データ処理方法 | |

| US9026697B2 (en) | Data processing apparatus | |

| KR20170049191A (ko) | 이미지 처리 장치 및 이미지 처리 방법 | |

| US10719458B2 (en) | Data transfer device, image processing device, and imaging device | |

| WO2017216840A1 (ja) | メモリアクセス制御装置、画像処理装置、および撮像装置 | |

| JP6442867B2 (ja) | 画像処理装置、撮像装置、及び画像処理方法 | |

| US7254283B1 (en) | Image processor processing image data in parallel with a plurality of processors | |

| US7103702B2 (en) | Memory device | |

| US8150215B2 (en) | Routable image pipeline device | |

| KR101608347B1 (ko) | 디지털 영상 신호 처리 장치 및 방법 | |

| JP4895355B2 (ja) | メモリ制御装置 | |

| JP5675278B2 (ja) | データ処理装置および画像処理装置 | |

| JP2008172410A (ja) | 撮像装置、画像処理装置、画像処理方法、画像処理方法のプログラム及び画像処理方法のプログラムを記録した記録媒体 | |

| JP2014229227A5 (ja) | ||

| JP2021157295A (ja) | メモリ制御装置 | |

| JP5537392B2 (ja) | データ処理装置 | |

| US12379926B2 (en) | Image processing apparatus with multibank registers for storing source, destination, and setting information for operational circuits | |

| US20060047866A1 (en) | Computer system having direct memory access controller | |

| JP7113368B2 (ja) | 撮像装置及びカメラシステム | |

| JP4635482B2 (ja) | 調停装置、調停方法、調停方法のプログラム、調停方法のプログラムを記録した記録媒体及び電子スチルカメラ | |

| TWI424372B (zh) | Selectable image line path means | |

| JP3977156B2 (ja) | 撮像装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20150611 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160128 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160128 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20161209 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170124 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170206 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6098366 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |