JP5693375B2 - 半導体発光素子 - Google Patents

半導体発光素子 Download PDFInfo

- Publication number

- JP5693375B2 JP5693375B2 JP2011114721A JP2011114721A JP5693375B2 JP 5693375 B2 JP5693375 B2 JP 5693375B2 JP 2011114721 A JP2011114721 A JP 2011114721A JP 2011114721 A JP2011114721 A JP 2011114721A JP 5693375 B2 JP5693375 B2 JP 5693375B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- light emitting

- electrode

- bump electrode

- metal layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 88

- 239000010410 layer Substances 0.000 claims description 259

- 229910052751 metal Inorganic materials 0.000 claims description 70

- 239000002184 metal Substances 0.000 claims description 70

- 239000011241 protective layer Substances 0.000 claims description 22

- 238000000034 method Methods 0.000 claims description 18

- 239000000463 material Substances 0.000 claims description 12

- 238000007747 plating Methods 0.000 claims description 11

- 238000009713 electroplating Methods 0.000 claims description 10

- 239000010931 gold Substances 0.000 description 18

- 239000000758 substrate Substances 0.000 description 18

- 230000005496 eutectics Effects 0.000 description 17

- JVPLOXQKFGYFMN-UHFFFAOYSA-N gold tin Chemical compound [Sn].[Au] JVPLOXQKFGYFMN-UHFFFAOYSA-N 0.000 description 16

- 230000017525 heat dissipation Effects 0.000 description 16

- 229910052594 sapphire Inorganic materials 0.000 description 13

- 239000010980 sapphire Substances 0.000 description 13

- 230000015572 biosynthetic process Effects 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 6

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 5

- 229910052737 gold Inorganic materials 0.000 description 5

- 229920005989 resin Polymers 0.000 description 5

- 239000011347 resin Substances 0.000 description 5

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- QTBSBXVTEAMEQO-UHFFFAOYSA-N acetic acid Substances CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 4

- 239000000428 dust Substances 0.000 description 4

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 238000004806 packaging method and process Methods 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 230000002265 prevention Effects 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 238000002310 reflectometry Methods 0.000 description 2

- 238000001771 vacuum deposition Methods 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- ZCYVEMRRCGMTRW-UHFFFAOYSA-N 7553-56-2 Chemical compound [I] ZCYVEMRRCGMTRW-UHFFFAOYSA-N 0.000 description 1

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000011889 copper foil Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- QOSATHPSBFQAML-UHFFFAOYSA-N hydrogen peroxide;hydrate Chemical compound O.OO QOSATHPSBFQAML-UHFFFAOYSA-N 0.000 description 1

- 229910052740 iodine Inorganic materials 0.000 description 1

- 239000011630 iodine Substances 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 229920002050 silicone resin Polymers 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/40—Materials therefor

- H01L33/405—Reflective materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/44—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the coatings, e.g. passivation layer or anti-reflective coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/64—Heat extraction or cooling elements

- H01L33/642—Heat extraction or cooling elements characterized by the shape

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Led Device Packages (AREA)

- Led Devices (AREA)

Description

12 回路基板

13 プラス電極

14 マイナス電極

15 LED装置

21 N側バンプ

21a 金錫共晶層

21b メッキ金属層

21c アンダーバンプメタル層

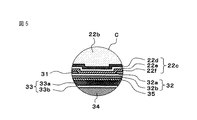

21d Au層

21e TiW層

21f Al層(高反射性金属層)

22 P側バンプ

22a 金錫共晶層

22b メッキ金属層

22c アンダーバンプメタル層

22d Au層

22e TiW層

22f Al層(高反射性金属層)

23、25 放熱バンプ

24 ダイ

31 保護層

32 p型半導体層

33 n型半導体層

34 サファイア基板

35 発光層

Claims (7)

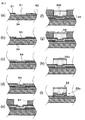

- 回路基板にフリップチップ実装する半導体発光素子であって、

発光層を含む半導体層と、

前記半導体層を保護するための保護層と、

前記半導体層を回路基板と接続するためのN側バンプ電極と、

前記半導体層を回路基板と接続するためのP側バンプ電極と、を有し、

前記N側バンプ電極及び前記P側バンプ電極のそれぞれが、アンダーバンプメタル層及び電解メッキ法によって形成されたメッキ金属層を含み、

前記アンダーバンプメタル層が、前記電解メッキ法が適用された際に前記メッキ金属層の下に残存したものであって、前記半導体層側に配置された高反射性金属層及び前記半導体層と反対側に配置された金属層を含み、

前記メッキ金属層の厚さが3μm以上、30μm以下であり、

前記発光層と前記保護層との間に配置された材料は透明であり、

前記N側バンプ電極及び前記P側バンプ電極は、前記発光層の上に配置されており、

前記保護層は、前記アンダーバンプメタル層と前記半導体層との間に配置される、

ことを特徴とする半導体発光素子。 - 前記メッキ金属層の厚さが10μm以上、30μm以下である、請求項1に記載の半導体発光素子。

- 前記高反射性金属層はAl層またはAg層である、請求項1又は2に記載の半導体発光素子。

- 前記P側バンプ電極及び前記N側バンプ電極の平面形状と、前記P側バンプ電極及び前記N側バンプ電極に含まれるそれぞれの前記アンダーバンプメタル層の平面形状が等しい、請求項1〜3の何れか一項に記載の半導体発光素子。

- 前記アンダーバンプメタル層は前記メッキ金属層が占める領域よりも広い面積を占める、請求項1〜3の何れか一項に記載の半導体発光素子。

- 前記保護層は開口部を有し、

開口部を有し且つ前記半導体層を被覆するための保護層を更に有し、前記開口部において前記N側バンプ電極及び前記P側バンプ電極のそれぞれが前記半導体層と電気的に接続される、請求項1〜5の何れか一項に記載の半導体発光素子。 - 前記N側バンプ電極が前記発光層と平面的に重なるように配置されている、請求項1〜6の何れか一項に記載の半導体発光素子。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011114721A JP5693375B2 (ja) | 2010-05-28 | 2011-05-23 | 半導体発光素子 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010122760 | 2010-05-28 | ||

| JP2010122760 | 2010-05-28 | ||

| JP2011114721A JP5693375B2 (ja) | 2010-05-28 | 2011-05-23 | 半導体発光素子 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2012009848A JP2012009848A (ja) | 2012-01-12 |

| JP2012009848A5 JP2012009848A5 (ja) | 2014-02-27 |

| JP5693375B2 true JP5693375B2 (ja) | 2015-04-01 |

Family

ID=45021351

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011114721A Active JP5693375B2 (ja) | 2010-05-28 | 2011-05-23 | 半導体発光素子 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8581285B2 (ja) |

| JP (1) | JP5693375B2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5414627B2 (ja) * | 2010-06-07 | 2014-02-12 | 株式会社東芝 | 半導体発光装置及びその製造方法 |

| CN103177662B (zh) * | 2011-12-21 | 2015-01-21 | 四川柏狮光电技术有限公司 | 高密度全彩led显示点阵模块 |

| EP2816621A4 (en) * | 2012-02-15 | 2015-10-21 | Panasonic Ip Man Co Ltd | LIGHT-EMITTING DEVICE AND METHOD OF MANUFACTURING THEREOF |

| DE102012213566A1 (de) * | 2012-08-01 | 2014-02-06 | Robert Bosch Gmbh | Verfahren zum Herstellen eines Bondpads zum Thermokompressionsbonden und Bondpad |

| DE102013103079A1 (de) * | 2013-03-26 | 2014-10-02 | Osram Opto Semiconductors Gmbh | Optoelektronischer Halbleiterchip und Verfahren zur Herstellung eines optoelektronischen Halbleiterchips |

| US20150325748A1 (en) * | 2014-05-07 | 2015-11-12 | Genesis Photonics Inc. | Light emitting device |

| TWI641285B (zh) | 2014-07-14 | 2018-11-11 | 新世紀光電股份有限公司 | 發光模組與發光單元的製作方法 |

| CN105895772A (zh) | 2015-02-17 | 2016-08-24 | 新世纪光电股份有限公司 | 发光二极管芯片 |

| JP6434878B2 (ja) * | 2015-09-10 | 2018-12-05 | 株式会社東芝 | 発光装置 |

| CN105226177B (zh) * | 2015-10-13 | 2018-03-02 | 厦门市三安光电科技有限公司 | 倒装led芯片的共晶电极结构及倒装led芯片 |

| JP6387973B2 (ja) * | 2016-01-27 | 2018-09-12 | 日亜化学工業株式会社 | 発光装置 |

| JP6504221B2 (ja) * | 2016-09-29 | 2019-04-24 | 日亜化学工業株式会社 | 発光装置の製造方法 |

| JP7256382B2 (ja) * | 2019-04-26 | 2023-04-12 | 日亜化学工業株式会社 | 発光装置の製造方法 |

| JP7491769B2 (ja) | 2020-08-04 | 2024-05-28 | 株式会社ジャパンディスプレイ | 回路基板、ledモジュール及び表示装置、並びにledモジュールの作製方法及び表示装置の作製方法 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5134460A (en) * | 1986-08-11 | 1992-07-28 | International Business Machines Corporation | Aluminum bump, reworkable bump, and titanium nitride structure for tab bonding |

| JP3130292B2 (ja) | 1997-10-14 | 2001-01-31 | 松下電子工業株式会社 | 半導体発光装置及びその製造方法 |

| US6936859B1 (en) * | 1998-05-13 | 2005-08-30 | Toyoda Gosei Co., Ltd. | Light-emitting semiconductor device using group III nitride compound |

| JP3896704B2 (ja) * | 1998-10-07 | 2007-03-22 | 松下電器産業株式会社 | GaN系化合物半導体発光素子 |

| JP4024994B2 (ja) | 2000-06-30 | 2007-12-19 | 株式会社東芝 | 半導体発光素子 |

| TWI239578B (en) * | 2002-02-21 | 2005-09-11 | Advanced Semiconductor Eng | Manufacturing process of bump |

| JP2004356129A (ja) * | 2003-05-27 | 2004-12-16 | Nichia Chem Ind Ltd | 半導体装置及びその製造方法 |

| KR100546346B1 (ko) * | 2003-07-23 | 2006-01-26 | 삼성전자주식회사 | 재배선 범프 형성방법 및 이를 이용한 반도체 칩과 실장구조 |

| TWI220578B (en) * | 2003-09-16 | 2004-08-21 | Opto Tech Corp | Light-emitting device capable of increasing light-emitting active region |

| TWI257714B (en) | 2004-10-20 | 2006-07-01 | Arima Optoelectronics Corp | Light-emitting device using multilayer composite metal plated layer as flip-chip electrode |

| DE102005051857A1 (de) * | 2005-05-25 | 2007-02-22 | Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. | UBM-PAD, Lötkontakt und Verfahren zur Herstellung einer Lötverbindung |

| TW200644261A (en) * | 2005-06-06 | 2006-12-16 | Megica Corp | Chip-package structure and manufacturing process thereof |

| US8148822B2 (en) * | 2005-07-29 | 2012-04-03 | Megica Corporation | Bonding pad on IC substrate and method for making the same |

| US20090173956A1 (en) * | 2007-12-14 | 2009-07-09 | Philips Lumileds Lighting Company, Llc | Contact for a semiconductor light emitting device |

| TWI447870B (zh) * | 2008-02-20 | 2014-08-01 | Chipmos Technologies Inc | 用於一半導體積體電路之導電結構 |

-

2011

- 2011-05-23 JP JP2011114721A patent/JP5693375B2/ja active Active

- 2011-05-27 US US13/117,555 patent/US8581285B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US8581285B2 (en) | 2013-11-12 |

| US20110291141A1 (en) | 2011-12-01 |

| JP2012009848A (ja) | 2012-01-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5693375B2 (ja) | 半導体発光素子 | |

| JP7384848B2 (ja) | 半導体発光素子の製造方法 | |

| JP6530442B2 (ja) | 反射構造を有する半導体発光ダイオードおよびその製造方法 | |

| US9859466B2 (en) | Light-emitting diode module having light-emitting diode joined through solder paste and light-emitting diode | |

| US10950758B2 (en) | Light-emitting device with reflective layer | |

| KR101546929B1 (ko) | 발광 다이오드 및 그것을 갖는 발광 다이오드 모듈 | |

| JP5551649B2 (ja) | 発光素子 | |

| JP6413460B2 (ja) | 発光装置及び発光装置の製造方法 | |

| JP6384202B2 (ja) | 発光装置の製造方法 | |

| CN111987208B (zh) | 发光元件 | |

| KR20150078296A (ko) | 신뢰성이 향상된 발광 소자 | |

| JP2013045943A (ja) | 半導体発光装置及びその製造方法 | |

| JP2012015437A (ja) | 半導体発光装置 | |

| JP5755102B2 (ja) | 半導体発光素子 | |

| JP2006073618A (ja) | 光学素子およびその製造方法 | |

| KR20160065349A (ko) | 질화물 반도체 발광 칩 및 이를 갖는 발광 소자 | |

| JP5767934B2 (ja) | 半導体発光素子の製造方法 | |

| JP5996045B2 (ja) | 半導体発光素子 | |

| KR20150014135A (ko) | 발광 다이오드 및 그것을 갖는 발광 다이오드 모듈 | |

| US20110261847A1 (en) | Light emitting devices | |

| CN108365073A (zh) | 一种反射层金属结构及其制造方法 | |

| CN108365072A (zh) | 一种led芯片及其制造方法 | |

| JP6940739B2 (ja) | 発光素子及び発光素子の製造方法 | |

| TW202339311A (zh) | 發光元件 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140114 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140114 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140423 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140513 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140709 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150106 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150203 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5693375 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |