JP5671237B2 - 半導体素子検査用基板 - Google Patents

半導体素子検査用基板 Download PDFInfo

- Publication number

- JP5671237B2 JP5671237B2 JP2010004970A JP2010004970A JP5671237B2 JP 5671237 B2 JP5671237 B2 JP 5671237B2 JP 2010004970 A JP2010004970 A JP 2010004970A JP 2010004970 A JP2010004970 A JP 2010004970A JP 5671237 B2 JP5671237 B2 JP 5671237B2

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- protruding member

- metallized layer

- semiconductor element

- stud

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Electric Connection Of Electric Components To Printed Circuits (AREA)

- Measuring Leads Or Probes (AREA)

- Testing Or Measuring Of Semiconductors Or The Like (AREA)

Description

(3)請求項3の発明は、多層セラミック基板の表面にメタライズ層を備えるとともに、該メタライズ層上にロウ材層を介して基板表面から突出する突出部材が接合され、該突出部材は半導体素子検査用基板を基板保持装置に固定するためのスタッドである半導体素子検査用基板であって、前記メタライズ層の表面積Mと前記突出部材の底面積Sとの比(M/S)が、1.8以上、4.0以下であることを特徴とする。

本発明は、多層セラミック基板のセラミック材料を例示したものである。つまり、セラミック成分がガラスセラミックである場合は、ガラスを含まない場合に比べて強度が弱いが、本発明では、そのような強度が弱い材料であっても、クラック等の発生を抑制することができる。

(7)請求項7の発明では、前記スタッドは、前記基板表面に接合される面の面積が60〜110mm2であることを特徴とする。

本発明は、スタッドの基板表面に接合される面の面積を例示している。

・前記突出部材は、多層セラミック基板の表面に接合されてその表面より(例えば垂直に)外側方向に突出する部材であり、その材料としては、例えばコバールなどの金属を採用できる。また、その形状としては、その底面が円形等の柱状(円柱状)の部材を採用できる。

・前記ロウ材の材料としては、Au−Sn系、Ag−Cu系等の材料を採用できる。

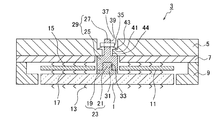

図1に示す様に、本実施例の半導体素子検査用基板1は、半導体素子の一つであるシリコンウェハー(図示せず)の電気検査を行う場合に、基板保持装置3に固定されて使用されるものである。

この半導体素子検査用基板1の下面側には、シリコンウェハーに接触する接触端子13が設けられており、インターポーザー11の両側にも、接触端子15、17が設けられている。なお、インターポーザー11の各面側の接触端子15、17は、それぞれ配線ボード7と半導体素子検査用基板1とに接触している。

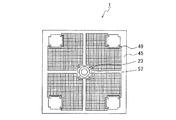

図2に示す様に、半導体素子検査用基板1は、例えば縦96.25mm×横91.17mm×厚み4.45mmの長方形の板状の多層セラミック基板45を主体とし、この多層セラミック基板45の一方の表面に、前記スタッド23がAgとCuを含むロウ材によってロウ付けされたものである。

このガラスセラミック層47は、例えばガラス成分とセラミック成分との混合物を、例えば800〜1050℃程度の低温にて焼成した低温焼成のガラスセラミックで構成されている。詳しくは、各ガラスセラミック層47(従って多層セラミック基板45のガラスセラミック部分)は、ムライト及びホウケイ酸系ガラスをセラミックの主成分とするガラスセラミックからなる。

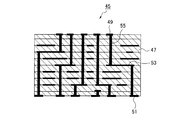

更に、前記多層セラミック基板45の表面には、多数の電極49以外に、基板表面の中央と四隅に、メタライズ層57が形成されている。

即ち、図6(b)に示す様に、フィレット61の底辺の長さFとフィレット61の高さHとの比(F/H)が、4.3以上である。

(1)まず、多層セラミック基板45の製造方法を説明する。

そして、アルミナ製のポットに、ホウケイ酸ガラス粉末とムライト粉末とを、質量比で50:50、総量1000g投入するとともに、アクリル樹脂を120g投入した。更に、適当なスラリー粘度とシート強度を持たせるのに必要な量の溶剤(MEK:メチルエチルケトン)と可塑剤(DOP)を上記ポットに入れ、3時間混合することにより、セラミックスラリーを得た。

・また、前記第1グリーンシートを作製する工程とは別に、拘束シート(第2グリーンシート)を作製するために、セラミック原料粉末として、平均粒径:2μm、比表面積:1m2/gのアルミナ粉末を用意した。

そして、前記第1グリーンシートと同様に、アルミナ製のポットに、アルミナ粉末を1000g、アクリル樹脂を120g投入し、更に、スラリー粘度とシート強度を持たせるために、必要な量の溶剤(MEK)と可塑剤(DOP)を投入し、3時間混合してスラリーを得た。

・次に、前記第1グリーンシートに、ビアホールを形成し、そのビアホールに、例えばAg系ペーストを充填した。また、第1グリーンシートの表面の必要な箇所に、Ag系ペーストを用いて、印刷によって(内部配線層53となる)導電パターンを形成した。

・次に、プレス機にて、第2セラミックシートを積層した積層体の積層方向の両側から0.2MPaの押圧力を加えながら、850℃にて30分間焼成(脱脂焼成)した。

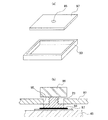

図7に示す様に、研磨した焼結体の表面に、スパッタによって、Ti薄膜71、Cu薄膜73を順次形成した。

次に、メタライズ層57のパターンの部分に、電解メッキによってCu層77、Ni層79を形成した。

その後、残ったパターン部分の周囲に、電解メッキによって、Ni層81、Au層83を形成して、メタライズ層57を完成した。

図8(b)に示す様に、メタライズ層57の上に、80Au/20Snのロウ材箔(プリフォーム)91を配置し、図8(a)に示す様な、カーボン製のロウ付け治具の容器93内に多層セラミック基板45をセットし、貫通孔95を有するカーボン製の蓋97をした。

そして、還元雰囲気のベルト炉中にて、ロウ付けした。詳しくは、300℃以上で30分間保持し、その後冷却した。

d)この様にして製造された本実施例の半導体素子検査用基板1においては、スタッド23の底面の面積中心を中心にして、メタライズ層57の半径方向の長さMLと、ロウ材層59の底面の同じ半径方向の長さRLとの差(ML−RL)が、スタッド23の外周の全周にわたり0.65mm以上であるので、ロウ付け工程における冷却段階で、ロウ材端部に発生する応力がメタライズ層57中で緩和されることにより、後に実験例の表1及び表4に示す様に、スタッド23の接合強度を十分に確保することができる。

ここでは、スタッドとして、前記実施例1と同様に、底面が円形のものを用い、メタライズ層も同様に、十字形状のパターンのものを採用した。なお、寸法等、特に記載しない事項は、前記実施例1と同様である。

ここでは、スタッドとして、前記実施例1と同様に、底面が円形のものを用い、メタライズ層も同様に、十字形状のパターンのものを採用した。なお、寸法等、特に記載しない事項は、前記実施例1と同様である。

ここでは、スタッドとして、前記実施例1と同様に、底面が円形のものを用い、メタライズ層も同様に、十字形状のパターンのものを採用した。なお、寸法等、特に記載しない事項は、前記実施例1と同様である。

<実験例>

次に、本発明の効果を確認するために行った実験例について説明する。

なお、ここで、表6のデータは、請求項2の比較例に対応する値を示しており、表7のデータは、請求項3の比較例に対する値を示している。また、表8のデータは、請求項1の比較例として、(ML−RL)が0.65mm未満の例を示している。また、同表8のデータは、請求項4の比較例として、ML/SLが1.4未満の例と、請求項5の比較例として、ML/RLが1.1未満の例を示している。なお、比較例のメタライズ層、ロウ材層、スタッドの底面は、全て円形である。

尚、本発明は前記実施例になんら限定されるものではなく、本発明を逸脱しない範囲において種々の態様で実施しうることはいうまでもない。

23…スタッド

45…多層セラミック基板

47…ガラスセラミック層

49、51…電極

57…メタライズ層

59…ロウ材層

Claims (7)

- 多層セラミック基板の表面にメタライズ層を備えるとともに、該メタライズ層上にロウ材層を介して基板表面から突出する突出部材が接合され、該突出部材は半導体素子検査用基板を基板保持装置に固定するためのスタッドである半導体素子検査用基板であって、

前記突出部材の底面の面積中心を中心にして、前記メタライズ層の径方向の長さMLと、前記ロウ材層の底面の同じ径方向の長さRLとの差(ML−RL)が、前記突出部材の外周の全周にわたって0.65mm以上であることを特徴とする半導体素子検査用基板。 - 多層セラミック基板の表面にメタライズ層を備えるとともに、該メタライズ層上にロウ材層を介して基板表面から突出する突出部材が接合され、該突出部材は半導体素子検査用基板を基板保持装置に固定するためのスタッドである半導体素子検査用基板であって、

前記突出部材の外周における前記ロウ材層のフィレットの底辺の長さFとフィレットの高さHとの比(F/H)が、4.3以上であることを特徴とする半導体素子検査用基板。 - 多層セラミック基板の表面にメタライズ層を備えるとともに、該メタライズ層上にロウ材層を介して基板表面から突出する突出部材が接合され、該突出部材は半導体素子検査用基板を基板保持装置に固定するためのスタッドである半導体素子検査用基板であって、

前記メタライズ層の表面積Mと前記突出部材の底面積Sとの比(M/S)が、1.8以上、4.0以下であることを特徴とする半導体素子検査用基板。 - 多層セラミック基板の表面にメタライズ層を備えるとともに、該メタライズ層上にロウ材層を介して基板表面から突出する突出部材が接合され、該突出部材は半導体素子検査用基板を基板保持装置に固定するためのスタッドである半導体素子検査用基板であって、

前記半導体素子検査用基板を厚み方向に見た場合に、前記突出部材の底面の面積中心を中心にして、前記メタライズ層の径方向の長さMLと前記突出部材の底面の同じ径方向の長さSLとの比(ML/SL)が1.4以上となる範囲が、前記突出部材の中心角の62%以上であることを特徴とする半導体素子検査用基板。 - 多層セラミック基板の表面にメタライズ層を備えるとともに、該メタライズ層上にロウ材層を介して基板表面から突出する突出部材が接合され、該突出部材は半導体素子検査用基板を基板保持装置に固定するためのスタッドである半導体素子検査用基板であって、

前記半導体素子検査用基板を厚み方向に見た場合に、前記突出部材の底面の面積中心を中心にして、前記メタライズ層の径方向の長さMLと前記ロウ材層の底面の同じ径方向の長さRLとの比(ML/RL)が1.1以上となる範囲が、前記突出部材の中心角の62%以上であることを特徴とする半導体素子検査用基板。 - 前記多層セラミック基板は、ガラスセラミックからなることを特徴とする請求項1〜5のいずれか1項に記載の半導体素子検査用基板。

- 前記スタッドは、前記基板表面に接合される面の面積が60〜110mm2であることを特徴とする請求項1〜5のいずれか1項に記載の半導体素子検査用基板。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010004970A JP5671237B2 (ja) | 2009-01-15 | 2010-01-13 | 半導体素子検査用基板 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009006754 | 2009-01-15 | ||

| JP2009006754 | 2009-01-15 | ||

| JP2010004970A JP5671237B2 (ja) | 2009-01-15 | 2010-01-13 | 半導体素子検査用基板 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014177588A Division JP2015025812A (ja) | 2009-01-15 | 2014-09-02 | 半導体素子検査用基板 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010185869A JP2010185869A (ja) | 2010-08-26 |

| JP5671237B2 true JP5671237B2 (ja) | 2015-02-18 |

Family

ID=42766600

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010004970A Active JP5671237B2 (ja) | 2009-01-15 | 2010-01-13 | 半導体素子検査用基板 |

| JP2014177588A Withdrawn JP2015025812A (ja) | 2009-01-15 | 2014-09-02 | 半導体素子検査用基板 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014177588A Withdrawn JP2015025812A (ja) | 2009-01-15 | 2014-09-02 | 半導体素子検査用基板 |

Country Status (1)

| Country | Link |

|---|---|

| JP (2) | JP5671237B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019049498A (ja) * | 2017-09-12 | 2019-03-28 | 日本特殊陶業株式会社 | 電子部品検査装置用配線基板 |

| JP7189047B2 (ja) * | 2019-02-22 | 2022-12-13 | 日本特殊陶業株式会社 | 電気検査用基板 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4672739A (en) * | 1985-04-11 | 1987-06-16 | International Business Machines Corporation | Method for use in brazing an interconnect pin to a metallization pattern situated on a brittle dielectric substrate |

| JPH0777989B2 (ja) * | 1989-01-25 | 1995-08-23 | 同和鉱業株式会社 | セラミックスと金属の接合体の製造法 |

| JP2629635B2 (ja) * | 1995-02-23 | 1997-07-09 | 日本電気株式会社 | 放熱用金属板付半導体装置 |

| JP2006337229A (ja) * | 2005-06-03 | 2006-12-14 | Micronics Japan Co Ltd | 通電試験用プローブ |

| JP5016342B2 (ja) * | 2006-03-27 | 2012-09-05 | 京セラ株式会社 | 太陽電池モジュール |

-

2010

- 2010-01-13 JP JP2010004970A patent/JP5671237B2/ja active Active

-

2014

- 2014-09-02 JP JP2014177588A patent/JP2015025812A/ja not_active Withdrawn

Also Published As

| Publication number | Publication date |

|---|---|

| JP2015025812A (ja) | 2015-02-05 |

| JP2010185869A (ja) | 2010-08-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN110678434B (zh) | 多层陶瓷基板及其制造方法 | |

| US8193456B2 (en) | Electrical inspection substrate unit and manufacturing method therefore | |

| JP5519312B2 (ja) | 多層セラミック基板及びその製造方法 | |

| JP2008034828A (ja) | Ic検査用治具に用いる多層セラミック基板及び多層セラミック基板の製造方法 | |

| JP6406646B2 (ja) | セラミックパッケージ及び電子部品 | |

| JP2009158576A (ja) | 電子部品検査治具用多層セラミック基板 | |

| JP5671237B2 (ja) | 半導体素子検査用基板 | |

| JP5566271B2 (ja) | 配線基板およびその製造方法 | |

| JP5461913B2 (ja) | 多層セラミック基板の製造方法 | |

| JP6088129B2 (ja) | 多層セラミック基板の製造方法 | |

| JP6835540B2 (ja) | セラミック配線基板、プローブ基板およびプローブカード | |

| CN118339930A (zh) | 电路模块 | |

| CN113678244B (zh) | 氮化硅电路基板及电子部件模块 | |

| KR101101574B1 (ko) | 세라믹 기판 및 그의 제조 방법 | |

| JP2004165291A (ja) | ビアホール付きセラミック基板及びその製造方法 | |

| JP2010177383A (ja) | 多層セラミック基板及びその製造方法並びにプローブカード | |

| JP4511013B2 (ja) | 多数個取りセラミック配線基板 | |

| JP6030373B2 (ja) | 多層セラミック基板及びその製造方法 | |

| JP5947018B2 (ja) | 多層セラミック基板及びその製造方法 | |

| JP2001210746A (ja) | 半導体素子搭載用基板 | |

| JP7093227B2 (ja) | セラミック配線基板、プローブ基板およびプローブカード | |

| JP2013232688A (ja) | 多層セラミック基板の製造方法 | |

| KR20240155879A (ko) | 인터포저, 반도체 패키지 및 그들의 제조 방법 | |

| JP2002026189A (ja) | 配線基板の製造方法 | |

| JP2753760B2 (ja) | バーンイン試験用電子回路基板とその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20121212 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130628 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130702 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130830 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140603 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140902 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20141017 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141211 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141219 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5671237 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |