JP5506170B2 - 実装構造体および電子機器 - Google Patents

実装構造体および電子機器 Download PDFInfo

- Publication number

- JP5506170B2 JP5506170B2 JP2008206079A JP2008206079A JP5506170B2 JP 5506170 B2 JP5506170 B2 JP 5506170B2 JP 2008206079 A JP2008206079 A JP 2008206079A JP 2008206079 A JP2008206079 A JP 2008206079A JP 5506170 B2 JP5506170 B2 JP 5506170B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- insulating resin

- mounting structure

- resin layer

- filler

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 229920005989 resin Polymers 0.000 claims description 111

- 239000011347 resin Substances 0.000 claims description 111

- 239000000945 filler Substances 0.000 claims description 99

- 239000000853 adhesive Substances 0.000 claims description 37

- 230000001070 adhesive effect Effects 0.000 claims description 37

- 229920001187 thermosetting polymer Polymers 0.000 claims description 22

- 230000017525 heat dissipation Effects 0.000 claims description 21

- 239000000758 substrate Substances 0.000 claims description 17

- 230000007423 decrease Effects 0.000 claims 1

- 239000004065 semiconductor Substances 0.000 description 73

- 239000011342 resin composition Substances 0.000 description 40

- 229920000647 polyepoxide Polymers 0.000 description 25

- 239000003822 epoxy resin Substances 0.000 description 23

- 230000000052 comparative effect Effects 0.000 description 18

- 229910000679 solder Inorganic materials 0.000 description 16

- -1 alkyl glycidyl ethers Chemical class 0.000 description 12

- 239000000203 mixture Substances 0.000 description 12

- 239000003795 chemical substances by application Substances 0.000 description 10

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 9

- 229910052799 carbon Inorganic materials 0.000 description 9

- 238000000034 method Methods 0.000 description 9

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 7

- 229910052802 copper Inorganic materials 0.000 description 7

- 239000010949 copper Substances 0.000 description 7

- RAXXELZNTBOGNW-UHFFFAOYSA-N imidazole Natural products C1=CNC=N1 RAXXELZNTBOGNW-UHFFFAOYSA-N 0.000 description 7

- 238000005259 measurement Methods 0.000 description 7

- 238000007789 sealing Methods 0.000 description 7

- 238000012360 testing method Methods 0.000 description 7

- IISBACLAFKSPIT-UHFFFAOYSA-N bisphenol A Chemical compound C=1C=C(O)C=CC=1C(C)(C)C1=CC=C(O)C=C1 IISBACLAFKSPIT-UHFFFAOYSA-N 0.000 description 6

- 239000004593 Epoxy Substances 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 238000005520 cutting process Methods 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- 229920000768 polyamine Polymers 0.000 description 4

- QGBSISYHAICWAH-UHFFFAOYSA-N dicyandiamide Chemical compound NC(N)=NC#N QGBSISYHAICWAH-UHFFFAOYSA-N 0.000 description 3

- LNEPOXFFQSENCJ-UHFFFAOYSA-N haloperidol Chemical compound C1CC(O)(C=2C=CC(Cl)=CC=2)CCN1CCCC(=O)C1=CC=C(F)C=C1 LNEPOXFFQSENCJ-UHFFFAOYSA-N 0.000 description 3

- 238000002347 injection Methods 0.000 description 3

- 239000007924 injection Substances 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 239000003566 sealing material Substances 0.000 description 3

- 230000035882 stress Effects 0.000 description 3

- CPLXHLVBOLITMK-UHFFFAOYSA-N Magnesium oxide Chemical compound [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- PXKLMJQFEQBVLD-UHFFFAOYSA-N bisphenol F Chemical compound C1=CC(O)=CC=C1CC1=CC=C(O)C=C1 PXKLMJQFEQBVLD-UHFFFAOYSA-N 0.000 description 2

- 238000004132 cross linking Methods 0.000 description 2

- 239000003085 diluting agent Substances 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- 230000005484 gravity Effects 0.000 description 2

- 150000002460 imidazoles Chemical class 0.000 description 2

- 238000009413 insulation Methods 0.000 description 2

- 238000005304 joining Methods 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229920003986 novolac Polymers 0.000 description 2

- 230000008646 thermal stress Effects 0.000 description 2

- VILCJCGEZXAXTO-UHFFFAOYSA-N 2,2,2-tetramine Chemical compound NCCNCCNCCN VILCJCGEZXAXTO-UHFFFAOYSA-N 0.000 description 1

- LXBGSDVWAMZHDD-UHFFFAOYSA-N 2-methyl-1h-imidazole Chemical compound CC1=NC=CN1 LXBGSDVWAMZHDD-UHFFFAOYSA-N 0.000 description 1

- QTWJRLJHJPIABL-UHFFFAOYSA-N 2-methylphenol;3-methylphenol;4-methylphenol Chemical compound CC1=CC=C(O)C=C1.CC1=CC=CC(O)=C1.CC1=CC=CC=C1O QTWJRLJHJPIABL-UHFFFAOYSA-N 0.000 description 1

- ZCUJYXPAKHMBAZ-UHFFFAOYSA-N 2-phenyl-1h-imidazole Chemical compound C1=CNC(C=2C=CC=CC=2)=N1 ZCUJYXPAKHMBAZ-UHFFFAOYSA-N 0.000 description 1

- RNLHGQLZWXBQNY-UHFFFAOYSA-N 3-(aminomethyl)-3,5,5-trimethylcyclohexan-1-amine Chemical compound CC1(C)CC(N)CC(C)(CN)C1 RNLHGQLZWXBQNY-UHFFFAOYSA-N 0.000 description 1

- ULKLGIFJWFIQFF-UHFFFAOYSA-N 5K8XI641G3 Chemical compound CCC1=NC=C(C)N1 ULKLGIFJWFIQFF-UHFFFAOYSA-N 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 229910052582 BN Inorganic materials 0.000 description 1

- PZNSFCLAULLKQX-UHFFFAOYSA-N Boron nitride Chemical compound N#B PZNSFCLAULLKQX-UHFFFAOYSA-N 0.000 description 1

- RPNUMPOLZDHAAY-UHFFFAOYSA-N Diethylenetriamine Chemical compound NCCNCCN RPNUMPOLZDHAAY-UHFFFAOYSA-N 0.000 description 1

- ISWSIDIOOBJBQZ-UHFFFAOYSA-N Phenol Chemical compound OC1=CC=CC=C1 ISWSIDIOOBJBQZ-UHFFFAOYSA-N 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- FDLQZKYLHJJBHD-UHFFFAOYSA-N [3-(aminomethyl)phenyl]methanamine Chemical compound NCC1=CC=CC(CN)=C1 FDLQZKYLHJJBHD-UHFFFAOYSA-N 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 125000002723 alicyclic group Chemical group 0.000 description 1

- 125000001931 aliphatic group Chemical group 0.000 description 1

- 125000000217 alkyl group Chemical group 0.000 description 1

- 150000001412 amines Chemical class 0.000 description 1

- 239000002518 antifoaming agent Substances 0.000 description 1

- 125000003118 aryl group Chemical group 0.000 description 1

- 125000004432 carbon atom Chemical group C* 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000013329 compounding Methods 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 238000005336 cracking Methods 0.000 description 1

- 239000006071 cream Substances 0.000 description 1

- 229930003836 cresol Natural products 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 235000014113 dietary fatty acids Nutrition 0.000 description 1

- ZZTCPWRAHWXWCH-UHFFFAOYSA-N diphenylmethanediamine Chemical compound C=1C=CC=CC=1C(N)(N)C1=CC=CC=C1 ZZTCPWRAHWXWCH-UHFFFAOYSA-N 0.000 description 1

- 125000003700 epoxy group Chemical group 0.000 description 1

- 239000000194 fatty acid Substances 0.000 description 1

- 229930195729 fatty acid Natural products 0.000 description 1

- 230000020169 heat generation Effects 0.000 description 1

- 239000000395 magnesium oxide Substances 0.000 description 1

- 238000000691 measurement method Methods 0.000 description 1

- 239000003607 modifier Substances 0.000 description 1

- QOHMWDJIBGVPIF-UHFFFAOYSA-N n',n'-diethylpropane-1,3-diamine Chemical compound CCN(CC)CCCN QOHMWDJIBGVPIF-UHFFFAOYSA-N 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 239000000049 pigment Substances 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 230000005855 radiation Effects 0.000 description 1

- 230000002787 reinforcement Effects 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/303—Surface mounted components, e.g. affixing before soldering, aligning means, spacing means

- H05K3/305—Affixing by adhesive

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/563—Encapsulation of active face of flip-chip device, e.g. underfilling or underencapsulation of flip-chip, encapsulation preform on chip or mounting substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/565—Moulds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/29—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the material, e.g. carbon

- H01L23/293—Organic, e.g. plastic

- H01L23/295—Organic, e.g. plastic containing a filler

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3135—Double encapsulation or coating and encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/74—Apparatus for manufacturing arrangements for connecting or disconnecting semiconductor or solid-state bodies

- H01L24/75—Apparatus for connecting with bump connectors or layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/0557—Disposition the external layer being disposed on a via connection of the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05571—Disposition the external layer being disposed in a recess of the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05573—Single external layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/16237—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the bump connector connecting to a bonding area disposed in a recess of the surface of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3121—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed a substrate forming part of the encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01012—Magnesium [Mg]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01019—Potassium [K]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/35—Mechanical effects

- H01L2924/351—Thermal stress

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0201—Thermal arrangements, e.g. for cooling, heating or preventing overheating

- H05K1/0203—Cooling of mounted components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/02—Fillers; Particles; Fibers; Reinforcement materials

- H05K2201/0203—Fillers and particles

- H05K2201/0206—Materials

- H05K2201/0209—Inorganic, non-metallic particles

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/02—Fillers; Particles; Fibers; Reinforcement materials

- H05K2201/0203—Fillers and particles

- H05K2201/0263—Details about a collection of particles

- H05K2201/0269—Non-uniform distribution or concentration of particles

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10621—Components characterised by their electrical contacts

- H05K2201/10674—Flip chip

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10954—Other details of electrical connections

- H05K2201/10977—Encapsulated connections

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/24—Structurally defined web or sheet [e.g., overall dimension, etc.]

- Y10T428/24355—Continuous and nonuniform or irregular surface on layer or component [e.g., roofing, etc.]

- Y10T428/24372—Particulate matter

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Casings For Electric Apparatus (AREA)

- Non-Metallic Protective Coatings For Printed Circuits (AREA)

- Wire Bonding (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

Description

一方の主面に複数の電極が形成された、電子部品と、実装面に複数の電極が形成された回路基板とを備え、前記電子部品の複数の電極が前記回路基板の複数の電極にそれぞれ接合された実装構造体であって、

前記一方の主面に対向する前記電子部品の他方の主面に、接着力および熱伝導率の異なる第1層と第2層とで構成された第1の絶縁性樹脂層が形成され、かつ

前記第1の絶縁性樹脂層の前記他方の主面と接する部分には、前記第2層より接着力が高い前記第1層が配置され、

前記第1の絶縁性樹脂層の前記他方の主面と接しない部分には、前記第1層より熱伝導率が高い前記第2層が配置され、

前記一方の主面と前記回路基板との間に、接着力および熱伝導率の異なる第3層と第4層とで構成された第2の絶縁性樹脂層が形成され、

前記第2の絶縁性樹脂層の前記一方の主面と接する部分には、前記第4層より接着力が高い前記第3層が配置され、

前記第2の絶縁性樹脂層の前記一方の主面と接しない部分には、前記第3層より熱伝導率が高い前記第4層が配置され、

前記第1層が、前記電子部品の側面、および、前記第2の絶縁性樹脂層の側面を覆っていることを特徴とする。

前記電子部品と接する部分には、前記第2層より接着強度が高い前記第1層が配置され、

前記電子部品と接しない部分には、前記第1層より熱伝導率が高い前記第2層が配置されている。

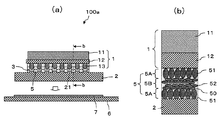

図1(a)に本発明の実施の形態1にかかる実装構造体の断面を示す。本実施の形態にかかる実装構造体100aは、半導体チップ1と回路基板2で構成されている。半導体チップ1は従来の実装構造体200と同様に、ベアIC11およびインターポーザ基板12で構成され、更にインターポーザ基板12のベアIC11と対向する面に、端子電極であるはんだボール13が形成されている。半導体チップ1は、はんだボール13と回路基板2のランド(電極)21がはんだ3で接合されることにより、回路基板2上に実装される。

図3(a)に本発明の実施の形態2にかかる実装構造体100cの断面を示す。また図3(b)に、図3(a)の実装構造体100cをb−b線に沿って切断した断面の一部を示す。図3(b)は、図1(b)と同様に、フィラーの混入状態を分かりやすく説明するため、フィラーの形状を誇張して模式的に表示している。

図4(a)に本発明の実施の形態3にかかる実装構造体100dの断面を示す。また図4(b)には、図4(a)の実装構造体100dをb−b線に沿って切断した断面の一部を示し、図4(c)には、図4(a)の実装構造体100dをc−c線に沿って切断した断面の一部を示す。なお図4(b)、(c)は、図1(b)と同様に、フィラーの混入状態を分かりやすく説明するため、フィラーの形状を誇張して模式的に表示している。

次に、本発明で用いられる熱硬化性樹脂組成物について具体的に説明する。使用可能な熱硬化性樹脂組成物として、エポキシ樹脂組成物やフェノール樹脂組成物あるいはアクリル樹脂組成物が挙げられる。吸湿性、熱膨張性、硬化収縮性などの点を考慮すると、エポキシ樹脂組成物が適している。

<熱伝導率と接着強度の測定>

絶縁性樹脂層を構成する、熱硬化性樹脂組成物に絶縁性フィラーが混入した樹脂組成物は、下記の(A)〜(D)の各成分に硬化促進剤を混合して作成する。

(A)成分(熱硬化性樹脂組成物):エポキシ樹脂、具体的にはビスフェノールA型エポキシ樹脂(ジャパンエポキシレジン株式会社、エピコート828、比重1.17、100重量部)、

(B)成分(硬化剤):ジシアンジアミド(味の素ファインテクノ株式会社、アミキュアAH-154、8重量部)、

(C)成分(絶縁性フィラー):形状の異なるアルミナフィラー、具体的には、40μ径のアルミナ球状フィラー、もしくは5μ厚みのリン片状アルミナフィラー、

(D)成分(反応性希釈剤:架橋調整剤):アルキルグリシジルエーテル(ジャパンエポキシレジン株式会社、YED216M、10重量部)、

硬化促進剤:味の素ファインテクノ株式会社、アミキュアPN−23、比重1.21、1重量部。

実施例1として、図1に示したのと同様の3層構造(各層の厚さは1mm)の絶縁性樹脂層を作成した。第1層の球状フィラーの含有率は60%である。第2層にはリン片状フィラーだけを混入し、その含有率は60%である。このようにして作成した絶縁性樹脂層の熱伝導率を測定した。熱伝導率は、単位長さあたり1℃の温度差があるとき、単位時間に単位面積を移動する熱量で定義され、ここでは、一般的な測定方法であるレーザフラッシュ方により測定を行った。

絶縁性樹脂層の第2層に、実施例の第1層に用いたのと同一の熱硬化性組成物および球状フィラーを用い、かつ第1層と第2層のフィラーの含有量を同一にした。このような絶縁性樹脂層について、実施例と同様の方法で熱伝導率および接着強度を測定した。フィラーの含有量および測定結果を表1に示す。いずれの比較例においても、接着強度は6kg以上となっているが、熱伝導率は1w/m・kを超えなかった。すなわち、比較例1〜4の絶縁性樹脂層は、熱伝導率について要求される条件を充足できなかった。

比較例1〜4で用いたのと同一の球状フィラーを用いて絶縁性樹脂層の第1層と第2層を形成したが、フィラーの含有量を比較例1〜4よりも高くした。実施例と同様の方法で測定した絶縁性樹脂層の熱伝導率と接着強度を表1に示す。熱伝導率は1w/m・k以上と良好な値を示しているが、接着強度は3kgまで低下している。従って、比較例5の絶縁性樹脂層は、接着強度について要求される条件を充足できなかった。

比較例1〜4で用いたのと同一の球状フィラーを用いて絶縁性樹脂層の第1層と第2層を形成したが、第1層のフィラーの含有量を50wt%とした。実施例と同様の方法で測定した絶縁性樹脂層の熱伝導率と接着強度を表1に示す。第1層のフィラー含有量が60wt%を下回ると、第2層のフィラー含有量が90wt%と高い値でも、1w/m・k以上の熱伝導率が得られない。従って、比較例6の絶縁性樹脂層は、熱伝導率について要求される条件を充足できなかった。

絶縁性樹脂層の第2層に、第1層と同一の形状である球状フィラーに加えて、フィラー間の接触面積が大きくなることが期待できるリン片状フィラーを5wt%加えた。実施例と同様の方法で測定した絶縁性樹脂層の熱伝導率および接着強度を表1に示す。実施例9〜11に示すようにリン片状フィラーの含有量は10wt%以上である必要であり、5wt%以下では熱伝導率を向上させることができない。

次に、上述の測定で優れた放熱性を示した各実施例の絶縁性樹脂層(図1参照)が、半導体素子や電子部品が実装された状態で高い接着強度を維持できるかどうか、温度サイクル試験により調べた。

2 回路基板

3 はんだ

1 半導体チップ

5、8、9 絶縁性樹脂層

10 型

12 インターポーザ基板

13 はんだボール

21 ランド

50 熱硬化性樹脂組成物

51 粒状フィラー

52 リン片状フィラー

100a〜100e 実装構造体

Claims (4)

- 一方の主面に複数の電極が形成された、電子部品と、実装面に複数の電極が形成された回路基板とを備え、前記電子部品の複数の電極が前記回路基板の複数の電極にそれぞれ接合された実装構造体であって、

前記一方の主面に対向する前記電子部品の他方の主面に、接着力および熱伝導率の異なる第1層と第2層とで構成された第1の絶縁性樹脂層が形成され、かつ

前記第1の絶縁性樹脂層の前記他方の主面と接する部分には、前記第2層より接着力が高い前記第1層が配置され、

前記第1の絶縁性樹脂層の前記他方の主面と接しない部分には、前記第1層より熱伝導率が高い前記第2層が配置され、

前記一方の主面と前記回路基板との間に、接着力および熱伝導率の異なる第3層と第4層とで構成された第2の絶縁性樹脂層が形成され、

前記第2の絶縁性樹脂層の前記一方の主面と接する部分には、前記第4層より接着力が高い前記第3層が配置され、

前記第2の絶縁性樹脂層の前記一方の主面と接しない部分には、前記第3層より熱伝導率が高い前記第4層が配置され、

前記第1層が、前記電子部品の側面、および、前記第2の絶縁性樹脂層の側面を覆っており、

前記第1層および前記第3層は、熱硬化性樹脂を主成分とし、これに球状のフィラーが混入されており、

前記第2層および第4層は、熱硬化性樹脂を主成分とし、これに球状のフィラーとリン片状のフィラーとが混入されていることを特徴とする実装構造体。 - 前記第2層が、さらに、前記第1層を覆うように形成されていることを特徴とする、請求項1記載の実装構造体。

- 前記第1の絶縁性樹脂層が複数の層で形成され、前記電子部品の他方の主面と接しない層の熱伝導率が一番高く、前記電子部品の他方の主面に近づくに従って熱伝導率が低下することを特徴とする、請求項1記載の実装構造体。

- 電子部品の他方の主面上に前記第1の絶縁性樹脂層が形成された請求項1記載の実装構造体が内蔵され、かつ前記第1の絶縁性樹脂層が、放熱シートまたは高熱伝導性接着剤を介して筐体に当接していることを特徴とする電子機器。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008206079A JP5506170B2 (ja) | 2008-08-08 | 2008-08-08 | 実装構造体および電子機器 |

| US12/535,760 US8319108B2 (en) | 2008-08-08 | 2009-08-05 | Mounting structure and electronic equipment |

| CN2009101618994A CN101645428B (zh) | 2008-08-08 | 2009-08-07 | 安装结构体以及电子设备 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008206079A JP5506170B2 (ja) | 2008-08-08 | 2008-08-08 | 実装構造体および電子機器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010045067A JP2010045067A (ja) | 2010-02-25 |

| JP2010045067A5 JP2010045067A5 (ja) | 2011-08-04 |

| JP5506170B2 true JP5506170B2 (ja) | 2014-05-28 |

Family

ID=41651848

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008206079A Active JP5506170B2 (ja) | 2008-08-08 | 2008-08-08 | 実装構造体および電子機器 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8319108B2 (ja) |

| JP (1) | JP5506170B2 (ja) |

| CN (1) | CN101645428B (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101117705B1 (ko) * | 2010-07-28 | 2012-02-29 | 삼성에스디아이 주식회사 | 배터리 팩 |

| CN103025122A (zh) * | 2011-09-23 | 2013-04-03 | 联想(北京)有限公司 | 一种电子设备 |

| CN104206036B (zh) * | 2012-04-10 | 2017-05-03 | 松下知识产权经营株式会社 | 电极接合方法、电极接合结构体的制造方法以及电极接合结构体的制造系统 |

| KR20160021366A (ko) * | 2014-08-14 | 2016-02-25 | 주식회사 아모그린텍 | 방열 시트 |

| JP5967629B2 (ja) | 2014-11-17 | 2016-08-10 | インターナショナル・ビジネス・マシーンズ・コーポレーションInternational Business Machines Corporation | 回路モジュール及びその製造方法 |

| CN106257652B (zh) * | 2015-06-16 | 2020-03-27 | 台达电子企业管理(上海)有限公司 | 封装模块及封装方法 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS522266B2 (ja) * | 1973-03-10 | 1977-01-20 | ||

| JPH0412556A (ja) | 1990-05-02 | 1992-01-17 | Oki Electric Ind Co Ltd | 半導体装置の放熱構造 |

| JPH04155853A (ja) | 1990-10-19 | 1992-05-28 | Hitachi Ltd | 半導体集積回路装置 |

| JPH06232294A (ja) | 1993-02-03 | 1994-08-19 | Hitachi Ltd | 半導体集積回路装置 |

| JP2756075B2 (ja) * | 1993-08-06 | 1998-05-25 | 三菱電機株式会社 | 金属ベース基板およびそれを用いた電子機器 |

| JP3378374B2 (ja) * | 1993-09-14 | 2003-02-17 | 株式会社東芝 | 樹脂封止型半導体装置の製造方法、樹脂封止型半導体装置及び封止用樹脂シート |

| JP3514340B2 (ja) * | 1995-06-26 | 2004-03-31 | 電気化学工業株式会社 | 接着性シート |

| US6245400B1 (en) * | 1998-10-07 | 2001-06-12 | Ucar Graph-Tech Inc. | Flexible graphite with non-carrier pressure sensitive adhesive backing and release liner |

| JP3773022B2 (ja) * | 1999-02-12 | 2006-05-10 | 信越化学工業株式会社 | フリップチップ型半導体装置 |

| JP3581268B2 (ja) * | 1999-03-05 | 2004-10-27 | 株式会社東芝 | ヒートシンク付半導体装置およびその製造方法 |

| US6570099B1 (en) * | 1999-11-09 | 2003-05-27 | Matsushita Electric Industrial Co., Ltd. | Thermal conductive substrate and the method for manufacturing the same |

| JP2003234585A (ja) * | 2002-02-06 | 2003-08-22 | Fujitsu Ten Ltd | 電子部品の放熱構造 |

| JP2004179552A (ja) * | 2002-11-28 | 2004-06-24 | Nec Corp | 半導体装置の実装構造、実装方法およびリワーク方法 |

| US7229683B2 (en) * | 2003-05-30 | 2007-06-12 | 3M Innovative Properties Company | Thermal interface materials and method of making thermal interface materials |

| US7494635B2 (en) * | 2003-08-21 | 2009-02-24 | Saint-Gobain Ceramics & Plastics, Inc. | Boron nitride agglomerated powder |

| JP2005353792A (ja) * | 2004-06-10 | 2005-12-22 | Matsushita Electric Ind Co Ltd | 樹脂封止型半導体装置 |

| JP2006100463A (ja) * | 2004-09-29 | 2006-04-13 | Ibiden Co Ltd | プリント配線板用層間絶縁層、プリント配線板およびその製造方法 |

| JP4046120B2 (ja) * | 2005-01-27 | 2008-02-13 | 三菱電機株式会社 | 絶縁シートの製造方法およびパワーモジュールの製造方法 |

-

2008

- 2008-08-08 JP JP2008206079A patent/JP5506170B2/ja active Active

-

2009

- 2009-08-05 US US12/535,760 patent/US8319108B2/en not_active Expired - Fee Related

- 2009-08-07 CN CN2009101618994A patent/CN101645428B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010045067A (ja) | 2010-02-25 |

| CN101645428A (zh) | 2010-02-10 |

| US20100032190A1 (en) | 2010-02-11 |

| CN101645428B (zh) | 2013-10-23 |

| US8319108B2 (en) | 2012-11-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5707316B2 (ja) | 電子部品の実装方法 | |

| EP2899245B1 (en) | Anisotropic conductive adhesive | |

| KR0181615B1 (ko) | 반도체 장치의 실장체, 그 실장방법 및 실장용 밀봉재 | |

| JP5506170B2 (ja) | 実装構造体および電子機器 | |

| CN106914710B (zh) | 树脂助焊剂焊膏和安装结构体 | |

| US20110058342A1 (en) | Semiconductor Device | |

| US7582510B2 (en) | Electronic packaging materials for use with low-k dielectric-containing semiconductor devices | |

| JP2013254921A (ja) | 回路基板及び電子部品搭載基板 | |

| JPH10289969A (ja) | 半導体装置およびそれに用いる封止用樹脂シート | |

| JP6413249B2 (ja) | 熱伝導性シートおよび半導体装置 | |

| JP2016094599A (ja) | 熱伝導性シート用樹脂組成物、基材付き樹脂層、熱伝導性シートおよび半導体装置 | |

| JP2011100757A (ja) | 電子部品及びその製造方法 | |

| JPH08330506A (ja) | 回路基板構造 | |

| KR101163172B1 (ko) | 방열성 에폭시 솔더링 플럭스 및 이를 이용한 반도체 소자 실장 방법 | |

| KR20170012206A (ko) | 접착제 및 접속 구조체 | |

| JP5070789B2 (ja) | アンダーフィル用液状樹脂組成物および半導体装置 | |

| JP6632618B2 (ja) | 実装用導電性ペースト | |

| JP3931855B2 (ja) | 電子回路装置 | |

| KR20130042241A (ko) | 방열성 에폭시 솔더링 플럭스 및 이를 이용한 반도체 소자 실장 방법 | |

| JP3818267B2 (ja) | アンダーフィル用樹脂組成物及び半導体装置 | |

| JPH0964103A (ja) | 半導体装置の実装体,その実装方法及びその実装用封止材 | |

| JP3183272B2 (ja) | 半導体装置およびその製造方法 | |

| JP6388228B2 (ja) | 半導体封止用液状エポキシ樹脂組成物とそれを用いた半導体装置 | |

| JP2015220390A (ja) | 回路基板の製造方法、回路基板および電子部品実装基板 | |

| JP2013211556A (ja) | 電子部品 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110615 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110615 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120802 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120906 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121101 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130627 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130812 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20131127 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140220 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140318 |