JP5491969B2 - トランスミッタ、インタフェイス装置、車載通信システム - Google Patents

トランスミッタ、インタフェイス装置、車載通信システム Download PDFInfo

- Publication number

- JP5491969B2 JP5491969B2 JP2010123950A JP2010123950A JP5491969B2 JP 5491969 B2 JP5491969 B2 JP 5491969B2 JP 2010123950 A JP2010123950 A JP 2010123950A JP 2010123950 A JP2010123950 A JP 2010123950A JP 5491969 B2 JP5491969 B2 JP 5491969B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- current

- source

- gate

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000006854 communication Effects 0.000 title claims description 16

- 238000004891 communication Methods 0.000 title claims description 16

- 230000005540 biological transmission Effects 0.000 claims description 40

- 239000003990 capacitor Substances 0.000 claims description 40

- 230000005669 field effect Effects 0.000 claims description 23

- 239000004065 semiconductor Substances 0.000 claims description 11

- 238000007599 discharging Methods 0.000 claims description 10

- 239000000758 substrate Substances 0.000 claims description 7

- 230000008054 signal transmission Effects 0.000 claims description 4

- 230000007175 bidirectional communication Effects 0.000 claims description 3

- 238000007667 floating Methods 0.000 claims description 3

- 230000002093 peripheral effect Effects 0.000 claims description 3

- 238000006243 chemical reaction Methods 0.000 claims description 2

- 238000010586 diagram Methods 0.000 description 27

- 230000015556 catabolic process Effects 0.000 description 15

- 238000000034 method Methods 0.000 description 13

- 230000008569 process Effects 0.000 description 11

- 101710170230 Antimicrobial peptide 1 Proteins 0.000 description 9

- 101100464779 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) CNA1 gene Proteins 0.000 description 9

- 230000003071 parasitic effect Effects 0.000 description 7

- 230000007423 decrease Effects 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 238000012986 modification Methods 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 230000004044 response Effects 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 2

- 230000008859 change Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 210000000746 body region Anatomy 0.000 description 1

- 230000009194 climbing Effects 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- YMXREWKKROWOSO-VOTSOKGWSA-N methyl (e)-3-(2-hydroxyphenyl)prop-2-enoate Chemical compound COC(=O)\C=C\C1=CC=CC=C1O YMXREWKKROWOSO-VOTSOKGWSA-N 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/003—Modifications for increasing the reliability for protection

- H03K19/00346—Modifications for eliminating interference or parasitic voltages or currents

- H03K19/00361—Modifications for eliminating interference or parasitic voltages or currents in field effect transistor circuits

Description

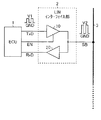

図1は、車載通信システムの一構成例を示すブロック図である。本図に例示した車載通信システムは、ECU[Electronic Control Unit]1と、LIN[Local Interconnect Network]インターフェイス部2と、LINバス3と、を有する。

図2は、トランスミッタ10の概略的構成を示す回路図である。本構成例のトランスミッタ10は、スイッチ101及び102と、定電流源103及び104と、コンデンサ105と、スイッチ制御部106と、基準電圧生成部107と、定電流制御部108と、アンプ109と、Nチャネル型MOS[Metal Oxide Semiconductor]電界効果トランジスタ110〜112と、Pチャネル型MOS電界効果トランジスタ113及び114と、抵抗115及び116と、を有する。

図3は、トランスミッタ10(前段部分に設けられた充電電圧Vaの生成機能部)の具体的構成を示す回路図である。

図4は、図2及び図3の構成から成るトランスミッタ10の動作を説明するための信号波形図であり、上から順に、送信入力信号IN、コンパレータCMP1の比較信号Scmp、トランジスタP1のゲート信号G1、トランジスタN1のゲート信号G2(送信入力信号INと同一)、充電電圧Va、及び、送信出力信号OUTが描写されている。

次に、トランスミッタ10の変形例について図5を参照しながら説明する。図5は、トランスミッタ10(後段部分)の一変形例を示す回路図である。

図8は、オープンドレイン出力段の第1構成例を示す回路図であり、図2や図5のオープンドレイン出力段のみを改めて描写し直したものである。図8に示すように、トランジスタ112のドレイン・ソース間には、寄生ダイオードDpが付随している。そのため、送信出力信号OUTの出力端に負電位のサージが入力された場合には、接地端から寄生ダイオードDpを介する経路で大量の順方向電流が流れ、トランジスタ112が破壊する恐れがある。

図12は、レシーバ20の第1構成例を示す回路図である。第1構成例のレシーバ20は、Nチャネル型電界効果トランジスタ201及び202と、抵抗203及び204と、定電流源205と、レベルシフタ206と、を有する。

また、本発明の構成は、上記実施形態のほか、発明の主旨を逸脱しない範囲で種々の変更を加えることが可能である。すなわち、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

2 LINインタフェイス部

3 LINバス

4 操作部

5 ドアミラー駆動部

6 パワーウィンドウ駆動部

10 トランスミッタ

20 レシーバ

101、102 スイッチ

103、104 定電流源

105 コンデンサ

106 スイッチ制御部

107 基準電圧生成部

108 定電流制御部

109 アンプ

110〜112 Nチャネル型MOS電界効果トランジスタ

113、114 Pチャネル型MOS電界効果トランジスタ

115、116 抵抗

117 Nチャネル型MOS電界効果トランジスタ

118、119 定電流源

120 スイッチ

121 コンパレータ

122 ダイオード

123 Nチャネル型DMOS電界効果トランジスタ

201、202 Nチャネル型MOS電界効果トランジスタ

203、204 抵抗

205 定電流源

206 レベルシフタ

207、208 Nチャネル型MOS電界効果トランジスタ

209、210 定電流源

211〜214 ツェナダイオード

215 抵抗

216、217 ダイオード

N1〜N4 Nチャネル型MOS電界効果トランジスタ

P1〜P4 Pチャネル型MOS電界効果トランジスタ

R1〜R4 抵抗

AMP1 アンプ

CMP1 コンパレータ

OR1 論理和演算器

BST ブースト部

Dp 寄生ダイオード

Claims (15)

- その一端から充電電圧が引き出されるコンデンサと;

前記コンデンサの充電電流を生成する第1定電流源と;

前記コンデンサの放電電流を生成する第2定電流源と;

送信入力信号の論理レベル、及び、前記充電電圧と基準電圧との比較結果に基づいて、前記コンデンサの充放電制御を行う充放電制御部と;

前記充電電圧に応じて論理レベルが切り替わる送信出力信号を生成する出力段と;

前記送信出力信号の信号振幅に相当する出力側電源電圧に依存して前記基準電圧を変動させる基準電圧生成部と;

前記基準電圧に依存して前記充電電流及び前記放電電流の各電流値を変動させる定電流制御部と;

を有することを特徴とするトランスミッタ。 - 前記出力段は、前記充電電圧に応じて導通度が制御されるオープンドレイン型トランジスタを含むことを特徴とする請求項1に記載のトランスミッタ。

- 前記オープンドレイン型トランジスタが飽和領域で動作し得る状態になるまで前記放電電流にブースト電流を加え、前記オープンドレイン型トランジスタが飽和領域で動作し得る状態になった時点で前記ブースト電流を切るブースト部をさらに有することを特徴とする請求項2に記載のトランスミッタ。

- 前記充放電制御部は、

前記コンデンサと前記第1定電流源との間を導通/遮断する第1スイッチと;

前記コンデンサと前記第2定電流源との間を導通/遮断する第2スイッチと;

前記第1スイッチ及び前記第2スイッチのオン/オフ制御を行うスイッチ制御部と;

を含むことを特徴とする請求項1〜請求項3のいずれかに記載のトランスミッタ。 - 前記基準電圧生成部は、前記出力側電源電圧を分圧して前記基準電圧を生成する抵抗ラダーであることを特徴とする請求項1〜請求項4のいずれかに記載のトランスミッタ。

- 前記定電流制御部は、

前記基準電圧を電圧/電流変換して基準電流を生成する基準電流生成部と;

前記基準電流を前記充電電流及び前記放電電流として複製するカレントミラー部と;

を含むことを特徴とする請求項1〜請求項5のいずれかに記載のトランスミッタ。 - 前記出力段は、アノードが前記送信出力信号の出力端に接続され、カソードが前記オープンドレイン型トランジスタのドレインに接続されたダイオードを含むことを特徴とする請求項2に記載のトランスミッタ。

- 前記ダイオードは、半導体基板上の一領域に形成された埋め込み絶縁層と、前記埋め込み絶縁層の上部周縁上に形成されたコレクタウォールと、によって取り囲まれたフローティング領域内に形成されていることを特徴とする請求項7に記載のトランスミッタ。

- 前記出力段は、前記オープンドレイン型トランジスタのドレインと前記ダイオードのカソードとの間に接続されたDMOS電界効果トランジスタを含むことを特徴とする請求項7または請求項8に記載のトランスミッタ。

- 信号送信経路に設けられた請求項1〜請求項9のいずれかに記載のトランスミッタと;

信号受信経路に設けられたレシーバと;

を有することを特徴とするインタフェイス装置。 - 前記レシーバは、

互いのソースが共通接続され、一方のドレインから受信出力信号が引き出される一対の第1トランジスタ及び第2トランジスタと;

ゲートが受信入力信号の入力端に接続され、ソースが第1トランジスタのゲートに接続された第3トランジスタと;

ゲートが受信基準電圧の入力端に接続され、ソースが第2トランジスタのゲートに接続された第4トランジスタと;

カソードが前記第1トランジスタのゲートに接続され、アノードが前記第1トランジスタのソースに接続された第1ツェナダイオードと;

カソードが前記第2トランジスタのゲートに接続され、アノードが前記第2トランジスタのソースに接続された第2ツェナダイオードと;

カソードが前記第3トランジスタのゲートに接続され、アノードが前記第3トランジスタのソースに接続された第3ツェナダイオードと;

カソードが前記第4トランジスタのゲートに接続され、アノードが前記第4トランジスタのソースに接続された第4ツェナダイオードと;

前記第1トランジスタと前記第2トランジスタのソース電流を生成する第1電流源と;

前記第3トランジスタのソース電流を生成する第2電流源と;

前記第4トランジスタのソース電流を生成する第3電流源と;

を含むことを特徴とする請求項10に記載のインタフェイス装置。 - 前記レシーバは、前記第1トランジスタのゲートと前記第3トランジスタのソースとの間に挿入された電流制限抵抗をさらに含むことを特徴とする請求項11に記載のインタフェイス装置。

- 前記レシーバは、

互いのソースが共通接続され、一方のドレインから受信出力信号が引き出される一対の第1トランジスタ及び第2トランジスタと;

カソードが前記第1トランジスタのゲートに接続され、アノードが前記第1トランジスタのソースに接続された第1ツェナダイオードと;

カソードが前記第2トランジスタのゲートに接続され、アノードが前記第2トランジスタのソースに接続された第2ツェナダイオードと;

前記第1トランジスタと前記第2トランジスタのソース電流を生成する電流源と;

アノードが前記第1トランジスタのソースに接続され、カソードが前記電流源に接続された第1ダイオードと;

アノードが前記第2トランジスタのソースに接続され、カソードが前記電流源に接続された第2ダイオードと;

を含むことを特徴とする請求項10に記載のインタフェイス装置。 - 前記第1ダイオード及び前記第2ダイオードは、ダイオード接続されたpnp型バイポーラトランジスタであることを特徴とする請求項13に記載のインタフェイス装置。

- ECUと;

バスと;

前記ECUと前記バスとの双方向通信を仲介する請求項10〜請求項14のいずれかに記載のインタフェイス装置と;

を有することを特徴とする車載通信システム。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010123950A JP5491969B2 (ja) | 2010-05-31 | 2010-05-31 | トランスミッタ、インタフェイス装置、車載通信システム |

| US13/113,235 US8410827B2 (en) | 2010-05-31 | 2011-05-23 | Transmitter, interface device, and car mounted communication system |

| CN201110142968.4A CN102290982B (zh) | 2010-05-31 | 2011-05-30 | 发送器、接口装置和车载通信系统 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010123950A JP5491969B2 (ja) | 2010-05-31 | 2010-05-31 | トランスミッタ、インタフェイス装置、車載通信システム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011250345A JP2011250345A (ja) | 2011-12-08 |

| JP2011250345A5 JP2011250345A5 (ja) | 2013-07-04 |

| JP5491969B2 true JP5491969B2 (ja) | 2014-05-14 |

Family

ID=45021591

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010123950A Active JP5491969B2 (ja) | 2010-05-31 | 2010-05-31 | トランスミッタ、インタフェイス装置、車載通信システム |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8410827B2 (ja) |

| JP (1) | JP5491969B2 (ja) |

| CN (1) | CN102290982B (ja) |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102823125B (zh) * | 2010-06-25 | 2015-08-05 | 无锡中星微电子有限公司 | Ac-dc电源转换器及其内的电流调制电路 |

| US8860398B2 (en) * | 2011-02-11 | 2014-10-14 | Fairchild Semiconductor Corporation | Edge rate control gate driver for switching power converters |

| TW201306416A (zh) * | 2011-07-28 | 2013-02-01 | Raydium Semiconductor Corp | 具有靜電放電保護效應的電子裝置 |

| CN103684400B (zh) * | 2012-09-25 | 2017-04-05 | 联咏科技股份有限公司 | 接口电路 |

| US8742803B2 (en) * | 2012-09-26 | 2014-06-03 | Broadcom Corporation | Output driver using low voltage transistors |

| US8848770B2 (en) * | 2012-12-17 | 2014-09-30 | Em Microelectronic-Marin S.A. | Automatic gain control unit for a low power receiver or transceiver |

| JP6013214B2 (ja) * | 2013-02-04 | 2016-10-25 | ルネサスエレクトロニクス株式会社 | バス通信トランシーバ |

| JP6065737B2 (ja) * | 2013-05-10 | 2017-01-25 | 株式会社ソシオネクスト | 出力回路および電圧信号出力方法 |

| JP2015015643A (ja) * | 2013-07-05 | 2015-01-22 | ローム株式会社 | 信号伝達回路 |

| JP6296535B2 (ja) | 2013-12-09 | 2018-03-20 | ローム株式会社 | ダイオードおよびそれを含む信号出力回路 |

| CN103684398B (zh) * | 2013-12-26 | 2016-08-31 | 中国科学院上海微系统与信息技术研究所 | 一种抗emi lin总线信号驱动器 |

| CN104900199B (zh) | 2014-03-05 | 2017-08-15 | 矽创电子股份有限公司 | 驱动模块及其显示装置 |

| KR102182572B1 (ko) * | 2014-04-15 | 2020-11-25 | 삼성디스플레이 주식회사 | 인터페이스 회로 |

| CN104202024B (zh) * | 2014-08-29 | 2017-06-30 | 杭州士兰微电子股份有限公司 | 适合高压浮地的开漏电路 |

| JP2017118185A (ja) * | 2015-12-21 | 2017-06-29 | 富士電機株式会社 | 半導体集積回路 |

| CN106788392B (zh) * | 2017-01-09 | 2023-05-09 | 四川埃姆克伺服科技有限公司 | 一种用于伺服控制器的单端型模拟量输入接口电路 |

| CN108732462B (zh) * | 2018-04-12 | 2020-02-21 | 华为技术有限公司 | 一种检测装置及方法 |

| CN109546999B (zh) * | 2018-11-28 | 2022-11-15 | 中国电子科技集团公司第四十七研究所 | 一种可编程usb限流开关 |

| JP2021013142A (ja) * | 2019-07-09 | 2021-02-04 | 株式会社村田製作所 | 電力増幅回路 |

| US11237612B2 (en) | 2019-08-22 | 2022-02-01 | Micron Technology, Inc. | Charge-sharing capacitive monitoring circuit in a multi-chip package to control power |

| US10884480B1 (en) | 2019-08-22 | 2021-01-05 | Micron Technology, Inc. | Current summing monitoring circuit in a multi-chip package to control power |

| US11164784B2 (en) * | 2019-08-22 | 2021-11-02 | Micron Technology, Inc. | Open-drain transistor monitoring circuit in a multi-chip package to control power |

| TWI773968B (zh) * | 2020-03-02 | 2022-08-11 | 瑞昱半導體股份有限公司 | 發射電路以及運作方法 |

| CN113381774B (zh) * | 2020-03-09 | 2022-07-19 | 瑞昱半导体股份有限公司 | 发射电路及其工作方法 |

| US10938387B1 (en) * | 2020-06-24 | 2021-03-02 | Cypress Semiconductor Corporation | Local interconnect network (LIN) driver circuit |

| WO2024053217A1 (ja) * | 2022-09-08 | 2024-03-14 | ローム株式会社 | 信号送信装置 |

| WO2024053216A1 (ja) * | 2022-09-08 | 2024-03-14 | ローム株式会社 | 信号送信装置 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5160142A (ja) * | 1974-10-25 | 1976-05-25 | Nippon Electric Co | Chokuryuzofukuki |

| JPS61118010A (ja) * | 1984-11-14 | 1986-06-05 | Mitsubishi Electric Corp | 半導体集積回路 |

| ATE100256T1 (de) * | 1987-06-29 | 1994-01-15 | Digital Equipment Corp | Bussender mit gesteuerter, trapezfoermiger ausgangsspannung. |

| JPS6451710A (en) * | 1987-08-21 | 1989-02-28 | Mitsubishi Electric Corp | Voltage controlled oscillation circuit |

| JPH07221568A (ja) * | 1994-02-09 | 1995-08-18 | Fuji Electric Co Ltd | 増幅回路装置 |

| JP2000323973A (ja) * | 1999-05-06 | 2000-11-24 | Nec Corp | 出力スルーレート制御回路 |

| DE19962523A1 (de) * | 1999-12-23 | 2001-08-02 | Texas Instruments Deutschland | Gleichspannungswandler und Verfahren zum Betreiben eines Gleichspannungswandlers |

| US6459602B1 (en) * | 2000-10-26 | 2002-10-01 | O2 Micro International Limited | DC-to-DC converter with improved transient response |

| US7999601B2 (en) * | 2005-04-01 | 2011-08-16 | Freescale Semiconductor, Inc. | Charge pump and control scheme |

| WO2008027038A1 (en) * | 2006-08-28 | 2008-03-06 | Semiconductor Components Industries, L.L.C. | Charge pump controller and method therefor |

| US7986175B2 (en) * | 2007-05-30 | 2011-07-26 | Panasonic Corporation | Spread spectrum control PLL circuit and its start-up method |

| CN101420223B (zh) * | 2007-10-23 | 2012-05-23 | 三星电子株式会社 | 差分发送器 |

| JP5071151B2 (ja) | 2008-02-27 | 2012-11-14 | トヨタ自動車株式会社 | 通信システム、その異常推定方法、及び情報読出装置 |

| JP2010105632A (ja) * | 2008-10-31 | 2010-05-13 | Autonetworks Technologies Ltd | 通信機器集約装置 |

| US8305053B2 (en) * | 2010-08-18 | 2012-11-06 | Texas Instruments Incorporated | System and method for controlling a power switch in a power supply system |

-

2010

- 2010-05-31 JP JP2010123950A patent/JP5491969B2/ja active Active

-

2011

- 2011-05-23 US US13/113,235 patent/US8410827B2/en active Active

- 2011-05-30 CN CN201110142968.4A patent/CN102290982B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20110291733A1 (en) | 2011-12-01 |

| JP2011250345A (ja) | 2011-12-08 |

| CN102290982A (zh) | 2011-12-21 |

| CN102290982B (zh) | 2015-07-08 |

| US8410827B2 (en) | 2013-04-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5491969B2 (ja) | トランスミッタ、インタフェイス装置、車載通信システム | |

| US8427220B2 (en) | Ringing suppression circuit | |

| US10461634B2 (en) | Charge pump circuit for providing voltages to multiple switch circuits | |

| US9041439B2 (en) | Transmitter having voltage driver and current driver | |

| US20090134930A1 (en) | Level shift circuit | |

| US20160308515A1 (en) | Low-Cost, Capacitive-Coupled Level Shifter Scalable for High-Voltage Applications | |

| US10018680B2 (en) | Semiconductor device, battery monitoring system, and method for activating semiconductor device | |

| US6859089B2 (en) | Power switching circuit with controlled reverse leakage | |

| CN209948734U (zh) | 自动负载检测电路 | |

| EP2487795B1 (en) | Output circuit, system including output circuit, and method of controlling output circuit | |

| EP2933923B1 (en) | Interface circuit | |

| US10025749B2 (en) | Tracking circuit and method | |

| US9991882B2 (en) | Semiconductor apparatus | |

| CN107562671B (zh) | 通讯总线供电电路 | |

| EP2876812B1 (en) | Input circuit with mirroring | |

| US20090167359A1 (en) | Current mode logic circuit and control apparatus therefor | |

| US8495273B2 (en) | Switch employing precharge circuits | |

| US9160334B2 (en) | Semiconductor device | |

| US8686763B2 (en) | Receiver circuit | |

| US8320471B2 (en) | Transmission device for differential communication | |

| JP6231793B2 (ja) | 差動信号伝送回路 | |

| JP5689778B2 (ja) | 入力回路 | |

| JP2008258818A (ja) | 信号出力回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130520 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130524 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131115 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20131126 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140117 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20140204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20140228 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5491969 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D03 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |