JP5449032B2 - メモリシステム - Google Patents

メモリシステム Download PDFInfo

- Publication number

- JP5449032B2 JP5449032B2 JP2010121728A JP2010121728A JP5449032B2 JP 5449032 B2 JP5449032 B2 JP 5449032B2 JP 2010121728 A JP2010121728 A JP 2010121728A JP 2010121728 A JP2010121728 A JP 2010121728A JP 5449032 B2 JP5449032 B2 JP 5449032B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- memory

- output

- nth

- clock

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/10—Distribution of clock signals, e.g. skew

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Memory System (AREA)

- Dram (AREA)

Description

tREA>tRLOH

tREA>tRC

である場合には、メモリコントローラがデータ線からデータを取り込むことが出来なくなる。

tROH<tREA

tROH<tREA

102 メモリコントローラ

111 コマンドイネーブル線

112 アドレスイネーブル線

113 ライトクロック線

114 リードクロック線

115 データ線

116 戻りリードクロック線

117 ビジー線

401 制御回路

402 クロック制御回路

403 入力回路

404 カウンタ

405 出力回路

Claims (12)

- メモリと、メモリコントローラと、前記メモリと前記メモリコントローラとを電気的に接続するメモリインターフェースとを含むメモリシステムであって、

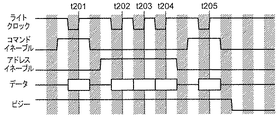

前記メモリインターフェースは、データの転送を行うために前記メモリが駆動するデータ線と、前記メモリから前記データ線へのデータ出力のタイミングを制御するためのリードクロックが伝送され、前記メモリコントローラが駆動するクロック線とを含み、

前記メモリは、N個のデータを出力する際、前記メモリコントローラから連続的に出力される1番目からN番目のリードクロックに同期して出力を開始し、1番目からN−1番目のデータについては2番目からN番目のリードクロックにそれぞれ同期して出力を停止し、N番目のデータについてはN番目のリードクロックの出力停止から第1の所定時間経過後に出力を停止し、

前記メモリコントローラは、1番目からN−1番目のデータについては2番目からN番目のリードクロックにそれぞれ同期して取り込み、N番目のデータについてはN番目のリードクロックによるN番目のデータの出力開始後N番目のデータの出力停止までの間に取り込み、N番目のリードクロックの出力期間を1番目からN−1番目のリードクロックの出力期間よりも長く設定することを特徴とするメモリシステム。 - 前記メモリは、N個のデータを出力する際、前記メモリコントローラから連続的に出力される1番目からN番目のリードクロックの立下りエッジまたは立上りエッジから第2の所定時間以内に出力を開始し、1番目からN−1番目のデータについてはそれぞれ2番目からN番目のリードクロックの立下りエッジまたは立上りエッジから第3の所定時間以内に出力を停止し、N番目のデータについてはN番目のリードクロックの出力停止から前記第1の所定時間経過後に出力を停止することを特徴とする請求項1記載のメモリシステム。

- 前記メモリコントローラは、1番目からN−1番目のリードクロックの周期を、前記第2の所定時間から第3の所定時間を減じた時間よりも大きくなるように制御することを特徴とする請求項2記載のメモリシステム。

- 前記メモリコントローラは、1番目からN−1番目のリードクロックの周期を、前記第2の所定時間の2倍の時間よりも小さく、かつ前記第2の所定時間よりも大きくなるように制御することを特徴とする請求項2記載のメモリシステム。

- 前記メモリコントローラは、1番目からN−1番目のデータについては2番目からN番目のリードクロックの立下りエッジまたは立上りエッジに同期して取り込むことを特徴とする請求項1記載のメモリシステム。

- 前記メモリコントローラは、N番目のデータについてはN番目のリードクロックの出力完了時のエッジに同期して取り込むことを特徴とする請求項1記載のメモリシステム。

- メモリと、メモリコントローラと、前記メモリと前記メモリコントローラとを電気的に接続するメモリインターフェースとを含むメモリシステムであって、

前記メモリインターフェースは、データの転送を行うために前記メモリが駆動するデータ線と、前記メモリから前記データ線へのデータ出力のタイミングを制御するためのリードクロックが伝送され、前記メモリコントローラが駆動するクロック線と、前記クロック線を介して前記メモリに到達したリードクロックを前記メモリコントローラに、戻りリードクロックとして戻す戻りクロック線とを含み、

前記メモリは、N個のデータを出力する際、前記メモリコントローラから連続的に出力される1番目からN番目のリードクロックに同期して出力を開始し、1番目からN−1番目のデータについては2番目からN番目のリードクロックにそれぞれ同期して出力を停止し、N番目のデータについてはN番目のリードクロックの出力停止から第1の所定時間経過後に出力を停止し、

前記メモリコントローラは、1番目からN−1番目のデータについては2番目からN番目の戻りリードクロックにそれぞれ同期して取り込み、N番目のデータについてはN番目のリードクロックによるN番目のデータの出力開始後N番目のデータの出力停止までの間に取り込み、N番目のリードクロックの出力期間を1番目からN−1番目のリードクロックの出力期間よりも長く設定することを特徴とするメモリシステム。 - 前記メモリは、N個のデータを出力する際、前記メモリコントローラから連続的に出力される1番目からN番目のリードクロックの立下りエッジまたは立上りエッジから第2の所定時間以内に出力を開始し、1番目からN−1番目のデータについてはそれぞれ2番目からN番目のリードクロックの立下りエッジまたは立上りエッジから第3の所定時間以内に出力を停止し、N番目のデータについてはN番目のリードクロックの出力停止から前記第1の所定時間経過後に出力を停止することを特徴とする請求項7記載のメモリシステム。

- 前記メモリコントローラは、1番目からN−1番目のリードクロックの周期を、前記第2の所定時間から第3の所定時間を減じた時間よりも大きくなるように制御することを特徴とする請求項8記載のメモリシステム。

- 前記メモリコントローラは、1番目からN−1番目のリードクロックの周期を、前記第2の所定時間の2倍の時間よりも小さく、かつ前記第2の所定時間よりも大きくなるように制御することを特徴とする請求項8記載のメモリシステム。

- 前記メモリコントローラは、1番目からN−1番目のデータについては2番目からN番目の戻りリードクロックの立下りエッジまたは立上りエッジに同期して取り込むことを特徴とする請求項7記載のメモリシステム。

- 前記メモリコントローラは、N番目のデータについてはN番目のリードクロックの出力完了時のエッジに同期して取り込むことを特徴とする請求項7記載のメモリシステム。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010121728A JP5449032B2 (ja) | 2009-05-28 | 2010-05-27 | メモリシステム |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009128461 | 2009-05-28 | ||

| JP2009128461 | 2009-05-28 | ||

| JP2010121728A JP5449032B2 (ja) | 2009-05-28 | 2010-05-27 | メモリシステム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011008779A JP2011008779A (ja) | 2011-01-13 |

| JP2011008779A5 JP2011008779A5 (ja) | 2013-07-04 |

| JP5449032B2 true JP5449032B2 (ja) | 2014-03-19 |

Family

ID=43301613

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010121728A Expired - Fee Related JP5449032B2 (ja) | 2009-05-28 | 2010-05-27 | メモリシステム |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8375238B2 (ja) |

| JP (1) | JP5449032B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101188264B1 (ko) * | 2010-12-01 | 2012-10-05 | 에스케이하이닉스 주식회사 | 반도체 시스템, 반도체 메모리 장치 및 이를 이용한 데이터 출력 방법 |

| US10083137B2 (en) * | 2015-04-02 | 2018-09-25 | Atmel Corporation | Peripheral interface circuit for serial memory |

| US12002541B2 (en) | 2021-12-08 | 2024-06-04 | Advanced Micro Devices, Inc. | Read clock toggle at configurable PAM levels |

| US20230178138A1 (en) * | 2021-12-08 | 2023-06-08 | Advanced Micro Devices, Inc. | Read clock start and stop for synchronous memories |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| IL96808A (en) * | 1990-04-18 | 1996-03-31 | Rambus Inc | Introductory / Origin Circuit Agreed Using High-Performance Brokerage |

| JPH05298241A (ja) * | 1992-04-23 | 1993-11-12 | Meidensha Corp | バースト転送方式 |

| JP3276798B2 (ja) * | 1995-02-02 | 2002-04-22 | 株式会社日立国際電気 | デジタルオシロスコープにおける波形の表示方法及び装置 |

| JP2003140962A (ja) * | 2001-10-30 | 2003-05-16 | Mitsubishi Electric Corp | 信号送受信システム |

| JP2002304323A (ja) * | 2002-02-04 | 2002-10-18 | Hitachi Ltd | 情報処理装置 |

| JP2003257200A (ja) * | 2002-03-01 | 2003-09-12 | Mitsubishi Electric Corp | 半導体記憶装置 |

| EP1501100B1 (en) * | 2003-07-22 | 2018-11-28 | Samsung Electronics Co., Ltd. | Nonvolatile memory device, memory system, and operating methods |

| KR100546418B1 (ko) * | 2004-07-27 | 2006-01-26 | 삼성전자주식회사 | 데이터 출력시 ddr 동작을 수행하는 비휘발성 메모리장치 및 데이터 출력 방법 |

| JP2006277892A (ja) | 2005-03-30 | 2006-10-12 | Elpida Memory Inc | 半導体記憶装置 |

| EP2011122A2 (en) * | 2006-04-24 | 2009-01-07 | SanDisk Corporation | High-performance flash memory data transfer |

| JP4267002B2 (ja) * | 2006-06-08 | 2009-05-27 | エルピーダメモリ株式会社 | コントローラ及びメモリを備えるシステム |

| US8015382B1 (en) * | 2007-02-28 | 2011-09-06 | Altera Corporation | Method and apparatus for strobe-based source-synchronous capture using a first-in-first-out unit |

-

2010

- 2010-05-27 JP JP2010121728A patent/JP5449032B2/ja not_active Expired - Fee Related

- 2010-05-27 US US12/788,740 patent/US8375238B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011008779A (ja) | 2011-01-13 |

| US8375238B2 (en) | 2013-02-12 |

| US20100313055A1 (en) | 2010-12-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP1807766B1 (en) | De-coupled memory access system and method | |

| US8687451B2 (en) | Power management in semiconductor memory system | |

| US8547760B2 (en) | Memory access alignment in a double data rate (‘DDR’) system | |

| KR100907016B1 (ko) | 반도체 메모리 장치의 데이터 입력 회로 및 그 제어 방법 | |

| US10970243B2 (en) | Front end serial bus automatic bus park tri-state activation | |

| US9026746B2 (en) | Signal control device and signal control method | |

| KR20180113371A (ko) | 데이터 저장 장치 | |

| JP5449032B2 (ja) | メモリシステム | |

| US20060236007A1 (en) | Apparatus to improve bandwidth for circuits having multiple memory controllers | |

| US10846021B2 (en) | Memory devices with programmable latencies and methods for operating the same | |

| KR102148806B1 (ko) | 반도체 장치 및 그를 포함하는 반도체 시스템 | |

| US9183900B2 (en) | Data paths using a first signal to capture data and a second signal to output data and methods for providing data | |

| US20190258400A1 (en) | Memory devices configured to latch data for output in response to an edge of a clock signal generated in response to an edge of another clock signal | |

| US7706195B2 (en) | Strobe signal controlling circuit | |

| JP2011008779A5 (ja) | ||

| US6629226B1 (en) | Fifo read interface protocol | |

| JP5423483B2 (ja) | データ転送制御装置 | |

| US8320204B2 (en) | Memory interface control circuit | |

| US7827455B1 (en) | System and method for detecting glitches on a high-speed interface | |

| US20130054937A1 (en) | Apparatuses and methods for providing data from multiple memories | |

| CN106847319A (zh) | 一种fpga电路及窗口信号调整方法 | |

| JP5489871B2 (ja) | 画像処理装置 | |

| US7644226B1 (en) | System and method for maintaining RAM command timing across phase-shifted time domains | |

| CN115035929A (zh) | 一种高效实现伪ddr信号跨时钟域的电路、方法和电子设备 | |

| WO2006112968A1 (en) | Apparatus to improve bandwidth for circuits having multiple memory controllers |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130517 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130517 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20131120 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131126 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131224 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5449032 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |