JP5369552B2 - 画素回路の駆動方法、発光装置および電子機器 - Google Patents

画素回路の駆動方法、発光装置および電子機器 Download PDFInfo

- Publication number

- JP5369552B2 JP5369552B2 JP2008226735A JP2008226735A JP5369552B2 JP 5369552 B2 JP5369552 B2 JP 5369552B2 JP 2008226735 A JP2008226735 A JP 2008226735A JP 2008226735 A JP2008226735 A JP 2008226735A JP 5369552 B2 JP5369552 B2 JP 5369552B2

- Authority

- JP

- Japan

- Prior art keywords

- period

- potential

- pixel circuit

- driving transistor

- gate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 36

- 239000003990 capacitor Substances 0.000 claims abstract description 84

- 230000008859 change Effects 0.000 claims description 19

- 238000013459 approach Methods 0.000 claims description 13

- 238000010586 diagram Methods 0.000 description 16

- 101100351213 Chromobacterium violaceum (strain ATCC 12472 / DSM 30191 / JCM 1249 / NBRC 12614 / NCIMB 9131 / NCTC 9757) pcp gene Proteins 0.000 description 13

- 101100126615 Mus musculus Itpr1 gene Proteins 0.000 description 13

- 101150075058 pcp1 gene Proteins 0.000 description 13

- 101001098880 Homo sapiens Purkinje cell protein 2 homolog Proteins 0.000 description 11

- 102100028516 Receptor-type tyrosine-protein phosphatase U Human genes 0.000 description 11

- 230000008901 benefit Effects 0.000 description 8

- 230000000694 effects Effects 0.000 description 8

- 230000007423 decrease Effects 0.000 description 7

- 230000004048 modification Effects 0.000 description 7

- 238000012986 modification Methods 0.000 description 7

- 230000007704 transition Effects 0.000 description 3

- 230000009471 action Effects 0.000 description 2

- 230000001413 cellular effect Effects 0.000 description 2

- 238000005401 electroluminescence Methods 0.000 description 2

- 239000011159 matrix material Substances 0.000 description 2

- 238000004904 shortening Methods 0.000 description 2

- 230000002123 temporal effect Effects 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 230000000052 comparative effect Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 239000010408 film Substances 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 239000000758 substrate Substances 0.000 description 1

Images

Landscapes

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Control Of El Displays (AREA)

Description

図1は、本発明の第1実施形態に係る発光装置のブロック図である。発光装置100は、画像を表示する表示体として電子機器に搭載される。図1に示すように、発光装置100は、複数の画素回路Uが配列された素子部10と、各画素回路Uを駆動する駆動回路30とを具備する。駆動回路30は、走査線駆動回路32と信号線駆動回路34と電位制御回路36とを含んで構成される。駆動回路30は、例えば複数の集積回路に分散して実装される。ただし、駆動回路30の少なくとも一部は、基板上に形成された薄膜トランジスタで構成され得る。

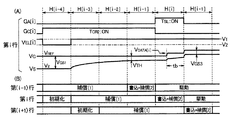

図3および図4に示すように、初期化期間PRSにおいては、信号線駆動回路34が信号S[j]を基準電位VREFに設定し、電位制御回路36が電位VEL[i]を電位V2に設定する。選択スイッチTSLはオン状態であるから、駆動トランジスタTDRのゲートの電位VGは、信号線14と選択スイッチTSLとを介して信号S[j]の基準電位VREFに設定される。また、駆動トランジスタTDRのソースの電位VSは電位V2に設定される。すなわち、駆動トランジスタTDRの電圧VGS(保持容量C1の両端間の電圧)は、基準電位VREFと電位V2との差分の電圧VGS1(VGS1=VREF−V2)に初期化される。

VGS1=VREF−V2≫VTH ……(1)

V2−VCT≪VTH_OLED……(2)

図3および図5に示すように、補償期間PCPが開始すると、電位制御回路36は、給電線16の電位VEL[i](駆動トランジスタTDRのドレインの電位)を電位V1に変化させる。図3に示すように、電位V1は、電位V2や基準電位VREFを充分に上回る。一方、信号線駆動回路34は、初期化期間PRSと同様に信号S[j]を基準電位VREFに維持する。選択スイッチTSLは補償期間PCPでもオン状態を維持するから、駆動トランジスタTDRのゲートの電位VGは基準電位VREFに維持される。駆動トランジスタTDRは初期化期間PRSにてオン状態に遷移しているから、以上の状態のもとでは、図5に示すように、以下の数式(3)で表現される電流Idsが駆動トランジスタTDRのドレインとソースとの間に流れる。数式(3)のμは駆動トランジスタTDRの移動度である。また、W/Lは、駆動トランジスタTDRのチャネル長Lに対するチャネル幅Wの相対比であり、Coxは、駆動トランジスタTDRのゲート絶縁膜の単位面積あたりの容量である。

Ids=1/2・μ・W/L・Cox・(VGS−VTH)2 ……(3)

図3に示すように、書込期間PWRは待機期間PWR1と動作期間PWR2とに区分される。待機期間PWR1は、書込期間PWRの始点から時間長taが経過するまでの期間であり、動作期間PWR2は、書込期間PWRの残余の期間(待機期間PWR1の終点から書込期間PWRの終点までの時間長tbの期間)である。動作期間PWR2の時間長tbは、画素回路Uに指定された階調値Dに応じて可変に設定される。すなわち、図3に示すように、階調値Dが高階調(高輝度)を指定する場合の時間長tbは、階調値Dが低階調(低輝度)を指定する場合の時間長tbと比較して短い。書込期間PWRの時間長は固定値であるから、待機期間PWR1の時間長taは時間長tb(階調値D)に応じて変化する。なお、動作期間PWR2の時間長tbの設定については後述する。

VGS2=VTH+ΔVDATA・cp2/(cp1+cp2)

=VIN+VTH ……(4)

VGS3=VGS2−ΔV

=VIN+VTH−ΔV ……(5)

電圧VGS3は、階調電位VDATAおよび時間長tbに応じて変化する。したがって、動作期間PWR2の時間長tbを階調値Dに応じて制御する動作は、動作期間PWR2の終点における電圧VGS3を階調値Dに応じて可変に制御する動作としても把握される。

図3および図7に示すように、駆動期間PDRが開始すると、走査線駆動回路32は走査信号GA[i]を非アクティブレベル(ローレベル)に変化させる。したがって、第i行目の各画素回路Uの選択スイッチTSLはオフ状態に変化し、駆動トランジスタTDRのゲートは電気的なフローティング状態となる(すなわち、駆動トランジスタTDRのゲートに対する電位の供給が停止する)。一方、書込期間PWRにてオン状態に設定された駆動トランジスタTDRのドレイン−ソース間に数式(3)の電流Idsが流れることで容量C2が充電される。したがって、図3に示すように、駆動トランジスタTDRの電圧VGSが書込期間PWRの終点での電圧VGS3に維持されたまま、容量C2の両端間の電圧(駆動トランジスタTDRのソースの電位VS)が徐々に増加する。そして、容量C2の両端間の電圧が発光素子Eの閾値電圧VTH_OLEDに到達した時点で電流Idsが駆動電流IDRとして発光素子Eを流れる。したがって、駆動電流IDRは以下の数式(6)で表現される。

IDR=1/2・μ・W/L・Cox・(VGS3−VTH)2

=1/2・μ・W/L・Cox・{(VIN+VTH−ΔV)−VTH}2

=K・(VIN−ΔV)2 ……(6)

K=1/2・μ・W/L・Cox

以上のように駆動電流IDRは、階調電位VDATAを反映した電圧VGS3に応じた電流量に制御されるから、発光素子Eは階調電位VDATA(すなわち階調値D)に応じた輝度で発光する。発光素子Eの発光は、走査信号GA[i]が次にアクティブレベルとなる単位期間H[i]の開始まで継続される。

Ids=dQ/dt=C・(dVS/dt) ……(7)

また、駆動トランジスタTDRのソースの電位VSの時間的な変化が電圧ΔVの時間的な変化と同等であること(dVS/dt=dΔV/dt)を考慮すると、数式(6)と数式(7)とから以下の数式(8)が導出される。なお、数式(8)における電圧ΔV(t)は、第2補償動作の開始(動作期間PWR2の始点)から経過した時間tに応じて数式(6)の電圧ΔVが変化することを意味する。

C(dΔV/dt)=K(VIN−ΔV(t))2 ……(8)

C=KVINtb ……(11)

数式(11)の電圧VINは階調電位VDATAに応じて設定されるから、階調電位VDATAと動作期間PWR2の時間長tbとについて、図9を参照して説明したのと同様の条件(階調電位VDATAが高いほど時間長tbを短くする)が数式(11)からも確認される。さらに詳述すると、電圧VINと動作期間PWR2の時間長tbとの乗算値(あるいは階調電位VDATAと時間長tbとの乗算値)が所定値となる場合に、第2補償動作による駆動電流IDRの補償の効果が最大となる。

次に、本発明の第2実施形態について説明する。なお、以下の各形態において作用や機能が第1実施形態と同様である要素については、以上と同じ符号を付して各々の詳細な説明を適宜に省略する。

図15は、本発明の第3実施形態における画素回路Uの回路図である。図15に示すように、画素回路Uは、第1実施形態の画素回路Uに制御スイッチTCR2を追加した構成である。制御スイッチTCR2は、駆動トランジスタTDRのゲートと給電線54との間に介在して両者の電気的な接続(導通/非導通)を制御するNチャネル型のトランジスタである。給電線54には基準電位VREFが供給される。すなわち、第1実施形態や第2実施形態においては画素回路Uに対する基準電位VREFの供給に信号線14を兼用したのに対し、本形態においては信号線14とは別個の給電線54を利用して各画素回路Uに基準電位VREFを供給する。

次に、本発明の第4実施形態について説明する。第1実施形態においては、書込期間PWRにおける第2補償動作の時間長tbを階調値Dに応じて可変に制御する構成を例示した。本形態においては、第2補償動作の時間長tbの制御に加えて、補償期間PCPにおける第1補償動作の時間長を階調値Dに応じて可変に制御する。画素回路Uの構成は第1実施形態(図2)と同様である。

VGSb=VGSa−ΔVREF・cp2/(cp1+cp2) ……(12)

以上の各形態は様々に変形される。各形態に対する変形の具体的な態様を以下に例示する。なお、以下の例示から2以上の態様を任意に選択して組合わせてもよい。

画素回路Uを構成する各トランジスタ(駆動トランジスタTDR,選択スイッチTSL,制御スイッチTCR1,制御スイッチTCR2)の導電型は任意である。例えば、図18に示すように、駆動トランジスタTDRや選択スイッチTSLをPチャネル型とした構成も採用される。図18の画素回路Uにおいては、発光素子Eの陽極が給電線18(電位VCT)に接続され、駆動トランジスタTDRのドレインが給電線16(電位VEL[i])に接続されるとともにソースが発光素子Eの陰極に接続される。駆動トランジスタTDRのゲートとソースとの間に保持容量C1が介在する構成や、駆動トランジスタTDRのゲートと信号線14との間に選択スイッチTSLが介在する構成は図2と同様である。以上のようにPチャネル型の駆動トランジスタTDRを採用した場合、Nチャネル型の駆動トランジスタTDRを採用した場合と比較して電圧の関係(高低)は逆転するが、本質的な動作は以上の例示と同様であるから、具体的な動作の説明は省略する。第2実施形態の制御スイッチTCR1や第3実施形態の制御スイッチTCR2を図18の画素回路Uに追加した構成も採用される。

以上の各形態のように、複数の画素回路Uが行列状に配列された構成のもとで各画素回路Uを行単位で時分割に駆動する場合には各画素回路U内に選択スイッチTSLが必要である。しかし、例えば複数の画素回路UがX方向に沿って1列のみに配列された構成においては、時分割での複数行の選択という動作が不要であるから、画素回路U内の選択スイッチTSLは不要となる。複数の画素回路Uが1列のみに配列された発光装置100は、例えば、電子写真方式の画像形成装置(印刷装置)において感光体ドラムなどの像担持体を露光する露光装置として好適に採用される。

以上の各形態においては発光素子Eに付随する容量C2を利用したが、図19に示すように、発光素子Eとは別個に形成した容量CXを容量C2とともに利用する構成も好適である。容量CXの電極e1は、駆動トランジスタTDRと発光素子Eとを結ぶ経路上(駆動トランジスタTDRのソース)に接続される。容量CXの電極e2は、所定の電位が供給される配線(例えば電位VCTが供給される給電線18や基準電位VREFが供給される図15の給電線54)に接続される。以上の構成においては、数式(4)や数式(12)における容量値cp2が容量CXと発光素子Eの容量C2との合計値となる。したがって、数式(4)の電圧VGS2や数式(12)の電圧VGSbを容量CXに応じて適宜に調整することが可能である。

有機EL素子は発光素子の例示に過ぎない。例えば、無機EL素子やLED(Light Emitting Diode)素子などの発光素子を配列した発光装置にも以上の各態様と同様に本発明が適用される。本発明における発光素子は、電流の供給で駆動される(典型的には階調(輝度)が制御される)電流駆動型の被駆動素子である。

次に、以上の各態様に係る発光装置100を利用した電子機器について説明する。図20ないし図22には、発光装置100を表示装置として採用した電子機器の形態が図示されている。

Claims (13)

- 相互に直列に接続された発光素子および駆動トランジスタと、前記発光素子と前記駆動トランジスタとの間の経路と前記駆動トランジスタのゲートとの間に介在する保持容量とを含む画素回路を駆動する方法であって、

前記駆動トランジスタを導通させるとともに当該駆動トランジスタのゲートに基準電位を供給することで前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第1補償動作を補償期間において実行し、

前記補償期間の経過後の書込期間において、前記基準電位から当該画素回路に指定された階調値に応じた階調電位に切り替える時点を前記階調値に応じて変更することで当該階調値に応じて可変に設定された第1の時間長にわたって前記駆動トランジスタのゲートに前記階調電位を供給するとともに、前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第2補償動作を実行し、

前記書込期間の経過後の駆動期間において、前記駆動トランジスタのゲートに対する電位の供給を停止することで、前記保持容量の両端間の電圧に応じた駆動電流を前記発光素子に供給する

画素回路の駆動方法。 - 前記書込期間において前記階調電位を供給したときの前記保持容量の両端間の電圧の変化量が大きいほど前記第1の時間長が短くなるように、前記第1の時間長を設定する

請求項1の画素回路の駆動方法。 - 前記階調値が所定値を下回る場合に、前記第1の時間長を、前記階調値に依存しない所定値に設定する

請求項1または請求項2の画素回路の駆動方法。 - 前記補償期間において、前記保持容量の両端間の電圧を、前記第1補償動作によって前記駆動トランジスタの閾値電圧に設定する

請求項1の画素回路の駆動方法。 - 前記補償期間において、前記階調値に応じて設定された第2の時間長にわたって前記第1補償動作を実行する

請求項1の画素回路の駆動方法。 - 相互に直列に接続された発光素子および駆動トランジスタと、前記発光素子と前記駆動トランジスタとの間の経路と前記駆動トランジスタのゲートとの間に介在する保持容量とを各々が含む複数の画素回路を駆動する方法であって、

前記複数の画素回路の各々について、

前記駆動トランジスタを導通させるとともに前記駆動トランジスタのゲートに信号線から基準電位を供給することで前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第1補償動作を、第1期間と第2期間とを各々が含む複数の単位期間のうち当該画素回路に対応する単位期間の第2期間の開始前の2以上の第1期間において間欠的に実行する一方、

当該画素回路に指定された階調値に応じた階調電位に切り替える時点を前記階調値に応じて変更して前記信号線から当該画素回路の前記駆動トランジスタのゲートに前記階調電位を当該階調値に応じて可変に設定された第1の時間長にわたって供給することで、前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第2補償動作を、当該画素回路に対応する単位期間の第2期間において、前記第1の時間長にわたって実行し、

当該画素回路に対応する単位期間の第2期間の経過後に、当該画素回路の前記駆動トランジスタのゲートに対する電位の供給を停止することで、前記保持容量の両端間の電圧に応じた駆動電流を前記発光素子に供給する

画素回路の駆動方法。 - 相互に直列に接続された発光素子および駆動トランジスタと、前記発光素子と前記駆動トランジスタとの間の経路と前記駆動トランジスタのゲートとの間に介在する保持容量とを各々が含む複数の画素回路を駆動する方法であって、

前記複数の画素回路の各々について、

前記駆動トランジスタを導通させるとともに前記駆動トランジスタのゲートに給電線から基準電位を供給することで前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第1補償動作を、複数の単位期間のうち当該画素回路に対応する単位期間の開始前の2以上の単位期間において間欠的に実行する一方、

当該画素回路に指定された階調値に応じた階調電位に切り替える時点を前記階調値に応じて変更して信号線から当該画素回路の前記駆動トランジスタのゲートに前記階調電位を当該階調値に応じて可変に設定された第1の時間長にわたって供給することで、前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第2補償動作を、当該画素回路に対応する単位期間において、前記第1の時間長にわたって実行し、

当該画素回路に対応する前記単位期間の経過後に、当該画素回路の前記駆動トランジスタのゲートに対する電位の供給を停止することで、前記保持容量の両端間の電圧に応じた駆動電流を前記発光素子に供給する

画素回路の駆動方法。 - 相互に直列に接続された発光素子および駆動トランジスタと、前記発光素子と前記駆動トランジスタとの間の経路と前記駆動トランジスタのゲートとの間に介在する保持容量とを含む画素回路と、

前記画素回路を駆動する駆動回路とを具備し、

前記駆動回路は、

当該画素回路に指定された階調値に応じた階調電位を生成する電位生成部と、

基準電位と前記電位生成部が生成した前記階調電位との何れかを選択する電位選択部と、

前記電位選択部において前記基準電位から前記階調電位に変更する時点を前記階調値に応じて可変に制御する時間調整部と、

を備え、

前記駆動回路は、

前記駆動トランジスタを導通させるとともに当該駆動トランジスタのゲートに前記基準電位を供給することで前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第1補償動作を補償期間において実行し、

前記補償期間の経過後の書込期間において、前記駆動トランジスタのゲートに前記電位選択部からの電位を供給するとともに、前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第2補償動作を、前記階調値に応じた時間長にわたって実行し、

前記書込期間の経過後の駆動期間において、前記駆動トランジスタのゲートに対する電位の供給を停止することで、前記保持容量の両端間の電圧に応じた駆動電流を前記発光素子に供給する

発光装置。 - 相互に直列に接続された発光素子および駆動トランジスタと、前記発光素子と前記駆動トランジスタとの間の経路と前記駆動トランジスタのゲートとの間に介在する保持容量とを各々が含む複数の画素回路と、

前記各画素回路を駆動する駆動回路とを具備し、

前記駆動回路は、

当該画素回路に指定された階調値に応じた階調電位を生成する電位生成部と、

基準電位と前記電位生成部が生成した前記階調電位との何れかを選択する電位選択部と、

前記電位選択部において前記基準電位から前記階調電位に変更する時点を前記階調値に応じて可変に制御する時間調整部と、

を備え、

前記駆動回路は、

前記複数の画素回路の各々について、

前記駆動トランジスタを導通させるとともに前記駆動トランジスタのゲートに信号線から基準電位を供給することで前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第1補償動作を、第1期間と第2期間とを各々が含む複数の単位期間のうち当該画素回路に対応する単位期間の第2期間の開始前の2以上の第1期間において間欠的に実行する一方、

前記駆動トランジスタのゲートに前記電位選択部からの電位を前記信号線を介して供給することで、前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第2補償動作を、当該画素回路に対応する単位期間の第2期間において、前記階調値に応じた時間長にわたって実行し、

当該画素回路に対応する前記単位期間の前記第2期間の経過後に、当該画素回路の前記駆動トランジスタのゲートに対する電位の供給を停止することで、前記保持容量の両端間の電圧に応じた駆動電流を前記発光素子に供給する

発光装置。 - 前記複数の画素回路の各々は、

前記駆動トランジスタのゲートと前記信号線との間に介在する選択スイッチと、

前記駆動トランジスタに流れる電流の経路上に配置された制御スイッチとを含み、

前記駆動回路は、前記複数の画素回路の各々について、

当該画素回路に対応する単位期間の第2期間の開始前の2以上の第1期間において、前記選択スイッチおよび前記制御スイッチをオン状態に制御するとともに前記信号線に前記基準電位を供給することで前記第1補償動作を実行させ、

当該画素回路に対応する単位期間の第2期間において、前記選択スイッチおよび前記制御スイッチをオン状態に制御するとともに前記信号線に前記電位選択部からの電位を供給することで前記第2補償動作を実行させ、

当該画素回路に対応する単位期間の第2期間以外の各第2期間において、前記選択スイッチをオフ状態に制御する

請求項9の発光装置。 - 相互に直列に接続された発光素子および駆動トランジスタと、前記発光素子と前記駆動トランジスタとの間の経路と前記駆動トランジスタのゲートとの間に介在する保持容量とを各々が含む複数の画素回路と、

前記各画素回路を駆動する駆動回路とを具備し、

前記駆動回路は、

当該画素回路に指定された階調値に応じた階調電位を生成する電位生成部と、

基準電位と前記電位生成部が生成した前記階調電位との何れかを選択する電位選択部と、

前記電位選択部において前記基準電位から前記階調電位に変更する時点を前記階調値に応じて可変に制御する時間調整部と、

を備え、

前記駆動回路は、

前記複数の画素回路の各々について、

前記駆動トランジスタを導通させるとともに前記駆動トランジスタのゲートに給電線から基準電位を供給することで前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第1補償動作を、複数の単位期間のうち当該画素回路に対応する単位期間の開始前の2以上の単位期間において間欠的に実行する一方、

前記電位選択部からの電位を信号線から当該画素回路の前記駆動トランジスタのゲートに供給することで、前記保持容量の両端間の電圧を前記駆動トランジスタの閾値電圧に接近させる第2補償動作を、当該画素回路に対応する単位期間において、前記階調値に応じた時間長にわたって実行し、

当該画素回路に対応する前記単位期間の経過後に、当該画素回路の前記駆動トランジスタのゲートに対する電位の供給を停止することで、前記保持容量の両端間の電圧に応じた駆動電流を前記発光素子に供給する

発光装置。 - 前記複数の画素回路の各々は、

前記駆動トランジスタのゲートと前記信号線との間に介在する選択スイッチと、

前記駆動トランジスタのゲートと前記給電線との間に介在する制御スイッチとを含み、

前記駆動回路は、前記複数の画素回路の各々について、

当該画素回路に対応する単位期間の開始前の2以上の単位期間において、前記制御スイッチをオン状態に制御することで前記第1補償動作を実行させ、

当該画素回路に対応する単位期間において、前記選択スイッチをオン状態に制御するとともに前記制御スイッチをオフ状態に制御して前記信号線に前記階調電位を供給することで前記第2補償動作を実行させ、

当該画素回路に対応する単位期間以外の各単位期間において、前記選択スイッチをオフ状態に制御する

請求項11の発光装置。 - 請求項8から請求項12の何れかの発光装置を具備する電子機器。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008226735A JP5369552B2 (ja) | 2008-09-04 | 2008-09-04 | 画素回路の駆動方法、発光装置および電子機器 |

| US12/544,563 US8599222B2 (en) | 2008-09-04 | 2009-08-20 | Method of driving pixel circuit, light emitting device, and electronic apparatus |

| US14/065,771 US9117399B2 (en) | 2008-09-04 | 2013-10-29 | Method of driving pixel circuit, light emitting device, and electronic apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008226735A JP5369552B2 (ja) | 2008-09-04 | 2008-09-04 | 画素回路の駆動方法、発光装置および電子機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010060867A JP2010060867A (ja) | 2010-03-18 |

| JP5369552B2 true JP5369552B2 (ja) | 2013-12-18 |

Family

ID=42187733

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008226735A Expired - Fee Related JP5369552B2 (ja) | 2008-09-04 | 2008-09-04 | 画素回路の駆動方法、発光装置および電子機器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5369552B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN105869574B (zh) * | 2016-06-07 | 2017-03-29 | 京东方科技集团股份有限公司 | 一种像素驱动电路及其驱动方法、阵列基板及显示装置 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4923527B2 (ja) * | 2005-11-14 | 2012-04-25 | ソニー株式会社 | 表示装置及びその駆動方法 |

| JP2007316454A (ja) * | 2006-05-29 | 2007-12-06 | Sony Corp | 画像表示装置 |

| JP4151714B2 (ja) * | 2006-07-19 | 2008-09-17 | ソニー株式会社 | 表示装置及びその駆動方法 |

| JP5130667B2 (ja) * | 2006-07-27 | 2013-01-30 | ソニー株式会社 | 表示装置 |

| JP4203772B2 (ja) * | 2006-08-01 | 2009-01-07 | ソニー株式会社 | 表示装置およびその駆動方法 |

| JP2008122647A (ja) * | 2006-11-13 | 2008-05-29 | Sony Corp | 表示装置、電気光学素子の駆動方法および電子機器 |

| JP2008164796A (ja) * | 2006-12-27 | 2008-07-17 | Sony Corp | 画素回路および表示装置とその駆動方法 |

| JP2008197516A (ja) * | 2007-02-15 | 2008-08-28 | Sony Corp | 表示装置とその駆動方法 |

-

2008

- 2008-09-04 JP JP2008226735A patent/JP5369552B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010060867A (ja) | 2010-03-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5287024B2 (ja) | 画素回路の駆動方法、発光装置および電子機器 | |

| US9117399B2 (en) | Method of driving pixel circuit, light emitting device, and electronic apparatus | |

| JP5326850B2 (ja) | 発光装置、発光装置の駆動方法および電子機器 | |

| JP5286992B2 (ja) | 電気光学装置および電子機器 | |

| JP5720100B2 (ja) | 発光装置、画素回路の駆動方法および電子機器 | |

| JP5458671B2 (ja) | 発光装置、発光装置の駆動方法および電子機器 | |

| JP5458540B2 (ja) | 画素回路の駆動方法、発光装置および電子機器 | |

| JP2011039269A (ja) | 発光装置、電子機器および発光装置の駆動方法 | |

| US8310416B2 (en) | Method of driving pixel circuit, light-emitting apparatus, and electronic apparatus | |

| JP2008083680A (ja) | 電気光学装置および電子機器 | |

| JP5412770B2 (ja) | 画素回路の駆動方法、発光装置および電子機器 | |

| JP2011008161A (ja) | 発光装置および電子機器、画素回路の駆動方法 | |

| JP2010286541A (ja) | 発光装置、電子機器、および発光装置の駆動方法 | |

| JP5374976B2 (ja) | 画素回路の駆動方法、発光装置および電子機器 | |

| JP5369578B2 (ja) | 画素回路の駆動方法、発光装置および電子機器 | |

| JP5439782B2 (ja) | 画素回路の駆動方法、発光装置および電子機器 | |

| JP5392963B2 (ja) | 電気光学装置及び電子機器 | |

| JP5332454B2 (ja) | 画素回路の駆動方法、発光装置および電子機器 | |

| JP2010281867A (ja) | 電気光学装置,電子機器および電気光学装置の駆動方法 | |

| JP5401895B2 (ja) | 画素回路の駆動方法、発光装置および電子機器 | |

| JP2011033678A (ja) | 発光装置、電子機器および発光装置の駆動方法 | |

| JP5369552B2 (ja) | 画素回路の駆動方法、発光装置および電子機器 | |

| JP2012113195A (ja) | 電気光学装置および電子機器 | |

| JP2011170033A (ja) | 発光装置および電子機器、画素回路の駆動方法 | |

| JP2013057701A (ja) | 電気光学装置,電子機器および電気光学装置の駆動方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110819 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121017 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121023 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121218 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130709 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130730 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130820 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130902 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5369552 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |