JP5339824B2 - 画像形成装置およびその制御方法 - Google Patents

画像形成装置およびその制御方法 Download PDFInfo

- Publication number

- JP5339824B2 JP5339824B2 JP2008229770A JP2008229770A JP5339824B2 JP 5339824 B2 JP5339824 B2 JP 5339824B2 JP 2008229770 A JP2008229770 A JP 2008229770A JP 2008229770 A JP2008229770 A JP 2008229770A JP 5339824 B2 JP5339824 B2 JP 5339824B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- image

- unit

- address

- pixel data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N1/00—Scanning, transmission or reproduction of documents or the like, e.g. facsimile transmission; Details thereof

- H04N1/04—Scanning arrangements, i.e. arrangements for the displacement of active reading or reproducing elements relative to the original or reproducing medium, or vice versa

- H04N1/047—Detection, control or error compensation of scanning velocity or position

- H04N1/0473—Detection, control or error compensation of scanning velocity or position in subscanning direction, e.g. picture start or line-to-line synchronisation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N1/00—Scanning, transmission or reproduction of documents or the like, e.g. facsimile transmission; Details thereof

- H04N1/04—Scanning arrangements, i.e. arrangements for the displacement of active reading or reproducing elements relative to the original or reproducing medium, or vice versa

- H04N1/113—Scanning arrangements, i.e. arrangements for the displacement of active reading or reproducing elements relative to the original or reproducing medium, or vice versa using oscillating or rotating mirrors

- H04N1/1135—Scanning arrangements, i.e. arrangements for the displacement of active reading or reproducing elements relative to the original or reproducing medium, or vice versa using oscillating or rotating mirrors for the main-scan only

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N1/00—Scanning, transmission or reproduction of documents or the like, e.g. facsimile transmission; Details thereof

- H04N1/04—Scanning arrangements, i.e. arrangements for the displacement of active reading or reproducing elements relative to the original or reproducing medium, or vice versa

- H04N1/12—Scanning arrangements, i.e. arrangements for the displacement of active reading or reproducing elements relative to the original or reproducing medium, or vice versa using the sheet-feed movement or the medium-advance or the drum-rotation movement as the slow scanning component, e.g. arrangements for the main-scanning

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N2201/00—Indexing scheme relating to scanning, transmission or reproduction of documents or the like, and to details thereof

- H04N2201/024—Indexing scheme relating to scanning, transmission or reproduction of documents or the like, and to details thereof deleted

- H04N2201/02406—Arrangements for positioning elements within a head

- H04N2201/02439—Positioning method

- H04N2201/02441—Positioning method using screws

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N2201/00—Indexing scheme relating to scanning, transmission or reproduction of documents or the like, and to details thereof

- H04N2201/04—Scanning arrangements

- H04N2201/047—Detection, control or error compensation of scanning velocity or position

- H04N2201/04753—Control or error compensation of scanning position or velocity

- H04N2201/04758—Control or error compensation of scanning position or velocity by controlling the position of the scanned image area

- H04N2201/04787—Control or error compensation of scanning position or velocity by controlling the position of the scanned image area by changing or controlling the addresses or values of pixels, e.g. in an array, in a memory, by interpolation

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N2201/00—Indexing scheme relating to scanning, transmission or reproduction of documents or the like, and to details thereof

- H04N2201/04—Scanning arrangements

- H04N2201/047—Detection, control or error compensation of scanning velocity or position

- H04N2201/04753—Control or error compensation of scanning position or velocity

- H04N2201/04793—Control or error compensation of scanning position or velocity using stored control or compensation data, e.g. previously measured data

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N2201/00—Indexing scheme relating to scanning, transmission or reproduction of documents or the like, and to details thereof

- H04N2201/04—Scanning arrangements

- H04N2201/047—Detection, control or error compensation of scanning velocity or position

- H04N2201/04753—Control or error compensation of scanning position or velocity

- H04N2201/04794—Varying the control or compensation during the scan, e.g. using continuous feedback or from line to line

- H04N2201/04796—Varying the sub-scan control during the main-scan, e.g. for correcting skew, tilt or bow of a scanning beam

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Record Information Processing For Printing (AREA)

- Laser Beam Printer (AREA)

- Control Or Security For Electrophotography (AREA)

Description

図1は本発明の第1の実施の形態に係る画像形成装置の構成を示す図である。本実施の形態においては、画像形成装置として、複数の機能を実現する複合機であるMFP(Multi Function Peripheral)について説明する。

(*2) : Reg_SINGLE_MODEとは、ライン端部のデータをどのように処理するかを選択するモードレジスタである。1ページの画像データを画像メモリ203上に隙間無く詰めて格納する場合は、ライン端部の端数データに対してシングルアクセスモード(single access mode)によるアクセスを行う必要がある。このモードは、メモリ容量を削減する場合に有効である。これに対し、バースト転送モード(burst transfer mode)は、ライン端部の端数データ(ダミーデータ)をパディングしてデータバッファ部307にバースト転送し、バースト長分格納することが可能なモードである。このバースト転送モードは、パフォーマンスを優先する場合に有効となる。Reg_SINGLE_BYTEレジスタは、シングルアクセスモード(Reg_SINGLE_MODE)が有効か否かに応じてデータの有効および無効を判断するためのものである。

次に、本発明の第2の実施の形態について図17および図18を参照しながら説明する。図17(a)は本発明の第2の実施の形態において画像印字部106における走査ラインの曲がりを補正する際の画像の曲がりの一例を示す図である。図17(b)は図17(a)の画像の曲がりに応じてDMAコントローラ301により画像メモリ203に書き込まれた画像データを模式的に示す図である。図18は図17の画像の曲がりを得るために設定されるレジスタ情報を示す図である。

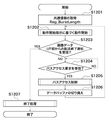

次に、本発明の第3の実施の形態について図19〜図23を参照しながら説明する。図19は本発明の第3の実施の形態に係る画像形成装置のデータ処理部の構成を示すブロック図である。図20は図19のDMAコントローラ209の構成を示すブロック図である。図21はバスインタフェース部309の動作の手順を示すフローチャートである。図22は画像データI/F部304の動作の手順を示すフローチャートである。図23は第1の実施形態と第3の実施形態の差異を説明するための図である。ここで、図中、上記第1の実施の形態と同じブロックには、同一の符号を付し、その説明は、省略する。

次に、本発明の第4の実施の形態について図24〜図26を参照しながら説明する。図24は本発明の第4の実施の形態に係る画像形成装置のDMAコントローラの構成を示すブロック図である。図25は図24のバスアクセス情報部306の動作を示すフローチャートである。図26は図24のRAM2104における画像データの格納状態を示す図である。ここで、図中、上記第1の実施の形態と同じブロックには、同一の符号を付し、その説明は、省略する。

101 データ処理部

108 デバイス制御部

109 読取データ処理部

110 印字データ処理部

209 DMAコントローラ

210 画像処理部

300,301 DMAコントローラ

302 レジスタ部

304 画像データI/F部

306 バスアクセス情報部

307 データバッファ部

308 アドレスレジスタ部

309 バスインタフェース部

Claims (4)

- 画像形成手段を備え、該画像形成手段の走査ラインの曲がりを補正するための曲がり補正を画像データに行い、さらに、前記曲がり補正が行われた画像データに基づいて前記画像形成手段によって画像形成を実行する画像形成装置において、

画像データをライン単位で入力する入力手段と、

前記入力手段により入力され、前記曲がり補正が行われた画像データを記憶する記憶手段と、

前記記憶手段の書き込み領域における副走査方向の複数のアドレスに一対一で対応する複数のデータ保持手段であって、各々が前記画像データの1ライン分の画素数よりも少ない所定数の画素データを保持する複数のデータ保持手段と、

前記複数のデータ保持手段に一対一で対応する複数のアドレス保持手段であって、各前記データ保持手段に保持された前記所定数の画素データを前記記憶手段へ記憶させる際に用いられる前記所定数の画素データの各々の主走査方向のアドレスを保持する複数のアドレス保持手段と、

前記曲がり補正において主走査方向の各アドレスにおける前記画素データを副走査方向へシフトさせる際の当該画素データのシフト量を示す曲がり情報に基づいて、前記ライン単位で入力された画像データを構成する画素データの各々を、前記複数のデータ保持手段のうち、当該画素データの前記曲がり補正における前記シフト量に対応する副走査方向のアドレスに対応する前記データ保持手段に書き込むとともに、当該画素データの主走査方向のアドレスを、当該画素データが書き込まれた前記データ保持手段に対応する前記アドレス保持手段に保持させる書き込み手段と、

前記複数のデータ保持手段のうち特定のデータ保持手段に前記所定数の画素データが書き込まれたことに応じて、前記所定数の画素データの各々を、前記記憶手段の書き込み領域における当該画素データが書き込まれた前記データ保持手段に対応する副走査方向のアドレスであって、当該画素データが書き込まれた前記データ保持手段に対応する前記アドレス保持手段に保持された主走査方向のアドレスである記憶先アドレスに記憶させるように制御する制御手段と、

前記記憶手段に記憶された画像データをライン単位で前記画像形成手段に転送する転送手段と、

を備えることを特徴とする画像形成装置。 - 前記複数のデータ保持手段の各々は、バースト転送量に対応する数の画素データを保持可能であることを特徴とする請求項1に記載の画像形成装置。

- 前記制御手段は、前記特定のデータ保持手段に前記バースト転送量に対応する数の画素データが書き込まれたことに応じて、当該バースト転送量に対応する数の画素データの各々が対応する前記記憶先アドレスへ記憶されるように、前記バースト転送量に対応する数の画素データをバースト転送で前記記憶手段へ転送して記憶させることを特徴とする請求項2に記載の画像形成装置。

- 画像形成手段を備え、該画像形成手段の走査ラインの曲がりを補正するための曲がり補正を画像データに行い、さらに、前記曲がり補正が行われた画像データに基づいて前記画像形成手段によって画像形成を実行する画像形成装置の制御方法において、

画像データをライン単位で入力する入力工程と、

前記入力工程で入力され、前記曲がり補正が行われた画像データを記憶手段に記憶する記憶工程と、

前記記憶手段の書き込み領域における副走査方向の複数のアドレスに一対一で対応する複数のデータ保持手段の各々が前記画像データの1ライン分の画素数よりも少ない所定数の画素データを保持するデータ保持工程と、

前記複数のデータ保持手段に一対一で対応する複数のアドレス保持手段が、各前記データ保持手段に保持された前記所定数の画素データを前記記憶手段へ記憶させる際に用いられる前記所定数の画素データの各々の主走査方向のアドレスを保持するアドレス保持工程と、

前記曲がり補正において主走査方向の各アドレスにおける前記画素データを副走査方向へシフトさせる際の当該画素データのシフト量を示す曲がり情報に基づいて、前記ライン単位で入力された画像データを構成する画素データの各々を、前記複数のデータ保持手段のうち、当該画素データの前記曲がり補正における前記シフト量に対応する副走査方向のアドレスに対応する前記データ保持手段に書き込むとともに、当該画素データの主走査方向のアドレスを、当該画素データが書き込まれた前記データ保持手段に対応する前記アドレス保持手段に保持させる書き込み工程と、

前記複数のデータ保持手段のうち特定のデータ保持手段に前記所定数の画素データが書き込まれたことに応じて、前記所定数の画素データの各々を、前記記憶手段の書き込み領域における当該画素データが書き込まれた前記データ保持手段に対応する副走査方向のアドレスであって、当該画素データが書き込まれた前記データ保持手段に対応する前記アドレス保持手段に保持された主走査方向のアドレスである記憶先アドレスに記憶させるように制御する制御工程と、

前記記憶工程で前記記憶手段に記憶された画像データをライン単位で前記画像形成手段に転送する転送工程と、

を備えることを特徴とする画像形成装置の制御方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008229770A JP5339824B2 (ja) | 2008-09-08 | 2008-09-08 | 画像形成装置およびその制御方法 |

| US12/554,300 US8542395B2 (en) | 2008-09-08 | 2009-09-04 | Image forming apparatus and control method therefor |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008229770A JP5339824B2 (ja) | 2008-09-08 | 2008-09-08 | 画像形成装置およびその制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010064254A JP2010064254A (ja) | 2010-03-25 |

| JP2010064254A5 JP2010064254A5 (ja) | 2011-10-27 |

| JP5339824B2 true JP5339824B2 (ja) | 2013-11-13 |

Family

ID=41799027

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008229770A Expired - Fee Related JP5339824B2 (ja) | 2008-09-08 | 2008-09-08 | 画像形成装置およびその制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8542395B2 (ja) |

| JP (1) | JP5339824B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5750899B2 (ja) * | 2011-01-17 | 2015-07-22 | 株式会社リコー | 画像形成装置およびその制御方法 |

| JP6270597B2 (ja) * | 2014-04-04 | 2018-01-31 | キヤノン株式会社 | 画像形成装置 |

| JP6690232B2 (ja) | 2015-12-25 | 2020-04-28 | 株式会社リコー | 画像処理装置、画像形成装置、画像処理方法及びプログラム |

| US10380969B2 (en) * | 2016-02-28 | 2019-08-13 | Google Llc | Macro I/O unit for image processor |

| JP2017175404A (ja) * | 2016-03-24 | 2017-09-28 | コニカミノルタ株式会社 | 画像形成装置及びプログラム |

| JP7256660B2 (ja) * | 2019-03-13 | 2023-04-12 | キヤノン株式会社 | 画像形成装置、その制御方法、及びプログラム |

| US10990782B2 (en) * | 2019-09-09 | 2021-04-27 | Novatek Microelectronics Corp. | Operating method of an optical fingerprint capture apparatus and operating method of an optical fingerprint recognition system |

| CN112862724B (zh) * | 2021-03-12 | 2022-09-09 | 上海壁仞智能科技有限公司 | 用于计算的方法、计算设备和计算机可读存储介质 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH08184772A (ja) * | 1994-12-28 | 1996-07-16 | Minolta Co Ltd | 光ビーム走査方法及び光ビーム走査装置 |

| US6934049B1 (en) * | 1999-09-13 | 2005-08-23 | Minolta Co., Ltd. | Data processing apparatus |

| JP2001080124A (ja) * | 1999-09-13 | 2001-03-27 | Minolta Co Ltd | 印字装置 |

| JP2003058418A (ja) * | 2001-08-09 | 2003-02-28 | Canon Inc | 画像形成装置 |

| JP2003241131A (ja) | 2002-02-22 | 2003-08-27 | Canon Inc | 偏向走査装置及び画像形成装置 |

| JP3600228B2 (ja) * | 2002-03-01 | 2004-12-15 | 株式会社リコー | 光走査装置および画像形成装置 |

| JP2004170755A (ja) | 2002-11-21 | 2004-06-17 | Canon Inc | カラー画像形成装置 |

| US20060227198A1 (en) * | 2005-04-08 | 2006-10-12 | Eastman Kodak Company | Electronic bow correction and registration control for a printer |

| JP2007090620A (ja) * | 2005-09-28 | 2007-04-12 | Matsushita Electric Ind Co Ltd | 画像形成装置および画像形成装置の制御方法 |

| JP2010011429A (ja) * | 2008-06-30 | 2010-01-14 | Canon Inc | 画像処理装置及び画像処理装置の制御方法 |

-

2008

- 2008-09-08 JP JP2008229770A patent/JP5339824B2/ja not_active Expired - Fee Related

-

2009

- 2009-09-04 US US12/554,300 patent/US8542395B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010064254A (ja) | 2010-03-25 |

| US8542395B2 (en) | 2013-09-24 |

| US20100060933A1 (en) | 2010-03-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5339824B2 (ja) | 画像形成装置およびその制御方法 | |

| US7859720B2 (en) | Image forming apparatus and method thereof | |

| JP4865529B2 (ja) | 画像形成システム及び画像形成装置並びにその画像形成方法 | |

| JP5812669B2 (ja) | 画像処理装置および画像処理方法およびコンピュータプログラム。 | |

| US20010015821A1 (en) | Method and apparatus for image processing method, and a computer product | |

| US20100103435A1 (en) | Image processing apparatus and image processing method for processing screen-processed image | |

| US8441690B2 (en) | Image processing apparatus and image processing method for processing screen-processed image | |

| JP4891273B2 (ja) | 画像形成装置及びその制御方法 | |

| JP4948448B2 (ja) | 画像処理装置及びその制御方法 | |

| JP3902907B2 (ja) | 画像処理装置及び方法と画像形成装置 | |

| JP5921155B2 (ja) | 画像処理装置、画像処理方法、コンピュータプログラム | |

| JP2007122478A (ja) | 印刷制御装置、印刷制御方法、プログラム、及び記憶媒体 | |

| JP5643045B2 (ja) | 複数のラインの印刷データを、マルチビーム印刷エンジンに用いられるマルチビーム用のライン順序に並べ替える方法、画像形成装置及び媒体 | |

| JP2010041383A (ja) | 画像処理装置、画像読取装置、画像形成装置 | |

| JP5754972B2 (ja) | 画像処理装置及び画像処理方法 | |

| JP5662675B2 (ja) | 画像形成装置及びその制御方法 | |

| JP5574727B2 (ja) | 画像形成装置及びその制御方法 | |

| US8437046B2 (en) | Image processing apparatus and method for outputting an image subjected to pseudo-halftone processing | |

| JP4753253B2 (ja) | 画像処理装置 | |

| JP7256660B2 (ja) | 画像形成装置、その制御方法、及びプログラム | |

| JP5709708B2 (ja) | 画像形成装置 | |

| JP3785295B2 (ja) | 画像処理装置 | |

| JP2002271615A (ja) | 画像処理装置及び画像形成装置 | |

| JP2009180920A (ja) | 画像形成装置及びそのデータ転送方法 | |

| JP2010056637A (ja) | 画像形成装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110908 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110908 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130226 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130430 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130709 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130806 |

|

| LAPS | Cancellation because of no payment of annual fees |