JP5336030B2 - 回路保護ユニットを備える発光装置 - Google Patents

回路保護ユニットを備える発光装置 Download PDFInfo

- Publication number

- JP5336030B2 JP5336030B2 JP2005291277A JP2005291277A JP5336030B2 JP 5336030 B2 JP5336030 B2 JP 5336030B2 JP 2005291277 A JP2005291277 A JP 2005291277A JP 2005291277 A JP2005291277 A JP 2005291277A JP 5336030 B2 JP5336030 B2 JP 5336030B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- light emitting

- emitting device

- potential barrier

- barrier layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000005036 potential barrier Methods 0.000 claims abstract description 87

- 230000004888 barrier function Effects 0.000 claims abstract description 18

- 239000004065 semiconductor Substances 0.000 claims description 20

- 239000000758 substrate Substances 0.000 claims description 16

- 229910052782 aluminium Inorganic materials 0.000 claims description 8

- 229910052804 chromium Inorganic materials 0.000 claims description 7

- 229910052737 gold Inorganic materials 0.000 claims description 7

- 229910052751 metal Inorganic materials 0.000 claims description 7

- 239000002184 metal Substances 0.000 claims description 7

- 229910052710 silicon Inorganic materials 0.000 claims description 7

- 229910052718 tin Inorganic materials 0.000 claims description 7

- UHYPYGJEEGLRJD-UHFFFAOYSA-N cadmium(2+);selenium(2-) Chemical compound [Se-2].[Cd+2] UHYPYGJEEGLRJD-UHFFFAOYSA-N 0.000 claims description 6

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 claims description 5

- 229910052790 beryllium Inorganic materials 0.000 claims description 5

- 229910052799 carbon Inorganic materials 0.000 claims description 5

- 229910052732 germanium Inorganic materials 0.000 claims description 5

- 229910052749 magnesium Inorganic materials 0.000 claims description 5

- 229910052759 nickel Inorganic materials 0.000 claims description 5

- 229910052717 sulfur Inorganic materials 0.000 claims description 5

- 229910052725 zinc Inorganic materials 0.000 claims description 5

- -1 MnTiO3 Inorganic materials 0.000 claims description 3

- 239000004642 Polyimide Substances 0.000 claims description 3

- 229910052738 indium Inorganic materials 0.000 claims description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 claims description 3

- 229920001721 polyimide Polymers 0.000 claims description 3

- 229910004298 SiO 2 Inorganic materials 0.000 claims description 2

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 claims 8

- 239000010931 gold Substances 0.000 claims 5

- MCMNRKCIXSYSNV-UHFFFAOYSA-N Zirconium dioxide Chemical compound O=[Zr]=O MCMNRKCIXSYSNV-UHFFFAOYSA-N 0.000 claims 4

- ZKATWMILCYLAPD-UHFFFAOYSA-N niobium pentoxide Chemical compound O=[Nb](=O)O[Nb](=O)=O ZKATWMILCYLAPD-UHFFFAOYSA-N 0.000 claims 4

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 claims 4

- 239000011787 zinc oxide Substances 0.000 claims 4

- 229910005451 FeTiO3 Inorganic materials 0.000 claims 2

- 229910005540 GaP Inorganic materials 0.000 claims 2

- 229910002370 SrTiO3 Inorganic materials 0.000 claims 2

- 229910002113 barium titanate Inorganic materials 0.000 claims 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 claims 2

- BEQNOZDXPONEMR-UHFFFAOYSA-N cadmium;oxotin Chemical compound [Cd].[Sn]=O BEQNOZDXPONEMR-UHFFFAOYSA-N 0.000 claims 2

- BCCOBQSFUDVTJQ-UHFFFAOYSA-N octafluorocyclobutane Chemical compound FC1(F)C(F)(F)C(F)(F)C1(F)F BCCOBQSFUDVTJQ-UHFFFAOYSA-N 0.000 claims 2

- 235000019407 octafluorocyclobutane Nutrition 0.000 claims 2

- KYKLWYKWCAYAJY-UHFFFAOYSA-N oxotin;zinc Chemical compound [Zn].[Sn]=O KYKLWYKWCAYAJY-UHFFFAOYSA-N 0.000 claims 2

- SKRWFPLZQAAQSU-UHFFFAOYSA-N stibanylidynetin;hydrate Chemical compound O.[Sn].[Sb] SKRWFPLZQAAQSU-UHFFFAOYSA-N 0.000 claims 2

- ZNOKGRXACCSDPY-UHFFFAOYSA-N tungsten(VI) oxide Inorganic materials O=[W](=O)=O ZNOKGRXACCSDPY-UHFFFAOYSA-N 0.000 claims 2

- 239000011701 zinc Substances 0.000 claims 2

- 229910004205 SiNX Inorganic materials 0.000 claims 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 claims 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 claims 1

- 229910045601 alloy Inorganic materials 0.000 claims 1

- 239000000956 alloy Substances 0.000 claims 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims 1

- 229910052733 gallium Inorganic materials 0.000 claims 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 claims 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical group [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 claims 1

- 229910052757 nitrogen Inorganic materials 0.000 claims 1

- 229910052709 silver Inorganic materials 0.000 claims 1

- 239000004332 silver Substances 0.000 claims 1

- 230000005611 electricity Effects 0.000 abstract description 2

- 230000003068 static effect Effects 0.000 abstract description 2

- 239000010410 layer Substances 0.000 description 231

- 239000000463 material Substances 0.000 description 59

- 239000002019 doping agent Substances 0.000 description 10

- 229910006404 SnO 2 Inorganic materials 0.000 description 9

- 229910007717 ZnSnO Inorganic materials 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 7

- 239000010936 titanium Substances 0.000 description 6

- 229910052719 titanium Inorganic materials 0.000 description 6

- 150000001875 compounds Chemical class 0.000 description 5

- 238000000034 method Methods 0.000 description 5

- 229910002367 SrTiO Inorganic materials 0.000 description 4

- 229910010413 TiO 2 Inorganic materials 0.000 description 4

- 230000015556 catabolic process Effects 0.000 description 4

- 229910002704 AlGaN Inorganic materials 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- 238000004806 packaging method and process Methods 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 229910017911 MgIn Inorganic materials 0.000 description 1

- 208000016791 bilateral striopallidodentate calcinosis Diseases 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000010292 electrical insulation Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 238000005476 soldering Methods 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/40—Materials therefor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/15—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components having potential barriers, specially adapted for light emission

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16135—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/16145—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/48145—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/02—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor bodies

- H01L33/26—Materials of the light emitting region

- H01L33/30—Materials of the light emitting region containing only elements of Group III and Group V of the Periodic Table

- H01L33/32—Materials of the light emitting region containing only elements of Group III and Group V of the Periodic Table containing nitrogen

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/36—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes

- H01L33/38—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the electrodes with a particular shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/04—Processes or apparatus for excitation, e.g. pumping, e.g. by electron beams

- H01S5/042—Electrical excitation ; Circuits therefor

- H01S5/0421—Electrical excitation ; Circuits therefor characterised by the semiconducting contacting layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01S—DEVICES USING THE PROCESS OF LIGHT AMPLIFICATION BY STIMULATED EMISSION OF RADIATION [LASER] TO AMPLIFY OR GENERATE LIGHT; DEVICES USING STIMULATED EMISSION OF ELECTROMAGNETIC RADIATION IN WAVE RANGES OTHER THAN OPTICAL

- H01S5/00—Semiconductor lasers

- H01S5/06—Arrangements for controlling the laser output parameters, e.g. by operating on the active medium

- H01S5/068—Stabilisation of laser output parameters

- H01S5/06825—Protecting the laser, e.g. during switch-on/off, detection of malfunctioning or degradation

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Led Devices (AREA)

- Electroluminescent Light Sources (AREA)

Description

1.低抵抗層材料は、仕事関数がΦLの金属であり、電位バリア層は、仕事関数がΦBのn型半導体材料であり、ΦL>ΦBとして、バリア電位=ΦL−ΦBである。

2.低抵抗層材料は、仕事関数がΦLの金属であり、電位バリア層は、仕事関数がΦBのp型半導体材料であり、ΦL<ΦBとして、バリア電位=ΦB−ΦLである。

3.低抵抗層材料は、仕事関数がΦLの透明導電性酸化物層(TCO)、例えばITO、CTO、Zn2SnO4、ZnSnO3、MgIn2O4、Zn2In2O5、In4Sn3O12、AgInO2SnまたはIn2O3Znおよび他の半導体化合物であり、電位バリア層は、仕事関数がΦBのn型半導体材料であり、ΦL>ΦBとして、バリア電位=ΦL−ΦBである。

4.低抵抗層材料は、仕事関数がΦLの透明導電性酸化物層であり、電位バリア層は、仕事関数がΦBのp型半導体材料であり、ΦL<ΦBとして、バリア電位=ΦB−ΦLである。

5.低抵抗層材料は、仕事関数がΦLのn型半導体材料であり、電位バリア層は、仕事関数がΦBのp型半導体材料であり、ΦL<ΦBとして、バリア電位=ΦB−ΦLである。

2 第2の発光装置

3 第3の発光装置

4 第4の発光装置

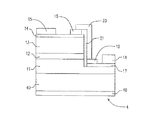

10 基板

11 第1のスタッキング層

12 発光層

13 第2のスタッキング層

14 第1の低抵抗層

15 第1の電極

16 第1の電位バリア層

17 第2の低抵抗層

18 第2の電極

19 第2の電位バリア層

20 電気接続層

24 第1のオーム接続層

27 第2のオーム接続層

28 第1の低抵抗層

29 第1の電気接続層

30 第2の電気接続層

31 絶縁層

40 導電性基板

48 第2の電極

301 結合層

Claims (17)

- 回路保護ユニットを有する発光装置であって、

第1の表面と第2の表面を有する発光スタッキング層であって、前記第2の表面を有する第1の半導体層と、前記第1の半導体層上に形成される発光層と、前記第1の表面を有し、前記発光層上に形成される第2の半導体層とを含む、発光スタッキング層と、

前記第1の表面と前記第2の表面の何れかに位置し、前記第1の表面と前記第2の表面にそれぞれ電気的に接続されて整流機能を提供する少なくとも一つの回路保護ユニットと、

を含み、

前記回路保護ユニットは、第1の抵抗層と第1の電位バリア層とを有し、前記第1の抵抗層と前記第1の電位バリア層との間の界面には、バリア電位が存在し、

前記第1の抵抗層と前記第1の電位バリア層との間の界面は、ショットキー界面又はp−n界面であり、

前記回路保護ユニットは、前記第1の表面と前記第2の表面に電気的に接続される電気接続層を更に含み、

前記回路保護ユニットは、前記第1の表面と前記第2の表面の他の表面に位置する第2の抵抗層と第2の電位バリア層を更に含む、発光装置。 - 前記発光スタッキング層は、Al、Ga、In、N又はPを含む、請求項1に記載の発光装置。

- 前記第1の抵抗層は、Ni/Au、NiO/Au、TiWN、透光性金属層、酸化インジウムスズ、酸化カドミウムスズ、酸化アンチモンスズ、酸化亜鉛、及び、酸化亜鉛スズからなるグループより選択される少なくとも一つを含む、請求項1に記載の発光装置。

- 前記第1の電位バリア層は、TiO2、SrTiO3、FeTiO3、MnTiO3、BaTiO3、ZrO2、Nb2O5、KTaO3、WO3、ZnO、SnO2、GaP、Si、SiC、CdSe、及び、CdSからなるグループより選択される少なくとも一つを含む、請求項1に記載の発光装置。

- 前記第1の電位バリア層には、Mg、Zn、Be、Cr、Si、Ge、Sn、Te、O、S及びCからなるグループより選択される一つがドーピングされる、請求項4に記載の発光装置。

- 前記第1の抵抗層上に位置する電極を更に含む、請求項1に記載の発光装置。

- 前記発光スタッキング層の側壁と前記回路保護ユニットとの間に形成される絶縁層を更に含む、請求項1に記載の発光装置。

- 前記絶縁層は、SiNx又はSiO2を含む、請求項7に記載の発光装置。

- 前記第1の抵抗層は、仕事関数ΦLを有し、前記第1の電位バリア層は、仕事関数ΦBを有し、

前記第1の抵抗層は、金属又は透明導電性酸化物であり、且つ、前記第1の電位バリア層は、n型半導体であるときに、ΦL>ΦBであり、

前記第1の抵抗層は、金属又は透明導電性酸化物であり、且つ、前記第1の電位バリア層は、p型半導体であるときに、ΦL<ΦBであり、

前記第1の抵抗層は、n型半導体であり、且つ、前記第1の電位パリア層は、p型半導体であるときに、ΦL<ΦBである、請求項1に記載の発光装置。 - 前記第2の抵抗層は、Ni/Au、NiO/Au、TiWN、透光性金属層、酸化インジウムスズ、酸化カドミウムスズ、酸化アンチモンスズ、酸化亜鉛、及び、酸化亜鉛スズからなるグループより選択される少なくとも一つを含む、請求項1に記載の発光装置。

- 前記第2の電位バリア層は、TiO2、SrTiO3、FeTiO3、MnTiO3、BaTiO3、ZrO2、Nb2O5、KTaO3、WO3、ZnO、SnO2、GaP、Si、SiC、CdSe、及び、CdSからなるグループより選択される少なくとも一つを含む、請求項1に記載の発光装置。

- 前記第2の抵抗層と前記第2の電位バリア層との間の界面は、ショットキー界面又はp−n界面である、請求項1に記載の発光装置。

- 前記第2の電位バリア層には、Mg、Zn、Be、Cr、Si、Ge、Sn、Te、O、S及びCからなるグループより選択される一つがドーピングされる、請求項11に記載の発光装置。

- 前記第2の抵抗層上に位置する電極を更に含む、請求項1に記載の発光装置。

- 前記発光スタッキング層の下に位置する基板を更に含む、請求項1に記載の発光装置。

- 前記発光スタッキング層と前記基板との間に位置する接続層を更に含む、請求項15に記載の発光装置。

- 前記接続層は、インジウム、錫、金、アルミニウム、銀とその合金、ポリイミド(PI)、BCB(Benzocyclobutane)及びPFCB(Perfluorocyclobutane)からなるグループより選択される少なくとも一つを含む、請求項16に記載の発光装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| TW093130813 | 2004-10-08 | ||

| TW093130813A TWI244748B (en) | 2004-10-08 | 2004-10-08 | A light-emitting device with a protecting structure |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006108682A JP2006108682A (ja) | 2006-04-20 |

| JP2006108682A5 JP2006108682A5 (ja) | 2008-11-20 |

| JP5336030B2 true JP5336030B2 (ja) | 2013-11-06 |

Family

ID=36120746

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005291277A Expired - Fee Related JP5336030B2 (ja) | 2004-10-08 | 2005-10-04 | 回路保護ユニットを備える発光装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7683383B2 (ja) |

| JP (1) | JP5336030B2 (ja) |

| KR (1) | KR101056457B1 (ja) |

| DE (1) | DE102005043649A1 (ja) |

| TW (1) | TWI244748B (ja) |

Families Citing this family (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100833313B1 (ko) * | 2006-01-02 | 2008-05-28 | 삼성전기주식회사 | 질화갈륨계 발광다이오드 소자 및 그의 제조방법 |

| JP4694395B2 (ja) * | 2006-03-22 | 2011-06-08 | 日本オプネクスト株式会社 | 窒化物半導体発光素子及びその製造方法 |

| US7994514B2 (en) * | 2006-04-21 | 2011-08-09 | Koninklijke Philips Electronics N.V. | Semiconductor light emitting device with integrated electronic components |

| GB2439358B (en) * | 2006-06-19 | 2010-12-15 | Cambridge Display Tech Ltd | Organic electroluminescent optocouplers |

| US8148733B2 (en) | 2007-06-12 | 2012-04-03 | SemiLEDs Optoelectronics Co., Ltd. | Vertical LED with current guiding structure |

| US7759670B2 (en) * | 2007-06-12 | 2010-07-20 | SemiLEDs Optoelectronics Co., Ltd. | Vertical LED with current guiding structure |

| US8546818B2 (en) | 2007-06-12 | 2013-10-01 | SemiLEDs Optoelectronics Co., Ltd. | Vertical LED with current-guiding structure |

| DE102007057672A1 (de) * | 2007-11-30 | 2009-06-04 | Osram Opto Semiconductors Gmbh | Optoelektronischer Halbleiterkörper |

| KR101438811B1 (ko) * | 2008-01-03 | 2014-09-05 | 엘지이노텍 주식회사 | 반도체 발광소자 및 그 제조방법 |

| KR101457204B1 (ko) * | 2008-02-01 | 2014-11-03 | 서울바이오시스 주식회사 | 발광 다이오드 및 그 제조방법 |

| US7923744B2 (en) * | 2008-02-22 | 2011-04-12 | Huga Optotech Inc. | Semiconductor light-emitting device |

| TWI371873B (en) * | 2008-02-22 | 2012-09-01 | Huga Optotech Inc | Semiconductor light-emitting device |

| US8884321B2 (en) * | 2008-04-06 | 2014-11-11 | Lg Innotek Co., Ltd. | Luminous element |

| DE102008034560B4 (de) * | 2008-07-24 | 2022-10-27 | OSRAM Opto Semiconductors Gesellschaft mit beschränkter Haftung | Strahlungsemittierender Halbleiterchip und Verfahren zur Herstellung eines strahlungsemittierenden Halbleiterchips |

| CN101656260B (zh) * | 2009-09-08 | 2011-09-21 | 厦门市三安光电科技有限公司 | 一种抗静电氮化镓基发光器件及其制作方法 |

| KR101039896B1 (ko) * | 2009-12-03 | 2011-06-09 | 엘지이노텍 주식회사 | 발광소자 및 그 제조방법 |

| KR100999692B1 (ko) * | 2010-02-18 | 2010-12-08 | 엘지이노텍 주식회사 | 발광 소자, 발광 소자 제조방법 및 발광 소자 패키지 |

| KR101028206B1 (ko) * | 2010-04-08 | 2011-04-11 | 엘지이노텍 주식회사 | 발광소자, 발광소자의 제조방법 및 발광소자 패키지 |

| JP5281612B2 (ja) * | 2010-05-26 | 2013-09-04 | 株式会社東芝 | 半導体発光装置及びその製造方法 |

| US9548286B2 (en) * | 2010-08-09 | 2017-01-17 | Micron Technology, Inc. | Solid state lights with thermal control elements |

| KR101785644B1 (ko) | 2011-01-26 | 2017-10-16 | 엘지이노텍 주식회사 | 발광소자 및 그 발광 소자의 제조 방법 |

| EP2686892B1 (en) | 2011-03-14 | 2019-10-02 | Lumileds Holding B.V. | Led having vertical contacts redistributed for flip chip mounting |

| US8809897B2 (en) | 2011-08-31 | 2014-08-19 | Micron Technology, Inc. | Solid state transducer devices, including devices having integrated electrostatic discharge protection, and associated systems and methods |

| US9490239B2 (en) | 2011-08-31 | 2016-11-08 | Micron Technology, Inc. | Solid state transducers with state detection, and associated systems and methods |

| KR102085897B1 (ko) * | 2013-06-10 | 2020-03-06 | 엘지이노텍 주식회사 | 발광 소자 및 발광 소자 패키지 |

| KR102255196B1 (ko) | 2014-02-03 | 2021-05-25 | 삼성디스플레이 주식회사 | 플렉서블 디스플레이 장치 및 그 제조 방법 |

| KR101553372B1 (ko) * | 2014-03-28 | 2015-09-15 | 전북대학교산학협력단 | 자발 보호 기능을 겸비한 발광 소자 |

| KR102224245B1 (ko) * | 2015-01-26 | 2021-03-08 | 엘지이노텍 주식회사 | 발광소자, 발광소자 패키지, 및 이를 포함하는 조명시스템 |

| CN109860364B (zh) * | 2017-08-30 | 2020-09-01 | 天津三安光电有限公司 | 发光二极管 |

| CN108172668B (zh) * | 2018-01-16 | 2020-02-11 | 福建兆元光电有限公司 | 一种发光二极管 |

| KR20200075430A (ko) | 2018-12-18 | 2020-06-26 | 김은혜 | 미용실용 고객관리 카드 |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06112525A (ja) * | 1992-09-25 | 1994-04-22 | Nisshin Steel Co Ltd | 発光デバイス用ヘテロ接合素子 |

| JPH06267301A (ja) * | 1993-03-15 | 1994-09-22 | Olympus Optical Co Ltd | 有機ホトルミネッセンス素子 |

| JPH1065215A (ja) | 1996-08-22 | 1998-03-06 | Toyoda Gosei Co Ltd | Iii族窒化物半導体発光素子 |

| JP3787202B2 (ja) * | 1997-01-10 | 2006-06-21 | ローム株式会社 | 半導体発光素子 |

| JP3257455B2 (ja) * | 1997-07-17 | 2002-02-18 | 松下電器産業株式会社 | 発光装置 |

| JP3914615B2 (ja) * | 1997-08-19 | 2007-05-16 | 住友電気工業株式会社 | 半導体発光素子及びその製造方法 |

| JPH11298041A (ja) * | 1998-04-15 | 1999-10-29 | Toyoda Gosei Co Ltd | 3族窒化物半導体発光素子及び光源装置 |

| JP2950811B1 (ja) * | 1998-05-22 | 1999-09-20 | 株式会社エイ・ティ・アール環境適応通信研究所 | 超格子半導体発光素子 |

| JP3686569B2 (ja) * | 2000-03-02 | 2005-08-24 | シャープ株式会社 | 半導体発光装置及びそれを用いた表示装置 |

| US6693352B1 (en) | 2000-06-05 | 2004-02-17 | Emitronix Inc. | Contact structure for group III-V semiconductor devices and method of producing the same |

| JP2002368103A (ja) | 2001-06-05 | 2002-12-20 | Hitachi Ltd | 半導体装置とその製造方法 |

| JP3791765B2 (ja) * | 2001-06-08 | 2006-06-28 | 豊田合成株式会社 | Iii族窒化物系化合物半導体発光素子 |

| JP2003289176A (ja) * | 2002-01-24 | 2003-10-10 | Sony Corp | 半導体発光素子およびその製造方法 |

| TW577184B (en) * | 2002-12-26 | 2004-02-21 | Epistar Corp | Light emitting layer having voltage/resistance interdependent layer |

| TW579610B (en) * | 2003-01-30 | 2004-03-11 | Epistar Corp | Nitride light-emitting device having adhered reflective layer |

| TWI229463B (en) * | 2004-02-02 | 2005-03-11 | South Epitaxy Corp | Light-emitting diode structure with electro-static discharge protection |

| US20050218414A1 (en) * | 2004-03-30 | 2005-10-06 | Tetsuzo Ueda | 4H-polytype gallium nitride-based semiconductor device on a 4H-polytype substrate |

-

2004

- 2004-10-08 TW TW093130813A patent/TWI244748B/zh not_active IP Right Cessation

-

2005

- 2005-09-02 KR KR1020050081565A patent/KR101056457B1/ko active IP Right Grant

- 2005-09-08 US US11/222,922 patent/US7683383B2/en not_active Expired - Fee Related

- 2005-09-13 DE DE102005043649A patent/DE102005043649A1/de not_active Ceased

- 2005-10-04 JP JP2005291277A patent/JP5336030B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR101056457B1 (ko) | 2011-08-11 |

| KR20060050956A (ko) | 2006-05-19 |

| US7683383B2 (en) | 2010-03-23 |

| US20060081857A1 (en) | 2006-04-20 |

| JP2006108682A (ja) | 2006-04-20 |

| TW200612541A (en) | 2006-04-16 |

| TWI244748B (en) | 2005-12-01 |

| DE102005043649A1 (de) | 2006-04-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5336030B2 (ja) | 回路保護ユニットを備える発光装置 | |

| JP4697397B2 (ja) | 複合半導体装置 | |

| US7652296B2 (en) | Light emitting device with high light extraction efficiency | |

| JP5466156B2 (ja) | 電流誘導構造を備えた縦型led | |

| EP2225783B1 (en) | Semiconductor light emitting device | |

| KR101039896B1 (ko) | 발광소자 및 그 제조방법 | |

| US6593597B2 (en) | Group III-V element-based LED having ESD protection capacity | |

| JP4577497B2 (ja) | 半導体発光素子と保護素子との複合半導体装置 | |

| KR101428085B1 (ko) | 반도체 발광소자 및 그 제조방법 | |

| JP4777293B2 (ja) | 窒化物系半導体発光ダイオード | |

| CN102194847B (zh) | 发光器件、发光器件封装、发光器件的制造方法及照明系统 | |

| JP2006086300A (ja) | 保護素子を有する半導体発光装置及びその製造方法 | |

| JP2007043046A (ja) | 保護素子を備えた発光素子 | |

| JP6262856B2 (ja) | オプトエレクトロニクス半導体チップ | |

| KR100609968B1 (ko) | 정전기 보호 기능을 갖는 발광 다이오드 및 그 제조 방법 | |

| KR100649642B1 (ko) | Esd 보호 소자를 구비한 화합물 반도체 발광 소자 및 그제조 방법 | |

| JP2007324591A (ja) | 窒化物系半導体発光素子 | |

| US8963172B2 (en) | Optical semiconductor device including antiparallel semiconductor light-emitting element and Schottky diode element | |

| EP3188241B1 (en) | Light-emitting diode chip | |

| CN100403561C (zh) | 具有电路保护装置的发光元件 | |

| KR100631907B1 (ko) | Esd 보호용 p-n 다이오드를 구비한 질화갈륨계 발광소자 | |

| KR101457207B1 (ko) | 정전기 방전 보호소자가 구비된 발광 다이오드 | |

| KR20110119930A (ko) | 발광 소자, 그 제조 방법 및 발광 소자 패키지 | |

| KR101709992B1 (ko) | 발광소자 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081003 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081003 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110801 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110809 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111107 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120214 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130620 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130627 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130723 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130801 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5336030 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |