JP5295250B2 - 半導体ベースの素子、半導体ベースの素子の収容部材、ならびに、半導体ベースの素子の製造方法 - Google Patents

半導体ベースの素子、半導体ベースの素子の収容部材、ならびに、半導体ベースの素子の製造方法 Download PDFInfo

- Publication number

- JP5295250B2 JP5295250B2 JP2010526157A JP2010526157A JP5295250B2 JP 5295250 B2 JP5295250 B2 JP 5295250B2 JP 2010526157 A JP2010526157 A JP 2010526157A JP 2010526157 A JP2010526157 A JP 2010526157A JP 5295250 B2 JP5295250 B2 JP 5295250B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor

- based device

- glass substrate

- manufacturing

- deposited

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 188

- 238000000034 method Methods 0.000 title claims abstract description 30

- 238000004519 manufacturing process Methods 0.000 title claims description 33

- 239000000758 substrate Substances 0.000 claims abstract description 76

- 239000011521 glass Substances 0.000 claims abstract description 71

- 230000003287 optical effect Effects 0.000 claims description 27

- 238000006243 chemical reaction Methods 0.000 claims description 22

- 239000010409 thin film Substances 0.000 claims description 14

- 229920001296 polysiloxane Polymers 0.000 claims description 4

- 238000004544 sputter deposition Methods 0.000 claims description 4

- 230000005670 electromagnetic radiation Effects 0.000 claims description 3

- 238000007639 printing Methods 0.000 claims description 3

- 238000007650 screen-printing Methods 0.000 claims description 3

- 238000000151 deposition Methods 0.000 claims description 2

- 230000007935 neutral effect Effects 0.000 claims description 2

- 238000007747 plating Methods 0.000 claims description 2

- 230000032683 aging Effects 0.000 claims 1

- 238000005137 deposition process Methods 0.000 claims 1

- 238000000149 argon plasma sintering Methods 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 238000009434 installation Methods 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 238000005019 vapor deposition process Methods 0.000 description 3

- 238000009826 distribution Methods 0.000 description 2

- 238000000407 epitaxy Methods 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 238000005476 soldering Methods 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000005266 casting Methods 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 239000006185 dispersion Substances 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000005304 joining Methods 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 230000005693 optoelectronics Effects 0.000 description 1

- 239000011347 resin Substances 0.000 description 1

- 229920005989 resin Polymers 0.000 description 1

- 239000003566 sealing material Substances 0.000 description 1

- 229910000679 solder Inorganic materials 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 230000006641 stabilisation Effects 0.000 description 1

- 238000011105 stabilization Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/483—Containers

- H01L33/486—Containers adapted for surface mounting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/58—Optical field-shaping elements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L33/00—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L33/48—Semiconductor devices having potential barriers specially adapted for light emission; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof characterised by the semiconductor body packages

- H01L33/50—Wavelength conversion elements

- H01L33/505—Wavelength conversion elements characterised by the shape, e.g. plate or foil

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Led Device Packages (AREA)

Description

Claims (21)

- 収容部材(12)の組み込み位置への実装のために、

第1の表面(2)と該第1の表面(2)の反対側の第2の表面(3)とを有するガラス基板(1)と、

前記第1の表面(2)に収容された、発光特性を有する半導体素子(5)と、

前記ガラス基板(1)の前記第1の表面(2)上でそのコーナー領域に配置された実装用基部(10)と

を有する、

半導体ベースの素子において、

前記実装用基部(10)は、前記半導体ベースの素子の全体が該実装用基部(10)を通して前記組み込み位置に支持されるように構成されており、

前記第1の表面(2)の一部の領域のみが前記半導体素子(5)によって覆われており、前記第1の表面(2)の残りの領域は鏡(8)によって覆われている

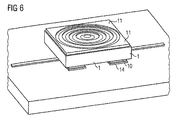

ことを特徴とする半導体ベースの素子。 - 前記第2の表面(3)に光学素子(11)が収容されている、請求項1記載の半導体ベースの素子。

- 前記第1の表面(2)と前記発光特性を有する前記半導体素子(5)とのあいだに変換層(4)が配置されている、請求項1または2記載の半導体ベースの素子。

- 前記光学素子(11)は、フレネルレンズの形態を有しているか、または、光学的ディフューザとして構成されている、請求項2記載の半導体ベースの素子。

- 前記第1の表面(2)のうち前記鏡(8)によって覆われていない中央領域は、前記鏡(8)によって覆われていない変換層(4)によってコーティングされている、請求項3記載の半導体ベースの素子。

- 前記変換層(4)は円形に成形されており、透明な前記ガラス基板(1)は正方形の基本形状を有している、請求項5記載の半導体ベースの素子。

- 前記半導体素子(5)は前記ガラス基板(1)の前記第1の表面(2)から遠いほうの面に少なくとも2つの電気コンタクト面(7)を有する、請求項1から6までのいずれか1項記載の半導体ベースの素子。

- 前記半導体素子(5)は、前記第1の表面(2)の中央に位置しており、かつ、前記実装用基部(10)に包囲されている、請求項7記載の半導体ベースの素子。

- 前記ガラス基板(1)は前記半導体ベースの素子を支持している、請求項1から8までのいずれか1項記載の半導体ベースの素子。

- 前記半導体素子(5)は、前記ガラス基板(1)を除いた厚さが20μm以下の薄膜発光ダイオードである、請求項1から9までのいずれか1項記載の半導体ベースの素子。

- 前記半導体素子(5)のうち前記ガラス基板(1)から遠いほうの主表面に、前記半導体素子(5)内で形成される電磁放射の少なくとも一部を前記ガラス基板(1)の方向へ反射させて戻す反射層が被着されているかまたは形成されている、請求項10記載の半導体ベースの素子。

- 前記光学素子(10)は、経時劣化および温度に対して安定なシリコーンから形成される層内に埋め込まれている、請求項2記載の半導体ベースの素子。

- 請求項1から12までのいずれか1項記載の半導体ベースの素子に対する収容部材(12)において、

半導体ベースの素子のコンタクト面(7)に電気的に接続されている、収容部の2つの電気コンタクト(13)と、実装用基部(10)を収容した基部収容部(14)とが設けられており、

前記基部収容部(14)は電気的に中性であり、前記2つの電気コンタクト(13)に電気的に接続されていない

ことを特徴とする半導体ベースの素子に対する収容部材。 - 請求項1から12までのいずれか1項記載の半導体ベースの素子の製造方法であって、

ガラス基板(1)を用意するステップ、および、

該ガラス基板(1)の第1の表面(2)上に半導体素子(5)を被着するステップ

を有する

ことを特徴とする半導体ベースの素子の製造方法。 - 前記第1の表面(2)上に鏡面層(8)を被着する、請求項14記載の半導体ベースの素子の製造方法。

- 前記ガラス基板(1)の第2の表面(3)に光学素子(11)を被着する、請求項14または15記載の半導体ベースの素子の製造方法。

- 前記ガラス基板の前記第1の表面(2)と前記半導体素子(5)とのあいだに変換層(4)を被着する、請求項14から16までのいずれか1項記載の半導体ベースの素子の製造方法。

- 鏡面層(8)をフォト技術によって制御されるスパッタリングプロセスまたは蒸着プロセスによって被着するか、および/または、変換層(4)をプリンティングプロセスまたはスクリーンプリンティングプロセスによって被着する、請求項14から17までのいずれか1項記載の半導体ベースの素子の製造方法。

- 前記ガラス基板(1)の前記第1の表面(2)上にめっきプロセスにより少なくとも1つの実装用基部(10)を被着する、請求項14から18までのいずれか1項記載の半導体ベースの素子の製造方法。

- 前記光学素子(11)を経時劣化および温度に対して安定な層内へ組み込む、請求項16から19までのいずれか1項記載の半導体ベースの素子の製造方法。

- 前記経時劣化および温度に対して安定な層をシリコーンから形成する、請求項20記載の半導体ベースの素子の製造方法。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102007046744.5 | 2007-09-28 | ||

| DE102007046744 | 2007-09-28 | ||

| DE102008005345.7 | 2008-01-21 | ||

| DE102008005345A DE102008005345A1 (de) | 2007-09-28 | 2008-01-21 | Halbleiterbasiertes Bauelement, Aufnahme für ein halbleiterbasiertes Bauelement und Verfahren zur Herstellung eines halbleiterbasierten Bauelements |

| PCT/DE2008/001533 WO2009039829A1 (de) | 2007-09-28 | 2008-09-12 | Strahlungsemittierendes halbleiterbauelement, aufnahme für ein strahlungsemittierendes halbleiterbauelement und verfahren zur herstellung eines strahlungsemittierenden halbleiterbauelements |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010541222A JP2010541222A (ja) | 2010-12-24 |

| JP2010541222A5 JP2010541222A5 (ja) | 2011-08-18 |

| JP5295250B2 true JP5295250B2 (ja) | 2013-09-18 |

Family

ID=40384495

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010526157A Expired - Fee Related JP5295250B2 (ja) | 2007-09-28 | 2008-09-12 | 半導体ベースの素子、半導体ベースの素子の収容部材、ならびに、半導体ベースの素子の製造方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US8878195B2 (ja) |

| EP (1) | EP2195865B1 (ja) |

| JP (1) | JP5295250B2 (ja) |

| KR (1) | KR101515252B1 (ja) |

| CN (1) | CN101809774B (ja) |

| DE (1) | DE102008005345A1 (ja) |

| TW (1) | TW200921953A (ja) |

| WO (1) | WO2009039829A1 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9270427B2 (en) | 2010-01-11 | 2016-02-23 | Futurewei Technologies, Inc. | System and method for multiplexing control and data channels in a multiple input, multiple output communications system |

| DE102011077898A1 (de) * | 2011-06-21 | 2012-12-27 | Osram Ag | LED-Leuchtvorrichtung und Verfahren zum Herstellen einer LED-Leuchtvorrichtung |

| JP6848245B2 (ja) * | 2016-07-27 | 2021-03-24 | 日亜化学工業株式会社 | 発光装置 |

Family Cites Families (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE3470441D1 (en) | 1983-12-22 | 1988-05-19 | Sumitomo Chemical Co | Film-forming composition comprising indium and tin compounds |

| US4837927A (en) * | 1985-04-22 | 1989-06-13 | Savage John Jun | Method of mounting circuit component to a circuit board |

| JPS63262259A (ja) | 1987-04-20 | 1988-10-28 | Matsushita Electric Ind Co Ltd | 光プリンタ用書き込みヘツド |

| US4942405A (en) | 1988-10-11 | 1990-07-17 | Hewlett-Packard Company | Light emitting diode print head assembly |

| JPH04159519A (ja) * | 1990-10-24 | 1992-06-02 | Stanley Electric Co Ltd | Ledバックライト付き液晶表示装置及びその製造方法 |

| JP3460330B2 (ja) | 1994-08-31 | 2003-10-27 | 京セラ株式会社 | 画像装置 |

| DE19527026C2 (de) * | 1995-07-24 | 1997-12-18 | Siemens Ag | Optoelektronischer Wandler und Herstellverfahren |

| DE19600306C1 (de) * | 1996-01-05 | 1997-04-10 | Siemens Ag | Halbleiter-Bauelement, insb. mit einer optoelektronischen Schaltung bzw. Anordnung |

| DE19746893B4 (de) * | 1997-10-23 | 2005-09-01 | Siemens Ag | Optoelektronisches Bauelement mit Wärmesenke im Sockelteil und Verfahren zur Herstellung |

| JP4109756B2 (ja) | 1998-07-07 | 2008-07-02 | スタンレー電気株式会社 | 発光ダイオード |

| JP2000135814A (ja) | 1998-10-30 | 2000-05-16 | Kyocera Corp | 光プリンタヘッド |

| EP1119058A4 (en) | 1999-07-29 | 2006-08-23 | Citizen Electronics | LIGHT-EMITTING DIODE |

| JP2001077430A (ja) * | 1999-09-02 | 2001-03-23 | Citizen Electronics Co Ltd | 発光ダイオード |

| JP3652945B2 (ja) | 1999-12-28 | 2005-05-25 | 松下電器産業株式会社 | 光情報処理装置 |

| US7064355B2 (en) * | 2000-09-12 | 2006-06-20 | Lumileds Lighting U.S., Llc | Light emitting diodes with improved light extraction efficiency |

| DE10308890A1 (de) | 2003-02-28 | 2004-09-09 | Opto Tech Corporation | Gehäusestruktur für eine Lichtemissionsdiode und Verfahren zu dessen Herstellung |

| WO2004082036A1 (ja) * | 2003-03-10 | 2004-09-23 | Toyoda Gosei Co., Ltd. | 固体素子デバイスおよびその製造方法 |

| JP4401681B2 (ja) * | 2003-05-19 | 2010-01-20 | 日東樹脂工業株式会社 | 光拡散体及びそれを用いた光学部材乃至光学デバイス |

| JP2005072129A (ja) * | 2003-08-21 | 2005-03-17 | Nec Lighting Ltd | 可視光線発光装置とその製造方法及び表示装置 |

| JP4843235B2 (ja) | 2004-03-18 | 2011-12-21 | 昭和電工株式会社 | Iii族窒化物半導体発光素子の製造方法 |

| WO2006117710A1 (en) * | 2005-04-29 | 2006-11-09 | Koninklijke Philips Electronics N.V. | Light source with glass housing |

| TWM285801U (en) | 2005-08-03 | 2006-01-11 | Lighthouse Technology Co Ltd | Light-emitting diode package structure |

| US7329907B2 (en) * | 2005-08-12 | 2008-02-12 | Avago Technologies, Ecbu Ip Pte Ltd | Phosphor-converted LED devices having improved light distribution uniformity |

| JP5219331B2 (ja) * | 2005-09-13 | 2013-06-26 | 株式会社住田光学ガラス | 固体素子デバイスの製造方法 |

| JP4759357B2 (ja) | 2005-09-28 | 2011-08-31 | 日立アプライアンス株式会社 | Led光源モジュール |

| US20070228386A1 (en) * | 2006-03-30 | 2007-10-04 | Jin-Shown Shie | Wire-bonding free packaging structure of light emitted diode |

| JP5137059B2 (ja) * | 2007-06-20 | 2013-02-06 | 新光電気工業株式会社 | 電子部品用パッケージ及びその製造方法と電子部品装置 |

-

2008

- 2008-01-21 DE DE102008005345A patent/DE102008005345A1/de not_active Withdrawn

- 2008-09-12 CN CN2008801096470A patent/CN101809774B/zh not_active Expired - Fee Related

- 2008-09-12 WO PCT/DE2008/001533 patent/WO2009039829A1/de active Application Filing

- 2008-09-12 EP EP08801325.5A patent/EP2195865B1/de not_active Not-in-force

- 2008-09-12 JP JP2010526157A patent/JP5295250B2/ja not_active Expired - Fee Related

- 2008-09-12 KR KR1020107009389A patent/KR101515252B1/ko active IP Right Grant

- 2008-09-12 US US12/680,674 patent/US8878195B2/en not_active Expired - Fee Related

- 2008-09-22 TW TW097136254A patent/TW200921953A/zh unknown

Also Published As

| Publication number | Publication date |

|---|---|

| KR20100063139A (ko) | 2010-06-10 |

| CN101809774B (zh) | 2012-08-29 |

| US8878195B2 (en) | 2014-11-04 |

| KR101515252B1 (ko) | 2015-04-24 |

| CN101809774A (zh) | 2010-08-18 |

| US20110057218A1 (en) | 2011-03-10 |

| JP2010541222A (ja) | 2010-12-24 |

| TW200921953A (en) | 2009-05-16 |

| EP2195865A1 (de) | 2010-06-16 |

| EP2195865B1 (de) | 2018-03-14 |

| WO2009039829A1 (de) | 2009-04-02 |

| DE102008005345A1 (de) | 2009-04-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI420705B (zh) | 發光裝置及發光裝置封裝件 | |

| KR100620844B1 (ko) | 발광장치 및 조명장치 | |

| KR101888604B1 (ko) | 발광 소자 및 발광 소자 패키지 | |

| KR101799451B1 (ko) | 발광 소자 | |

| CN111128987A (zh) | 发光二极管 | |

| TW202112181A (zh) | 整合式發光裝置、及發光模組 | |

| JP6781838B2 (ja) | 半導体素子パッケージ及びその製造方法 | |

| KR101830719B1 (ko) | 발광 소자 | |

| CN110676367A (zh) | 发光二极管 | |

| KR101799450B1 (ko) | 발광 소자 및 발광 소자 패키지 | |

| US20140209965A1 (en) | Light emitting device, light emitting device package, and lighting system | |

| KR20130022052A (ko) | 발광소자 패키지 및 조명 장치 | |

| KR101694175B1 (ko) | 발광소자, 발광소자 패키지 및 조명시스템 | |

| JP5295250B2 (ja) | 半導体ベースの素子、半導体ベースの素子の収容部材、ならびに、半導体ベースの素子の製造方法 | |

| KR101055003B1 (ko) | 발광 소자, 발광 소자 패키지, 조명 시스템, 및 발광 소자 제조방법 | |

| KR101843420B1 (ko) | 발광소자, 발광 소자 제조방법 및 발광 소자 패키지 | |

| KR101946832B1 (ko) | 백라이트 유닛 및 이를 포함하는 표시 장치 | |

| KR20190019594A (ko) | 반도체 소자 패키지 | |

| KR20130057903A (ko) | 발광소자 패키지 | |

| KR101906851B1 (ko) | 발광 소자 및 이를 구비한 발광 모듈 | |

| KR101946831B1 (ko) | 발광 소자 패키지 | |

| KR102170213B1 (ko) | 발광 소자 | |

| KR20120088985A (ko) | 발광소자 | |

| KR20160132658A (ko) | 발광 소자 및 발광 소자 패키지 | |

| KR101873587B1 (ko) | 발광소자 패키지 및 조명 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20101228 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110630 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110630 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121219 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121221 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130318 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130326 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130417 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130513 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130611 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5295250 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |