JP5240749B2 - 薄膜トランジスター基板、その製造方法及びこれを備える液晶表示装置 - Google Patents

薄膜トランジスター基板、その製造方法及びこれを備える液晶表示装置 Download PDFInfo

- Publication number

- JP5240749B2 JP5240749B2 JP2007103001A JP2007103001A JP5240749B2 JP 5240749 B2 JP5240749 B2 JP 5240749B2 JP 2007103001 A JP2007103001 A JP 2007103001A JP 2007103001 A JP2007103001 A JP 2007103001A JP 5240749 B2 JP5240749 B2 JP 5240749B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- pixel

- substrate

- electrode

- reflective

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000000758 substrate Substances 0.000 title claims description 87

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 51

- 239000010409 thin film Substances 0.000 title claims description 48

- 238000000034 method Methods 0.000 title description 34

- 238000004519 manufacturing process Methods 0.000 title description 17

- 239000010410 layer Substances 0.000 claims description 75

- 230000005540 biological transmission Effects 0.000 claims description 13

- 239000011159 matrix material Substances 0.000 claims description 12

- 239000003990 capacitor Substances 0.000 claims description 10

- 238000003860 storage Methods 0.000 claims description 10

- 239000010408 film Substances 0.000 description 76

- 230000001681 protective effect Effects 0.000 description 26

- 239000004065 semiconductor Substances 0.000 description 10

- 238000000059 patterning Methods 0.000 description 9

- 238000005530 etching Methods 0.000 description 7

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 7

- 229920005591 polysilicon Polymers 0.000 description 7

- 239000012535 impurity Substances 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 229910052581 Si3N4 Inorganic materials 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 5

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- 239000011651 chromium Substances 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- 239000010936 titanium Substances 0.000 description 4

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical group [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- 150000002500 ions Chemical class 0.000 description 3

- 229910052709 silver Inorganic materials 0.000 description 3

- 239000004332 silver Substances 0.000 description 3

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 238000002425 crystallisation Methods 0.000 description 2

- 230000008025 crystallization Effects 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 239000012528 membrane Substances 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 239000011733 molybdenum Substances 0.000 description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- 239000004593 Epoxy Substances 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 238000005452 bending Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 238000007715 excimer laser crystallization Methods 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 238000005499 laser crystallization Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 238000001579 optical reflectometry Methods 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000007790 solid phase Substances 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1335—Structural association of cells with optical devices, e.g. polarisers or reflectors

- G02F1/133553—Reflecting elements

- G02F1/133555—Transflectors

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1343—Electrodes

- G02F1/134309—Electrodes characterised by their geometrical arrangement

- G02F1/134345—Subdivided pixels, e.g. for grey scale or redundancy

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136213—Storage capacitors associated with the pixel electrode

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/137—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells characterised by the electro-optical or magneto-optical effect, e.g. field-induced phase transition, orientation effect, guest-host interaction or dynamic scattering

- G02F1/139—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells characterised by the electro-optical or magneto-optical effect, e.g. field-induced phase transition, orientation effect, guest-host interaction or dynamic scattering based on orientation effects in which the liquid crystal remains transparent

- G02F1/1393—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells characterised by the electro-optical or magneto-optical effect, e.g. field-induced phase transition, orientation effect, guest-host interaction or dynamic scattering based on orientation effects in which the liquid crystal remains transparent the birefringence of the liquid crystal being electrically controlled, e.g. ECB-, DAP-, HAN-, PI-LC cells

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

Description

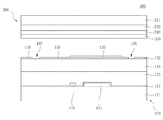

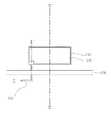

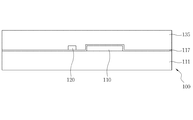

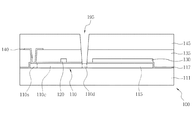

B 反射領域、

C1、C2 透過領域、

100 薄膜トランジスター基板、

110 活性層、

110s ソース領域、

110c チャンネル、

110d ドレイン領域、

115 第1の電極パターン、

117 ゲート絶縁膜、

120 ゲート線、

130 第2の電極パターン、

135 第1の保護膜、

140 データ線、

145 第2の保護膜、

150 画素電極、

160 接続部、

170 反射膜、

180 切欠部、

200 カラーフィルター基板、

211 第2の絶縁基板、

220 ブラックマトリックス、

230 カラーフィルター、

240 オーバーコート膜、

250 共通電極、

300 液晶表示パネル。

Claims (4)

- 基板上を一方向に伸びて形成された複数のゲート線と、

前記ゲート線と交差して形成された複数のデータ線と、

前記データ線の間に位置する画素領域に形成された複数の画素電極と、を備え、

各画素領域は、

前記ゲート線を含む領域に形成された反射領域と、

前記反射領域を挟んで両側に形成された透過領域と、

前記基板上の任意の領域に形成された第1の電極パターンと、

前記第1の電極パターンと同一層で形成されて連なることで接続され、前記ゲート線の下を通って前記データ線に接続された活性層と、を備え、

前記活性層は、

前記データ線に接続されたソース領域と、

前記画素電極に接続されたドレイン領域と、

前記ソース領域及びドレイン領域の間であって、上部に前記ゲート線を有するチャンネル領域と、

前記ゲート線と所定の間隔を隔てて形成された前記ストレジキャパシタの上部電極をなす第2の電極パターンと、を備え、

前記第2の電極パターンは、前記活性層と接続される部分を除き、前記第1の電極パターンと重なり合うように形成され、

前記画素電極は、それぞれ角部が丸く面取りされた矩形形状を有し、前記反射領域および前記透過領域にそれぞれ形成されるとともに、接合部により電気的に接続され、

前記ゲート線は前記反射領域と前記透過領域との境界のいずれか一方に沿って伸び、前記反射領域と重畳するように設けられていることを特徴とする薄膜トランジスター基板。 - 前記透過領域の前記画素電極には切欠部をさらに備えることを特徴とする請求項1に記載の薄膜トランジスター基板。

- 前記反射領域の前記画素電極の上部または下部に反射膜が形成されていることを特徴とする請求項1または2に記載の薄膜トランジスター基板。

- 基板上を一方向に伸びて形成された複数のゲート線と、

前記ゲート線と交差して形成された複数のデータ線と、

前記データ線の間に位置する画素領域に形成された複数の画素電極と、を備え、

各画素領域は、

前記ゲート線を含む領域に形成された反射領域と、

前記反射領域を挟んで両側に形成された透過領域と、

前記基板上の任意の領域に形成された第1の電極パターンと、

前記第1の電極パターンと同一層で形成されて連なることで接続され、前記ゲート線の下を通って前記データ線に接続された活性層と、を備え、

前記活性層は、

前記データ線に接続されたソース領域と、

前記画素電極に接続されたドレイン領域と、

前記ソース領域及びドレイン領域の間であって、上部に前記ゲート線を有するチャンネル領域と、

前記ゲート線と所定の間隔を隔てて形成された前記ストレジキャパシタの上部電極をなす第2の電極パターンと、を備え、

前記第2の電極パターンは、前記活性層と接続される部分を除き、前記第1の電極パターンと重なり合うように形成され、

前記画素電極は、それぞれ角部が丸く面取りされた矩形形状を有し、前記反射領域および前記透過領域にそれぞれ形成されるとともに、接合部により電気的に接続され、

前記ゲート線は前記反射領域と前記透過領域との境界のいずれか一方に沿って伸び、前記反射領域と重畳するように設けられている薄膜トランジスター基板と、

前記画素領域以外の領域に対応する第2の基板上の領域に形成されたブラックマトリックスと、前記画素領域に対応する前記第2の基板上の領域に形成されたカラーフィルターと、前記第2の基板上に形成された共通電極と、を備えるカラーフィルター基板と、

前記薄膜トランジスター基板と前記カラーフィルター基板との間に形成された液晶層と、

を備えることを特徴とする液晶表示装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR10-2006-0112859 | 2006-11-15 | ||

| KR1020060112859A KR20080044050A (ko) | 2006-11-15 | 2006-11-15 | 박막 트랜지스터 기판, 그 제조 방법 및 이를 구비하는액정 표시 장치 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008122904A JP2008122904A (ja) | 2008-05-29 |

| JP2008122904A5 JP2008122904A5 (ja) | 2010-05-27 |

| JP5240749B2 true JP5240749B2 (ja) | 2013-07-17 |

Family

ID=39368864

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007103001A Active JP5240749B2 (ja) | 2006-11-15 | 2007-04-10 | 薄膜トランジスター基板、その製造方法及びこれを備える液晶表示装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7995171B2 (ja) |

| JP (1) | JP5240749B2 (ja) |

| KR (1) | KR20080044050A (ja) |

| CN (1) | CN101226944B (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5623107B2 (ja) | 2009-04-22 | 2014-11-12 | キヤノン株式会社 | 半導体装置 |

| KR101822563B1 (ko) | 2010-12-08 | 2018-03-09 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| CN102981324B (zh) | 2012-12-10 | 2017-07-14 | 京东方科技集团股份有限公司 | 一种半透半反蓝相液晶显示面板及液晶显示装置 |

| CN103107095A (zh) * | 2013-01-25 | 2013-05-15 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制作方法、阵列基板、显示装置 |

| CN104269410A (zh) * | 2014-09-03 | 2015-01-07 | 合肥京东方光电科技有限公司 | 一种阵列基板及显示装置 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6195140B1 (en) * | 1997-07-28 | 2001-02-27 | Sharp Kabushiki Kaisha | Liquid crystal display in which at least one pixel includes both a transmissive region and a reflective region |

| JP4196505B2 (ja) * | 1999-12-13 | 2008-12-17 | ソニー株式会社 | 表示装置及びその製造方法とカラーフィルタ |

| JP3892715B2 (ja) * | 2000-12-26 | 2007-03-14 | 株式会社東芝 | 液晶表示装置 |

| JP4603190B2 (ja) | 2001-04-16 | 2010-12-22 | 株式会社日立製作所 | 液晶表示装置 |

| JP4050119B2 (ja) * | 2001-10-02 | 2008-02-20 | シャープ株式会社 | 液晶表示装置 |

| KR20030058012A (ko) | 2001-12-29 | 2003-07-07 | 엘지.필립스 엘시디 주식회사 | 반투과형 액정 표시 장치 |

| KR100752214B1 (ko) * | 2003-10-16 | 2007-08-28 | 엘지.필립스 엘시디 주식회사 | 반투과형 액정표시소자의 제조방법 |

| KR100617031B1 (ko) * | 2003-12-30 | 2006-08-30 | 엘지.필립스 엘시디 주식회사 | 반사투과형 액정표시장치 및 그 제조방법 |

| JP4390595B2 (ja) * | 2004-03-09 | 2009-12-24 | シャープ株式会社 | 液晶表示装置 |

| KR100715756B1 (ko) * | 2004-03-09 | 2007-05-08 | 샤프 가부시키가이샤 | 액정 표시 장치 |

| JP3915792B2 (ja) | 2004-03-12 | 2007-05-16 | セイコーエプソン株式会社 | 液晶表示装置および電子機器 |

| JP4738055B2 (ja) * | 2004-05-21 | 2011-08-03 | 三洋電機株式会社 | 液晶表示装置 |

| JP4873882B2 (ja) | 2004-05-21 | 2012-02-08 | 三洋電機株式会社 | 液晶表示装置 |

| JP3953059B2 (ja) * | 2004-09-01 | 2007-08-01 | セイコーエプソン株式会社 | 液晶表示装置および電子機器 |

| JP4016977B2 (ja) * | 2004-09-03 | 2007-12-05 | セイコーエプソン株式会社 | 液晶表示装置、電子機器 |

| KR20060034802A (ko) | 2004-10-19 | 2006-04-26 | 삼성전자주식회사 | 반투과형 액정 표시 장치 |

| JP4427436B2 (ja) | 2004-11-25 | 2010-03-10 | シャープ株式会社 | 液晶表示装置 |

| JP4578958B2 (ja) | 2004-12-16 | 2010-11-10 | シャープ株式会社 | 液晶表示装置 |

| KR101151799B1 (ko) * | 2005-11-09 | 2012-06-01 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이기판과 그 제조방법 |

| JP2007133293A (ja) * | 2005-11-14 | 2007-05-31 | Epson Imaging Devices Corp | 液晶装置及び電子機器 |

| JP4341617B2 (ja) | 2005-12-02 | 2009-10-07 | セイコーエプソン株式会社 | 液晶表示装置、及び電子機器 |

-

2006

- 2006-11-15 KR KR1020060112859A patent/KR20080044050A/ko not_active Application Discontinuation

-

2007

- 2007-04-10 JP JP2007103001A patent/JP5240749B2/ja active Active

- 2007-11-14 US US11/940,067 patent/US7995171B2/en active Active

- 2007-11-15 CN CN2007103007676A patent/CN101226944B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN101226944B (zh) | 2013-07-03 |

| KR20080044050A (ko) | 2008-05-20 |

| US7995171B2 (en) | 2011-08-09 |

| JP2008122904A (ja) | 2008-05-29 |

| CN101226944A (zh) | 2008-07-23 |

| US20080111956A1 (en) | 2008-05-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5307319B2 (ja) | 薄膜トランジスタ表示板及びその製造方法 | |

| JP5351388B2 (ja) | 表示装置 | |

| KR101413275B1 (ko) | 액정 표시 패널 및 이의 제조 방법 | |

| US7688417B2 (en) | Thin film transistor array panel and method for manufacturing the same | |

| JP5132894B2 (ja) | 表示板及びそれを含む液晶表示装置 | |

| TWI383234B (zh) | 薄膜電晶體陣列面板及該薄膜電晶體陣列面板之製造方法 | |

| JP2006133783A (ja) | 多重ドメイン薄膜トランジスタ表示板 | |

| US8300166B2 (en) | Display panel and method of manufacturing the same | |

| JP2006201775A (ja) | 薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法 | |

| JP5652841B2 (ja) | 薄膜トランジスタ表示板 | |

| JP4813050B2 (ja) | 表示板及びこれを含む液晶表示装置 | |

| JP5295483B2 (ja) | 薄膜トランジスタ表示板 | |

| JP2006023744A5 (ja) | ||

| JP5240749B2 (ja) | 薄膜トランジスター基板、その製造方法及びこれを備える液晶表示装置 | |

| US20070188682A1 (en) | Method for manufacturing a display device | |

| JP2006178445A (ja) | 薄膜トランジスタ表示板及びその製造方法 | |

| JP2005018069A (ja) | 液晶表示装置 | |

| KR20080073573A (ko) | 액정패널과 이의 제조방법 | |

| KR20020011574A (ko) | 액정 표시 장치용 어레이 기판 및 그 제조 방법 | |

| JP2007017756A (ja) | 液晶表示装置 | |

| JP2007011372A (ja) | 液晶表示装置 | |

| US8841677B2 (en) | Thin film transistor array panel and manufacturing method thereof | |

| KR20070031580A (ko) | 액정 표시 장치 | |

| KR20080034634A (ko) | 박막 트랜지스터 기판, 그 제조 방법 및 이를 구비하는액정 표시 장치 | |

| KR20090005258A (ko) | 액정 표시 패널의 제조 방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100409 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100409 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120207 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120507 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120510 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120607 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20121213 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130319 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130327 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160412 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5240749 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |