JP5215415B2 - レベルシフティング回路および方法 - Google Patents

レベルシフティング回路および方法 Download PDFInfo

- Publication number

- JP5215415B2 JP5215415B2 JP2010545100A JP2010545100A JP5215415B2 JP 5215415 B2 JP5215415 B2 JP 5215415B2 JP 2010545100 A JP2010545100 A JP 2010545100A JP 2010545100 A JP2010545100 A JP 2010545100A JP 5215415 B2 JP5215415 B2 JP 5215415B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- input

- path

- coupled

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 24

- 230000007704 transition Effects 0.000 claims description 44

- 230000004044 response Effects 0.000 claims description 21

- 230000004913 activation Effects 0.000 claims description 10

- 230000014759 maintenance of location Effects 0.000 claims description 6

- 230000003213 activating effect Effects 0.000 claims description 5

- 230000005669 field effect Effects 0.000 claims 8

- 230000000295 complement effect Effects 0.000 claims 4

- 230000001276 controlling effect Effects 0.000 claims 4

- 239000004615 ingredient Substances 0.000 claims 1

- 230000001105 regulatory effect Effects 0.000 claims 1

- 238000010586 diagram Methods 0.000 description 8

- 241000287463 Phalacrocorax Species 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- 230000008859 change Effects 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000010295 mobile communication Methods 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 241000287462 Phalacrocorax carbo Species 0.000 description 1

- 230000001413 cellular effect Effects 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000009849 deactivation Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000035945 sensitivity Effects 0.000 description 1

- 230000001052 transient effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0175—Coupling arrangements; Interface arrangements

- H03K19/0185—Coupling arrangements; Interface arrangements using field effect transistors only

- H03K19/018507—Interface arrangements

- H03K19/018521—Interface arrangements of complementary type, e.g. CMOS

- H03K19/018528—Interface arrangements of complementary type, e.g. CMOS with at least one differential stage

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/01—Modifications for accelerating switching

- H03K19/017—Modifications for accelerating switching in field-effect transistor circuits

- H03K19/01707—Modifications for accelerating switching in field-effect transistor circuits in asynchronous circuits

- H03K19/01721—Modifications for accelerating switching in field-effect transistor circuits in asynchronous circuits by means of a pull-up or down element

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/02—Generators characterised by the type of circuit or by the means used for producing pulses

- H03K3/353—Generators characterised by the type of circuit or by the means used for producing pulses by the use, as active elements, of field-effect transistors with internal or external positive feedback

- H03K3/356—Bistable circuits

- H03K3/356104—Bistable circuits using complementary field-effect transistors

- H03K3/356113—Bistable circuits using complementary field-effect transistors using additional transistors in the input circuit

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Logic Circuits (AREA)

Description

以下に、本願出願の当初の(誤訳訂正後の)特許請求の範囲に記載された発明を付記する。

[C1]

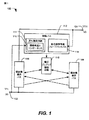

入力電圧信号を受け取るための入力と、

レベルシフトされた電圧信号を提供するための出力と、

前記入力に連結された第1の弱状態保持パスと、

前記出力に連結された第2の弱状態保持パスと、

前記第1の弱状態保持パスおよび前記第2の弱状態保持パスに連結された電圧プルアップ論理回路と、

前記電圧プルアップ論理回路のアクティブ化を選択的に制御するために前記電圧プルアップ論理回路に連結された制御パスと

を具備する回路装置。

[C2]

前記制御パスは、前記出力から前記電圧プルアップ論理回路までの自己調時式フィードバックパスをさらに具備するC1の回路装置。

[C3]

前記制御パスは、前記電圧プルアップ論理回路に前記入力を連結するC1の回路装置。

[C4]

前記制御パスは、タイミング遅れを提供するための遅れ論理回路を具備するC3の回路装置。

[C5]

前記遅れ論理回路は、調整可能遅れコンポーネントを具備するC4の回路装置。

[C6]

前記第1の弱状態保持パスは、

電源電圧に連結された第1の端子、前記第2の弱状態保持パスに連結された制御端子、および第3の端子を具備する第1の弱pチャネルトランジスタと、

前記第3の端子に連結された第4の端子、前記入力に連結された第2の制御端子、および前記電圧プルアップ論理回路に連結されたノードに連結された第5の端子を含む第2の弱pチャネルトランジスタと、

前記ノードに連結された第6の端子、前記入力に連結された第3の制御端子、および第2の電源電圧に連結された第7の端子を含む強nチャネルトランジスタと

をさらに具備するC1の回路装置。

[C7]

前記第2の弱状態保持パスは、直列配列された強nチャネルトランジスタ、および多数の弱pチャネルトランジスタを具備するC1の回路装置。

[C8]

前記電圧プルアップ論理回路は、

少なくとも1つの第1のトランジスタを含む第1の強プルアップパス、および、少なくとも1つの第2のトランジスタを含む第2の強プルアップパスを具備し、前記少なくとも1つの第2のトランジスタは、前記少なくとも1つの第1のトランジスタに連結されるC1の回路装置。

[C9]

前記第1の強プルアップパスおよび前記第2の強プルアップパスはインバータによって連結されるC8の回路装置。

[C10]

前記第1の弱状態保持パスおよび前記第2の弱状態保持パスはインバータによって連結されるC1の回路装置。

[C11]

前記第1の弱状態保持パスは第2の強プルアップパスに連結され、また、前記第2の弱状態保持パスは前記第1の強プルアップパスに連結されるC10の回路装置。

[C12]

前記制御パスは、前記第2の弱状態保持パスのエレメントに連結されるインバータの出力に連結されるC1の回路装置。

[C13]

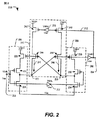

メモリアレイと、

第1のレベルシフティング回路によって前記メモリアレイに連結された第1の入力と、

第2のレベルシフティング回路によって前記メモリアレイに連結された第2の入力とを具備し、

前記第1のレベルシフティング回路は、

前記第1の入力を受け取るための入力と、

前記メモリアレイへ第1のレベルシフトされた電圧信号を供給するための出力と、

前記入力と前記出力に連結された第1の弱状態保持パスと、

前記第1の弱状態保持パスに連結された相互連結回路と、

前記第1の弱状態保持パスに連結された電圧プルアップ論理回路と、

前記電圧プルアップ論理回路のアクティブ化を選択的に制御するために前記電圧プルアップ論理回路に連結された制御パスと

を具備するシステム。

[C14]

前記相互連結回路は第2の弱状態保持パスを含むC13のシステム。

[C15]

前記メモリアレイは、第2の電圧レベルで電源によって電力供給され、また、前記第1の入力および前記第2の入力の少なくとも1つは第1の電圧レベルにあるC13のシステム。

[C16]

前記第1の電圧レベルは前記第2の電圧レベル未満であるC15のシステム。

[C17]

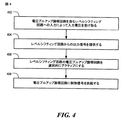

電圧プルアップ論理を含むレベルシフティング回路への入力で入力電圧を受け取ることと、

前記レベルシフティング回路からの出力信号を提供することと、

前記レベルシフティング回路の前記電圧プルアップ論理回路を選択的にアクティブにすることとを具備する方法。

[C18]

前記電圧プルアップ論理回路に制御信号を供給することをさらに具備するC17の方法。

[C19]

前記制御信号は前記出力信号に応答するフィードバック信号であるC18の方法。

[C20]

前記入力信号は第1の電圧を有し、前記出力信号は第2の電圧を有するC17の方法。

[C21]

前記入力信号は第1の弱状態保持パスに適用されるC17の方法。

[C22]

前記第1の弱状態保持パスは、直列配列された強nチャネルトランジスタ、および多数の弱pチャネルトランジスタを具備するC21の方法。

[C23]

電圧プルアップ論理を含むレベルシフティング回路への入力で入力電圧を受け取るための手段と、

前記レベルシフティング回路からの出力信号を提供するための手段と、

前記レベルシフティング回路の前記電圧プルアップ論理回路を選択的にアクティブにするための手段と

を具備する装置。

[C24]

前記電圧プルアップ論理回路に制御信号を供給するための手段をさらに具備するC23の装置。

[C25]

前記制御信号は前記出力信号に応答するフィードバック信号であるC24のデバイス。

Claims (23)

- 入力電圧信号を受け取るための単一入力と、前記入力電圧信号に対して反転されるレベルシフトされた電圧信号を提供するための反転出力と、を含む電圧レベルシフタを具備し、

前記電圧レベルシフタは、

前記単一入力に連結された第1の弱状態保持パス、ここにおいて、前記第1の弱状態保持パスは、第1のpチャネル電界効果トランジスタ(PFET)に直列に連結された第1のnチャネル電界効果トランジスタ(NFET)を含む、と、

前記反転出力に連結された第2の弱状態保持パス、ここにおいて、前記第2の弱状態保持パスは、第2のPFETに直列に連結された第2のNFETを含む、と、

前記入力電圧信号に応答する第1のインバータ、ここにおいて、前記第2のNFETおよび前記第2のPFETは、前記第1のインバータの出力に応答し、また、前記第1のインバータが、前記入力電圧信号の補数に応答するために前記第2のNFETおよび前記第2のPFETを制御する一方で、前記第1のNFETおよび前記第1のPFETは、前記入力電圧信号に応答する、と、

前記第1の弱状態保持パスおよび前記第2の弱状態保持パスに連結された電圧プルアップ論理回路と、

バッファのバッファ出力の遷移に応答して、前記電圧プルアップ論理回路のアクティブ化を選択的に制御するために前記電圧プルアップ論理回路に連結された制御パス、ここにおいて、前記バッファは、前記反転出力に連結された入力を有する、と、を備え、

前記バッファは、前記バッファ出力に適用される負荷に応答するために前記電圧プルアップ論理回路の制御を可能にする一方で、前記第2の弱状態保持パスの前記入力電圧信号の遷移への切り替え応答は、前記負荷により実質的に影響されず、

前記制御パスは、前記バッファ出力から前記電圧プルアップ論理回路までの自己調次式フィードバックパスをさらに含む回路装置。 - 前記制御パスは、前記電圧プルアップ論理回路に前記単一入力を連結する請求項1の回路装置。

- 前記制御パスは、タイミング遅れを提供するための遅れ論理回路を具備する請求項2の回路装置。

- 前記遅れ論理回路は、調整可能遅れコンポーネントを具備する請求項3の回路装置。

- 前記第1の弱状態保持パスは、

電源電圧に連結された第1の端子、前記第2の弱状態保持パスに連結された制御端子、および第3の端子を具備する第1の弱PFETと、

前記第3の端子に連結された第4の端子、前記単一入力に連結された第2の制御端子、および前記電圧プルアップ論理回路に連結されたノードに連結された第5の端子を含む前記第1のPFETと、

前記ノードに連結された第6の端子、前記単一入力に連結された第3の制御端子、および第2の電源電圧に連結された第7の端子を含む前記第1のNFETと

を具備する請求項1の回路装置。 - 第1の強プルアップパスおよび第2の強プルアップパスは、第3のインバータによって連結される請求項1の回路装置。

- 前記第1の強プルアップパスおよび前記第2の強プルアップパスは前記第1のインバータによって連結される請求項1の回路装置。

- 前記第1の弱状態保持パスは第2の強プルアップパスに連結され、また、前記第2の弱状態保持パスは前記第1の強プルアップパスに連結される請求項7の回路装置。

- 前記制御パスは、前記第2の弱状態保持パスのエレメントに連結される第2のインバータの出力に連結される請求項1の回路装置。

- 前記第2のインバータは、インバータ入力とインバータ出力とを含み、前記インバータ入力は前記第2の弱状態保持パスに連結され、また、前記インバータ出力は前記制御パスに連結される請求項9の回路装置。

- メモリアレイと、

第1のレベルシフティング回路によって前記メモリアレイに連結された第1の入力と、

第2のレベルシフティング回路によって前記メモリアレイに連結された第2の入力とを具備し、

前記第1のレベルシフティング回路は、

前記第1の入力を受け取るための単一入力と、バッファのバッファされた出力への前記入力電圧信号に対して反転される第1のレベルシフトされた電圧信号を供給するための反転出力と、を含む電圧レベルシフタを備え、ここにおいて、前記バッファされた出力は、前記メモリアレイに連結され、

前記電圧レベルシフタは、

前記単一入力と前記バッファされた出力に連結された第1の弱状態保持パス、ここにおいて、前記第1の弱状態保持パスは、第1のpチャネル電界効果トランジスタ(PFET)に直列に連結された第1のnチャネル電界効果トランジスタ(NFET)を含む、と、

前記反転出力に連結された第2の弱状態保持パス、ここにおいて、前記第2の弱状態保持パスは、第2のPFETに直列に連結された第2のNFETを含む、と、

前記第1の入力に応答するインバータ、ここにおいて、前記第2のNFETおよび前記第2のPFETは、前記インバータの出力に応答し、また、前記インバータが前記第1の入力の補数に応答するために前記第2のNFETおよび前記第2のPFETを制御する一方で、前記第1のNFETおよび前記第1のPFETは前記第1の入力に応答する、と、

前記第1の弱状態保持パスおよび前記第2の弱状態保持パスに連結された電圧プルアップ論理回路と、

前記電圧プルアップ論理回路のアクティブ化を選択的に制御するために前記バッファのバッファされた出力に応答する、また、前記電圧プルアップ論理回路に連結された制御パスとをさらに備え、

ここにおいて、前記バッファは、前記反転出力に連結された入力を有し、また、前記バッファは、前記バッファ出力に適用される負荷に応答するために前記電圧プルアップ論理回路の制御を可能にする一方で、前記第2の弱状態保持パスの前記入力電圧信号の遷移への切り替え応答は、前記負荷により実質的に影響されず、

前記制御パスは、前記バッファのバッファされた出力から前記電圧プルアップ論理回路までの自己調次式フィードバックパスをさらに含むシステム。 - 前記メモリアレイは、第2の電圧レベルで電源によって電力供給され、また、前記第1の入力および前記第2の入力の少なくとも1つは第1の電圧レベルにある請求項11のシステム。

- 前記第1の電圧レベルは前記第2の電圧レベル未満である請求項12のシステム。

- 前記バッファは、インバータ入力とインバータ出力とを有している第2のインバータを備え、ここにおいて、前記インバータ入力は前記第2の弱状態保持パスに連結され、また、前記インバータ出力は前記制御パスに連結される請求項11のシステム。

- 回路装置の電圧レベルシフタであって、前記電圧レベルシフタは、単一入力および反転出力を備え、

前記電圧レベルシフタへの単一入力で入力電圧信号を受け取ること、前記電圧レベルシフタは電圧プルアップ論理回路を更に含み、と、

前記電圧プルアップ論理回路へのバッファされたレベルシフトされる出力を生成するために連結されるバッファに前記電圧レベルシフタの前記反転出力から前記入力電圧信号に対して反転されるレベルシフトされた出力信号を提供すること、ここにおいて、前記バッファは前記反転に連結される入力を有する、と、

前記レベルシフティング回路の前記電圧プルアップ論理回路を選択的にアクティブにすることとを具備する方法であって、

前記電圧レベルシフタは、

前記単一入力に連結される第1の弱状態保持パス、ここにおいて、前記第1の弱状態保持パスは、第1のpチャネル電界効果トランジスタ(PFET)に直列に連結される第1のnチャネル電界効果トランジスタ(NFET)を含む、と、

前記反転出力に連結される第2の弱状態保持パス、ここにおいて、前記第2の弱状態保持パスは、第2のPFETに直列に連結される第2のNFETを含む、と、

前記入力電圧信号に応答するインバータ、ここにおいて、前記第2のNFETおよび前記第2のPFETは、前記インバータの出力に応答し、また、前記インバータが前記入力電圧信号の補数に応答するために前記第2のNFETおよび前記第2のPFETを制御する一方で、前記第1のNFETおよび前記第1のPFETは、前記入力電圧信号に応答する、とを含み、

ここにおいて、前記バッファは、前記バッファ出力に適用される負荷に応答するために前記電圧プルアップ論理回路の制御を可能にする一方で、前記第2の弱状態保持パスの前記入力電圧信号の遷移への切り替え応答は、前記負荷により実質的に影響されず、

前記制御パスは、前記バッファのバッファされた出力から前記電圧プルアップ論理回路までの自己調次式フィードバックパスをさらに含む方法。 - 前記電圧プルアップ論理回路に制御信号を供給することをさらに具備する請求項15の方法。

- 前記制御信号は前記出力信号に応答するフィードバック信号である請求項16の方法。

- 前記入力信号は第1の電圧を有し、前記出力信号は第2の電圧を有する請求項15の方法。

- 前記第1の弱状態保持パスは、直列配列された強NFET、および多数の弱PFETを具備する請求項15の方法。

- 単一入力および反転入力を有する電圧レベルシフタを備えるデバイスであって、

前記電圧レベルシフタは、

前記電圧レベルシフタへの前記単一入力で入力電圧信号を受け取るための手段、前記電圧レベルシフタは電圧プルアップ論理をさらに含む、と、

前記電圧レベルシフタの前記反転出力からの前記電圧プルアップ論理へ前記入力電圧信号に対して反転されるレベルシフトされたバッファされる出力信号を提供するための手段、ここにおいて、前記バッファされた出力信号は、前記電圧レベルシフタのバッファから提供され、また、前記バッファは、前記反転出力に連結される入力を有する、と、

前記レベルシフトされたバッファされる出力信号に応答して、前記電圧レベルシフタの前記電圧プルアップ論理回路を選択的にアクティブにするための手段とを具備し、

前記電圧レベルシフタは、

前記単一入力に連結される第1の弱状態保持パス、ここにおいて、前記第1の弱状態保持パスは、第1のpチャネル電界効果トランジスタ(PFET)に直列に連結される第1のnチャネル電界効果トランジスタ(NFET)を含む、と、

前記反転出力に連結される第2の弱状態保持パス、ここにおいて、前記第2の弱状態保持パスは、第2のPFETに直列に連結される第2のNFETを含む、と、

前記入力電圧信号に応答するインバータ、ここにおいて、前記第2のNFETおよび前記第2のPFETは、前記インバータの出力に応答し、また、前記インバータが前記入力電圧信号の補数に応答するために前記第2のNFETおよび前記第2のPFETを制御する一方で、前記第1のNFETおよび前記第1のPFETは、前記入力電圧信号に応答する、とを含み、

ここにおいて、前記バッファは、前記バッファ出力に適用される負荷に応答するために前記電圧プルアップ論理回路の制御を可能にする一方で、前記第2の弱状態保持パスの前記入力電圧信号の遷移への切り替え応答は、前記負荷により実質的に影響されず、

前記制御パスは、前記バッファのバッファされた出力から前記電圧プルアップ論理回路までの自己調次式フィードバックパスをさらに含むデバイス。 - 前記電圧プルアップ論理回路に制御信号を供給するための手段をさらに具備する請求項20の装置。

- 前記制御信号は前記出力信号に応答するフィードバック信号である請求項21のデバイス。

- 前記バッファは、第2のインバータを具備する請求項20のデバイス。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/023,276 | 2008-01-31 | ||

| US12/023,276 US7884645B2 (en) | 2008-01-31 | 2008-01-31 | Voltage level shifting circuit and method |

| PCT/US2009/032203 WO2009097315A1 (en) | 2008-01-31 | 2009-01-28 | Level shifting circuit and method |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011511567A JP2011511567A (ja) | 2011-04-07 |

| JP2011511567A5 JP2011511567A5 (ja) | 2012-05-31 |

| JP5215415B2 true JP5215415B2 (ja) | 2013-06-19 |

Family

ID=40451170

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010545100A Expired - Fee Related JP5215415B2 (ja) | 2008-01-31 | 2009-01-28 | レベルシフティング回路および方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7884645B2 (ja) |

| EP (1) | EP2248260A1 (ja) |

| JP (1) | JP5215415B2 (ja) |

| KR (1) | KR101197836B1 (ja) |

| CN (1) | CN101965684A (ja) |

| WO (1) | WO2009097315A1 (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8896360B2 (en) | 2011-02-15 | 2014-11-25 | Cavium, Inc. | Level-up shifter circuit for high speed and low power applications |

| US8525572B2 (en) * | 2011-02-15 | 2013-09-03 | Cavium, Inc. | Level-up shifter circuit |

| US9461624B2 (en) * | 2014-11-17 | 2016-10-04 | Infineon Technologies Ag | Output driver slew control |

| US11223359B2 (en) | 2016-03-31 | 2022-01-11 | Qualcomm Incorporated | Power efficient voltage level translator circuit |

| US10050624B2 (en) | 2016-05-18 | 2018-08-14 | Cavium, Inc. | Process-compensated level-up shifter circuit |

| KR102534821B1 (ko) * | 2016-10-31 | 2023-05-22 | 에스케이하이닉스 주식회사 | 전원 제어장치 및 이를 포함하는 반도체 메모리 장치 |

| US9997208B1 (en) * | 2017-03-29 | 2018-06-12 | Qualcomm Incorporated | High-speed level shifter |

| US9762238B1 (en) * | 2017-04-03 | 2017-09-12 | Nxp Usa, Inc. | Systems and methods for supplying reference voltage to multiple die of different technologies in a package |

| US11152937B2 (en) * | 2019-05-31 | 2021-10-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Level shifter |

| CN110601690B (zh) * | 2019-10-10 | 2024-10-01 | 无锡安趋电子有限公司 | 一种低工作电压的快速下行电平移位电路 |

| US11031054B1 (en) * | 2020-01-22 | 2021-06-08 | Micron Technology, Inc. | Apparatuses and methods for pre-emphasis control |

| US11437997B1 (en) * | 2021-09-30 | 2022-09-06 | Texas Instruments Incorporated | Level shifter circuit |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4039862A (en) * | 1976-01-19 | 1977-08-02 | Rca Corporation | Level shift circuit |

| JPH04192622A (ja) * | 1990-11-22 | 1992-07-10 | Nec Corp | 半導体集積回路 |

| JPH06243680A (ja) * | 1993-02-22 | 1994-09-02 | Mitsubishi Electric Corp | 信号レベル変換回路 |

| JPH07254275A (ja) * | 1994-01-31 | 1995-10-03 | Toshiba Corp | 半導体記憶装置 |

| US6002290A (en) * | 1997-12-23 | 1999-12-14 | Sarnoff Corporation | Crisscross voltage level shifter |

| US6445210B2 (en) | 2000-02-10 | 2002-09-03 | Matsushita Electric Industrial Co., Ltd. | Level shifter |

| JP3477448B2 (ja) * | 2000-02-10 | 2003-12-10 | 松下電器産業株式会社 | レベルシフト回路 |

| US6853234B2 (en) * | 2003-06-09 | 2005-02-08 | International Business Machines Corporation | Level shift circuitry having delay boost |

| US20070164789A1 (en) * | 2006-01-17 | 2007-07-19 | Cypress Semiconductor Corp. | High Speed Level Shift Circuit with Reduced Skew and Method for Level Shifting |

| US20070188194A1 (en) | 2006-02-15 | 2007-08-16 | Samsung Electronics Co: Ltd. | Level shifter circuit and method thereof |

| JP2007259005A (ja) * | 2006-03-23 | 2007-10-04 | Renesas Technology Corp | 半導体集積回路 |

-

2008

- 2008-01-31 US US12/023,276 patent/US7884645B2/en active Active

-

2009

- 2009-01-28 JP JP2010545100A patent/JP5215415B2/ja not_active Expired - Fee Related

- 2009-01-28 KR KR1020107019370A patent/KR101197836B1/ko not_active IP Right Cessation

- 2009-01-28 EP EP09705398A patent/EP2248260A1/en not_active Withdrawn

- 2009-01-28 WO PCT/US2009/032203 patent/WO2009097315A1/en active Application Filing

- 2009-01-28 CN CN2009801070899A patent/CN101965684A/zh active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| US20090195268A1 (en) | 2009-08-06 |

| WO2009097315A1 (en) | 2009-08-06 |

| KR101197836B1 (ko) | 2012-11-05 |

| EP2248260A1 (en) | 2010-11-10 |

| US7884645B2 (en) | 2011-02-08 |

| JP2011511567A (ja) | 2011-04-07 |

| KR20100107068A (ko) | 2010-10-04 |

| CN101965684A (zh) | 2011-02-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5215415B2 (ja) | レベルシフティング回路および方法 | |

| JP2011511567A5 (ja) | ||

| JP5680682B2 (ja) | 単一のクロックドトランジスタを含むシーケンシャル回路素子 | |

| US9785601B2 (en) | System and method for reducing cross coupling effects | |

| US9124276B2 (en) | Sense amplifier including a level shifter | |

| JP2006054886A (ja) | ロー漏洩電流を持つレベルシフタ | |

| US7109758B2 (en) | System and method for reducing short circuit current in a buffer | |

| KR20090123004A (ko) | 전압 스윙을 제어하는 회로 장치 및 방법 | |

| JP2016510201A (ja) | 信号比較電圧範囲を拡大するための回路および方法 | |

| KR100550143B1 (ko) | 시모스 드라이버회로를 구비한 반도체장치 | |

| JPH08116249A (ja) | データ出力バッファ | |

| JP2011061289A (ja) | 入力バッファ回路 | |

| JP2007060582A (ja) | 論理回路、半導体集積回路および携帯端末装置 | |

| US6462613B1 (en) | Power controlled input receiver | |

| JPH11136108A (ja) | 出力回路 | |

| KR100792356B1 (ko) | 반도체 메모리 소자 및 그의 구동방법 | |

| JP2003234649A (ja) | 入出力バッファ回路 | |

| JP2006033060A (ja) | ダイナミック回路 | |

| KR20050009419A (ko) | 데이타 출력 장치 | |

| KR20050033320A (ko) | 딜레이 신호 생성 회로 | |

| JP2006311176A (ja) | クロック検出回路ならびにそれを用いた信号処理回路、情報端末装置 | |

| KR20020054856A (ko) | 프리차지 회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A524 | Written submission of copy of amendment under article 19 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A524 Effective date: 20120409 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120713 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120724 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20121024 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20121031 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20121126 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20121203 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121225 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130129 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130228 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160308 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |